### Alma Mater Studiorum – Università di Bologna

### DOTTORATO DI RICERCA IN

### INGEGNERIA ELETTRONICA, TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE

Ciclo XXXII

| Settore Concorsuale: 09/ | E3 - ELETTRONICA |

|--------------------------|------------------|

|--------------------------|------------------|

Settore Scientifico Disciplinare: ING-INF/01 - ELETTRONICA

Optimized Biosignals Processing Algorithms for New Designs of Human Machine Interfaces on Parallel Ultra-Low Power Architectures

Presentata da: MONTAGNA FABIO

Coordinatore Dottorato Supervisore

Prof. COSTANZO ALESSANDRA Prof. BENINI LUCA

Esame finale anno 2020

### ALMA MATER STUDIORUM - UNIVERSITY OF BOLOGNA

# Optimized Biosignals Processing Algorithms for New Designs of Human Machine Interfaces on Parallel Ultra-Low Power Architectures

by Fabio Montagna

A thesis submitted for the degree of Doctor of Philosophy

in the

Faculty of Engineering

Department of Electrical, Electronic, and Information Engineering (DEI)

February 2020

#### ALMA MATER STUDIORUM - UNIVERSITY OF BOLOGNA

### **Abstract**

Faculty of Engineering

Department of Electrical, Electronic, and Information Engineering (DEI)

Doctor of Philosophy

by Fabio Montagna

The aim of this dissertation is to explore Human Machine Interfaces (HMIs) in a variety of biomedical scenarios. The research addresses typical challenges in wearable and implantable devices for diagnostic, monitoring, and prosthetic purposes, suggesting a methodology for tailoring such applications to cutting edge embedded architectures. The main challenge is the enhancement of high-level applications, also introducing Machine Learning (ML) algorithms, using parallel programming and specialized hardware to improve the performance. The majority of these algorithms are computationally intensive, posing significant challenges for the deployment on embedded devices, which have several limitations in term of memory size, maximum operative frequency, and battery duration. The proposed solutions take advantage of a Parallel Ultra-Low Power (PULP) architecture, enhancing the elaboration on specific target architectures, heavily optimizing the execution, exploiting software and hardware resources. The thesis starts by describing a methodology that can be considered a guideline to efficiently implement algorithms on embedded architectures. This is followed by several case studies in the biomedical field, starting with the analysis of a Hand Gesture Recognition, based on the Hyperdimensional Computing algorithm, which allows performing a fast on-chip re-training, and a comparison with the state-of-the-art Support Vector Machine (SVM); then a Brain Machine Interface (BCI) to detect the respond of the brain to a visual stimulus follows in the manuscript. Furthermore, a seizure detection application is also presented, exploring different solutions for the dimensionality reduction of the input signals. The last part is dedicated to an exploration of typical modules for the development of optimized ECG-based applications.

## Acknowledgements

I am especially indebted to Prof. Luca Benini for his invaluable research support and academic advice during the entire period of my PhD. I specifically appreciated Prof. Davide Rossi and Dr. Simone Benatti's extensive personal and professional guidance and provision of precious knowledge. I special thanks to Prof. David Atienza Alonso and the ESL Lab from EPFL that hosted me for 6 months. I would like to thanks my lab-mates Victor, Alberto, Mattia, Emanuele, Manu, Tommaso, Beppe, Angelo, Marco, ..., and the entire PULP team, for all the coffee breaks and (of course) the great technical advises. In the end, I am grateful to my parents, siblings, relatives, and friends for all their psychological support without which I would not have been able to go through this challenging work.

# **Contents**

| Al | bstrac  | et            |                                                                     | iv  |

|----|---------|---------------|---------------------------------------------------------------------|-----|

| A  | cknov   | vledgem       | nents                                                               | vi  |

| Li | st of l | Figures       |                                                                     | Xi  |

| Li | st of   | <b>Fables</b> |                                                                     | xiv |

| Al | bbrev   | iations       |                                                                     | XV  |

| 1  | Intr    | oductio       | n                                                                   | 1   |

|    | 1.1     |               | Context                                                             | 1   |

|    | 1.2     | Thesis        | Contribution                                                        | 2   |

|    | 1.3     |               | Structure                                                           |     |

| 2  | Bac     | kground       | d                                                                   | 7   |

|    | 2.1     | Biome         | dical Applications: an Overview                                     | 7   |

|    | 2.2     | Target        | Architectures                                                       | 11  |

|    |         | 2.2.1         | ARM Cortex M4                                                       | 13  |

|    |         | 2.2.2         | PULP platform                                                       | 14  |

|    |         |               | 2.2.2.1 PulpV3 Architecture                                         | 15  |

|    |         |               | 2.2.2.2 Mr.Wolf Architecture                                        | 15  |

|    | 2.3     | Metho         | dology                                                              | 17  |

|    |         | 2.3.1         | Software Optimization: Parallelization Paradigms                    | 18  |

|    |         |               | 2.3.1.1 Programming Model and Toolchain                             | 18  |

|    |         | 2.3.2         | Hardware Optimization: RI5CY ISA Extension                          | 20  |

|    |         | 2.3.3         | Memory Management Optimization: Double Buffering                    | 20  |

| 3  |         |               | ications for Human Machine Interfaces                               | 23  |

|    | 3.1     |               | Signals                                                             | 23  |

|    |         | 3.1.1         | Signal Description and Acquisition                                  |     |

|    | 3.2     |               | Learning and Classification for EMG-Based Hand Gestures Recognition |     |

|    |         | 3.2.1         | Related Work                                                        | 24  |

|    |         | 3.2.2         | Support Vector Machine                                              | 27  |

|    |         | 3.2.3         | Hyperdimensional Computing                                          | 29  |

Contents

|   |     |          | 3.2.3.1               | Implementation on the PULP platform                          | 31       |

|---|-----|----------|-----------------------|--------------------------------------------------------------|----------|

|   |     |          | 3.2.3.2               | Implementation and Optimization on Mr.Wolf                   | 32       |

|   |     |          | 3.2.3.3               | Parallelization and Memory Requirements                      | 33       |

|   |     | 3.2.4    | Experim               | ental Results                                                | 34       |

|   |     |          | 3.2.4.1               | Comparison of the HD computing with SVM on ARM Cortex M4     | 35       |

|   |     |          | 3.2.4.2               | HD computing on PULPv3 versus ARM Cortex M4                  | 37       |

|   |     |          | 3.2.4.3               | Comparison between SVM and HD computing of Training          | 5,       |

|   |     |          | 0.2                   | Times and Classification Accuracy                            | 38       |

|   |     |          | 3.2.4.4               | Evaluation of Execution Performance                          | 39       |

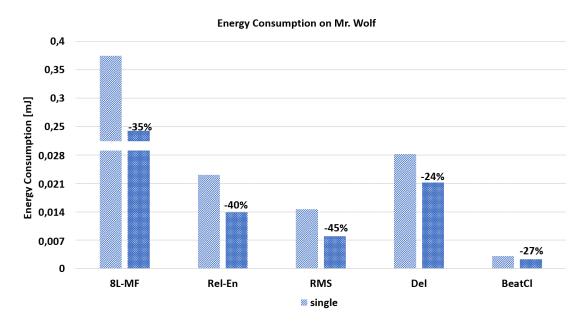

|   |     |          | 3.2.4.5               | Evaluation of Energy Consumption                             | 42       |

|   |     | 3.2.5    | Scalabili             | ty                                                           | 44       |

|   |     | 3.2.6    | Discussion            | on                                                           | 46       |

| 4 | EEG | S Applic | cations for           | Brain Machine Interfaces                                     | 48       |

|   | 4.1 | EEG S    | -                     |                                                              | 48       |

|   |     | 4.1.1    |                       | escription and Acquisition                                   | 48       |

|   | 4.2 |          |                       | e-Range Frequency Tagging Analysis in Embedded Neuromon-     |          |

|   |     | _        | -                     |                                                              | 49       |

|   |     | 4.2.1    |                       | Work                                                         | 50       |

|   |     | 4.2.2    |                       | and EEG Acquisition Setup                                    | 53       |

|   |     | 4.2.3    |                       | analysis                                                     | 54       |

|   |     |          | 4.2.3.1               | Pre-processing and artifact removal                          | 54       |

|   |     | 4.0.4    | 4.2.3.2               | Frequency-Tagging Analysis (FTA)                             | 54       |

|   |     | 4.2.4    |                       | ed Analysis                                                  | 55       |

|   |     |          | 4.2.4.1               | Artifact Removal                                             | 55       |

|   |     | 105      | 4.2.4.2               | Frequency Tagging Analysis (FTA)                             | 56       |

|   |     | 4.2.5    |                       | entation on PULP                                             | 58       |

|   |     | 4.2.6    | 4.2.6.1               | ental Results                                                | 61       |

|   |     |          | 4.2.6.1               | Execution Time Estimation                                    | 61<br>62 |

|   |     |          | 4.2.6.2               | Frequency Detection                                          | 63       |

|   |     | 4.2.7    | 4.2.0.3<br>Discussion |                                                              | 65       |

|   | 4.3 |          |                       | n Algorithms for an Efficient Implementation on Embedded De- | 0.5      |

|   | т.Э |          |                       |                                                              | 66       |

|   |     | 4.3.1    |                       | Work                                                         | 66       |

|   |     | 4.3.2    |                       | Component Analysis-based Seizure Detection                   | 69       |

|   |     |          | 4.3.2.1               | Parallel Implementation on PULP                              | 70       |

|   |     |          | 4.3.2.2               | Dimensionality Reduction                                     | 71       |

|   |     |          | 4.3.2.3               | Feature Extraction                                           | 72       |

|   |     |          | 4.3.2.4               | Pattern Recognition                                          | 72       |

|   |     | 4.3.3    |                       | oint Implementation                                          | 72       |

|   |     | 4.3.4    |                       | ental Results                                                | 74       |

|   |     |          | 4.3.4.1               | Experimental Setup                                           | 74       |

|   |     |          | 4.3.4.2               | Seizure Detection Accuracy                                   | 75       |

|   |     |          | 4.3.4.3               | Evaluation of Execution Performance                          | 76       |

|   |     |          | 4.3.4.4               | Hybrid Implementation Performance                            | 77       |

<u>Contents</u> x

|    |        |          | 4.3.4.5 Energy Considerations and Comparison with Commercial MCUs | 78 |

|----|--------|----------|-------------------------------------------------------------------|----|

|    |        | 4.3.5    | Discussion                                                        | 80 |

|    |        | 4.3.6    | Compressed Sensing-based Seizure Detection                        | 81 |

|    |        |          | 4.3.6.1 Experimental Results                                      | 83 |

|    |        |          | 4.3.6.2 Parallel Implementation on PULP                           | 84 |

|    |        |          | 4.3.6.3 Evaluation of the performance                             | 85 |

|    |        | 4.3.7    | Discussion                                                        | 86 |

| 5  | ECO    | G Applic | cations                                                           | 87 |

|    | 5.1    | ECG S    | Signals                                                           | 87 |

|    |        | 5.1.1    | Signal Description and Acquisition                                | 87 |

|    | 5.2    | Modula   | ar Design and Optimization of Kernels for the Development of ECG- |    |

|    |        |          |                                                                   | 88 |

|    |        | 5.2.1    | Filtering                                                         | 89 |

|    |        | 5.2.2    | Signal Enhancement                                                | 90 |

|    |        | 5.2.3    | Signal delineation                                                | 91 |

|    |        | 5.2.4    | Inference                                                         | 91 |

|    |        | 5.2.5    | Experimental setup and Results                                    | 92 |

|    |        | 5.2.6    | Future Work                                                       | 93 |

| 6  | Con    | clusion  |                                                                   | 95 |

|    |        |          |                                                                   |    |

| Bi | bliogi | raphy    |                                                                   | 98 |

# **List of Figures**

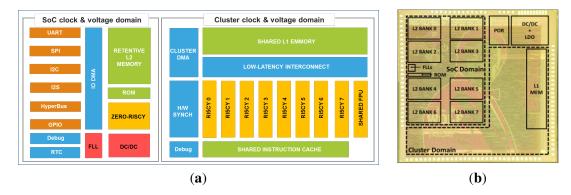

| 1.1 | Thesis structure diagram                                                                                                                                                                                                                    | 6  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

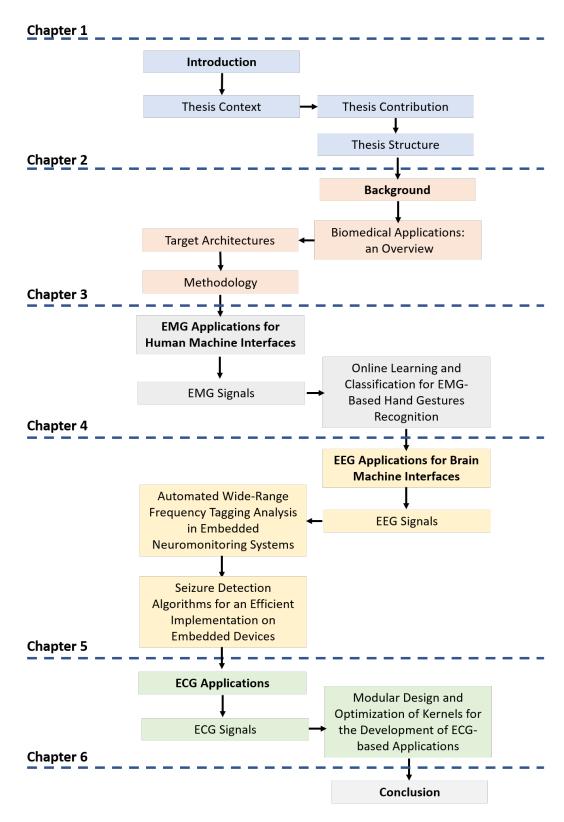

| 2.1 | A general view of the Parallel Ultra-Low Power (PULP) architecture (a) and the layout of the PULPv3 chip used for performance and power characterization (b).                                                                               | 14 |

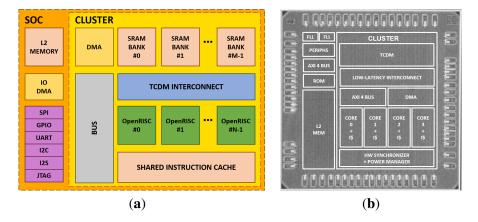

| 2.2 | A general view of the Parallel Ultra-Low Power (PULP) architecture (a) and the layout of the Mr. Wolf chip used for performance and power characterization                                                                                  |    |

|     | (b)                                                                                                                                                                                                                                         | 16 |

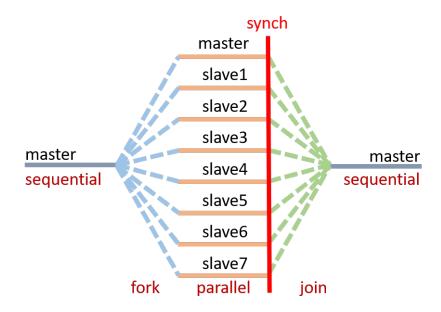

| 2.3 | Fork/Join paradigm                                                                                                                                                                                                                          | 18 |

| 2.4 | Double Buffering                                                                                                                                                                                                                            | 21 |

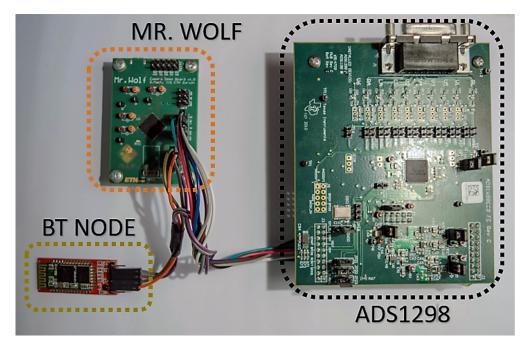

| 3.1 | Picture of the tested system. EMG data are acquired with an external ADC (ADS1298), connected to the wolf chip. Output and communication are man-                                                                                           |    |

|     | aged via a BT node                                                                                                                                                                                                                          | 28 |

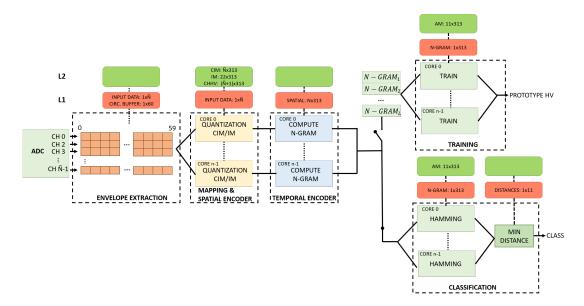

| 3.2 | Implementation on PULP platform of the processing chain. The first three kernels are in common for both training and classification phase. The open/closed switches are there just for a visual idea and the meaning is that once the model |    |

|     | is created during the training phase, we will not use that kernel anymore and we                                                                                                                                                            |    |

|     | pass to the classification kernel                                                                                                                                                                                                           | 29 |

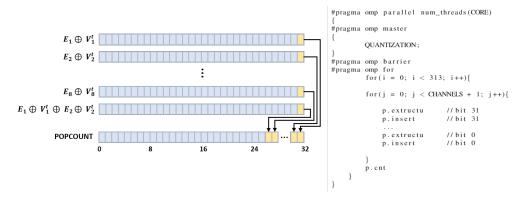

| 3.3 | Illustration of how built-ins (p.extract, p.insert, p.cnt) used in the spatial encoder                                                                                                                                                      |    |

|     | (left). A code snippet to show the usage of builtins and parallelism (OpenMP                                                                                                                                                                |    |

|     | directives) in the processing chain (right)                                                                                                                                                                                                 | 31 |

| 3.4 | Gestures used for the testing. Open hand, fist, index, 2-fingers pinch, rest position.                                                                                                                                                      | 35 |

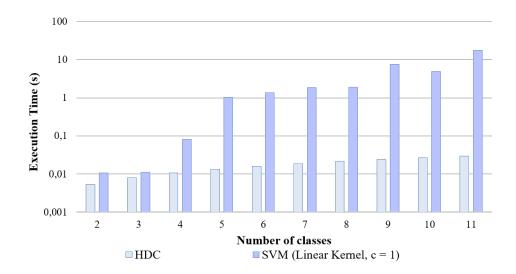

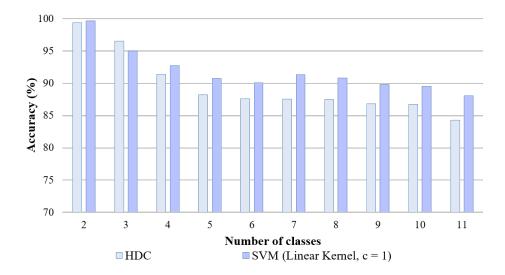

| 3.5 | Estimation of the execution time for the training of SVM and HD Computing increasing the number of gestures (from 1 to 11). Results are presented in loga-                                                                                  |    |

|     | rithmic scale.                                                                                                                                                                                                                              | 36 |

| 3.6 | Average accuracy obtaining by SVM and HD computing, using the same data collected by 10 subjects, increasing the number of gestures (from 1 to 11)                                                                                          | 38 |

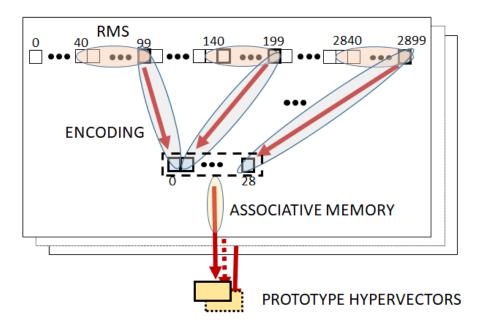

| 3.7 | Sequence of the computational kernels of the HDC training. The first kernel                                                                                                                                                                 |    |

|     | is the RMS, computed on 60-samples windows, every 100ms. Output of the                                                                                                                                                                      |    |

|     | RMS is used by the encoding kernel to calculate the AM vectors. Once the 29                                                                                                                                                                 |    |

|     | vectors of the associative memory are calculated, they are used to calculate the                                                                                                                                                            |    |

|     | prototype hypervectors (1 for each class of the problem)                                                                                                                                                                                    | 40 |

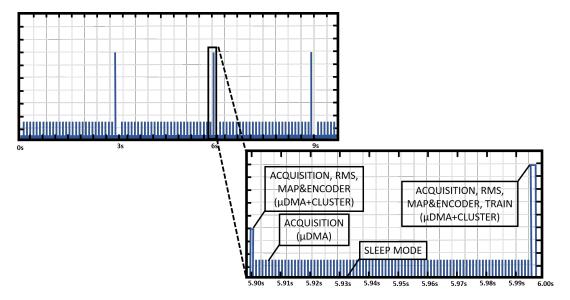

| 3.8 | Power envelope of the training algorithm. EMG samples are acquired during                                                                                                                                                                   |    |

|     | Acquisition steps, whereas PULP cluster is turned off and uDMA manages data                                                                                                                                                                 |    |

|     | transfer from SPI to uDMA. Once the buffer for RMS computation is ready,                                                                                                                                                                    |    |

|     | the cluster is switched on and calculates RMS value and hypervectors for the                                                                                                                                                                |    |

|     | encoder (RMS MAP and ENCODING)                                                                                                                                                                                                              | 41 |

List of Figures xii

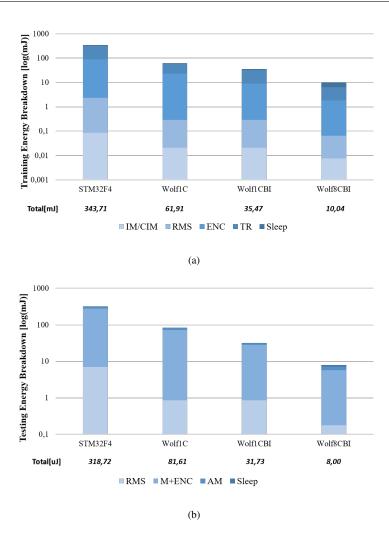

| 3.9        | Energy breakdown during training (a) and testing (b) using the HDC on the target platforms. The bars are plotted in log scale to better show the energy contribution of each function. The total energy consumption at the bottom of the figure is reported in linear scale. Working with 8-cores, Mr. Wolf achieves the lowest energy consumption, saving up to 34x energy with respect to the |          |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|            | commercial STM32F4 MCU                                                                                                                                                                                                                                                                                                                                                                          | 43       |

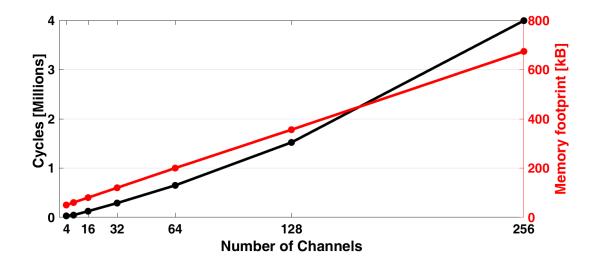

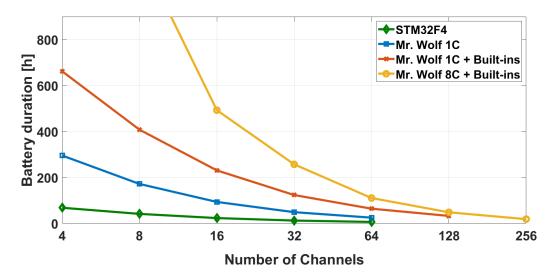

|            | Performance and memory footprint of HD computing, increasing the number of channels. The results refer to 8 cores Mr. Wolf execution with built-ins                                                                                                                                                                                                                                             | 44       |

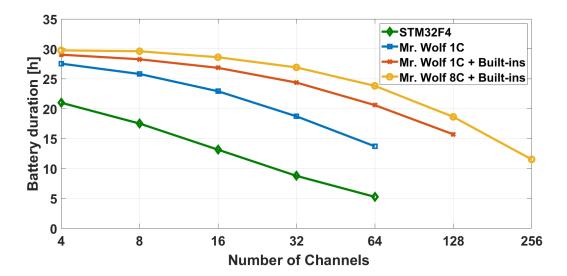

| 3.11       | Battery duration of the target applications including the static power of the ADC with an increasing number of channels. With a fixed latency of 40ms per classification, Mr. Wolf 8-cores, even with a single core, can provide the same                                                                                                                                                       | 4        |

| 3.12       | performance than the commercial STM32 (up to 64 channels)                                                                                                                                                                                                                                                                                                                                       | 45       |

| 4.1        |                                                                                                                                                                                                                                                                                                                                                                                                 | 52       |

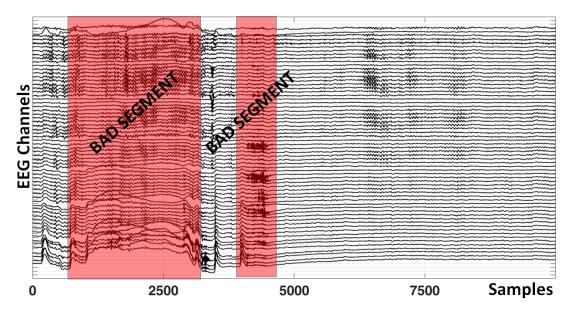

| 4.1        | EEG traces with bad segments                                                                                                                                                                                                                                                                                                                                                                    | 53       |

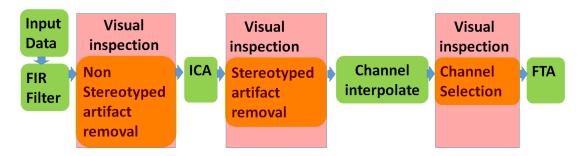

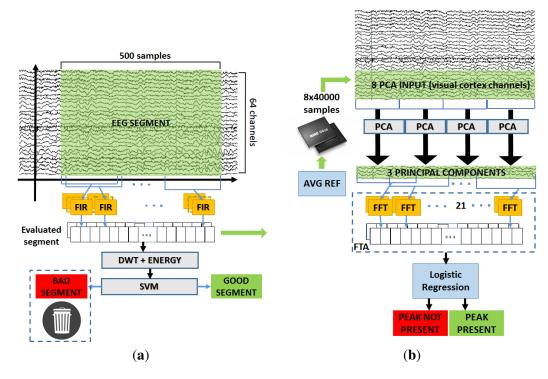

| 4.3        | Block diagram of the automated artifact removal (a) and block diagram of the                                                                                                                                                                                                                                                                                                                    | 33       |

|            | automated frequency detection (b). $\dots$                                                                                                                                                                                                                                                                                                                                                      | 55       |

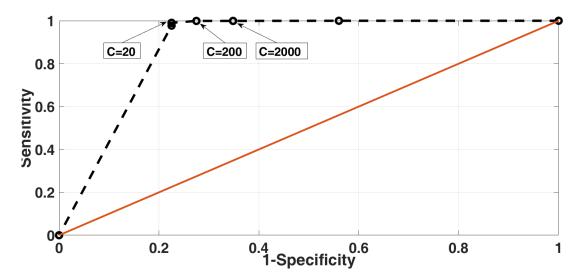

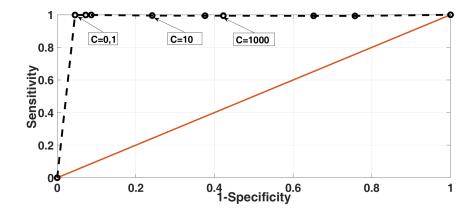

| 4.4        | ROC curve for SVM performance evaluation                                                                                                                                                                                                                                                                                                                                                        | 56       |

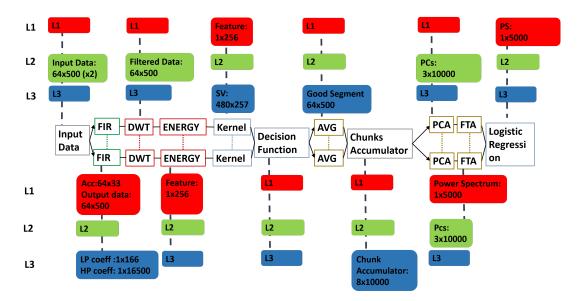

| 4.5        | Automated Artifacts Removal and Frequency Detection computational Kernels.                                                                                                                                                                                                                                                                                                                      | 58       |

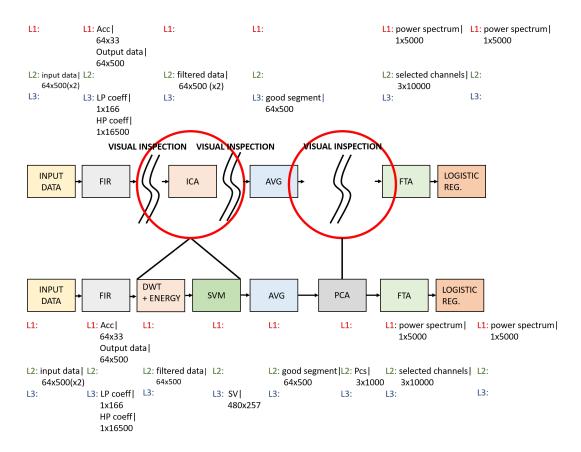

| 4.6        | Comparison of the processing chain of the Standard and Automated Analysis with the most relevant structures for an estimation of memory requirements                                                                                                                                                                                                                                            | 61       |

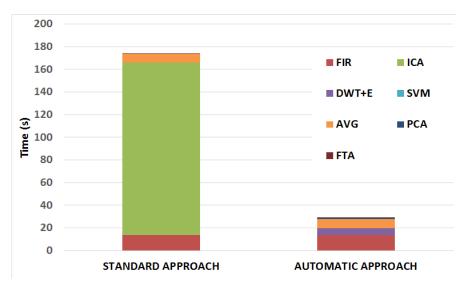

| 4.7        | Estimation of execution times between Standard and Automatic Approaches                                                                                                                                                                                                                                                                                                                         | 62       |

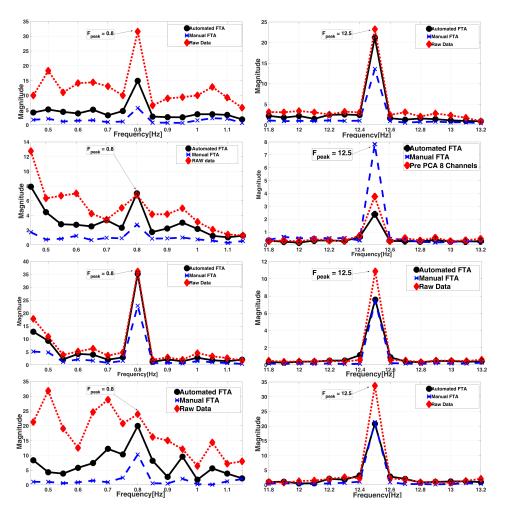

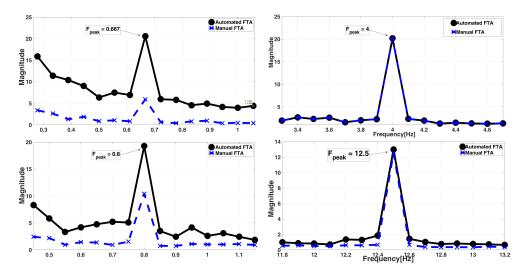

| 4.8        | Peaks obtained from the visual stimulus at 0.8Hz and 12.5Hz. Graphs show values obtained from 4 subjects exposed to stimulus at the target frequencies                                                                                                                                                                                                                                          | 63       |

| 4.9        | Peaks obtained from the visual stimulus at 0.667Hz, 0.8Hz, 4Hz and 12.5Hz. Graphs show mean values obtained from 4 subjects exposed to stimulus at the target frequencies                                                                                                                                                                                                                       | 64       |

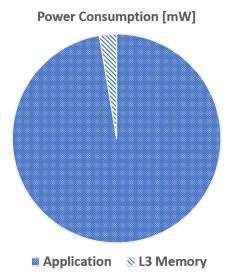

| 4.10       | Estimation of the power consumption of the 8-core execution - application and L3 memory                                                                                                                                                                                                                                                                                                         | 65       |

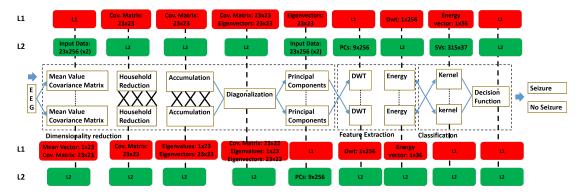

| 4.11       | Seizure detection algorithm processing chain and memory requirement for each block                                                                                                                                                                                                                                                                                                              | 69       |

| 4.12       | ROC curve for SVM performance evaluation                                                                                                                                                                                                                                                                                                                                                        | 71       |

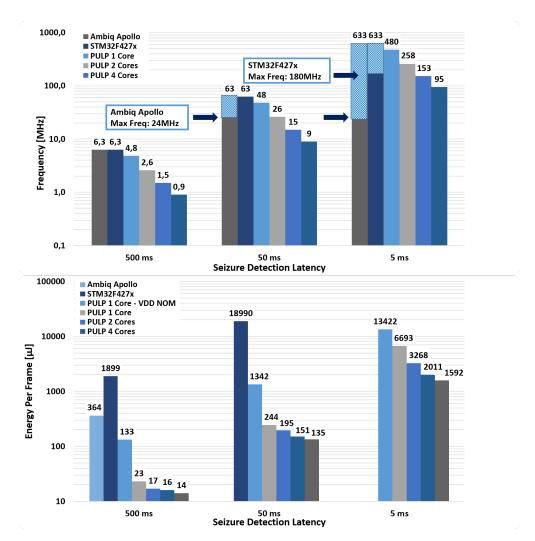

|            | Operating frequency and energy per frame of the hybrid approach on the PULP and commercial MCUs                                                                                                                                                                                                                                                                                                 | 79       |

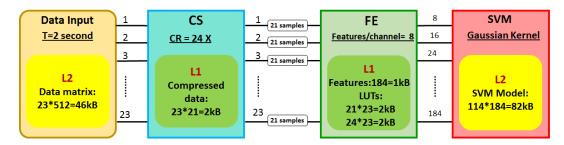

| 4.14       | Seizure detection algorithm processing chain and memory requirement for each block.                                                                                                                                                                                                                                                                                                             | 81       |

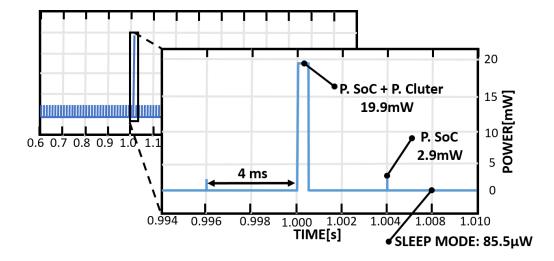

| 4.15       | Mr. Wolf (8-cores) Power consumptions: idle (deep sleep), only the acquisition (SoC), acquisition and elaboration (SoC+Cluster)                                                                                                                                                                                                                                                                 | 84       |

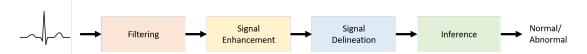

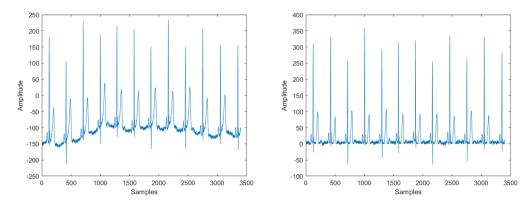

| 5.1<br>5.2 | Modules for a typical ECG application                                                                                                                                                                                                                                                                                                                                                           | 88<br>89 |

List of Figures xiii

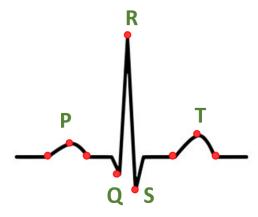

| 5.3 | 3 ECG-signal delineation. The figure highlights the QRS, P and T waves with the |    |  |  |  |  |

|-----|---------------------------------------------------------------------------------|----|--|--|--|--|

|     | onset and offset of the waves.                                                  | 90 |  |  |  |  |

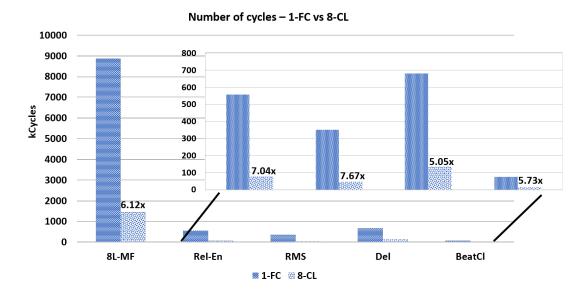

| 5.4 | Execution time in the ECG modules                                               | 92 |  |  |  |  |

| 5.5 | Energy consumption in the ECG modules                                           | 93 |  |  |  |  |

# **List of Tables**

| 3.1  | Comparison between SoA EMG embedded pattern recognition systems and our platform. Systems in [1] and [2] run in computationally hungry platforms and are not suitable for long-term operation, and, although the systems presented in |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | [3] and [4] have a comparable energy/classification as this work, our system is                                                                                                                                                       | 24 |

| 2.2  | capable of providing more than 2.7x improvement in battery life                                                                                                                                                                       | 26 |

| 3.2  | Comparison of HD computing (200-D) versus SVM at iso-accuracy on ARM                                                                                                                                                                  | 2. |

|      | Cortex M4. The results refer to a 10 ms detection latency                                                                                                                                                                             | 36 |

| 3.3  | Detailed power (P) comparison of HD algorithm on the ARM Cortex M4 and                                                                                                                                                                |    |

|      | PULPv3 based on number of cycles (CYC) and frequency (FREQ). The results                                                                                                                                                              | 27 |

| 2.4  | refer to a 10 ms detection latency                                                                                                                                                                                                    | 37 |

| 3.4  | HD Computing Execution times on the target architectures, with 10,000-D,                                                                                                                                                              |    |

|      | N=1. (Cyc, su) stand for (cycles, speed-up). The total energy/class reported, is the result of the addition of the contribution of these functions without con-                                                                       |    |

|      | sidering the energy during idle periods.                                                                                                                                                                                              | 39 |

|      | sidering the energy during fale periods                                                                                                                                                                                               | 39 |

| 4.1  | Comparison with state-of-the-art of Artifact Removal                                                                                                                                                                                  | 50 |

| 4.2  | Comparison with state-of-the-art of Frequency Tagging                                                                                                                                                                                 | 50 |

| 4.3  | Execution of automated frequency tagging analysis on embedded computing                                                                                                                                                               |    |

|      | platform                                                                                                                                                                                                                              | 64 |

| 4.4  | Comparison with the state of the art of seizure detection implementation                                                                                                                                                              | 67 |

| 4.5  | Accuracy and Precision obtained from MATLAB and PULP platform floating-                                                                                                                                                               |    |

|      | and fixed-point executions                                                                                                                                                                                                            | 75 |

| 4.6  | Execution of floating-point seizure detection on the embedded computing plat-                                                                                                                                                         |    |

|      | form                                                                                                                                                                                                                                  | 76 |

| 4.7  | Execution of fixed-point seizure detection on embedded computing platform                                                                                                                                                             | 77 |

| 4.8  | Execution time on the PULP platform                                                                                                                                                                                                   | 78 |

| 4.9  | Energy per frame on the PULP platform in J with 5-ms real-time constraint                                                                                                                                                             | 78 |

| 4.10 | Accuracy, sensitivity and specificity using data from 5 randomly chosen subjects                                                                                                                                                      |    |

|      | of the CHB-MIT dataset                                                                                                                                                                                                                | 83 |

| 4.11 | Proposed implementation on both ARM Cortex M4 [5] and Mr.Wolf. PP, FE,                                                                                                                                                                |    |

|      | C and TOT stand for pre-processing, feature extraction, classification and total,                                                                                                                                                     |    |

|      | while kCyc, ld, sp, E stand for thousands of cycles, load, speed-up and Energy.                                                                                                                                                       | 83 |

## **Abbreviations**

ADC Analog to Digital Converter

AFE Analog Front-End

AP Active Potential

ASIC Application Specific Integrated Circuit

ASSR Auditory Steady-State Response

BLE Bluetooth Low Energy

BT BlueTooth

CMOS Complementary Metal-Oxide Semiconductor

CORDIC COordinate Rotation DigItal Computer

**CR** Compression Ratio

**CS** Compressing Sensing

**DCT** Discrete Cosine Transform

DMA Direct Memory Access

**DSP** Digital Signal Processing

**DT** Decision Tree

**DWT** Discrete Wavelet Transform

ECG ElectroCardioGraphy

EEG ElectroEncephaloGraphy

EMG Electro Myo Graphy

**EPSP** Excitatory PostSynaptic Potential

**ERP** Event-Related Potential

FD-SOI Fully Depleted-Silicon On Insulator

FE Feature Extraction

FFT Fast Fourier Transform

FIR Finite Inpulse Response

Abbreviations xvi

FLL Frequency-Locked Loop

fMRI functional Magnetic Resonance Imaging

FPU Floating Point Unit

FTA Frequency Tagging Analysis

FWL Fractional Word Length

GMM Gaussian Mixture Model

GPIO General Purpose Input Output

HMI Human Machine Interfaces

HPF High Pass Filters

IA Instrumentation Amplifier

ICA Independent Component Analysis

**IoT** Internet of Things

ISA Instruction Set Architecture

IWA Integer Word Length

JTAG Joint Test Action Group

KNN K- Nearest Neighbor

LDO LowDropOut

LDA Linear Discriminant Analysis

LUT Look Up Tables

LPF Low Pass Filter

LSP Lomb-Scargle Periodogram

MAC Multiply-ACcumulate

MCU MicroController Unit

MEG MagnetoEncephaloGraphy

NP Normalized Power

PC Principal Component

PCA Principal Component Analysis

PULP Parallel Ultra-Low Power

QSPI Quad Serial Peripheral Interface

RBPNN Radial Basis Probabilistic Neural Network

**ROC** Receiver Operating Characteristic

RTC Real-Time Clock

SCM Standard Cell Memory

Abbreviations xvii

SIMD Single Instruction Multiple Data

SoC System on Chip

SNR Signal-to-Noise Ratio

SPI Serial Peripheral Interface

SRAM Static Random Access Memory

SSVEP Steady State Visually Evoked Potentials

SVD Singular Vector Decomposition

SVM Support Vector Machine

TCDM TightlyCoupled Data Memory

WPD Wavelet Packet Decomposition

to my lovely family.

## **Chapter 1**

### Introduction

#### 1.1 Thesis Context

Recent advances in bio-sensing and computing technology are enabling a wide range of cutting edge Human-Machine Interfaces (HMIs). Researchers have been working on HMIs to develop efficient devices for several purposes, among which the treatment of neurological pathology, monitoring and rehabilitation, to augment human abilities, restoring the daily life habits of a user. The fast improvement in the design of miniaturized and efficient electronic devices enables the development of unobtrusive implantable and wearable personal health care systems. In general, biosignals such as ECG, EEG, EMG (ExG) result from the physiological activity of the body, allowing to highlight biomedical parameters directly connected to the subject health status or simply to extract patterns that enable direct communication with the external environment.

ExG applications are widely used in various scenarios, ranging from consumer electronics (i.e. fitness, recreational) to medical-grade devices (i.e. patient monitoring, rehabilitation, prosthetic). For instance, ECG processing for the heart rate monitoring is employed in smartwatches for fitness, pacemakers [6] and Holter devices [7]. EEG based systems are becoming increasingly popular in medical applications for the treatment of neurological disorders, such as Parkinsons [8], epilepsy [9], spinal cord injuries [10], [11], [12] as well as attention loss, drowsiness [13] and autism detection [14]. Furthermore, implantable EMG recording has been extensively explored in research [15]; nevertheless, surface EMG devices for wearable systems are preferred thanks to their unobtrusiveness. It has been demonstrated that they are feasible for multiple applications, including the controllers of the upper limp prostheses[16] and hand gesture recognition systems for consumer Human-Machine interaction.

Due to the intrinsic variability of biosignals, in addition to an adequate signal conditioning and pre-processing phase, algorithms from the machine learning area are often necessary to

reach high accuracy in recognition, as required by medical standards. However, this requires substantial computational capabilities and very low power consumption that only became suitable for wearable or implantable devices in the last years. For this reason, the first studies on ExG were performed offline on benchtop platforms [17], which offered all the required computational power. The advances in digital low-power design and efficient computational architectures [18], [19] made possible the design of real-time systems able to execute algorithms like advanced filtering [20], dimensionality reduction [19] and pattern recognition [21].

Notwithstanding, several challenges are still open for the design of efficient real-time systems for the processing of ExG signals. The solution to these challenges requires a multilevel approach, ranging from the design of Analog Front Ends (AFE) and digital processor to the system level architecture and algorithms. A highly efficient multi-core platform, designed for ultra-low power processing allows the execution of computationally demanding algorithms complying with real-time requirements, bounding the power consumption to a few mW using power management techniques coupled with voltage scaling up to near-threshold computing. Among the possible commercial and academic solutions, it is worth to explore the capabilities of the PULP platform, compared with the ARM Cortex M4, widely used in embedded devices. It has been largely demonstrated that the PULP-based architectures offer high computational power, but still remaining in the ultra-low power budget, making them feasible for a wide range of applications, going from IoT, drones control, image processing, and finally to biomedical applications.

### **1.2** Thesis Contribution

The main contribution of this dissertation is the definition of a methodology to develop algorithms for the processing of different kinds of biosignals, focusing the attention on cutting edge parallel ultra-low power architectures and the derived benefits compared to the use of commercial micro-controllers (MCUs). The thesis offers guidelines to efficiently target biomedical applications on embedded devices, typically characterized by having limited resources. In particular, the description focuses on how to take advantage of the architectural behaviors using both software and hardware optimizations, such as parallel programming, specialized hardware, and memory management. Parallel computing helps in solving tasks that require to respect strict real-time requirements, which are impossible to reach with the maximum operative frequency of a single processing unit. In the case on which a single processing unit is enough to respect the latency constraint, the use of multiple cores working at a lower (and more efficient) operative frequency can lead to a considerable energy saving. In some architectures, the exploration of specialized hardware oriented to solve simple operations in a few clock cycles, further improves

the performance in latency and energy consumption. The memory management can be challenging in embedded devices, in particular for architectures that feature multi-level memories and for applications, which require frequent data transfers. For the architectures that feature a Direct Memory Access (DMA), the implementation of a policy to move data from one memory to another helps to reduce the overhead of the transfers and, thus, the latency.

Another contribution of this dissertation is the presentation of several case studies of different ExG applications, addressing challenges not only at system level but also at application level. Results in terms of execution time and energy consumption, with a detailed state-of-the-art (SoA) analysis, highlight the benefits derived from the use of software and hardware optimization applied in real applications. For instance, a challenge addressed in this thesis is related to the training of the algorithm for an EMG-based hand gesture recognition. This phase usually requires an off-line elaboration using an external device, not feasible for a fully embedded system, where several re-training sessions are necessary for the correct functionality of the device. In this scenario, the main contribution is the development of an algorithm suitable for real-time one-shot learning. To the best of my knowledge, this is the first time that a full EMG-based wearable system with online learning is being implemented. It has been demonstrated that the proposed solution is comparable with the well-known SoA method Support Vector Machine (SVM) and that the system can be scaled up efficiently to a higher number of channels for other more intensive ExG applications.

Focusing the attention on the EEG, during the acquisition the signal is prone to the noise coming from different sources such as power-line interference, movement and muscular artifacts. Considering as a possible task the detection of frequency as a response to an external stimulus, this noise significantly degrades the signal, which can reduce the system ability to detect very low frequencies. For this reason, for the noise that can not be removed using filters, the classical approach usually involves several sessions of visual inspection performed by a clinician to remove bad segments from the input data. The contribution in this field is the implementation of a fully automatic approach to remove bad segments from the input signals and, then, to perform all the processing for the detection of the target frequencies on-chip, providing immediate feedback to the user. Moreover, the EEG signals are usually acquired by multiple electrodes that cover the entire surface of the scalp of a subject. The number of electrodes ranges from 4 to 256, leading to a huge quantity of data. The embedded devices mainly feature small memories, with limited storage capacity. The processing of a huge quantity of inputs can lead to latency not compliant with the medical standards. Therefrom, dimensionality reduction algorithms help to remove all the redundancies in the data, drastically reducing the memory requirements and the latency of the processing. In this dissertation, two different approaches are compared, namely Principal Component Analysis and the Compressing Sensing (CS), showing a reduction of the computational complexity while maintaining the same accuracy.

### 1.3 Thesis Structure

The rest of the thesis is organized as follows.

Chapter 2 gives an overview of the commercial MCU (ARM Cortex M4) and the PULP platform, describing in detail the architectures targeted in this dissertation. Moreover, the same chapter shows a possible methodology that can be followed during the development of a variety of applications in several fields such as IoT, imagine processing, biomedical, etc. The suggested methodology can be considered as a guideline that helps the user during the developing process, giving some tips for the improvement of the efficiency. In particular, depending on the architecture, software and hardware optimization can be included in the implementation. In this chapter, a software optimization centered on the parallel paradigm is presented, with some guidelines on how to proceed during the parallelization of an algorithm. Then, hardware optimization is also presented, describing the RI5CY ISA extensions such as optimized instructions for loads and stores, ALU extensions, MAC operations, etc. The last optimization is related to memory management and how to efficiently handle the data transfers between the high latency external memory to the low latency internal one.

Furthermore, a collection of applications in the biomedical field are presented as case studies, showing the improvements derived by the integration of the optimization in performance. In particular, in Chapter 3, an EMG-based hand gesture recognition is implemented on embedded devices, based on two ML classification mechanisms. The first one based on the state of the art SVM and the second one on HD computing. Both approaches are compared in terms of execution time, energy consumption and training time.

In Chapter 4, several case studies related to the implementation of BMIs are presented. In this chapter, different kinds of pre-processing for the EEG signals are explored. Specifically, the first application is based on the FTA for the detection of the brain's response to an external visual stimulus. An automatic approach for the artifacts' removal is presented, that is compared to the classic approach that makes use of very complex algorithms (i.e. Independent Component Analysis), requiring manual inspection of the EEG traces performed by a clinician. Then, all the kernels that compose the final application are described, presenting results related to execution time and energy consumption of the final system. The second application targets the prediction of seizures in epileptic subjects and it is based on two different approaches are explored, differing from dimensionality reduction algorithm and feature extraction.

In Chapter 5, a description of the ECG signals is done, with an exploration of a collection of typical kernels that can be used for the development of a complete ECG-based system. We show results derived by the parallel computing on these kernels in terms of execution time and energy consumption.

Finally, in Chapter 6 conclusion and feature works are drawn to understand the direction of the research for future improvements.

**Figure 1.1:** Thesis structure diagram.

## **Chapter 2**

# **Background**

### 2.1 Biomedical Applications: an Overview

Traditionally, the monitoring of the signals acquired from the human body has been done in the laboratories under the supervision of clinicians. Researchers have been trying to improve people's quality of life, developing devices able to produce reliable data that can be used independently outside the medical environment and analyzed by clinicians to track health status or to detect specific events, providing immediate feedback. Moreover, the elaboration of all the information collected during the monitoring is also essential for off-line explorations to improve the knowledge of human body's behaviors. In the last years, with the fast progress in technologies, huge improvements have been done in biomedical devices. Nonetheless, there are still a variety of possible scenarios that require further improvements. For this dissertation, we explore possible applications for an efficient EMG-based hand gesture recognition, a frequency tagging analysis using EEG signals and a seizure detection algorithm. Before going into deeper details in the next chapters, an overview of each application scenario can be useful to have a general idea about the topics and the possible issues and challenges we might deal with.

Since interacting with hands represents one of the most intuitive ways to enable human-to-human or human-to-machine interactions, hand gesture recognition is the key element in designing solutions that can enable natural and advanced ways of communication between objects and users in many domains, in the wake of the IoT growing trend. The two major approaches used for hand gesture recognition are based on the processing of information coming from video cameras [22] and from muscular activity [23]. Video-based hand gesture recognition relies on computer vision techniques, which recognize users' hand gestures in a scene and decode the hand gestures using pattern recognition algorithms. Although this approach can decode a wide number of gestures, it suffers from ambient illumination variability and possible obstacles in the line of sight. Furthermore, it requires a bulky and fixed setup.

Another viable approach is inspired by hand prosthetic systems, where the muscular activity detected by the electromyographic (EMG) signals is used to decode the user's intention. Commercial prosthetic systems [24, 25] decode predefined bursts of muscular contractions into a set of gestures (i.e. 2 consecutive contractions mean hand closures, 3 consecutive contractions stands for hand opening, etc.). Such a method is highly reliable and amenable to implement on a wearable system. However, it requires a long learning curve and high levels of concentration of the user since it is a non-intuitive interface [26]. An approach that is gaining traction is based on machine learning (ML) techniques to analyze EMG signal patterns during muscular contractions. It has been demonstrated that algorithms such as Linear Discriminant Analysis (LDA) [27], Artificial Neural Networks (ANN) [28], Support Vector Machines (SVM) [29], Recursive Least Square [30], Hidden Markov Models (HMM) [4], Naive Bayes [31], Independent Component Analysis (ICA) [32], as well as Convolutional Neural Networks (CNN) [33] reach high level of accuracy, restoring a natural gesture recognition both in prosthetic and consumer Human Machine Interaction (HMI) scenarios.

Using such machine learning algorithms allows tailoring the recognition strategies to the physiological characteristic of the users. However, EMG-based gesture recognition is strongly dependent on the subject (i.e. it depends on subject-specific characteristics such as muscular mass, skin thickness, strength of the mean voluntary contractions), and classification algorithms need a training set for each user. Furthermore, EMG setup is intrinsically variable [34–36] because of fiber crosstalk, skin perspiration, small movements of the skin-to-electrode interface, power line interference and donning/doffing. As such, small changes of the EMG traces can hinder pattern recognition, degrading the system performance down to unacceptable levels [37]. An orthogonal approach consists of extending the training dataset, integrating it with samples coming from multiple sessions to gain up to 20% recognition accuracy [36]. A major drawback of increasing the size of the training dataset or repeating the algorithm training lies into its high computational requirements. For instance, SVM training minimizes a given cost function by solving a convex optimization problem, while in ANN [38] back-propagation requires many iterations to converge. Furthermore, training sessions require a PC or a graphical interface as well as human intervention to perform thresholding and labeling operations [39]. Developing a system capable of "one-shot" learning based on a computationally efficient and non-iterative algorithm for online training has the potential of significantly improving HMIs based on EMG signals.

Another important branch of research involves EEG signal processing for neurological applications. The advances in cognitive neuroscience have been giving us the possibility to interface directly with the human brain. Moreover, neurological disorders affect nearly one billion people, a considerable percentage of the world population [40]. The estimated economic costs were more than 2 trillions of USD in 2010 [41], with a high social impact. Despite the fact that effective treatments are available, a significant part of the population is untreated, because

of inadequate healthcare infrastructure, lack of trained staff, effective diagnostics and screening tools. Among diagnostic and screening techniques, Electroencephalography (EEG) analysis and instrumentation is an established standard, since it directly records the electrical field generated by neural activity with a set of electrodes distributed on the head surface (scalp) [42]. Thanks to its effectiveness, non-invasiveness, low cost and portability, EEG is one of the most used techniques for investigating brain function and pathology, both in clinical settings and scientific research [43] [44] [45].

One effective use of the EEG signals is to analyze brain responses to specific stimuli. The most popular method to measure the EEG response to a stimulus is to average the EEG signal across several stimulus presentations (Event-Related Potential, ERP [46]). Since the neural activity unrelated to the stimulus typically fluctuates within the same time scales of the stimulus related activity, a high number of stimulus presentations is needed to average it out and extract the stimulus-related response. An alternative technique, frequency-tagging (FT), has been developed to reliably measure stimulus-related EEG responses in a much shorter time. This technique exploits the property of the brain activity to respond to a visual or auditory stimulus presented periodically at a specific (i.e. "tag") temporal frequency by resonating at the same frequency during the stimulation period [47, 48]. This effect is manifested in the EEG recordings by a sharp peak in the power spectrum of the signal at that specific tag frequency. Since the EEG ongoing activity is broad-band in frequency, the stimulus-related response in the frequency domain is very easily discriminated from the stimulus-unrelated activity, yielding a much higher SNR than the one obtained with ERPs. Moreover, since most EEG artifacts (eye movements, blinks) are also broad-band in frequency, FT is more robust than ERP to artifacts and requires a lighter artifact rejection procedure.

Thanks to the short time needed to have a reliable response, FT has always been used in clinical settings to test the integrity of sensory areas [42] in the visual domain (classically defined Steady-State Visually Evoked Potentials - SSVEP [48]) and in the auditory domain (classically defined auditory steady-state responses - ASSR [47]), by presenting simple visual and auditory stimuli at relatively high frequencies (10 to 40 Hz), since sensory systems are most responsive at those frequencies. Since the amplitude of both ongoing EEG activity and eye-movement-related artifacts are relatively low in this frequency range, fast, automatic techniques have been developed to rapidly extract the frequency responses, in particular in the field of SSVEP-based BCI systems [49].

Most recently, the use of FT has been extended to investigate the neural responses related to higher-level perceptual or cognitive functions, such as attention [50], speech [51] or face [52] recognition. Since such functions require long neural processing, stimulation frequencies in a low-frequency range (0.5-6Hz, hereafter referred to as "low-frequency") have to be used. It has been shown that FT is still effective at those frequencies [51]. Because of their performance

in obtaining a stimulus-specific neural response in a short time, very recent FT designs based on stimulations in the low-frequency range have been successfully used as a tool for investigating the neural basis of cognitive development in very young children [53], [54]. Given these positive results, FT is a promising tool for testing brain function in clinical settings and/or with vulnerable populations as newborns or aged people.

However, for FT designs based on the low-frequency range, EEG ongoing fluctuations and artifacts are much more relevant than in the typical frequency range of SSVEP (>6Hz). Therefore a significant human intervention is needed to clean the data from artifacts and extract the response. Typically, the EEG traces are acquired and processed off-line on bench-top platforms, since most of the techniques to analyze brainwaves requires heavy computational processing and visual inspection from technicians or medical staff. This procedure implies non-negligible cost and time for an accurate analysis, due to the need for data transfer, off-line visualization, manual inspection and tagging. For instance, artifacts identification and removal require a combination of the visual evaluation of the EEG trace and of algorithmic techniques such as Independent Component Analysis (ICA), digital filtering, interpolations and averaging. Automating these analyses for FT stimulation in the low-frequency range would dramatically improve research and diagnosis, enabling the design of extensive screening systems for many neural disorders. Luckily, we are witnessing the massive technological trend of embedded wearable applications, that are quickly becoming pervasive [55], led by the constant growth of the health-care market and by the boost of digital technologies integration [3]. This trend paves the way for designing embedded, energy-efficient systems for biosignal processing based on advanced algorithmic techniques [20, 56, 57].

Another effective application using the EEG signals in BMI is represented by the detection of seizures in epilepsy. Among the neural diseases, epilepsy is characterized by recurrent seizures caused by abnormal neuronal electrical activity, which can lead to convulsions and loss of consciousness. Over the past few decades, drug delivery and brain surgery were largely used in treating epileptic seizures even though they present several drawbacks, like drug toxicity and risk connected to head surgery. Furthermore, there are at least 25% of epileptic subjects that present resistance to drugs or with surgically intractable seizures. Neuromodulation [58] is a brain stimulation technique based on the injection of small currents directly on the neural tissues. It has been demonstrated that neuromodulation has significant benefits in treating epilepsy while it does not present collateral effects [59]. Former neuromodulation devices were designed to give a continuous constant stimulation to the brain tissues, but they lack battery lifetime and efficient delivery of the treatment. Nowadays, to optimize the stimulation and enhance the battery life of the neuromodulators, closed-loop real-time systems are gaining ground [12]. A seizure can be identified from the EEG trace as an unexpected change in the amplitude and the

frequency of the neural signal; hence, the need to develop a responsive closed-loop neuromodulation system, which is able to detect seizures in a fully-automatic fashion, enabling a direct electrical feedback only when required.

Neuromodulation systems typically implement algorithms that analyze the EEG signal to detect changes representing a seizure activity. While the trend in research goes toward the design of dense multi-channel systems [60–62] with large and dense arrays of sensors (i.e., up to 128 electrodes) to allow a fine-grain coverage of the brain surface and target wider areas, current wearable and implantable solutions for seizure detection are only able to manage a few electrodes with a latency of 500 ms due to their limited computing power [9, 63]. The most common deeply-embedded systems for seizure detection are based on machine learning that can achieve high accuracy with a relatively small computational effort for a limited number of electrodes. Most of these systems are based on fixed-function ASIC designs, implementing feature extraction and pattern recognition algorithms for classification [64, 65]. The main issue with machine learning approaches such as SVM is that the computational complexity significantly increases with the number of channels, making it challenging to implement these algorithms in deeply-embedded systems.

From the algorithmic point of view, this issue has been addressed by applying dimensionality reduction algorithms, such as PCA and CS at the beginning of the processing chain. Although PCA approach has been exploited in several works elaborating the data offline [61], embedded solutions working with a number of electrodes greater than 18 have not been presented yet. Since the computational requirements for these algorithms are challenging, and the complexity scales up with the number of sensors, the design of a scalable digital architecture must target energy efficiency for a wide range of workloads. To drastically reduce the complexity of the preprocessing, a promising approach is to leverage the Compressed Sensing (CS) techniques. For instance, in [66], the authors implemented a seizure detection algorithm on a low-power domain-specific many-core platform. As opposed to multi-channel approaches based on traditional dimensionality reduction algorithms[5], in [66] compressed sensing reduced the computational complexity but with poor classification accuracy. On the other hand, it can be demonstrated that coupling preprocessing based on compressed sensing with powerful feature extraction and classification techniques allows achieving classification performance results similar to traditional approaches like PCA coupled with lightweight execution typical of CS approaches.

### 2.2 Target Architectures

Currently, the majority of the embedded devices able to operate in ultra-low power modes, last several years using a small battery, elaborating specific low complexity tasks and leaving the heavy computation to external devices. The aim of these devices is to consume the least

possible to the detriment of high performance. In fact, they are capable to operate at very low range frequencies (from a few tens of kHz, up to a few MHz), sometimes at sub-threshold voltages. Nowadays, a new trend is changing the way in which the raw signals acquired by the sensors are elaborated. Instead of transmitting the data to an external device or the cloud, the data are elaborated close to the sensor, leaving the data transfer only for highly compressed and informative data such as classes, trigger events or alarms. This approach paves the way to new challenges based on the development of heavily optimize algorithms, remaining in the mW-range power envelope for always-on battery-powered embedded devices.

Several solutions have been proposed in the last years to increase the performance requirements for these devices. One solution has the aim of increasing the operative range of low power processors to satisfy higher computational complexity, maintaining a reasonable efficiency. The problem occurs when the constraints of the application (i.e. latency) are too tight and the system is forced to operate out of the sub/near-threshold operative voltages, leading to a drop in energy efficiency. Another solution implies the use of specialized hardware to accelerate the computation, leaving the general-purpose processor for other tasks. Recently, a different solution is becoming popular and derives from parallel near-threshold computing. With this solution, it is possible to exploit the benefit of the near-threshold computing, maintaining high-performance thanks to the multi-core execution and the flexibility leveraging software programmable processors.

Typically, the hardware requirements for the processing of biosignals in biomedical applications depend on the complexity of the algorithms, the scope of the embedded device (i.e. implantable or wearable) and the application itself. First, to start the processing we need to collect inputs from the human body. To ensure this, the architecture we are targeting should be able to support an Analog Front End for the acquisition of multiple channels. As an example, a good choice is the ADS1298 from TI, the de-facto standard used in biopotential acquisition platforms. It presents a very favorable trade-off between performance and power consumption since its 3 V single supply does not require step-up DC/DC conversion of the battery voltage without significantly affecting noise performance.

The size of memories is another important aspect we should take into account. For some ExG applications, we need to store a huge quantity of data before starting the final elaboration (i.e. coefficients, weights, etc.) or simply the input vector. Furthermore, we may need to store the outputs for the next iteration (if required) at the end of the elaboration. Usually, embedded devices feature a small size memory directly connected to the processor (to the cluster in the case of multi-core architectures), and another external memory. A useful component that should be featured by the architecture is the DMA to handle the data transfers between memories in a very efficient way.

After ensuring an efficient processing unit feed, we should think about how to represent this information and elaborate them accordingly. It can happen that the application does not, or just in part, require floating-point arithmetic operations that are double-precision operations and, thus, more complex in terms of computation. In this case, we can decide if it is convenient to feature an FPU, leading to larger energy consumption, or to simulate these floating-point operations in software, but increasing the computation. Sometimes, the best solution is to convert the floating-point implementation into fixed-point. This is not always possible and it has been demonstrated that, in a complete application that includes several complex kernels, a hybrid approach (to switch from floating-point to fixed-point depending on the kernel) can be more effective[19]. Some architectures feature dedicated hardware to compute basic operations that can be used to dramatically optimize the execution of the code, such as MAC instructions, popcounters, SIMD instructions, etc. For all these considerations, we should carefully choose the target architecture, based on the specific requirements of the application we are working on.

#### 2.2.1 ARM Cortex M4

The ARM Cortex M4 processor, designed for efficient DSP and energy efficiency, is the most commonly used commercial MCU for embedded systems. The processor is based on Harvard architecture with three-pipeline stage and branch speculation, implementing 32-bit RISC ISA. It also includes the entire 16-bit  $Thumb^{\$} - 1$  and 16/32-bit  $Thumb^{\$} - 2$  instruction sets. It features an FPU that can be activated for fast floating-point operations. The ARM Cortex M4 MCU works at an operating frequency of 168 MHz and 1.85 V. Implemented in a 90nm technology with low power processing of 33 uW/MHz, it addresses the challenge of maintaining low dynamic power constraints. This low power consumption leads to a longer battery lifetime, which is critical in embedded devices for a wide range of applications.

When operating with critical tasks and interrupt routines, a known number of cycles manages these requests, enhancing determinism. It features non-maskable interrupts(NMI) and up to 240 physical interrupts, with different priority levels (from 8 to 256). It supports sleep modes to reduce energy waste, with up to 240 wake-up interrupts and optional retention mode, integrating Wait For Interrupt (WFI) and Wait For Event (WFE) instructions and Sleep On Exit capability. It includes extended single-cycle 16/32-bit multiply-accumulate (MAC), dual 16-bit MAC instructions, optimized 8/16-bit SIMD arithmetic and saturating arithmetic instructions. For debug, it features a JTAG and Serial-Wire Debug (SWD) ports, with up to eight breakpoints and four watchpoints. The processor also has a Memory Protection Unit (MPU), up to 8 sub-regions. This design is used to protect the memory content, preventing access to privileged application data. Different buses interconnect the components of the SoC, providing data transfer management. It features a DMA for efficient management of the data transfers (SRAM, FLASH memory), avoiding occupancy of the processor.

**Figure 2.1:** A general view of the Parallel Ultra-Low Power (PULP) architecture (**a**) and the layout of the PULPv3 chip used for performance and power characterization (**b**).

### 2.2.2 PULP platform

PULP platform is an open-source project born by the collaboration between the University of Bologna and the Eth Zurich. It is a many-core platform (Figure 2.2a) that can be based on OpenRISC or RISC-V Instruction Set Architecture (ISA). It is able to operate in a large range of operative voltages and frequencies, obtaining a high level of energy efficiency for different kinds of applications even with huge computational complexity (IoT, biomedical, image processing, etc). Several versions of the PULP architecture are available and they differ from the technology (CMOS, FD-SOI), form factor (65, 40, 28nm), number of processing units, and memory size.

The PULP fabric is integrated into a SoC that can feature an off-cluster (L2) memory; peripheral accesses are managed by a low power DMA (Direct Memory Access) tightly coupled to the TCDM featuring an ultra-low-latency programming interface (just 10 cycles for transfer configuration), up to 16 outstanding transactions and multiple physical channels [67]. At the SoC level, several peripherals are available including two SPI interfaces (one master and one slave), I2C, I2S, a camera interface, GPIOs, a boot-up ROM and a JTAG interface for debugging purposes. The SPI interfaces can be configured in single mode or quad mode, useful to interface high-bandwidth components such as off-chip SRAMs or FLASH memories. The SPI slave can be configured as a master, and a set of enable signals placed on both SPI interfaces allow the SoC to interface to up to four slave peripherals, such as eight-channel ADC suitable for EEG signal acquisition. To reduce the overall number of pads and make a low-cost wire bonding packaging of the SoC suitable for pervasive applications, the IO interfaces are multiplexed. The SoC supports up to four configurations of the IO matrix, programmed through a memorymapped interface accessible by the cores. Thanks to the presented peripheral architecture, the SoC is then capable of operating either in stand-alone mode or as an accelerator of a standard host microcontroller (e.g., an ARM Cortex M processor), which provides programming legacy and offloads performance-critical parallel tasks to PULP [68]. To operate at the best energy

point across a wide range of workloads, the PULP cluster and the rest of the SoC are in different power and clock domains. Fine-grained tuning of the cluster and SoC frequencies is managed by two FLLs (Frequency-Locked Loops).

In the exploration of the applications presented in this dissertation, different architectures related to the PULP platform were considered. The selection of the architecture was dictated by the requirements of the applications such as memory usage, the computational complexity of the algorithm, information representation (i.e. floating-point, fixed-point).

#### 2.2.2.1 PulpV3 Architecture