### UNIVERSITA' DEGLI STUDI DI BOLOGNA

### FACOLTA' DI INGEGNERIA

### SCUOLA DI DOTTORATO IN SCIENZE ED INGEGNERIA DELL'INFORMAZIONE

### DOTTORATO IN INGEGNERIA ELETTRONICA, INFORMATICA E DELLE TELECOMUNICAZIONI

XX° CICLO

## MODELS AND METHODS FOR POWER MONOLITHIC MICROWAVE INTEGRATED CIRCUITS

Tutore: Prof. FABIO FILICORI

Candidato: DAVIDE RESCA

Co-tutore: Prof. ALBERTO SANTARELLI

Coordinatore del corso: Prof. PAOLO BASSI

ANNO ACCADEMICO 2007-2008

Settore Scientifico Disciplinare: ING-INF/01

# ACKNOWLEDGMENTS

This thesis is the result of three and half years of work whereby I have been accompanied and supported by many people. It is a pleasant aspect that I have now the opportunity to express my gratitude for all of them. Any merit in this thesis is in large measure due to them.

First and foremost, I gladly acknowledge my debt to my tutor Prof. Fabio Filicori, my co-tutor Prof. Alberto Santarelli, Prof. Giorgio Vannini and Doctor Pier Andrea Traverso, that taught me all I know about electron device modelling techniques. Without their constant friendship, encouragement and advice over many years this work would ever have been completed. Furthermore I would like to thank Prof. Vito Monaco that, together with Prof. Giorgio Vannini, first introduced me in the Laboratory of Electronics for Telecommunications of the University of Bologna, giving me the opportunity of participating as a PhD Student to its research activities.

Another important person I would like to thank is Prof. Antonio Raffo whom I could define my "spiritual instructor". During these years I have known Antonio as a sympathetic and principlecentered person. His overly enthusiasm and integral view on research and his mission for keeping me involved in these work, has made a deep impression on me. I owe him lots of gratitude for having me shown this way of research. He could not even realize how much I have learned from him.

Dr. Rafael Cignani belongs to the special persons I've known during these years. He always kept an eye on the progress of my work and always was available when I needed his advises.

Antonio and Rafael besides of being excellent supervisors, they are as close as relative and a good friends to me.

My colleagues of the Laboratory of Electronic for Telecommunications and of the Spin-Off MEC (Microwave Electronic for Communication) all gave me the feeling of being at home at work. Francesco Scappaviva, Julio Andres Lonac, Ilan Melczarsky, Massimo Pirazzini, Valeria Di Giacomo, Federico Fantini, Svevo Monaco, Valeria Vadalà, Antonio Musio, Sara D'Angelo, Corrado Florian, Rudi Paolo Paganelli, many thanks for being your colleague.

I feel a deep sense of gratitude for my father and mother who formed part of my vision and taught me, through simple words, the good things that really matter in life.

I am very grateful for all my friends of my little town for rendering me the sense and the value of brotherhood. I am glad to be one of them.

The last... The last is the most precious. I am very grateful for my girlfriend Valentina, for her love and patience during this period of my life. My knowledge and what you learn from me is all due to her.

# INTRODUCTION

Computer aided design of Monolithic Microwave Integrated Circuits (MMICs) depends critically on active device models that are accurate, computationally efficient, and easily extracted from measurements or device simulators.

Empirical models of active electron devices, which are based on actual device measurements, do not provide a detailed description of the electron device physics. However they are numerically efficient and quite accurate. These characteristics make them very suitable for MMIC design in the framework of commercially available CAD tools.

In the empirical model formulation it is very important to separate linear memory effects (parasitic effects) from the nonlinear effects (intrinsic effects). Thus an empirical active device model is generally described by an extrinsic linear part which accounts for the parasitic passive structures connecting the nonlinear intrinsic electron device to the external world.

An important task circuit designers deal with is evaluating the ultimate potential of a device for specific applications. In fact once the technology has been selected, the designer would choose the best device for the particular application and the best device for the different blocks composing the overall MMIC. Thus in order to accurately reproducing the behaviour of different-in-size devices, good scalability properties of the model are necessarily required.

Another important aspect of empirical modelling of electron devices is the mathematical (or equivalent circuit) description of the nonlinearities inherently associated with the intrinsic device. Once the model has been defined, the proper measurements for the characterization of the device are performed in order to identify the model. Hence, the correct measurement of the device nonlinear characteristics (in the device characterization phase) and their reconstruction (in the identification or even simulation phase) are two of the more important aspects of empirical modelling.

This thesis presents an original contribution to nonlinear electron device empirical modelling treating the issues of model scalability and reconstruction of the device nonlinear characteristics.

The scalability of an empirical model strictly depends on the scalability of the linear extrinsic parasitic network, which should possibly maintain the link between technological process parameters and the corresponding device electrical response.

5

Since lumped parasitic networks, together with simple linear scaling rules, cannot provide accurate scalable models, either complicate technology-dependent scaling rules or computationally inefficient distributed models are available in literature.

This thesis shows how the above mentioned problems can be avoided through the use of commercially available electromagnetic (EM) simulators. They enable the actual device geometry and material stratification, as well as losses in the dielectrics and electrodes, to be taken into account for any given device structure and size, providing an accurate description of the parasitic effects which occur in the device passive structure. It is shown how the electron device behaviour can be described as an equivalent two-port intrinsic nonlinear block connected to a linear distributed four-port passive parasitic network, which is identified by means of the EM simulation of the device layout, allowing for better frequency extrapolation and scalability properties than conventional empirical models.

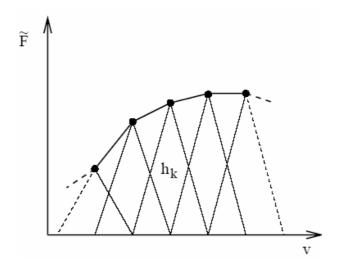

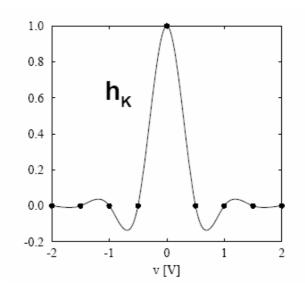

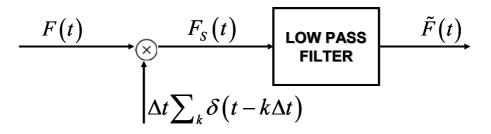

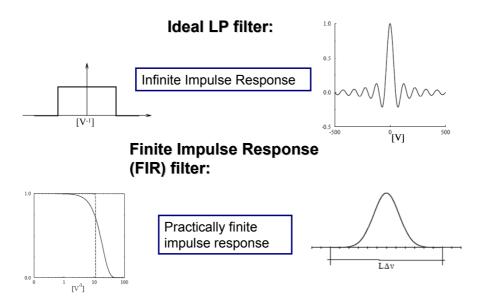

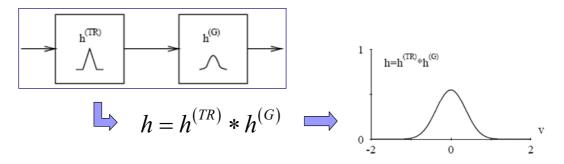

Concerning the issue of the reconstruction of the nonlinear electron device characteristics, a data approximation algorithm has been developed for the exploitation in the framework of empirical table look-up nonlinear models. Such an approach is based on the strong analogy between time-domain signal reconstruction from a set of samples and the continuous approximation of device nonlinear characteristics on the basis of a finite grid of measurements. According to this criterion, nonlinear empirical device modelling can be carried out by using, in the sampled voltage domain, typical methods of the time-domain sampling theory.

The research activity discussed in the thesis was partially performed in the context of the Network of Excellence TARGET (Top Amplifier Research Groups in a European Team) supported by the European Union.

A brief description of the contents of each chapter is provided in the following.

Chapter 1 provides an overview of different empirical models of high frequency electron devices which have been proposed in the literature. First, the most important phenomena related to the intrinsic device, such as non-quasi-static high frequency phenomena and low frequency dispersive phenomena, are discussed. Then, the most important conventional techniques for the identification of the linear extrinsic parasitic network are presented.

Chapter 2 deals with the model scalability. An example shows the poor accuracy obtained through conventional scaling rules applied to conventional empirical models. Then, more complicate extraction procedures, involving multiple measurements carried out on different devices, are discussed. Furthermore the definition of distributed empirical models is given, together with a discussion about their capability of reproducing different device behaviour at higher frequencies.

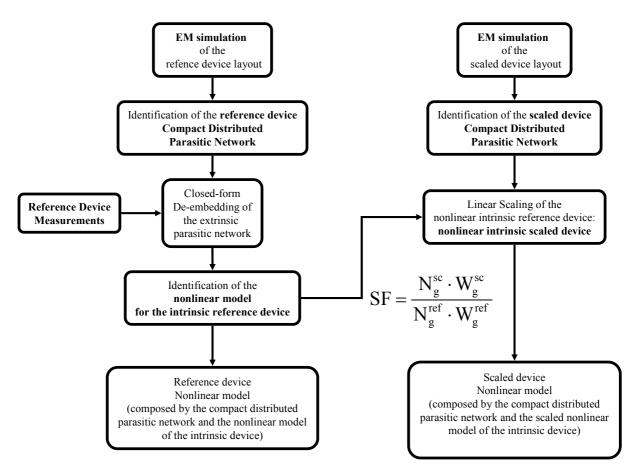

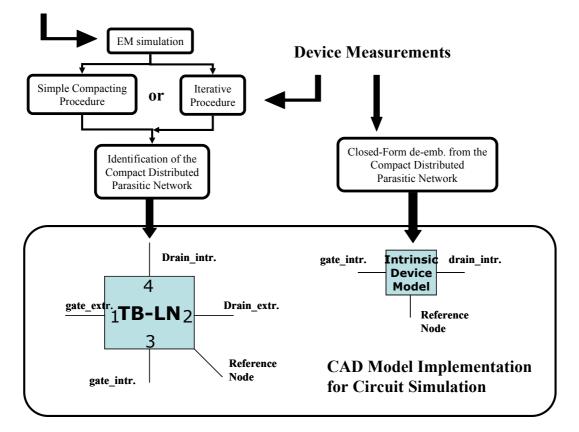

Chapter 3 represents the core of the thesis. The use of the EM simulation for the identification of the linear extrinsic parasitic network is discussed. Starting from a fully distributed EM-based linear model, two different procedures for the identification of a compact distributed parasitic network are presented. Such a compact distributed parasitic network allows for the definition of an empirical model described as an equivalent two-port intrinsic nonlinear block connected to the linear distributed compact parasitic network. This provides a nonlinear model which is as numerically efficient as conventional empirical models, maintaining also the frequency extrapolation and scalability properties of fully distributed models.

Chapter 4 provides a wide experimental validation of the compact distributed nonlinear model showing both its frequency extrapolation capability and its scaling properties. Such an experimental validation carried out on different technologies shows also the technology-independence of the EM-based approach.

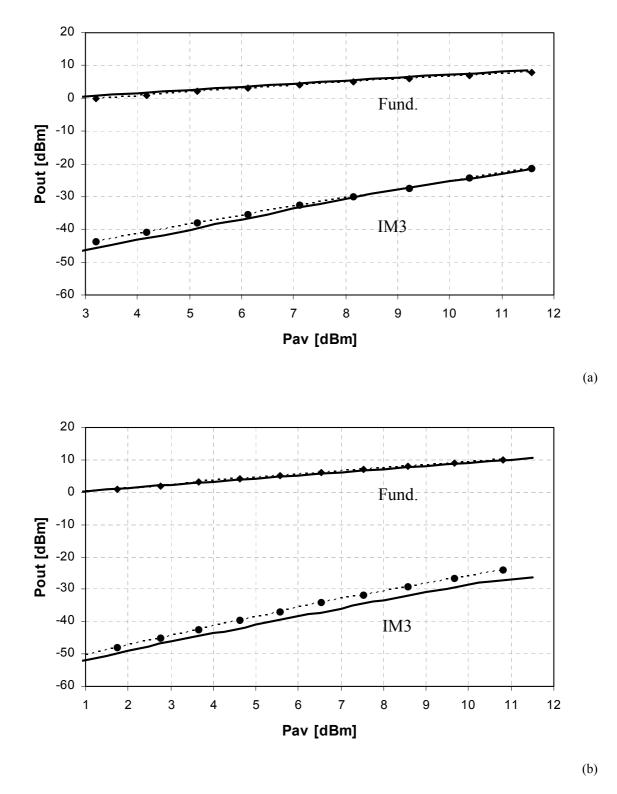

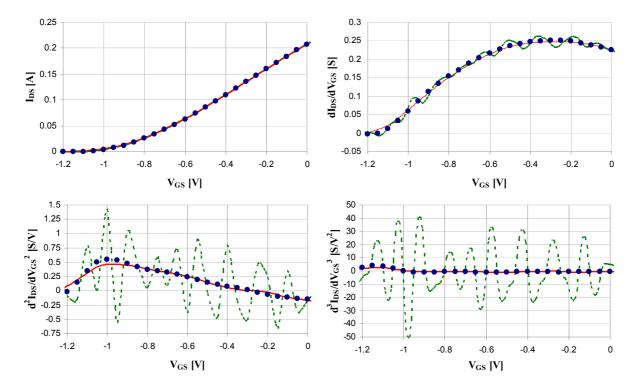

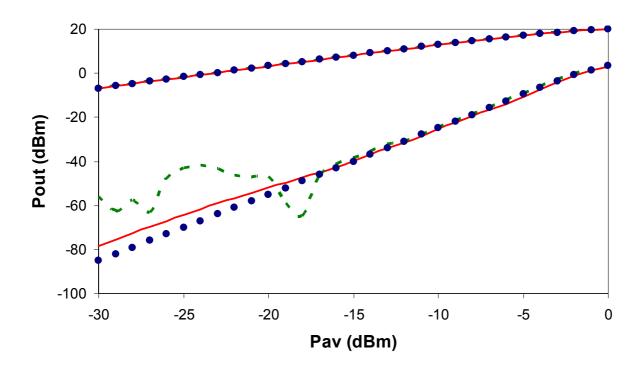

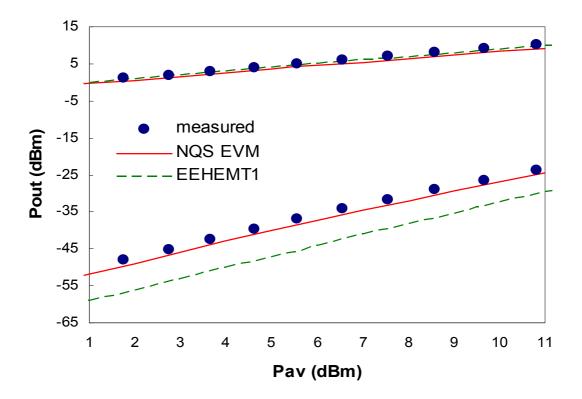

Chapter 5 deals with the developed data approximation formula. Experimental validation is provided through the differentiability evaluation of the proposed approximation formula, in comparison with conventional cubic-spline interpolation, and through the IMD prediction of a GaAs-based PHEMT.

# **CHAPTER 1**

# **REVIEW OF EMPIRICAL ELECTRON DEVICE MODELLING**

#### **1.1 Introduction to empirical modelling of Electron Devices.**

The design of MMICs depends critically on device models that are accurate, computationally efficient, and easily extracted from measurements or device simulators.

Numerical-physical models are derived by fundamental equations describing the physic of charge transport in electron devices. They provide a direct link between technological process parameters, such as materials, geometry, doping profile, etc., and the device electrical response, but the required large amount of computation time precludes their use in circuit simulators for design purposes, making them only suitable for device design and analysis.

Empirical models, based on electron device measurements, may be either equivalent circuit (EC) models or black-box models. Equivalent circuit models use lumped circuit elements to describe the measured characteristics, while black-box models are based on integral/differential predictive equations and/or look-up tables to reproduce the observed device behaviour. Empirical models, despite they don't provide a detailed description of the electron device physics, are numerically efficient and quite accurate. These characteristics make them very suitable for MMIC design in the framework of commercially available CAD tools.

MMICs usually operate with the active electron devices showing some (maybe even gross) nonlinear behaviour. In fact Large-Signal RF operation of the electron devices involves nonlinear dynamic behaviour. The concurrent presence of memory effects and nonlinearity turns into high complexity in the model formulation. In compact empirical models the memory effects are

described by linear operators, i.e. time derivatives, integrals, delays, etc., while the nonlinearity is described by nonlinear algebraic (i.e. memoryless) functions which can be analytical, Look-Up-Table-based, Artificial-Neural-Network-based.

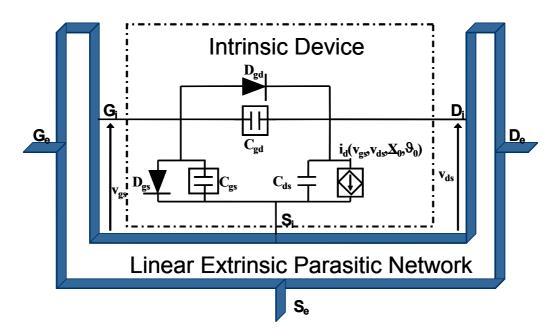

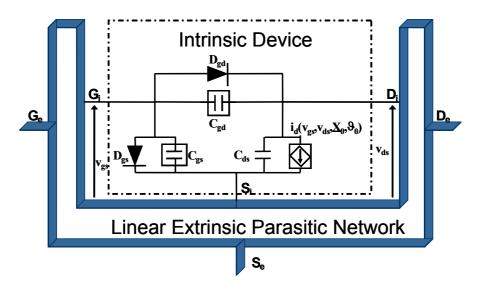

In order to obtain a good model formulation it is very important to separate linear memory effects (parasitic effects) from the nonlinear effects (intrinsic effects). Thus an empirical FET model is generally described by an extrinsic part which accounts for the parasitic passive structures connecting the intrinsic electron device to the external world. Typically, the parasitic network is supposed linear (i.e. *bias independent*) and it is usually modelled through different topologies according to specific technology/packaging choices (lumped or distributed). The intrinsic device, describing the basic physics of operation of the electron device, is nonlinear (i.e. *bias dependent*) with "short" memory at typical operating frequencies.

In empirical modelling, the main nonlinear functions describing the intrinsic device behaviour are current-voltage and charge-voltage relationships. They may be approximated by means of analytical functions depending on a restricted number of parameters or stored into look-up table and implemented into CAD with Data Access Components.

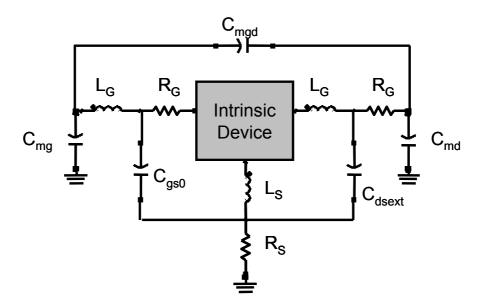

Fig.1.1 shows the general schematic representation of an empirical electron device model.

Fig. 1.1 Empirical electron device model. The model is composed by a linear extrinsic parasitic network connecting the nonlinear intrinsic device to the external world.

Since the late '70, different empirical models of high frequency electron devices have been proposed and accepted by the scientific community, according to different parasitic network topology and/or different intrinsic device formulations. In fact the empirical model properties, such

as accuracy, computational efficiency, scalability, easiness of identification, etc., strongly depend on both parasitic network and intrinsic device description. An overview of the most important intrinsic device and extrinsic parasitic network modelling approaches, which can be found in literature, is the main aim of this chapter.

#### **1.2 Empirical Modelling of the Intrinsic Device.**

#### 1.2.1 Charge Controlled Quasi-Static Formulation

The intrinsic device must account for the conductive plus displacement current contributions which flow in the device channel depending on the selected quiescent condition of the device. As far as relatively low frequencies of operation are considered for the device, the intrinsic device behaviour can be described through a charge-controlled formulation:

$$\mathbf{i}(t) = \mathbf{\Phi} \left\{ \mathbf{q}(t), \mathbf{v}(t) \right\} + \frac{d\mathbf{q}(t)}{dt}$$

$$\mathbf{q}(t) = \mathbf{\Psi} \left\{ \mathbf{v}(t) \right\}$$

(1.1)

where

$$\mathbf{i} = \begin{vmatrix} i_1 \\ i_2 \end{vmatrix}, \mathbf{v} = \begin{vmatrix} v_1 \\ v_2 \end{vmatrix}, \mathbf{q} = \begin{vmatrix} q_1 \\ q_2 \end{vmatrix}$$

are the vectors of the currents, voltages and charges at the two port of the device respectively.

The equivalent charges completely define the intrinsic device state (state variables) and they only depend on the instantaneous values of the intrinsic transistor voltages. Both numerical device simulations and experimental validation show that the simple formulation (1.1) correctly models the intrinsic device behaviour up to moderately high frequencies.

Since FETs are often controlled by the port voltages, substituting the second of (1.1) in the first of (1.1) the charge-controlled equations describing the intrinsic behaviour can be put in a voltage-controlled form (1.2).

$$\mathbf{i}(t) = \mathbf{F}\left\{\mathbf{v}(t)\right\} + \mathbf{C}\left\{\mathbf{v}(t)\right\} \cdot \frac{d\mathbf{v}(t)}{dt}$$

(1.2)

where

$$\mathbf{F}\left\{\mathbf{v}(t)\right\} \doteq \mathbf{\Phi}\left\{ \mathbf{\Psi}\left\{\mathbf{v}(t)\right\}, \mathbf{v}(t) \right\}$$

$$\mathbf{C}\left\{\mathbf{v}(t)\right\} \doteq \frac{d\mathbf{\Psi}\left\{\mathbf{v}(t)\right\}}{d\mathbf{v}}$$

The current-voltage relationship in (1.2) is nonlinear with memory having an infinitely small duration

$$\frac{d\mathbf{v}}{dt} = \lim_{\tau \to 0} \frac{\mathbf{v}(t) - \mathbf{v}(t-\tau)}{\tau},$$

leading to a quasi-static (QS) model definition.

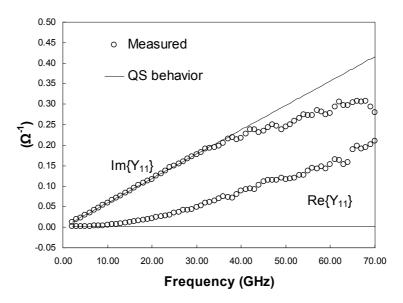

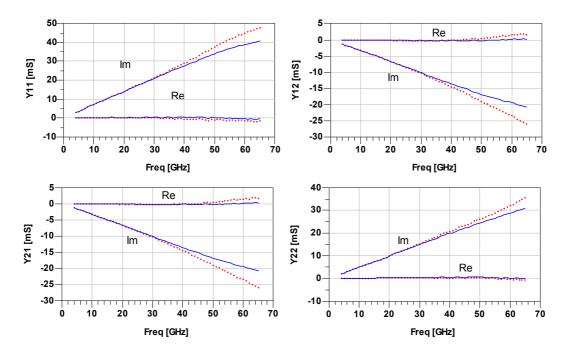

The hypothesis of vanishingly small duration of memory effects is not acceptable for device operation at higher frequencies. In fact the intrinsic small-signal FET admittance parameters, especially  $Y_{11}$  and  $Y_{21}$ , exhibit strong deviations from the quasi-static behaviour as shown in Fig.1.2.

Fig. 1.2 Deviation from the quasi static behaviour of the measured intrinsic Y11 for a commercial FET.

#### 1.2.2 Non-Quasi-Static Effects

The intrinsic device Non-Quasi-Static (NQS) effects can be theoretically explained by the fact that the charges depend on voltage values at both actual and past time instants within a finite memory time  $T_M$ . By considering such a dependence on the past values of the applied voltages, the charges of (1.1) becomes NQS as expressed in (1.3).

$$\mathbf{i}(t) = \mathbf{\Phi} \left\{ \mathbf{q}^{NQS}(t), \mathbf{v}(t) \right\} + \frac{d\mathbf{q}^{NQS}(t)}{dt}$$

$$\mathbf{q}^{NQS}(t) = \mathbf{\Psi}^{NQS} \left| \mathbf{v}(t-\tau) \right|_{\tau=0}^{T_M}$$

(1.3)

Many models adopt a charge perturbation approach  $\mathbf{q}^{NQS}(t) \doteq \mathbf{q}^{QS}(t) + \Delta \mathbf{q}(t)$ , that is the NQS charges are obtained from the QS charges plus a charge perturbation  $\Delta \mathbf{q}(t)$ . They also assume that the NQS phenomena affect the displacement current only, that is  $\mathbf{i}(t) = \mathbf{F} \{\mathbf{v}(t)\} + d\mathbf{q}^{NQS}(t)/dt$ .

In 1993 Daniels *et al.* [1], adopted a charged controlled formulation defining the following NQS model for FET devices:

$$\mathbf{i}(t) = \mathbf{i}_{c} \left\{ \mathbf{v}(t) \right\} + \frac{d\mathbf{q}^{NQS}(t)}{dt}$$

$$\mathbf{q}^{NQS}(t) = \mathbf{q}^{QS} \left\{ \mathbf{v}(t) \right\} - \mathbf{\tau} \left\{ \mathbf{v}(t) \right\} \cdot \frac{d\mathbf{q}^{NQS}(t)}{dt}$$

(1.4)

where  $\mathbf{i}_{c}(\mathbf{v})$  are the quasi-static conductive currents,  $\mathbf{q}^{QS}$  are the quasi-static charges and  $\tau(\mathbf{v})$  is a voltage depending charge redistribution time. Considering the  $\tau$  parameter voltage independent, it leads to the NQS model proposed by M. Fernandez-Barciela *et al.* in 2000 [2].

In 2006 A.Santarelli *et al.* [3] proposed a NQS model based on the description of the NQS effects as a charges perturbation. In fact the functional describing the NQS charges, the second of (1.3), is defined as follows:

$$\mathbf{q}^{NQS}(t) = \mathbf{\Psi}^{NQS} \left| \mathbf{v}(t-\tau) \right|_{\tau=0}^{T_M} \doteq \mathbf{q}^{QS}(t) + \Delta \mathbf{q}(t) \,. \tag{1.4}$$

The inverse function of the  $\Psi$  functional leads to the definition of the equivalent voltages:

$$\mathbf{v}^{\mathcal{QS}}(t) \doteq \mathbf{\Psi}^{-1} \left\{ \mathbf{q}^{\mathcal{QS}}(t) + \Delta \mathbf{q}(t) \right\} \doteq \mathbf{v}(t) + \Delta \mathbf{v}(t)$$

(1.5)

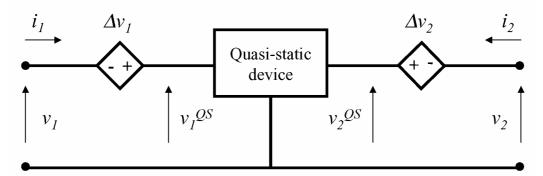

where the charge perturbations  $\Delta \mathbf{q}(t)$  are modelled by means of suitable defined voltage deviations  $\Delta \mathbf{v}(t)$ . Thus Nonlinear device is still described by a quasi-static model, but controlled by equivalent instead of actual voltages, as shown in Fig.1.3.

Fig. 1.3 Non-Quasi-Static Equivalent Voltage model as proposed in [3]. The NQS effects are taken into account by means of suitable voltage perturbations applied to the QS voltages.

The NQS effects may be taken into account by means of linear Voltage-Controlled Voltage-Sources (VCVS):

$$\Delta \mathbf{v}(t) = \int_0^{T_M} \mathbf{a}(\tau) \cdot \left[ \mathbf{v}(t-\tau) - \mathbf{v}(t) \right] d\tau .$$

(1.6)

The effect of the voltage deviations vanishes when signal frequencies involved are in quasi-static range, that is when the actual and past voltage values coincide one another.

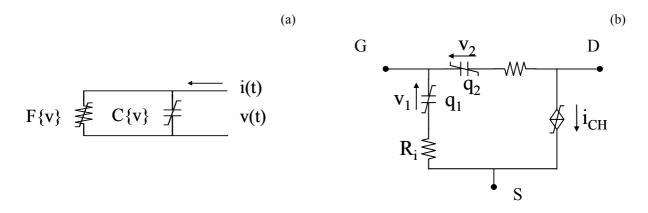

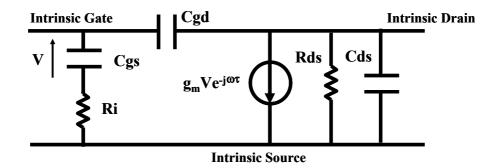

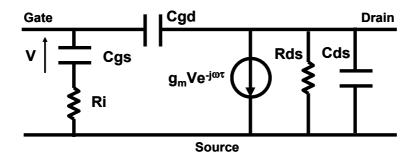

The charge-controlled-based formulation (1.2) is very suitable for the definition of equivalent circuit models. In fact the circuit-based interpretation of quasi-static model (1.2) is the parallel of nonlinear resistive and purely-capacitive elements, as shown in Fig.1.4.

Fig. 1.4 (a) Quasi-static charge-controlled equation equivalent circuit representation. (b) Equivalent circuit of a two ports intrinsic device model accounting for non-quasi-static effects.

As stated for example by W. R. Curtice [4] and I. Angelov *et al.* [5], added series resistive elements may partially account for NQS phenomena. Owing to series resistors the capacitor charges  $q_1$ ,  $q_2$ , the voltages  $v_1$ ,  $v_2$  and the controlled source  $i_{CH}$  of Fig.1.4 are also dependent on "past"

values of  $v_{GS}$ ,  $v_{DS}$  applied to the intrinsic device. This is a circuit way for taking into account "memory" effects due to the NQS phenomena. Delays can also be explicitly considered in the controlled current source [4], [5].

#### **1.2.3 Black-box empirical modelling of the intrinsic device**

In black-box empirical models the electron device is studied with a behavioural perspective: theoretical and mathematical tools such as state-space nonlinear equations or Volterra Series expansions are used to describe the electron device behaviour. This results in the loss of the insight view of the internal physics of the device, but it provides, at least in principle, technology independent approaches.

Fig. 1.5 Single-port intrinsic electron device described by the voltage controlled nonlinear dynamic functional (1.7).

Under the hypothesis of finite memory effects within the device and considering the single-port nonlinear electron device of Fig.1.5, the current can be expressed as a functional of the present and past voltage values in a "memory time" interval  $0 \le \tau \le T_M$ .

$$i(t) = \Psi \left[ \left[ \nu(t-\tau) \right] \right]_{\tau=0}^{T_M}$$

(1.7)

The most general modelling approach for systems characterized by nonlinear dynamic behaviour described by (1.7), is the Volterra Series expansion [6], which is based on a description of the nonlinear dynamic effects by means of multi-dimensional convolution integrals (1.8), which can be considered a generalization of the one-dimensional convolution integral for dynamic linear systems.

$$i(t) = \int_0^{T_M} h_1(\tau_1) v(t-\tau_1) d\tau_1 + \iint h_2(\tau_1, \tau_2) v(t-\tau_1) v(t-\tau_2) d\tau_1 d\tau_2 + \\ + \iiint h_3(\tau_1, \tau_2, \tau_3) v(t-\tau_1) v(t-\tau_2) v(t-\tau_3) d\tau_1 d\tau_2 d\tau_3 + \dots$$

(1.8)

The identification of the Volterra kernels  $h_1(\tau_1)$ ,  $h_2(\tau_1, \tau_2)$ ,  $h_3(\tau_1, \tau_2, \tau_3)$ ,... completely characterize the nonlinear dynamic system response.

The Volterra kernels identification is very difficult at microwave frequencies [7]: only few kernels can be identified and practically this description is well suited for the modelling of weak nonlinearities.

In 2003 Schreurs et al. [8] proposed a black-box modelling approach in which the nonlinear dynamic behaviour of the electron device is described by means of state-space-like equations:

$$\vec{\dot{X}}(t) = F_a\left(\vec{X}(t), \vec{V}(t)\right)$$

$$\vec{I}(t) = F_b\left(\vec{X}(t), \vec{V}(t)\right)$$

(1.9)

where, in order to describe a voltage controlled device, the inputs are the controlling voltages  $\vec{V}(t)$ , the outputs are the output currents  $\vec{I}(t)$  and  $\vec{X}(t)$  are the state variables of the device.

Considering a two-port device and rearranging (1.9), the space-state equations can be rewritten as

$$I_{1}(t) = f_{1}\left(V_{1}(t), V_{2}(t), \dot{V}_{1}(t), \dot{V}_{2}(t), \ddot{V}_{1}(t), \cdots, \dot{I}_{1}(t), \dot{I}_{2}(t), \ldots\right)$$

$$I_{2}(t) = f_{2}\left(V_{1}(t), V_{2}(t), \dot{V}_{1}(t), \dot{V}_{2}(t), \ddot{V}_{1}(t), \cdots, \dot{I}_{1}(t), \dot{I}_{2}(t), \ldots\right)$$

(1.10)

where the required order of derivative must be determined. The identification of the functions  $f_1$  and  $f_2$  are carried out through fitting of large signal experimental data at various bias and input power levels by means of ANN.

#### 1.2.4 Alternative Black-Box approach (The Modified Volterra Theory)

Considering a single-port electron device described by the functional (1.7), which holds under the hypothesis of finite duration of memory effects, after some algebraic manipulation the following equation can be written:

$$i(t) = \Psi \left| v(t-\tau) \right|_{\tau=0}^{T_M} = \Psi \left| v(t) + v(t-\tau) - v(t) \right|_{\tau=0}^{T_M},$$

(1.11)

that is

$$i(t) = \tilde{\Psi} \left| v(t), e(t, \tau) \right|_{\tau=0}^{T_M}$$

(1.12)

where the new functional  $\tilde{\Psi}$  explicitly depends on  $e(t,\tau) = v(t-\tau) - v(t)$ , the dynamic voltage deviation, which consider the difference between the past values of the controlling voltage, within the memory time of the device, and the present value of the controlling voltage.

If the Taylor expansion of  $v(t-\tau)$  at  $\tau = 0$  is considered, i.e.  $v(t-\tau) = v(t) - \dot{v} \cdot \tau + \ddot{v} \cdot \tau^2 - ...$ , the functional (12) can be rewritten as:

$$i(t) = \tilde{\Psi} \left| v(t), -\frac{dv}{dt}\tau + \frac{d^2v}{dt^2}\tau^2 - \dots \right|_{\tau=0}^{T_M} = f\left(v(t), \dot{v}(t), \ddot{v}(t), \dots\right)$$

(1.13)

which is analogous to the state-space description of the electron device.

The electron devices used for high frequency application show that their memory effects are also short with respect to their actual operating frequencies, that is  $f \ll 1/T_M$ . This basic feature of electron devices is justified both by experiment and by simulation and it is the so called *short duration of memory effects* phenomenon described by Filicori *et al.* in 1992 [9]. In that work it is also shown how the Volterra Series expansion can be rewritten as a function of the dynamic voltage deviations (Modified Volterra Series) and how under such an hypothesis the Volterra Series decrease their order.

Under the hypothesis of short duration of memory effects for an electron device described in a voltage controlled form, the voltage dynamic deviation in the functional (1.12) are small even with large voltage amplitudes which means that they are *small even at high nonlinear operations*.

This means that through the linearization of (1.12) with respect to  $e(t,\tau)$ , the modified Volterra Series expansion reduces its multi-dimensional order to the first order, without excessively increasing the linearization error [10]. This results in the following equation which describes the Nonlinear Integral Model (NIM) proposed in [9]:

$$i(t) = F[v(t)] + \int_{0}^{T_{M}} g[v(t),\tau] e(t,\tau) d\tau. \qquad (1.14)$$

In (1.14) the first term F[v(t)] represents the static behaviour of the electron device, while the second term represents a single-fold convolution integral between the small dynamic voltage deviations and the nonlinearly voltage-controlled impulse response  $g[v(t), \tau]$ . The NIM

formulation (1.14) is in analogy with the convolution which describes dynamic linear system, but is valid even in high nonlinear operating conditions.

This integral description of the high frequency nonlinear behaviour of an electron device is in analogy with the charge-controlled QS description of the intrinsic device also accounting for the high frequency NQS phenomena. In fact the Taylor expansion of  $e(t-\tau)$  at  $\tau = 0$ ,  $v(t-\tau)-v(t) = -\dot{v}\cdot\tau + \ddot{v}\cdot\tau^2 - ...$ , leads to the following modification of equation (1.14):

$$i(t) = F[v(t)] + \left(-\int_{0}^{T_{M}} g[v(t),\tau] \tau d\tau\right) \frac{dv}{dt} + \left(\int_{0}^{T_{M}} g[v(t),\tau] \tau^{2} d\tau\right) \frac{d^{2}v}{dt^{2}} + \dots = F[v(t)] + F_{1}[v(t)] \frac{dv}{dt} + F_{2}[v(t)] \frac{d^{2}v}{dt^{2}} + \dots$$

(1.15)

where

$$F_1[v] = -\int_0^{T_M} g[v,\tau] \cdot \tau \, d\tau = C[v]$$

$$(1.16)$$

$$F_{n}[v] = \frac{(-1)^{n}}{n!} \int_{0}^{T_{M}} g[v,\tau] \cdot \tau^{n} d\tau$$

(1.17)

the term defined by (1.16) accounts for the quasi-static effects, while the terms defined by (1.17) account for the non-quasi-static effects. Hence (1.15), (1.16) and (1.17) show that the NIM is a black-box model which account for high frequency NQS effects and it is equivalent to the charge-controlled-based models. In fact at relatively low frequencies this limit holds

$$\lim_{\omega T_{M} \to 0} \left\{ \int_{0}^{T_{M}} g \left[ v(t), \tau \right] e(t, \tau) \, d\tau \right\} = \mathbf{C} [\mathbf{v}] \frac{dv}{dt}$$

(1.18)

and the NIM is analogous to a conventional QS model, while at higher frequencies, the higher order terms (1.17) introduce their effects, accounting for non-quasi-static effects.

The model given by eq. (1.14) can be implemented with some suitable approximations in HBbased circuit simulators and is suitable for identification on the basis of conventional static and small-signal measurements. However, in order to make the model implementation and its empirical characterisation easier, the integral convolution in eq. (1.14) may be approximated by a discrete

convolution, where the memory time  $T_M$  is divided into  $N_D$  elementary time slots (that is,  $T_M = N_D \cdot \Delta \tau$ ). In particular, the discretized model is expressed as

$$i(t) \cong F_{DC}\left[v(t)\right] + \sum_{p=1}^{N_D} g_p\left[v(t)\right] \cdot \left[v(t - p\Delta\tau) - v(t)\right]$$

(1.19)

where the dynamic current contribution, given by the summation term in (1.19), represents the nonlinear discrete convolution (NDC) model [10], which is fully identified by the  $N_D$  real functions  $g_p[v(t)]$ , identified through a linear least square fitting of the model to the measured DC and Small-Signal multi-bias device characteristics.

#### <u>1.2.5 Modelling of the Low-Frequency Dispersive Phenomena</u>

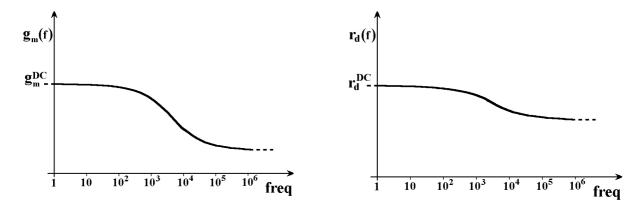

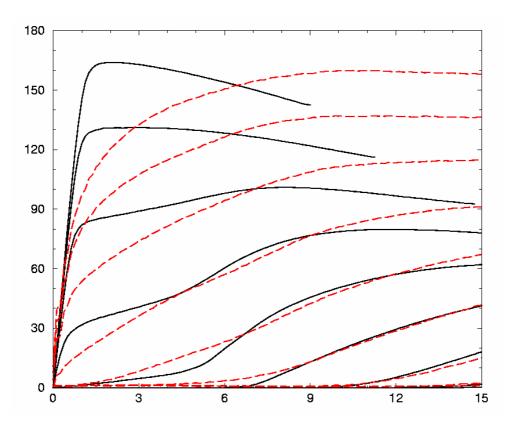

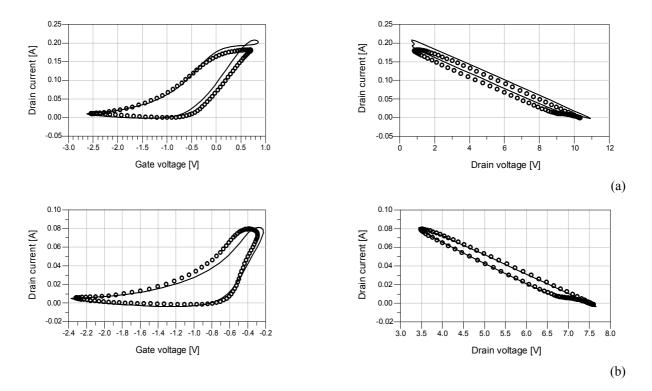

Electron devices used in high operating frequencies show low-frequency dispersive phenomena due to charge-trapping in spurious energy levels (in both deep-bulk and surface regions) and device self-heating. From a behavioural point of view, these phenomena results in the frequency dispersion of the measured trans-admittance and output impedance of the device (see Fig.1.6) and in a very different device I/V characteristics under static and dynamic conditions (see Fig.1.7).

Fig. 1.6 Low frequency dispersion of the measured device trans-admittance and output impedance due to the charge-trapping phenomena and device self-heating.

Unfortunately, dynamic dispersive phenomena due to self-heating and charge-trapping effects must be also considered whenever accurate nonlinear modelling is needed. The time constants involved in this kind of dynamics are typically much longer than the quasi-static and non-quasi-static dynamics and much longer than the typical operation period at microwave frequencies. They are usually considered in the range from tens of [µs] to even [s], corresponding to a frequency dispersion of the device characteristics in the range from few [Hz] to hundreds of [kHz].

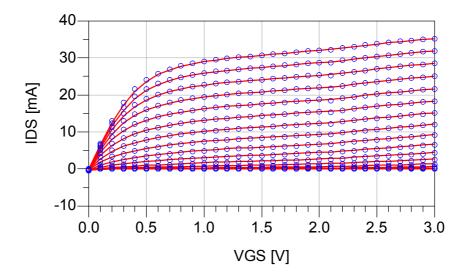

Fig. 1.7 Measured I/V characteristics of the device showing its different behaviour under static (black lines) and pulsed dynamic (dashed red lines) operations.

Considering the voltage-controlled description of the intrinsic electron device behaviour expressed by the functional (1.7) or, equivalently, by the functional (1.12), can be modelled by a new functional  $\Phi$  which also depends on the additional state variables  $\mathbf{x}(t)$  and  $T_j(t)$ , which are the trap filling status and the junction temperature respectively.

Considering a two-port electron device and hence a vectorial formulation, the device behaviour can be expressed as

$$\mathbf{i}(t) = \Phi \left| \mathbf{v}(t-\tau), T_j(t), \mathbf{x}(t) \right|_{\tau=0}^{T_M}.$$

(1.20)

Since the empirical device model aimed at the prediction of the device nonlinear behaviour at microwave or millimetre-wave frequencies, the additional state variables may be simply replaced by their static values  $T_{j0}$  and  $\mathbf{X}_0$ , respectively. In fact, all the spectral components of the signals involved are in this case above the upper cut-off frequencies of the dispersive effects.

The junction temperature depends on the instantaneous dissipated power and on the case temperature of the electron device, while the trap-filling status depends on the instantaneous

voltages applied to the device ports. Considering the fact that only the static values of the additional state variables can be taken into account and considering a constant case temperature, the following equations hold:

$$T_{j0} = F_T[P_0]$$

$$\mathbf{X}_0 = F_{\mathbf{X}}[\mathbf{V}_0, T_{j0}]$$

(1.21)

where  $F_T$  and  $F_X$  are suitable algebraic functions and  $V_0$  and  $P_0$  are the average voltage and dissipated power values in the actual dynamic conditions. Substituting (1.21) in (1.20) the following modified functional can be obtained:

$$\mathbf{i}(t) = \tilde{\Phi} \left| \mathbf{v}(t-\tau), P_0, \mathbf{V}_0 \right|_{\tau=0}^{T_M}$$

(1.22)

Eq. (1.22) is still too general to be directly used for device modelling; thus, it is simplified here by introducing a linearization with respect to suitable variables, which are now defined. To this aim, a new instantaneous entity is introduced as follows:

$$p_{s}(t) = F_{DC}^{i}[\mathbf{v}(t)] \cdot v_{i}(t)$$

(1.23)

where  $F_{DC}^{i}$  is the *i*-th component of the static current of the intrinsic device at a constant case temperature. The quantity  $p_{s}(t)$  represents a virtual (that is, purely mathematical) instantaneous power corresponding at every time instant to the power which would be dissipated in the presence of a constant applied voltage equal to  $v_{i}(t)$ .

After some simple algebraic manipulation (1.23) becomes

$$\mathbf{i}(t) = \tilde{\Phi} \left| \mathbf{v}(t-\tau) - \mathbf{v}(t) + \mathbf{v}(t), P_0 - p_s(t) + p_s(t), \mathbf{V}_0 - \mathbf{v}(t) + \mathbf{v}(t) \right|_{\tau=0}^{T_M}$$

(1.24)

and considering that  $p_s(t)$  is a purely algebraic function of  $v_2(t)$ , a new functional can be defined,

$$\mathbf{i}(t) = \Upsilon \left| \mathbf{v}(t), \mathbf{v}(t-\tau) - \mathbf{v}(t), p_{S}(t) - P_{0}, \mathbf{v}(t) - \mathbf{V}_{0} \right|_{\tau=0}^{T_{M}}.$$

(1.25)

Aside from its dependence on the instantaneous applied voltages, the new functional  $\Upsilon$  depends on three new variables: the dynamic voltage deviation  $\mathbf{v}(t-\tau) - \mathbf{v}(t)$ , the instantaneous power

deviation  $p_s(t) - P_0$ , which is related to the device self heating and the instantaneous voltage deviations  $\mathbf{v}(t) - \mathbf{V}_0$ , which are related to the device trap filling status.

The linearization of (1.25) with respect of the dynamic voltage deviation leads to the following equation

$$\mathbf{i}(t) = \mathbf{F}_{LF} \left[ \mathbf{v}(t), p_{S}(t) - P_{0}, \mathbf{v}(t) - \mathbf{V}_{0} \right] + \int_{0}^{T_{M}} \mathbf{g} \left[ \mathbf{v}(t) \right] \left[ \mathbf{v}(t-\tau) - \mathbf{v}(t) \right] d\tau$$

(1.26)

where the integral term accounts for the purely dynamic contribution to the device current due to reactive effects in the presence of very fast-varying signals (that is, microwave and millimetre-wave ranges), while the  $\mathbf{F}_{LF}$  nonlinear function represents the static device current, when the case is kept at a constant temperature, including also the deviations of the dynamic device current due to self-heating and the charge-trapping phenomena. Substantially  $\mathbf{F}_{LF}$  account for the nonlinear low-frequency dynamic behaviour of the electron device. Eq. (1.26) is the formulation of the NIM when low-frequency dispersive phenomena must be taken into account in the device empirical model.

Many empirical models based on (1.26) have been proposed (e.g. [10], [11]). In this paragraph only [11] will be exploited because it is identified on the basis of DC and Small-Signal (SS) low-frequency parameters [11] or low-frequency Large-Signal (LS) sinusoidal excitation (as recently proposed in [12]). It is also very suitable for the implementation in both equivalent circuit and Black-Box models. Such a model is based on the assumption that the macroscopic dynamic effect due to traps can be described in terms of a distributed electrical coupling (with very low cut-off frequency) between the gate-drain electrodes and the semi-insulator bulk ('self-backgating').

Such a 'self-backgating' model proposed in [11] expresses the  $\mathbf{F}_{LF}$  function as follows

$$\mathbf{F}_{LF}\left[\cdot\right] = \begin{bmatrix} F_{LF}^{1}\left[\mathbf{v}(t)\right] \\ F_{LF}^{2}\left[\mathbf{v}(t), p_{S}(t) - P_{0}, \mathbf{v}(t) - \mathbf{V}_{0}\right] \end{bmatrix} = \begin{bmatrix} F_{DC}^{1}\left[\mathbf{v}(t)\right] \\ \left[1 + k \cdot (p_{S}(t) - P_{0})\right] \cdot F_{DC}^{2}\left[\mathbf{v}_{m}(t)\right] \end{bmatrix}$$

(1.27)

where

$$\mathbf{v}_{m}(t) = \mathbf{v}(t) + \begin{bmatrix} \alpha_{G} & \alpha_{D} \\ 0 & 0 \end{bmatrix} \cdot (\mathbf{v}(t) - \mathbf{V}_{0}).$$

(1.28)

In (1.27) and (1.28),  $F_{DC}^{i}$  are the static current characteristics, and  $\alpha_{G}$ ,  $\alpha_{D}$ , and k are suitable scalar coefficients to be determined.

This model treats the low-frequency dispersive phenomena by controlling the static drain current with an equivalent gate voltage, which accounts for the trapping phenomena within the device, and multiplying the obtained drain current by a correcting factor, which accounts for the device selfheating.

For what concern the equivalent circuit modelling of the low-frequency dispersive phenomena, many solutions have been also proposed [13]-[18].

#### **1.3 Modelling of the Extrinsic Parasitic Network**

The modelling of the linear extrinsic parasitic network of Fig.1.1 is another important aspect of the empirical modelling of electron devices.

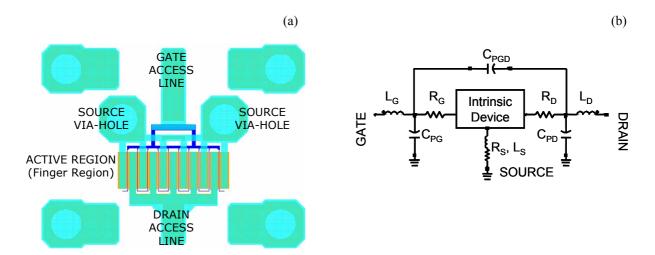

Considering the typical device layout of a FET for on-wafer measurements of Fig.1.8 it is clear that the intrinsic device (which is physically related to the finger region of the device) is connected to the external world through the gate and drain access lines and the source via holes. Although the design of those structures aimed to minimize their parasitic effects, these latter cannot be neglected at the typical frequencies of operation of the device.

In conventional approaches, the modelling of the linear extrinsic parasitic network is carried out by means of an equivalent circuit (also for Black-Box modelling approaches), which is identified by means of the measured characteristics of the electron device.

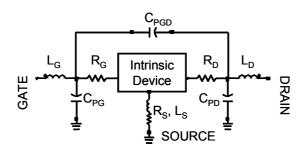

Fig. 1.8 (a) Typical layout of a multi-finger FET transistor for on-wafer measurements. (b) Typical topology of lumped component modelling the linear extrinsic parasitic network.

The topology of the equivalent circuit describing the extrinsic parasitic network, is shown in Fig.1.8. The series elements account for the series parasitic effects (resistive and inductive effects)

due to the gate and drain accesses, the gate and drain manifolds and the source via holes and air bridge. The capacitive parallel shell accounts for the pad capacitances and all the capacitive coupling between the finger metallizations. In many recent works the capacitance shell is placed outermost in order to simplify the de-embedding procedure.

The values of the lumped extrinsic elements can be obtained by several techniques proposed in many works which can be found in the literature. Most of them aimed to the extraction of a broadband multi-bias linear (i.e. Small-Signal) equivalent circuit electron device model, describing also the linear extrinsic element extraction procedure.

The linear Equivalent Circuit Parameters (ECP) extraction techniques are based on different methods. Optimizer-based extraction techniques are in widespread use, but they suffer from the non-uniqueness [19] of solutions. Improvements have been aimed e.g. at taking into account additional measurements [20], using a partitioning approach [21], or an automatic decomposition technique [22], but uncertainties are still existing with respect to the starting value problem. Fast analytical techniques [23]-[27] need special test structures or additional measurement steps such as dc and/or RF characterization of FET's under forward-bias condition. Such sequentially derived solutions may yield large errors in FET modelling [28]. Using multi-circuit measurements [29] the model parameters can uniquely be identified, but the number of optimization variables increases rapidly. A purely analytical reverse solution [30] can only be applied under the assumption of almost ideal measured S-parameters.

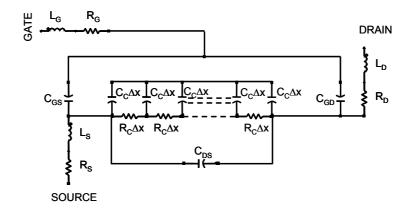

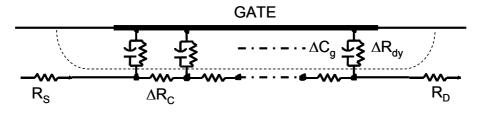

Both analytical and optimizer-based conventional techniques use some simplifications occurring at particular bias conditions. Analytical techniques use them in order to derive simpler analytical description of the electron device equations, while the optimizer-based techniques use them in order to derive the initial condition of the optimization problem. Often the simplifications used are those obtained with an unbiased drain with the device operating in the so called "Cold FET" conditions. F. Diamand *et al.* [23] in 1982 presented a new measurement method of the parasitic series impedances of microwave MESFETs based on "Cold FET" condition. "Cold FET" condition means that the common source device is biased at zero drain voltage, that is  $V_{DS} = 0$  V. In such condition the region under the gate can be described by the distributed, uniform, R-C transmission line of Fig.1.9, leading to a simple analytical model.

Review of empirical electron device modelling

Fig. 1.9 Equivalent circuit model proposed in [23] for  $V_{DS} = 0$  V.

In Fig.1.9 the pad capacitances are neglected. The device equivalent circuit is composed by the R-C transmission line modelling the region under the gate, the parasitic lumped series element and the lumped capacitances  $C_{GS}$ ,  $C_{GD}$ ,  $C_{DS}$ . The total capacitance of the depletion layer under the gate is  $C_c$ , the total channel resistance is  $R_C$ .  $C_{GS}$  and  $C_{GD}$  represent the fringing capacitances due to the extension of the depleted layer between the gate and source at one side and the gate and drain at the other side, and  $C_{DS}$  is the inter-electrode capacitance between the drain and source. Both pad capacitances  $C_{PG}$  and  $C_{PD}$  can be neglected throughout this section to ease the analysis without a loss of generality.

The analytic description of the network of Fig.1.9 can be simplified if the electrical length of the transmission line is short. This assumption can be satisfied under two conditions: a channel opening higher than 20% of the total channel height and a low frequency band. The former condition is important so that the value of  $R_C$  is reasonably small. This condition is already satisfied because the gate is always biased throughout the analysis at  $V_{GS} \ge 0$ . The latter condition is met for frequencies up to about 10 GHz. Therefore, a subfrequency band of the measurements should be used so that the maximum frequency of the subband is 10 GHz. This assumption it is called low-frequency-open-channel approximation. Assuming that it holds for all the capacitances of Fig.1.9, the impedance matrix which define the device  $\mathbf{Z} = \mathbf{R} + j \cdot \mathbf{X}$  is given by

$$\mathbf{R} = \begin{bmatrix} R_{S} + R_{G} + \frac{1}{3} \frac{C_{C} + 3C_{DS} + 3C_{GD}}{C_{C} + C_{DS} + C_{GD}} R_{C} & R_{S} + \frac{1}{2} \frac{C_{C} + 2C_{GD}}{C_{C} + C_{DS} + C_{GD}} R_{C} \\ R_{S} + \frac{1}{2} \frac{C_{C} + 2C_{GD}}{C_{C} + C_{DS} + C_{GD}} R_{C} & R_{S} + R_{D} + R_{C} \end{bmatrix}$$

(1.29)

$$\mathbf{X} = \begin{bmatrix} \omega(L_{S} + L_{G}) - \frac{1}{\omega(C_{C} + C_{GS} + C_{GD})} & \omega L_{S} \\ \omega L_{S} & \omega(L_{S} + L_{D}) \end{bmatrix}$$

In [23] is shown how starting from multi-bias "Cold FET" device measurements and fitting the measured Z-parameters to the analytical model (1.29), the values of the extrinsic parasitic elements can be found. Unfortunately the proposed technique requires that some technological parameters (such as the built-in potential) are known a priori.

In 1988 Dambrine et al. [24] extended the analytical technique proposed by Diamand considering the distributed R-C network of Fig.1.10 representing the FET channel under the gate at  $V_{DS} = 0$  V.

Fig. 1.10 Sketch of the distributed R-C network under the gate as proposed in [24].

According to Fig. 1.10, for any gate biasing condition, the following impedance matrix describing the intrinsic device can be written

$$\mathbf{Z} = \begin{bmatrix} R_C / 3 + z_{dy} & R_C / 2\\ R_C / 2 & R_C \end{bmatrix}$$

(1.30)

where  $R_C$  is the channel resistance under the gate and  $z_{dy}$  is the equivalent impedance of the schottky barrier which can be written as follows:

$$z_{dy} = \frac{R_{dy}}{1 + j\omega C_g R_{dy}} \qquad \text{with} \quad R_{dy} = \frac{nkT}{qI_g}$$

(1.31)

In (1.31) *n* is the ideality factor, *k* the Boltzmann constant, *T* the temperature,  $C_g$  the gate capacitance and  $I_g$  the dc gate current. As the gate current increases,  $R_{dy}$  decreases and  $C_g$  increases but the exponential behaviour of  $R_{dy}$  versus the gate-source voltage (which is increased as well) is the dominant factor; consequently the term  $\omega R_{dy}C_g$  tends to zero for gate current densities close to  $10^8$  [A/m<sup>2</sup>]. For such a gate current, the capacitive effect of the gate disappears and the  $z_{11}$  parameter becomes real. Besides the influence of the  $C_{PG}$  and  $C_{PD}$  parasitic capacitances of Fig.1.8 is negligible and consequently the extrinsic **Z** matrix is simply determined by adding the parasitic resistances and inductances of Fig.1.8 to the intrinsic **Z** matrix (1.30). Thus we have

$$\mathbf{Z} = \mathbf{R} + j\mathbf{X} = \begin{bmatrix} R_s + R_G + \frac{R_C}{3} + \frac{nkT}{qI_g} & R_s + \frac{R_C}{2} \\ R_s + \frac{R_C}{2} & R_s + R_D + R_C \end{bmatrix} + j \begin{bmatrix} \omega(L_s + L_G) & \omega L_s \\ \omega L_s & \omega(L_s + L_D) \end{bmatrix}$$

(1.32)

In (1.32) it is shown that the imaginary part of the Z-parameters increases linearly versus frequency while the real part is frequency independent. In addition it must be noted that the real part of  $z_{11}$  increases as  $1/I_g$ . As shown in [24], the theoretical expression (1.32) of the Z-parameters of the device are in quite good agreement with the experimental data.

From the imaginary parts of the measured the parasitic inductances can be uniquely determined. Besides the Z-parameters' real parts provide three relations between the four unknowns  $R_G$ ,  $R_D$ ,  $R_S$  and  $R_C$ . At this step, an additional relation is needed to separate the four unknowns. This additional relation can be:

- 1) The value of the sum  $R_s + R_D$  determined by some conventional method for example with the network analyzer using the real part of  $z_{22}$ .

- 2) The value of  $R_G$  if it can be provided from the resistance measurement from pad to pad.

- 3) The value of  $R_s$  and  $R_D$  provided by dc measurement.

- 4) The value of  $R_c$  if the channel technological parameters are known.

It is important to note that (1.32) holds only at high gate current and for devices with low metallization resistances. If those conditions are not met, the distribution effect shown in Fig.1.10 and expressed by (1.30) and (1.31) has to be taken into consideration.

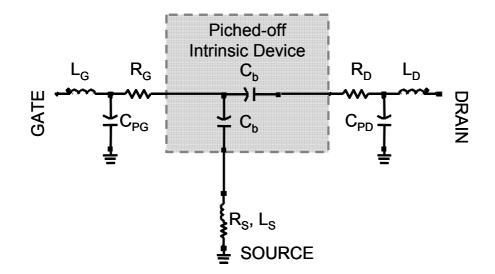

The  $C_{PG}$  and  $C_{PD}$  parasitic capacitances are measured by suppressing the conductivity of the channel. As a matter of fact, at zero drain bias and for a gate voltage lower than the pinch-off voltage  $V_P$ , the intrinsic gate capacitance (i.e., under the gate) cancels, as does the channel conductance. Under these biasing conditions, the FET equivalent circuit is shown in Fig.1.11. In this figure  $C_b$  represents the fringing capacitance due to the depleted layer extension at each side of the gate. For frequencies up to a few gigahertz, the resistances and inductances have no influence on the imaginary part of the Y-parameters and the **Y** matrix simply is

$$\mathbf{Y} = \begin{bmatrix} j\omega(C_{PG} + C_b) & -j\omega C_b \\ -j\omega C_b & j\omega(C_{PD} + C_b) \end{bmatrix}$$

(1.33)

The analytic behaviour stated by (1.33) is in quite good agreement with the Y-parameters measurements in "Cold FET" pinched-off conditions.

Fig. 1.11 Small-signal equivalent circuit of a FET at zero drain bias voltage and gate voltage lower than the pinch-off voltage.

In the context of empirical modelling, the "Cold FET" characteristics are very suitable for the identification of the extrinsic parasitic network of an electron device as shown by Dambrine [24] and by other authors. For example in 1990 Berroth and Bosh [25] extended the Dambrine's method in order to derive a broadband small-signal equivalent circuit for microwave FETs.

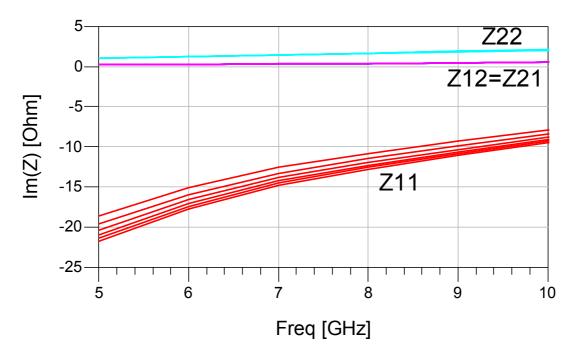

The main drawback of those techniques is the additional information needed in order to extract the correct values of the series resistances. Another problem is also shown in Fig.1.12.

Fig. 1.12 Imaginary part of the measured Z-parameters of a 0.25x900  $\mu$ m2 GaAs PHEMT for different forward gate bias conditions.

The figure shows that the measured  $z_{11}$  of an actual PHEMT device is in contrast with the analytic behavior of eq. (1.32). This is due to the fact that the hypothesis of high gate current densities is not verified and the measured imaginary part of  $z_{11}$  presents an high capacitive effect as expected in (1.29).

In literature can be found many works which solve the mentioned problems. For example in 1994 Lin and Kompa [31] proposed a method to estimate the parasitic elements of Fig.1.8 from pinch-off measurements, in order to generate the initial guess of their optimization-based technique. Their method had been extended in 2003 by Khalaf and Riad [32] using also "Cold FET" forward bias measurements in order to reduce the measurement noise dependence of the extracted values. In 1996, instead, Yanagawa *et al.* [33] proposed an analytical extraction procedure of all the parasitic elements of Fig.1.8 using only "Cold FET" pinched-off measurements.

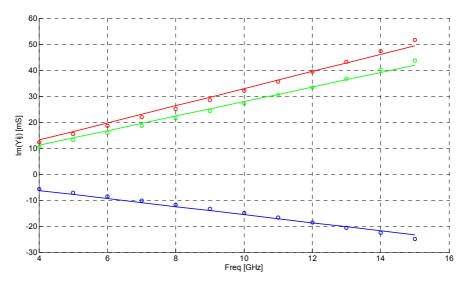

Let consider for example the extraction of the extrinsic parasitic element of a 0.25x900  $\mu$ m<sup>2</sup> GaAs PHEMT by means of the Yanagawa [33] direct method. Only a single bias broadband S-parameters measurement in pinch-off condition is needed. Thus the device has been biased at V<sub>GS</sub> = -1.4 V ( $V_p = -1.1 V$ ) and V<sub>DS</sub> = 0 V and its S-parameters have been measured in the frequency range [4 - 110 GHz]. Converting the S-parameters to Y-parameters it is found that for low-frequency (i.e. in the range [4 - 10 GHz]) these latter are in agreement with the behaviour expressed

in (1.33). Thus the value of  $C_{PG}$  and  $C_{PD}$  parasitic elements can be deduced. Since the equivalent circuit of Fig.1.12 neglect the effect of the inter-electrode capacitance  $C_{DS}$  and  $C_{PD}$  results overestimated, its value is selected equal to the value of  $C_{PG}$ : this is a good approximation when the device has equal gate and drain access structures. Fig.1.13 shows the model (1.33) fitting to the device measurement in the low-frequency range of validity of the model.

Fig. 1.13 Imaginary part of the admittance parameter of the 0.25x900  $\mu$ m<sup>2</sup> GaAs PHEMT in the low-frequency range [4 – 10 GHz] of validity of model (1.33). Measured Y-parameters (circles) versus model fitting (lines). Y<sub>12</sub> = Y<sub>21</sub> (blue), Y<sub>11</sub> (red) and Y<sub>22</sub> (green).

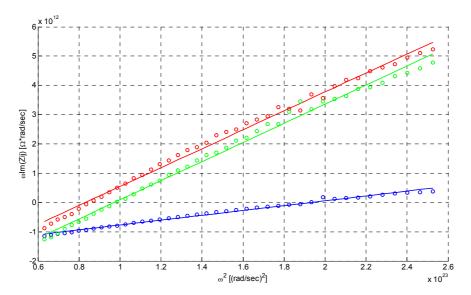

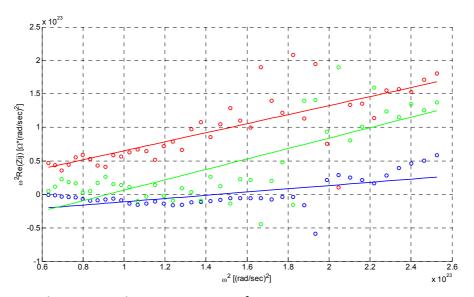

After de-embedding the effect of the extracted pad capacitances, the other six extrinsic elements can be determined from the Z-parameters as shown in [33]. In fact both inductances and resistances are extracted at very high frequencies (i.e. in the range [40 – 80 GHz]), in order to increase the accuracy of these extrinsic elements by decreasing the intrinsic capacitive effects. As shown in Fig.1.14 and Fig.1.15, the inductances are determined by the slopes of the straight lines approximating  $\omega \text{Im}(Z_{ij})$  vs.  $\omega^2$ , while the resistances are obtained from the slope of the straight lines approximating  $\omega^2 \text{Re}(Z_{ij})$  vs.  $\omega^2$ .

Fig. 1.14 Plot of  $\omega \text{Im}(Z_{ij})$  vs.  $\omega^2$  of the 0.25x900  $\mu \text{m}^2$  GaAs PHEMT in the high-frequency range [40 – 80 GHz].  $Z_{12} = Z_{21}$  (blue),  $Z_{11}$  (red) and  $Z_{22}$  (green).

Fig. 1.15 Plot of  $\omega^2 \operatorname{Re}(Z_{ij})$  vs.  $\omega^2$  of the 0.25x900  $\mu m^2$  GaAs PHEMT in the high-frequency range [40 – 80 GHz].  $Z_{12} = Z_{21}$  (blue),  $Z_{11}$  (red) and  $Z_{22}$  (green).

In this example the extracted values of the 0.25x900  $\mu$ m<sup>2</sup> GaAs PHEMT extrinsic parasitic elements are: C<sub>PG</sub> = C<sub>PD</sub> = 39.0 fF, R<sub>G</sub> = 0.43  $\Omega$ , R<sub>D</sub> = 0.54  $\Omega$ , R<sub>S</sub> = 0.24  $\Omega$ , L<sub>G</sub> = 24.0 pH, L<sub>D</sub> = 24.4 pH, L<sub>S</sub> = 8.3 pH.

Although the above techniques are the most used for the identification of the extrinsic lumped parasitic elements, it should be noticed that the Cold FET conditions are potentially inaccurate because they use the device in operating conditions which are different from the actual conditions used in MMIC designs. Hence other techniques have been developed using so called "Hot FET"

measurements where the device is biased in the actual operating condition. This kind of techniques are used for example in [34] where the parasitic elements of Fig.1.8 are extracted once the resistances have been calculated from DC measurements.

#### **References.**

- R. R. Daniels, A. T. Yang, and J. P. Harrang, "A universal large/small signal 3-terminal FET model using a nonquasistatic charge-based approach", *IEEE Trans. Electron Devices*, vol. 40, issue 10, pp. 1723-1729, Oct. 1993.

- [2] M. Fernández-Barciela, P. J. Tasker, Y. Campos-Roca, M. Demmler, H. Massler, E. Sánchez, C. Currás-Francos, and M. Schlechtweg, "A simplified broadband large-signal nonquasi-static table-based FET model", *IEEE Trans. Microwave Theory Tech.*, vol. 48, issue 3, pp. 395-405, March 2000.

- [3] A. Santarelli, V. Di Giacomo, A. Raffo, P. A. Traverso, G. Vannini, F. Filicori, "A Nonquasi-Static Empirical Model of Electron Devices", *IEEE Trans. Microwave Theory Tech.*, vol. 54, issue 12, pp. 4021-4031, December 2006.

- [4] W. R. Curtice, "A MESFET model for use in the design of GaAs integrated circuits", *IEEE Trans. Microwave Theory Tech.*, vol. 28, issue 5, pp. 448-455, May 1980.

- [5] I. Angelov, H. Zirath, N. Rosman, "A new empirical nonlinear model for HEMT and MESFET devices", *IEEE Trans. Microwave Theory Tech.*, vol. 40, issue 12, pp. 2258-2266, December 1992.

- [6] V. Volterra, Theory of functional and Integral and Integro-differential Equations, New York: Dover, 1959.

- [7] L. O. Chua, Y. Liao"Measuring Volterra kernels (II)", *Int. Journal of Circuit Theory and Application*, vol. 17, issue 2, pp. 151-190, 1989.

- [8] D. Schreurs, J. Wood, N. Tufillaro, L. Barford, D. E. Root, "Construction of behavioral models for microwave devices from time domain large-signal measurements to speed up high-level design simulations", *Int J RF and Microwave CAE*, vol. 13, issue 1, pp. 54-61, Dec 2002.

- [9] F. Filicori, G. Vannini, V. A. Monaco, "A nonlinear integral model of electron devices for HB circuit analysis", *IEEE Trans. Microwave Theory Tech.*, vol. 40, issue 7, pp. 1456-1465, July 1992.

- [10] F. Filicori, A. Santarelli, P.A. Traverso, A. Raffo, G. Vannini, M. Pagani, "Non-linear RF device modelling in the presence of low-frequency dispersive phenomena", *Int J RF and Microwave CAE*, vol. 16, issue 1, pp. 81-94, Nov. 2005.

- [11] A. Santarelli, G. Vannini, F. Filicori, P. Rinaldi, "Backgating model including self-heating for low-frequency dispersive effects in III-V FETs", *Electron. Letters*, vol. 34, pp. 1974–1976, Oct 1998,.

- [12] A. Raffo, A. Santarelli, P. A. Traverso, G. Vannini, F. Filicori, "On-wafer I/V measurement setup for the characterization of low-frequency dispersion in electron devices", in *Proceedings of 63rd ARFTG Conference Digest Spring*, pp. 21-28, June 2004.

- [13] N. Scheinberg, R. Bayruns, and R. Goyal, "A low frequency GaAs MESFET circuit model", *IEEE J. Solid-State Circuits*, vol.23, issue 2, pp. 605 608, April 1988.

- [14] J.M. Golio. M.G. Miller, G.N. Maracas, D.A. Johnson, "Frequency-Dependent Electrical Characteristics of GaAs MESFET's", *IEEE Trans. Electron Devices*, vol.37 No.5, pp. 1217 – 1227, May. 1990.

- [15] J.-W. Lee and K.J. Webb, "A Temperature-Dependent Nonlinear Analytic Model for AlGaN–GaN HEMTs on SiC", IEEE Trans. Microwave Theory and Techn., vol. 52, No. 1, pp. 2–9, Jan. 2004.

- [16] W.R. Curtice, M. Ettenberg, "A Temperature-Dependent Nonlinear Analytic Model for AlGaN–GaN HEMTs on SiC", *IEEE Trans. Microwave Theory and Techn.*, vol. 33, No. 12, pp. 1383 - 1394, Dec. 1985.

- [17] I. Angelov, L. Bengtsson, and M. Garcia, "Extensions of the Chalmers nonlinear HEMT and MESFET model", *IEEE Trans. Microwave Theory and Techn.*, vol. 44, pp. 1664-1674, Oct. 1996.

- [18] V.I. Cojocaru and T. Brazil, "A scalable general-purpose model for microwave FET's including DC/AC dispersion effects", *IEEE Trans. Microwave Theory and Techn.*, vol. 45, pp. 2248-2255, Dec. 1997.

- [19] R. L. Vaitkus, "Uncertainty in the values of GaAs MESFET equivalent circuit elements extracted from measured two-port scattering parameters," in *Proc. IEEE Conf. High Speed Semiconductor Devices Circuits*, Cornell Univ., Ithaca, NY, pp. 301-308, 1983.

- [20] W. R. Curtice and R. L. Camisa, "Self-consistent GaAs FET models for amplifier design and device diagnostics," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 1573-1578, Dec. 1984.

- [21] H. Kondoh, "An accurate FET modelling from measured S-parameters," in *IEEE MTT-S Int. Microwave Symp.* Dig., Baltimore, MD, 1986, pp. 377-380.

- [22] J. W. Bandler and Q. J. Zhang, "An automatic decomposition technique for device modelling and large circuit design," in IEEE MTT-S Int. Microwave Symp. Dig., Las Vegas, NV, 1987, pp. 709-712.

- [23] F. Diamand, M. Laviron, "Measurement of the Extrinsic Series Elements of a Microwave Mesfet Under Zero Current Conditions", in *Proc. 12th European Microwave Conf.*, pp. 451-456, Oct. 1982.

- [24] G. Dambrine, A. Cappy, F. Heliodore, and E. Playez, "A new method for determining the FET small-signal equivalent circuit", *IEEE Trans. Microwave Theory and Tech.*, vol. MTT36, issue 7, pp. 1151-1159, July 1988.

- [25] M. Berroth, R. Bosch, "Broad-band determination of the FET small-signal equivalent circuit", *IEEE Trans. Microwave Theory and Tech.*, vol. 38, issue 7, pp. 891-895, July 1990.

- [26] J. C. Costa, M. Miller, M. Golio, and G. Noms, "Fast, accurate, on-wafer extraction of parasitic resistances and inductances in GaAs MESFET's and HEMT's," *in IEEE MTT-S Int. Microwave Symp. Dig.*, Albuquerque, NM, pp. 1011-1014, 1992.

- [27] H. Sledzik and I. Wolff, "A new approach to nonlinear modelling and simulation of MESFET's and MODFET's," in *Proc. 20th European Microwave Conf.*, Budapest, Hungary, 1990, pp. 784-789.

- [28] W. R. Curtice, "Active device modeling for GaAs MMIC's," in *IEEE MTT-S Int. Microwave Symp.*, Albuquerque, NM, 1992.

- [29] J. W. Bandler, S. H. Chen, and S. Daijavad, "Microwave device modeling using efficient I 1 optimization: a novel approach," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-36, pp. 1282-1293, Dec. 1986.

- [30] G. Kompa and F. Lin, "FET modelling using an analytical extraction method based on broadband S-parameter measurement," in *Proc. 20th European Microwave Conf.*, Budapest, Hungary, 1990, pp. 778-783.

- [31] F. Lin, G. Kompa, "FET Model Parameter Extraction Based on Optimization With Multiplane Data-Fitting and Bidirectional Search–A New Concept," *IEEE Trans. Microwave Theory and Tech.*, vol. 42, issue 7, pp. 1114-1121, July 1994.

- [32] Y. A. Khalaf, S. M. Riad, "Novel technique for estimating metal semiconductor field effect transistor parasitics", *Int J RF and Microwave CAE*, vol. 13, issue 1, pp. 62-73, Dec. 2002.

- [33] S. Yanagawa, H. Ishihara, M. Ohtomo, "Analytical method for determining equivalent circuit parameters ofGaAs FETs", *IEEE Trans. Microwave Theory and Tech.*, vol. 44, issue 10, pp. 1637-1641, Oct. 1996.

[34] E. Arnold, M. Golio, M. Miller, B. Beckwith, "Direct extraction of GaAs MESFET intrinsic element and parasitic inductance values", *in IEEE MTT-S Int. Microwave Symp. Dig.*, Dallas, TX, pp. 359-362, May 1990.

Review of empirical electron device modelling

## **CHAPTER 2**

# SCALING OF Empirical Models

### 2.1 Introduction to the scalability problem.

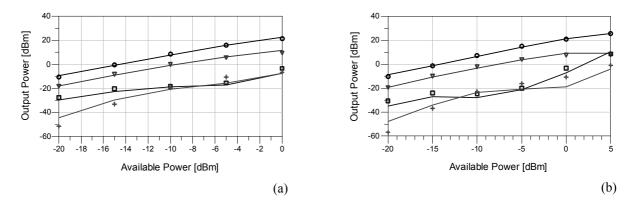

Micro- and millimetre-wave Integrated Circuit (MMIC) design requires electron device models which accurately describe the linear and nonlinear behaviour up to extremely high frequencies. When incorporated into circuit simulation routines, accurate device models allow engineers to design and optimize circuit performance prior to fabrication. Standing alone, device models often provide the information required when choosing an appropriate device for a specific application or when making decision concerning device processing [1]. The combination of physically based models and monolithic circuit technology potentially allows designers to perform simultaneous device and circuit optimization during the design process.

An important task facing both circuit designers and design fabrication engineers is evaluating the ultimate potential of a device for specific applications. This information can be important for choosing an appropriate device for particular applications. Although such an evaluation can be accomplished by developing a model for the device and optimizing the performance using a circuit simulation routine, such an approach is usually prohibitively time consuming. Instead, the problem is often first approached using easily derive performance figures of merit (FOMs).

The FOMs strictly depend on the technological process, e.g. the device gate length [1], and their evaluation can be accomplished only through physically based models, but once the technology has been selected, many FOMs can be estimated directly from device empirical models.

In fact, in addiction to their dependence on the device bias conditions, most of the FOMs depend on some device geometrical parameters, such as the number of gate fingers and the gate width, dependences which can be somehow taken into account also by empirical models. Hence the

availability of empirical models of different-in-size device is a key aspect for MMIC's designers, avoiding the characterization and the extraction of an empirical model for each device size.

The scalability property of an empirical model could be comprehended as the extrapolation capability of the empirical model with respect to the device geometrical parameters. This important property allows the designer to select the best device for the particular application and the best device for the different blocks composing the overall MMIC (e.g. the driver stage and the power stage of a power amplifier).

Moreover, in order to extract an empirical model valid for the entire technological process, the availability of a scalable empirical model allows to the characterization of only one device (or only few devices), providing a less time consuming characterization phase.

Fig.2.1 represents again the general empirical model description showing the extrinsic parasitic network connecting the intrinsic device to the external terminals.

Fig. 2.1 Empirical electron device model. The model is composed by a linear extrinsic parasitic network connecting the nonlinear intrinsic device to the external world.

Many authors proposing scalable models [2]-[4], adopt the fundamental hypothesis that *the intrinsic device elements scale linearly with the periphery* of the device. This is a quite generally accepted conclusion which implicitly assumes that the intrinsic model is a sound representation of the "active part" of the electron device and, consequently, that the parasitic effects have been accurately modelled. In other words, the scalability of an electron device model strictly depends on the scalability of the linear extrinsic parasitic network of Fig.2.1.

The aim of this chapter is showing how conventional lumped parasitic networks, together with simple linear scaling rules, cannot provide the definition of accurate scalable models. In order to

overcome this problem either more complicate technology-dependent scaling rules or the use of distributed models had been proposed in the literature to provide scalability issues.

### **2.2 Conventional Scaling Rules**

Conventional topologies adopted for the extrinsic parasitic networks of Fig.2.1 offer a poor link between technological process parameters and the corresponding device electrical response, providing poor model accuracy using conventional scaling rules [1]. Fig.2.2 shows the conventional description of the extrinsic parasitic network discussed in Chapter 1.3.

Fig. 2.2 Typical topology of lumped component modelling the linear extrinsic parasitic network.

Considering the gate series parasitic elements  $L_G$ ,  $R_G$ , they account for the resistance and inductance associated to the gate fingers but also to the gate manifold. While the resistance and inductance of the paralleled gate fingers scale with linear relations with respect to the gate width and the number of fingers, the effect of the manifold cannot follow the linear rules and it may causes some inaccuracies in the scaled model. The same considerations hold for the drain series parasitic elements  $L_D$ ,  $R_D$ . The source series parasitic elements  $L_S$ ,  $R_S$ , instead, account for the resistance and inductance associated to the source metallization placed within the finger area and connected to the via holes through the air bridge. The air bridge and the via holes are responsible in this case of the inaccuracies which occur when using a simple linear approximation.

The shunt capacitance parasitic elements  $C_{PG}$ ,  $C_{PD}$  and  $C_{PGD}$  account for both the gate and drain pad and manifold capacitive effects and the inter-electrode capacitances. All these capacitive effects don't scale linearly with the device periphery.

It is clear that simple linear rules lead to some inaccuracies which are emphasized at higher frequencies. This is the case of the scaling rules proposed in [1], where the extrinsic parasitic elements of Fig.2.2 scale according to the following rules:

$$(L_x)^{sc} = (L_x)^{ref}$$

, where  $x = G, D, S$  (2.1a)

Scaling of empirical models

$$(C_{x})^{sc} = (C_{x})^{ref}, \text{ where } x = PG, PD, PGD$$

$$(R_{G})^{sc} = (R_{G})^{ref} \cdot \frac{W^{sc} \cdot (N^{ref})^{2}}{(N^{sc})^{2} \cdot W^{ref}}$$

$$(R_{D})^{sc} = (R_{D})^{ref} \cdot \frac{W^{ref}}{W^{sc}} \qquad (2.1c)$$

$$(R_{S})^{sc} = (R_{S})^{ref} \cdot \frac{W^{ref}}{W^{sc}}$$

Rules (2.1a) and (2.1b) express that the parasitic inductances and capacitances do not scale with the device periphery, while rule (2.1c) expresses that the parasitic resistances scale with respect to the total gate width W (i.e. the total periphery of the device) and the number of gate fingers N. The subscripts 'sc' and 'ref' mean "scaled device" and "reference device" respectively.

In order to point out the inaccuracy of the scaling rules (2.1) a conventional Small-Signal (SS) Equivalent Circuit (EC) model has been extracted for a reference  $4x50 \mu m$  PHEMT belonging to a 0.5  $\mu m$  GaAs process. The SS-EC model has the linear extrinsic parasitic network defined as in Fig.2.2 and the conventional 7 element intrinsic EC of Fig.2.3.

Fig. 2.3 Conventional 7 elements Small-Signal Equivalent Circuit for the intrinsic device.

The SS-EC model has been extracted for a typical class-A operation bias condition, identifying the extrinsic elements through the Yanagawa direct extraction method (as shown in Chapter 1.3) and the intrinsic element through CAD optimization. The values of the extracted parameters are shown in Table I.

| Срд           | Cpd           | Rg            | Rd   | Rs   | Lg   | Ld   | Ls   |

|---------------|---------------|---------------|------|------|------|------|------|

| [fF]          | [ <b>fF</b> ] | [Ω]           | [Ω]  | [Ω]  | [pH] | [pH] | [pH] |

| 11.3          | 0.00          | 4.60          | 2.02 | 0.58 | 19.7 | 16.5 | 12.5 |

| Cgs           | Cgd           | Cds           | Ri   | Rds  | gm   | τ    |      |

| [ <b>fF</b> ] | [ <b>f</b> F] | [ <b>fF</b> ] | [Ω]  | [Ω]  | [mS] | [ps] |      |

| 262           | 18.6          | 46.6          | 0.75 | 472  | 66.0 | 1.45 |      |

TABLE I

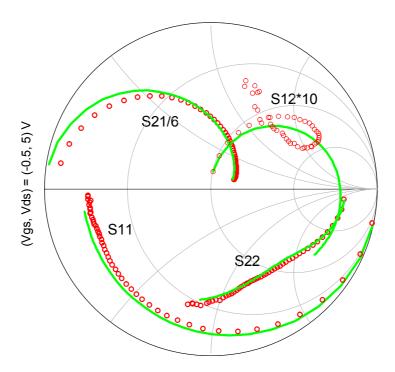

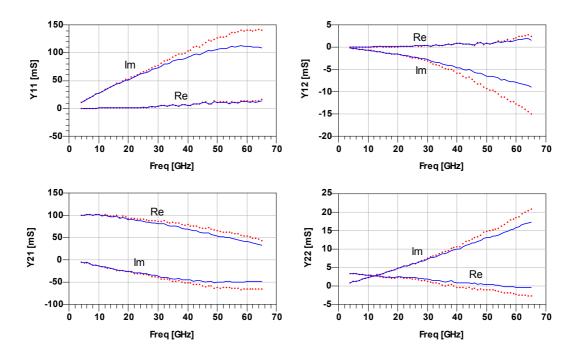

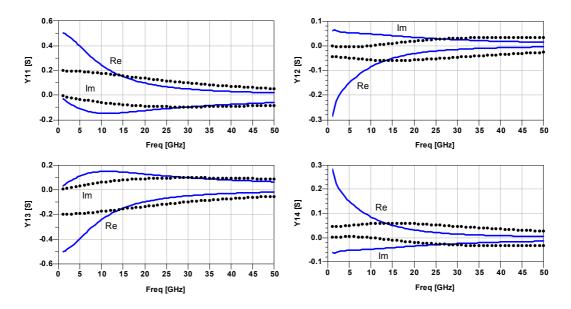

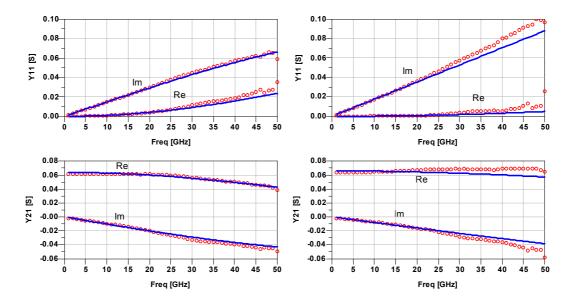

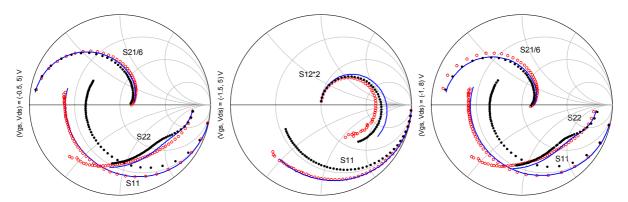

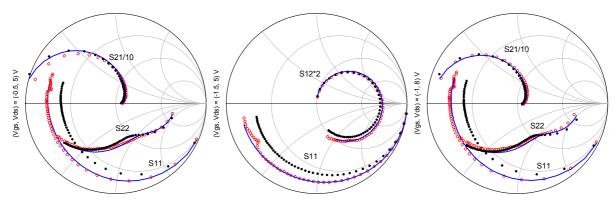

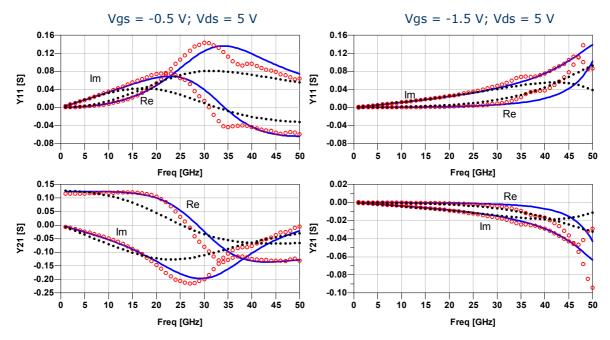

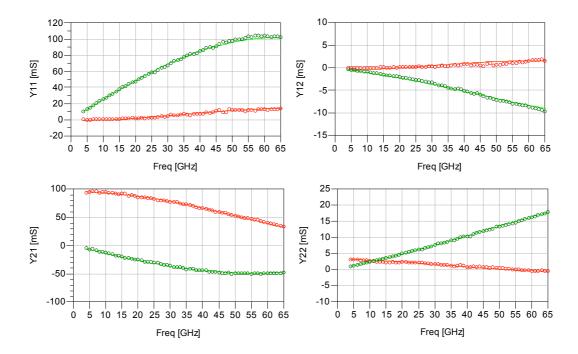

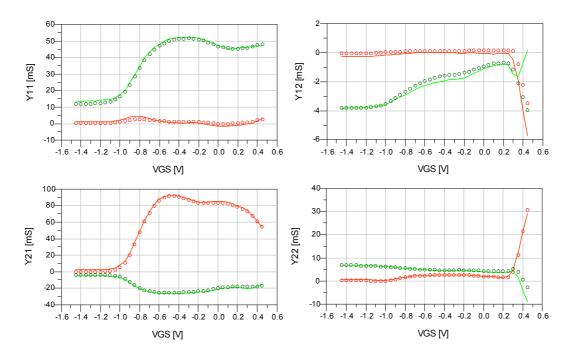

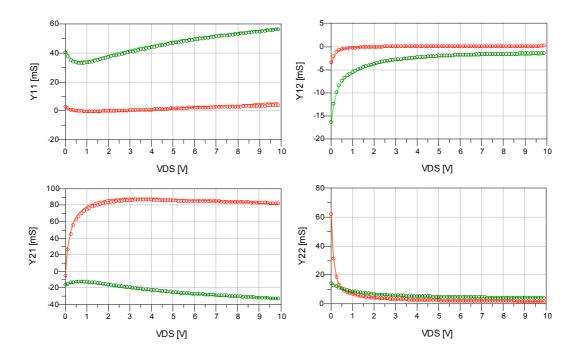

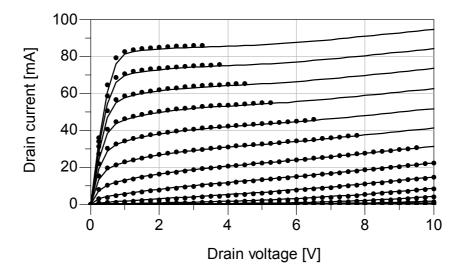

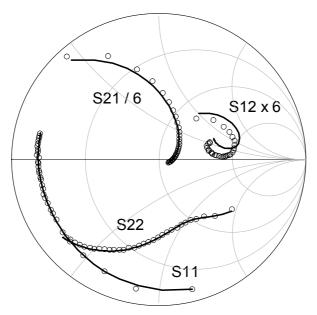

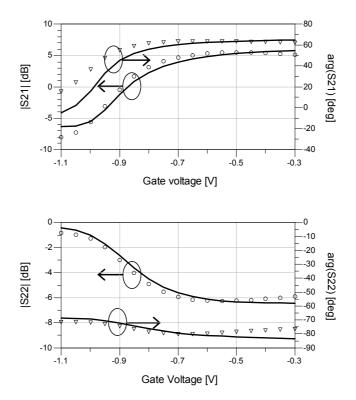

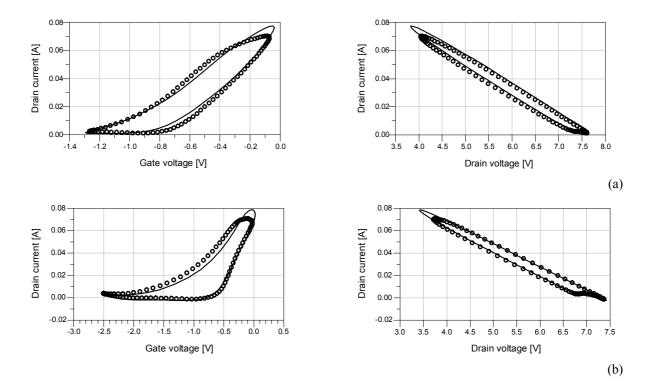

The SS-EC model predictions of the measured device behaviour is shown in Fig.2.4. It can be seen that the model is quite accurate up to the maximum measured frequency for all the scattering parameters.

Fig. 2.4 SS-EC model prediction (lines) of the reference 4x50  $\mu$ m PHEMT measured behaviour (circles). S-parameter in the frequency range [0.5 – 50 GHz] at V<sub>GS</sub> = -0.5 V, V<sub>DS</sub> = 5 V.

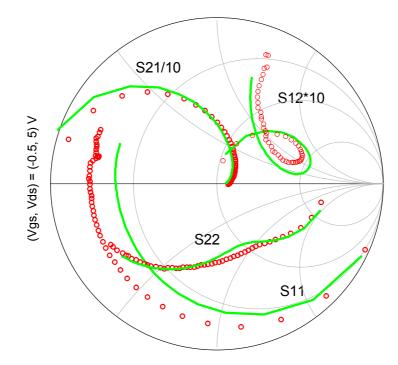

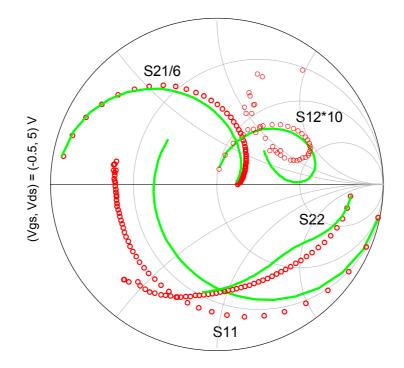

In order to predict the behaviour of different devices belonging to the same technological process, namely a  $4x100 \mu m$  and a  $2x100 \mu m$  PHEMTs, such a SS-EC model has been scaled according to rules (2.1) for the extrinsic parasitic elements and by linearly scaling the intrinsic elements according to [1].

Fig. 2.5 SS-EC scaled model prediction (lines) of the 4x100  $\mu$ m PHEMT measured behaviour (circles). S-parameter in the frequency range [0.5 – 50 GHz] at V<sub>GS</sub> = -0.5 V, V<sub>DS</sub> = 5 V.

Fig. 2.6 SS-EC scaled model prediction (lines) of the 2x100  $\mu$ m PHEMT measured behaviour (circles). Sparameter in the frequency range [0.5 – 50 GHz] at V<sub>GS</sub> = -0.5 V, V<sub>DS</sub> = 5 V.

The SS-EC scaled models predictions are shown in Fig.2.5 and Fig.2.6. These experimental results point out that the scaled models are inaccurate also at relatively low frequencies. This suggests that not only the conventional scaling rules (2.1) are inaccurate, but also that conventional

topologies adopted for the extrinsic parasitic networks offer a poor link between technological process parameters and the corresponding device electrical response.

This call for the definition of completely empirical and process-dependent scaling rules, based on the evaluation of the variation of the extrinsic elements with the dimension of the device [2]-[5], through very complicate procedures, even in conjunction with more complicate lumped networks [4], [5].

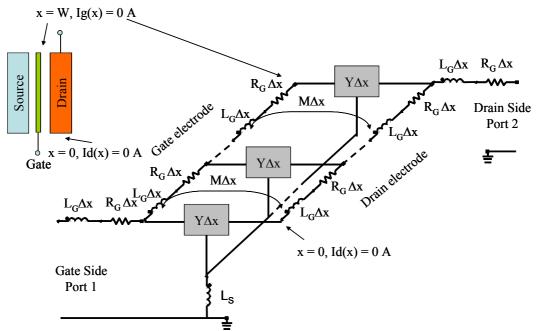

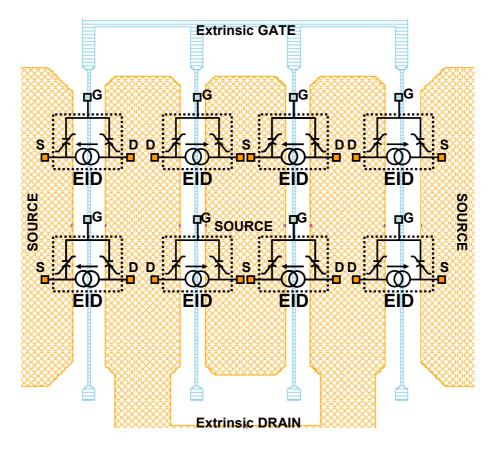

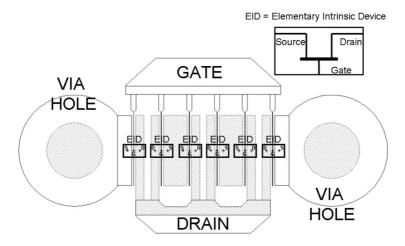

On the other hand, the solution is the use of purely distributed models [6]-[15], which maintain the link between the device geometrical parameters (such as number and width of fingers) by taking into account the propagation effects along and transversely the device fingers.

### 2.3 Lumped Topologies and Empirical Scaling Rules

In 1997 S. W. Chen *et al.* [2] report an approach for constructing scalable small-signal models for interdigitated power PHEMTs. The SS-EC model is defined by the topology of Fig.2.2 for the extrinsic parasitic network and the 7 element EC of Fig.2.3 for the intrinsic device. By using Dambrine's cold-FET direct extraction, the values of the equivalent circuit parameters (ECPs) have been extracted for a typical class-A operation bias condition, for five devices having different peripheries. By considering the extracted ECP values for the different peripheries, scaling rules for extrinsic components were found, and here briefly recalled:

$$(L_x)^{sc} = (L_x)^{ref}$$

, where  $x = G, D, S$  (2.2a)

$$\left(C_{X}\right)^{sc} = \left(C_{X}\right)^{ref} \frac{N^{sc}}{N^{ref}} \cdot \left(\frac{S_{cpw}^{ref}}{S_{cpw}^{sc}}\right)^{0.38}, \text{ where } x = PG, PD$$

(2.2b)

$$\left( \mathbf{R}_{G} \right)^{sc} = \left( \mathbf{R}_{G} \right)^{ref} \cdot \frac{\mathbf{W}^{ref}}{\mathbf{W}^{sc}} \cdot \frac{\mathbf{L}_{g}^{sc}}{\mathbf{L}_{g}^{ref}}$$

$$\left( \mathbf{R}_{D} \right)^{sc} = \left( \mathbf{R}_{D} \right)^{ref} \cdot \frac{\mathbf{W}^{ref}}{\mathbf{W}^{sc}} ,$$

$$\left( \mathbf{R}_{S} \right)^{sc} = \left( \mathbf{R}_{S} \right)^{ref} \cdot \frac{\mathbf{W}^{ref}}{\mathbf{W}^{sc}} ,$$

$$(2.2c)$$

where the subscripts 'sc' and 'ref' mean "scaled device" and "reference device" respectively. N, W,  $L_g$  are the number of gate fingers, the width of gate finger and the length of gate finger respectively, while  $S_{cpw}$  is the spacing distance of the inner coplanar waveguide transmission line.

After taking a further look at the scaling rules (2.2) they are very similar to conventional rules (2.1). Considering the experimental results shown in [2] the proposed rules provide an improvement

in accuracy, specially on the S11 parameter prediction, but the overall predictions are still inaccurate at higher frequencies. Furthermore the empirical rule (2.2b) appears to be process-dependent at it must be reviewed when changing the technology.

The major drawback of approach [2] is the great amount of time required for characterization phase. In fact the same Cold FET measurements have to be carried out on different device sizes prior to derive the empirical scaling rules.

In 1997 Cojocaru and Brazil [3] addressed the issue of scalability in equivalent circuit-based models for FET's, emphasizing for the first time the particularly difficult problems associated with the scalability of DC/AC dispersion phenomena. The study had been carried out on devices from both MESFET (0.5  $\mu$ m gate length) and PHEMT (0.25  $\mu$ m gate length) foundry processes, with total gate widths between 60 – 1200  $\mu$ m. They used a conventional topology for the extrinsic parasitic network and a slightly modified Cold FET direct extraction technique [3] as well as very simple linear scaling rules for the extrinsic ECPs. They put in evidence that the proper scaling of second order effects such as the DC/AC dispersion strongly influences the scalability of the model.

The shown experimental results point out that such a model scales very well with the periphery of the device, although the experimental validation is carried out only up to a relatively lowfrequencies for the considered mm-wave process.

In 2000 Wood and Root [4] proposed a Small-Signal Multi-Bias (SS-MB) scalable model for mm-wave applications. The extrinsic parameters are a slightly more complex network than the conventional network of Fig.2.2, in an attempt to model the multi-finger gate and drain manifolds. As shown in Fig.2.7, two additional capacitance components are added to account for the interaction between the gate-source and gate-drain interdigitated metallizations.

Fig. 2.7 The extrinsic parasitic network topology for the SS-MB scalable model proposed in [4].

An array of 0.25  $\mu$ m gate length InGaAs-channel PHEMTs, with total gate widths from 30 to 480  $\mu$ m and number of gate fingers from 2 to 12, was prepared and measured to determine the ECPs and their scaling rules [4].

A pinched-off gate condition was used to determine the extrinsic capacitances of the array of test FETs. First, the two-gate-finger devices were measured to estimate the variation with gate width of the gate capacitance and the drain-source capacitance. These relations were then used in the multi-finger devices to determine the influence of the manifold metallizations on the capacitances.

A new extraction method for the extrinsic Z-shell parameters had been proposed in [4]. It is based on optimizing the measured data over frequency. The drain-source voltage is set to zero, again eliminating the influence of the controlled current source from the equivalent circuit, and the gate bias is set to 0 V. Under these conditions, the intrinsic circuit of the FET can be reduced to a simple T-network in which the gate branch contains a parallel resistance/capacitance combination representing the gate-to-channel contact, and the source and drain branches are half the channel resistance, as shown in [4]. The value of the channel resistance was estimated by using a physical simulation to find the channel charge density at 0 V gate bias for the given device structures. After de-embedding the extrinsic capacitances, the branch impedance functions were fitted to the measured data using a rational function optimizer routine to determine the resistances and inductances. The complete extraction was accomplished in a two-pass process. In the first pass, *all* the extrinsic capacitance was subtracted from the measured data, and the optimizer produced initial values for the series resistances and inductances. In the second pass, the de-embedding process was

carried out in accordance with the equivalent circuit in Fig. 2.7. First, the outer capacitance shell was subtracted from the measured data, followed by the initial values of inductance, and then the second capacitance shell. At this point the optimizer was run to yield new values of branch inductance and resistance. The new value of inductance was added to the initial value to provide the final extrinsic inductance value. Two passes were considered sufficient.

That procedure had been carried out on some of the different devices of the array in order to derive the dependence on the gate width and number of finger of the ECPs. All the components in this equivalent circuit scale with gate width or number of fingers, or both according to the found empirical rules proposed in [4].

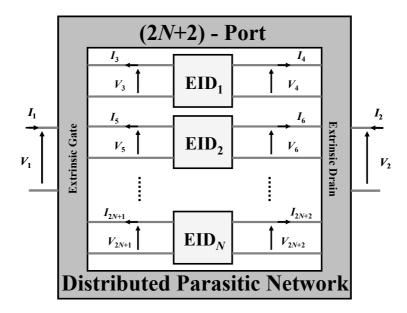

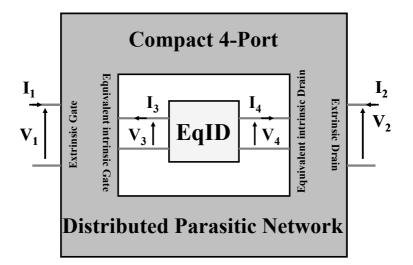

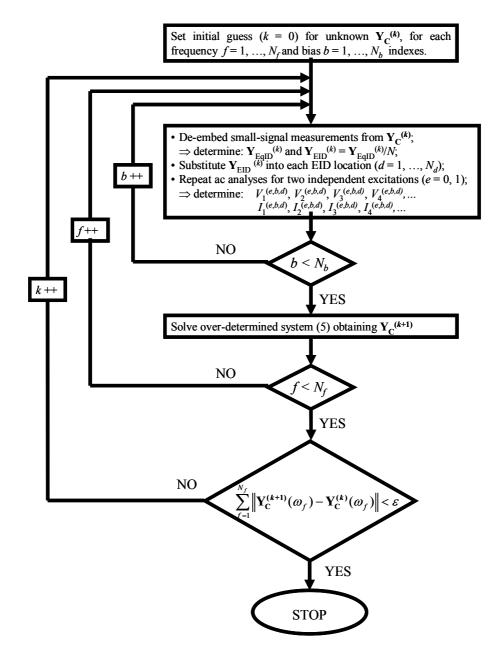

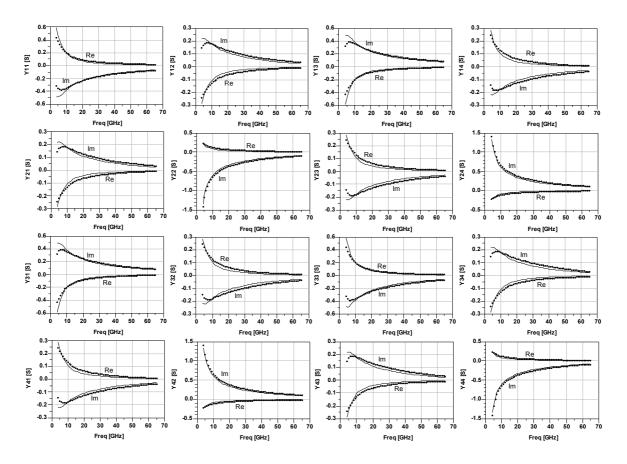

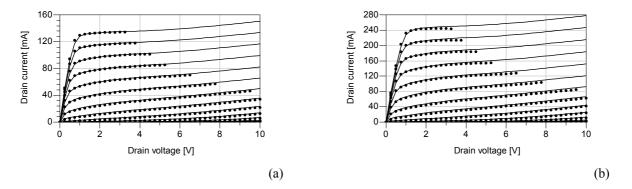

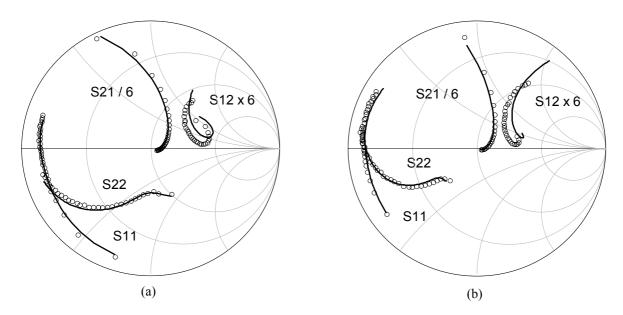

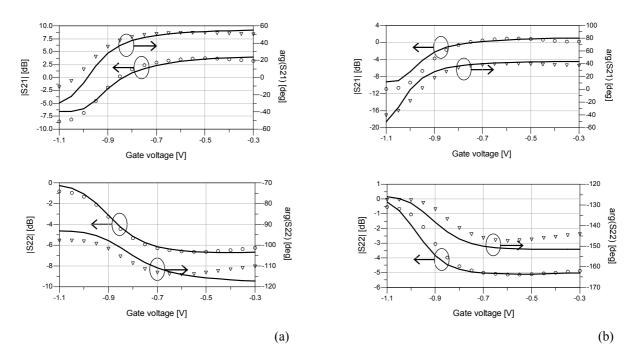

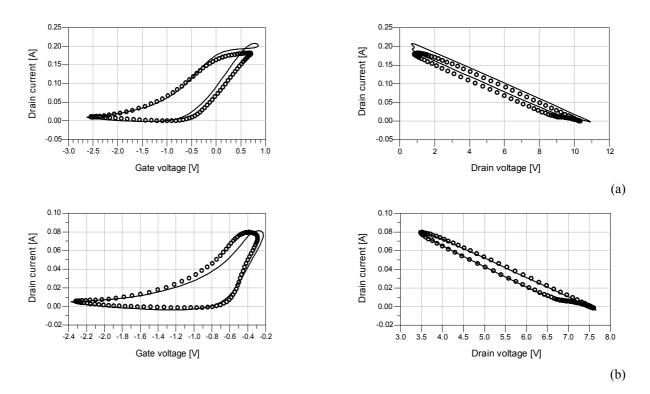

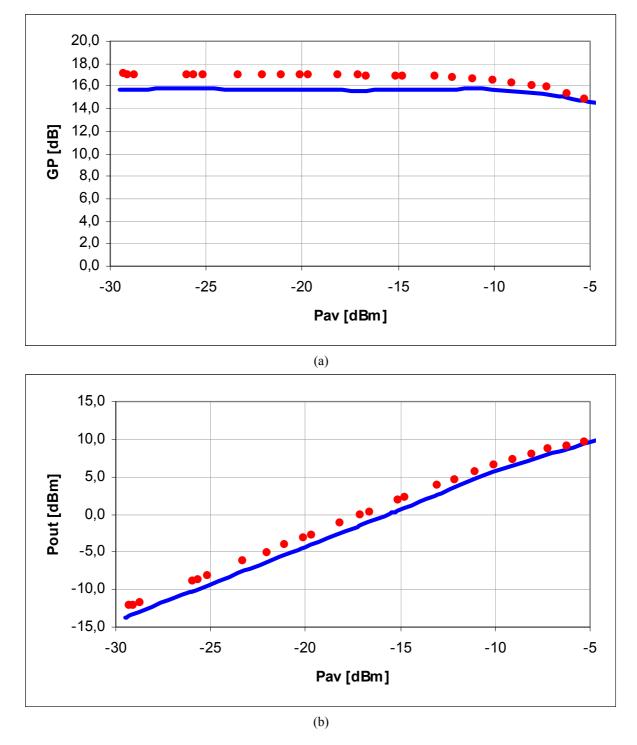

Although the SS-MB scalable model is very accurate up to millimetre-wave frequencies thank to the slight modification of extrinsic network of Fig.2.7, the approach [4] still needs a great amount of characterization data to find the empirical scaling rules. It also need the availability of two-gate-finger devices to derive the dependence of the capacitance shell on the gate width. Furthermore changing to another technological process, the proposed scaling rules could be different and de facto they must be newly evaluated.