## Alma Mater Studiorum – Università di Bologna

## DOTTORATO DI RICERCA IN

# INGEGNERIA ELETTRONICA, TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE

Ciclo XXX

Settore Concorsuale: 09/F1 - CAMPI ELETTROMAGNETICI

Settore Scientifico disciplinare: ING-INF/02 - CAMPI ELETTROMAGNETICI

# RF Circuits and Systems Design and Technologies Enabling IoT Applications

Presentata da: Massimo Del Prete

**Coordinatore Dottorato**

**Supervisore**

Prof. Alessandro Vanelli-Coralli

Prof.ssa Ing. Alessandra Costanzo

**Co-Supervisore**

Prof. Ing. Diego Masotti

Esame finale anno 2018

## Abstract

Internet of Things (IoT) is the paradigm used nowadays to summarize what is expected form the fourth industrial revolution (Industry 4.0) that is the connectivity of a huge number of "smart" objects disseminated in dissimilar scenarios. This concept is foreseen for practically any possible application domain: from home to transportation, from industry plants to health care, and for space monitoring. Long-term and self-sustainability of these smart thinks (people, objects, tools, etc.) becomes the most relevant aspect for the implementation of such a complex vision. In this framework, my PhD activities have been concentrated. The common goal is to investigate advanced solutions for energy-aware systems and circuits cooperating to enable the IoT paradigm. In particular, I have studied, designed and experimentally demonstrated quite a few novel solutions able to overcome some of the energy limitations existing in IoT.

The first project I have developed is an energy-autonomous power relay node at 2.45 GHz that is able to harvest energy from ambient-available or from dedicated RF sources and either use it for operating the node or for supplying power to other nodes. Both a hybrid and a monolithic implementation of the relay system has been implemented.

Then I was dedicated to the design of a system enabling Wake-Up Radio (WuR) operation at ultra-low power. The ambitious goal of WuR radios is to reduce the communication power consumption in Wireless Sensor Networks (WSN) and IoT. With this scope in mind, I have proposed and implemented a multi-band WuR architecture. The flexibility of using frequency diversity in WuR enables a more reliable and robust communication channel. From the source side, analytical and experimental studies have been carried out to define the optimum Power Optimized Waveform (POW) excitation to push the WuR sensitivity down to power as low as -65 dBm.

## Contents

| C  | onter  | nts                                               | iii                    |

|----|--------|---------------------------------------------------|------------------------|

| Li | ist of | Figures                                           | vii                    |

| Li | ist of | Tables                                            | $\mathbf{x}\mathbf{v}$ |

| A  | bbre   | viations                                          | vii                    |

| 1  | Inti   | roduction                                         | 1                      |

|    | 1.1    | Motivation                                        | 1                      |

|    | 1.2    | Research Objective                                | 8                      |

|    |        | 1.2.1 Radiative Wireless Power Transfer           | 8                      |

|    |        | 1.2.2 Non-Radiative Wireless Power Transfer       | 9                      |

|    |        | 1.2.3 Wake-Up Radio                               | 9                      |

|    | 1.3    | Thesis Structure                                  | 10                     |

| 2  | Aut    | tonomous Power Relay Node (APRN)                  | 13                     |

|    | 2.1    | System Overview                                   | 15                     |

|    | 2.2    | Oscillator Design and Results                     | 22                     |

|    | 2.3    | Self-Bias Rectifier: Design and Validation        | 31                     |

|    | 2.4    | Self-Bias Rectifier: Bias-Assisting Loop Approach | 36                     |

|    | 2.5    | System Experimental Validation                    | 41                     |

|    | 2.6    | Conclusion                                        | 46                     |

## ${\bf Contents}$

| 3            | $\mathbf{AP}$ | RN: Monolithic Implementation                           | <b>49</b> |

|--------------|---------------|---------------------------------------------------------|-----------|

|              | 3.1           | Technology                                              | 52        |

|              | 3.2           | System Overview                                         | 56        |

|              | 3.3           | MMIC Oscillator/Rectifier Design                        | 61        |

|              | 3.4           | SPDT Switch Design                                      | 68        |

|              | 3.5           | Bias-Assisting Loop Design                              | 75        |

|              | 3.6           | Experimental Results                                    | 82        |

|              | 3.7           | Conclusion                                              | 96        |

| 4            | Sim           | ultaneous Wireless Information and Power Transfer       |           |

|              | (SW           | VIPT)                                                   | 99        |

|              | 4.1           | Introduction                                            | .00       |

|              | 4.2           | Antenna Feeding for Simultaneous Operations             | .02       |

|              | 4.3           | Dual-band Printed Antenna and Far-Field Performance . 1 | .04       |

|              | 4.4           | Design of the Diplexer for Antenna Feeding              | .08       |

|              | 4.5           | Experimental Characterization                           | .11       |

|              | 4.6           | Conclusion                                              | .18       |

| 5            | Wal           | ke-Up Radio 1                                           | 19        |

|              | 5.1           | Introduction to Wake-Up Radios                          | .21       |

|              | 5.2           | Dual-Band Wake-Up Radio                                 | .25       |

|              | 5.3           | Power Optimized Waveform (POW)                          | .34       |

|              | 5.4           | Power Optimized Waveforms: Experimental Validation 1    | .43       |

|              | 5.5           | WuR Validation by Off-the-Shelf Components              | .49       |

|              | 5.6           | Conclusion                                              | .51       |

| $\mathbf{T}$ | nesis         | Conclusions 1                                           | 53        |

| Li           | st of         | Achievements 1                                          | 55        |

| Ac           | cknov         | wledgements 1                                           | 57        |

|              | Contents |

|--------------|----------|

|              |          |

| Bibliography | 157      |

# List of Figures

| 1.1 | Examples of IoT applications                                 | 2  |

|-----|--------------------------------------------------------------|----|

| 1.2 | Examples of commercial IoT devices                           | 3  |

| 1.3 | Schematic representation of a generic Energy Harvesting      |    |

|     | system                                                       | 5  |

| 1.4 | Techniques used to tackle the IoT energy limitations         | 6  |

| 2.1 | System representation of a bidirectional switchable en-      |    |

|     | ergy autonomous power relay node: switch in state 1 cor-     |    |

|     | responds to oscillator operating mode; switch in state $2$   |    |

|     | corresponds to rectifier operating mode                      | 18 |

| 2.2 | Link budget setup: (a) without relay node; (b) with relay    |    |

|     | node                                                         | 21 |

| 2.3 | Power budget versus distance analyzed without (blue curve)   |    |

|     | and with (red curve) relay node                              | 21 |

| 2.4 | GaAs FET transistor model                                    | 23 |

| 2.5 | Circuit schematic of the bidirectional energy autonomous     |    |

|     | power relay node with $2^{nd}$ harmonic termination          | 25 |

| 2.6 | Simulated transient behavior of the oscillator: (a) oscil-   |    |

|     | lator output voltage waveform; (b) gate voltage waveforms.   | 26 |

| 2.7 | Simulated transient behavior of the oscillator bias current. | 27 |

|     |                                                              |    |

| 2.8  | Measured and simulated oscillator dc-to-RF efficiency and                  |    |

|------|----------------------------------------------------------------------------|----|

|      | output power with respect to drain bias                                    | 28 |

| 2.9  | Measured and simulated oscillation frequency and simu-                     |    |

|      | lated self-bias gate voltage as a function of the input RF                 |    |

|      | power                                                                      | 29 |

| 2.10 | Measured oscillator output power spectrum                                  | 30 |

| 2.11 | Measured phase noise of the oscillator circuit in oscillator               |    |

|      | mode                                                                       | 30 |

| 2.12 | dc characteristics of the bilateral FET model, parameter-                  |    |

|      | ized by $V_{GS}$ for $V_{DS} > 0$ , and by $V_{GD}$ for $V_{DS} < 0$ , and |    |

|      | dynamic load lines in both operating modes                                 | 33 |

| 2.13 | Measured and simulated RF-to-dc conversion efficiency                      |    |

|      | (a) and output voltage (b) for the rectifier mode                          | 34 |

| 2.14 | Measured and simulated self-bias gate voltage as a func-                   |    |

|      | tion of the input RF power                                                 | 36 |

| 2.15 | Oscillator/rectifier system schematic with bias assisting                  |    |

|      | loop                                                                       | 37 |

| 2.16 | Measured and simulated self-bias gate voltage with bias-                   |    |

|      | assisting loop as a function of the input power                            | 38 |

| 2.17 | Measured and simulated RF-to-dc conversion efficiency                      |    |

|      | and output voltage with bias-assisting loop as a function                  |    |

|      | of the input power                                                         | 39 |

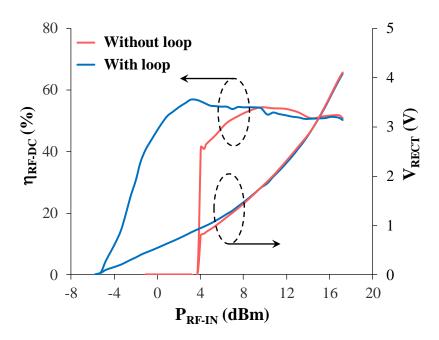

| 2.18 | Measured RF-to-dc conversion efficiency and output volt-                   |    |

|      | age, with and without bias-assisting loop, as a function                   |    |

|      | of the input power                                                         | 40 |

| 2.19 | Photo of the fabricated prototype of the bidirectional sys-                |    |

|      | tem with bias-assisting feedback loop                                      | 41 |

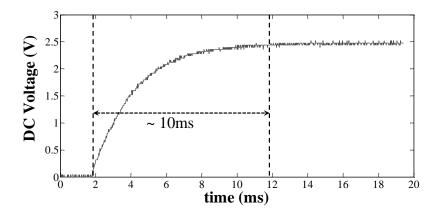

| 2.20 | Measured waveform of the voltage $(V_{DD})$ on the storage     |    |

|------|----------------------------------------------------------------|----|

|      | capacitance $(C_{ST})$ with the system in rectifier mode       | 42 |

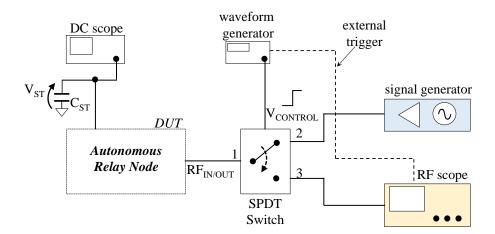

| 2.21 | Block diagram of the measurement set-up                        | 43 |

| 2.22 | Measured waveform of the voltage $(V_{DD})$ on the storage     |    |

|      | capacitance $(C_{ST})$ with the system in rectifier mode       | 44 |

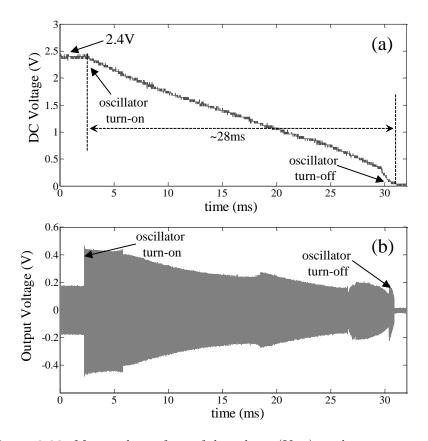

| 2.23 | Measured waveform of the voltage $(V_{DD})$ on the storage     |    |

|      | capacitance $(C_{ST})$ with the system in oscillator mode (a), |    |

|      | and transient oscillation waveform (b) of the prototype of     |    |

|      | Fig. 2.19(a)                                                   | 45 |

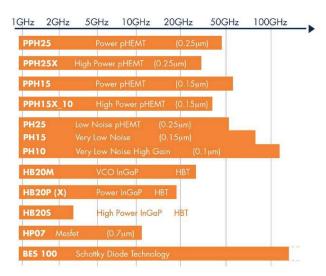

| 3.1  | UMS Foundry GaAs processes (source: www.ums-gaas.com).         | 53 |

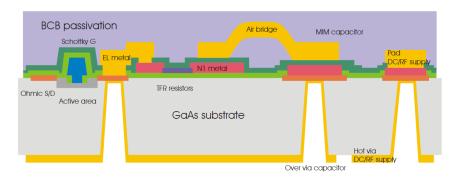

| 3.2  | Cross section view of PH10 process (source: UMS PH10-          |    |

|      | 10 Design Kit)                                                 | 54 |

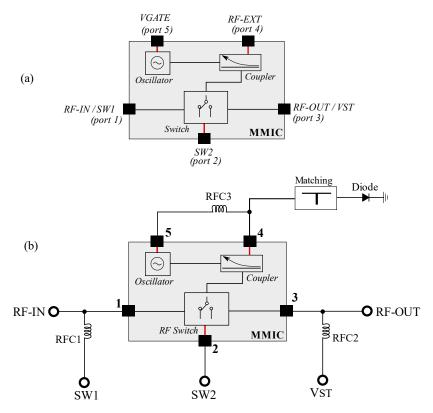

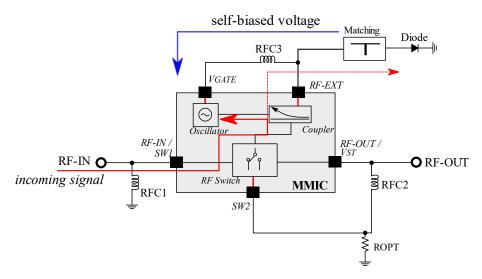

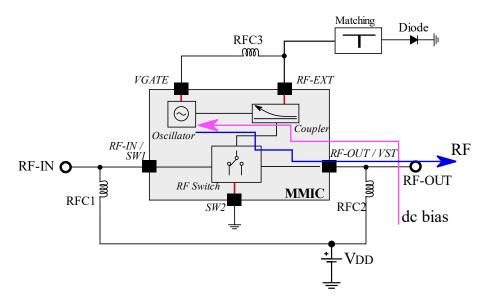

| 3.3  | System Architecture: (a) MMIC architecture, (b) com-           |    |

|      | plete system configuration                                     | 57 |

| 3.4  | System behavior in receiver mode                               | 59 |

| 3.5  | System behavior in transmitter mode                            | 60 |

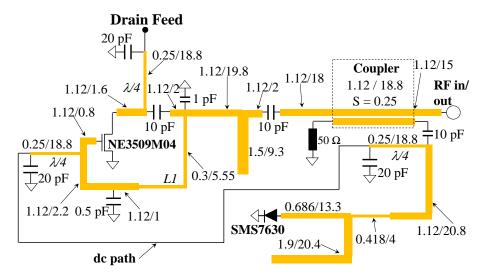

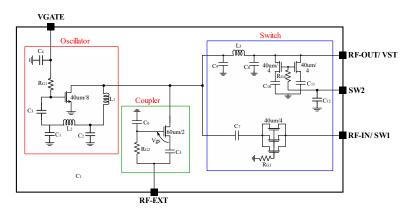

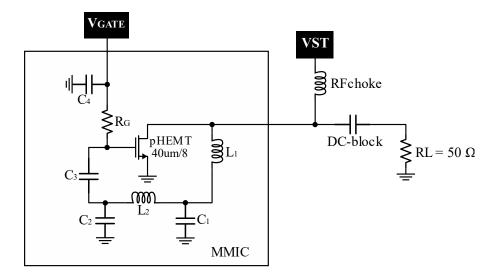

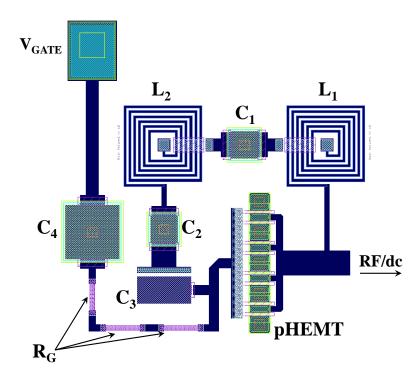

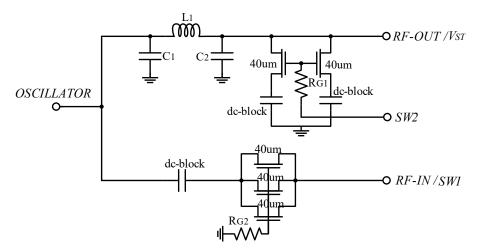

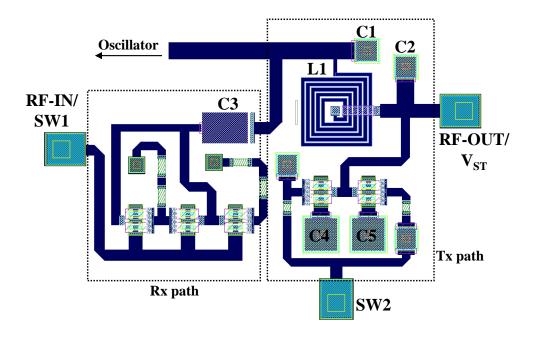

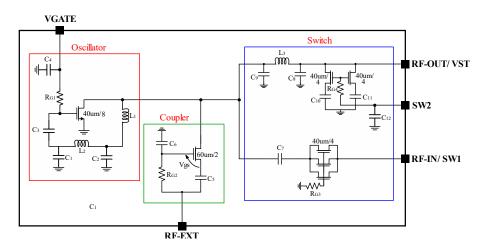

| 3.6  | Final schematic of the MMIC relay node                         | 61 |

| 3.7  | Oscillator architecture with external bias network             | 62 |

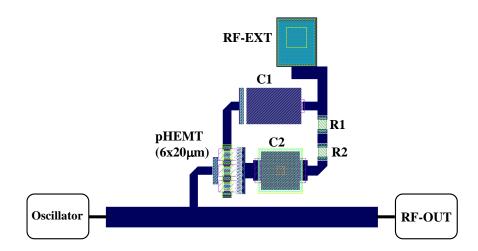

| 3.8  | Oscillator layout arrangements                                 | 64 |

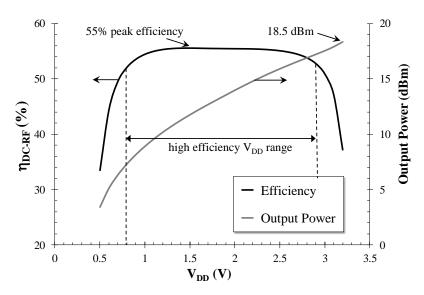

| 3.9  | Simulated oscillator dc-to-RF efficiency and output power      |    |

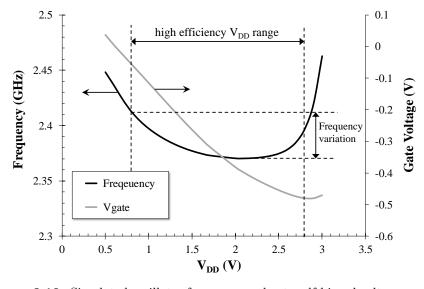

|      | versus drain voltage                                           | 65 |

| 3.10 | Simulated oscillator frequency and gate self-biased volt-      |    |

|      | age versus drain voltage                                       | 65 |

| 3.11 | Simulated rectifier RF-to-dc efficiency and output recti-      |    |

|      | fied voltage                                                   | 67 |

| 3.12 | Simulated gate self-biased voltage in the rectifier phase      | 67 |

| 3.13 | SPDT switch configurations: (a) standard approach (b)          |    |

|      | proposed approach                                              | 68 |

| 3.14 | Proposed switch behavior: (a) RX mode, (b) TX mode                                       | 70 |

|------|------------------------------------------------------------------------------------------|----|

| 3.15 | Final schematic of the proposed asymmetric switch. $\ .$                                 | 71 |

| 3.16 | Final layout of the asymmetric SPDT switch                                               | 73 |

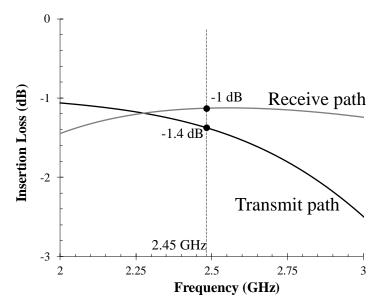

| 3.17 | Simulated Insertion loss of the switch in RX and TX mode.                                | 74 |

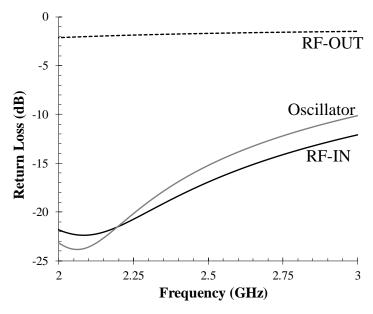

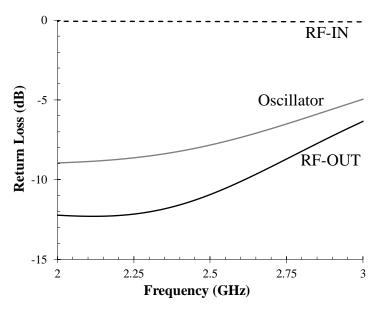

| 3.18 | Simulated Return loss at all ports of the switch for the                                 |    |

|      | relay in RX mode                                                                         | 74 |

| 3.19 | Simulated Return loss at all ports of the switch for the                                 |    |

|      | relay in TX mode                                                                         | 75 |

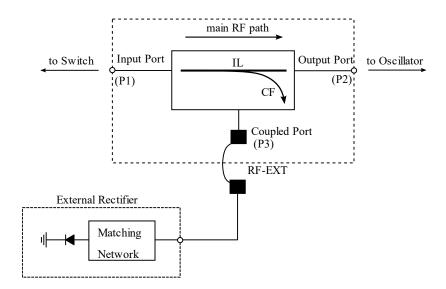

| 3.20 | $\label{thm:control} \mbox{Hybrid approach for the bias-assisting loop implementation.}$ | 77 |

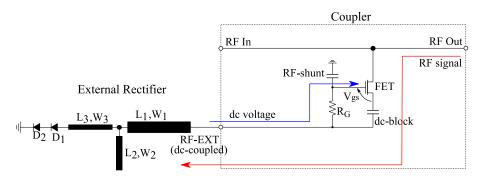

| 3.21 | Final schematic of the proposed hybrid bias-assisting loop.                              | 78 |

| 3.22 | Final layout of the coupler                                                              | 79 |

| 3.23 | Simulated coupling factor at 2.45 GHz and insertion loss                                 |    |

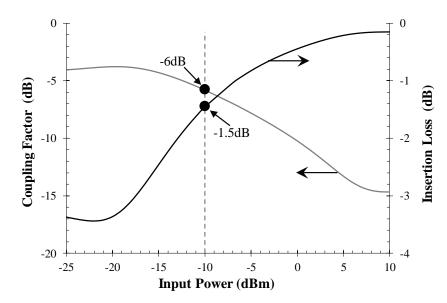

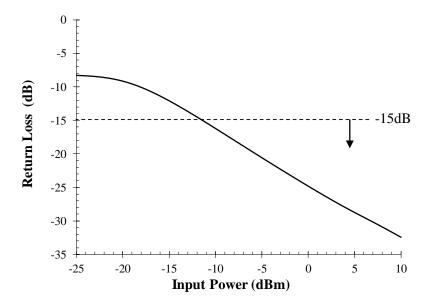

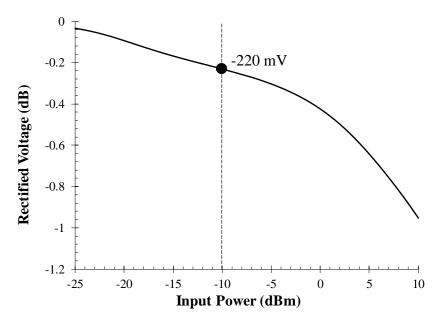

|      | for the coupler in Fig. 3.21, against RF input power                                     | 80 |

| 3.24 | Simulated return loss of the bias-assisting loop at 2.45                                 |    |

|      | GHz against RF input power                                                               | 80 |

| 3.25 | Simulated rectified dc-voltage by the external rectifier                                 |    |

|      | against input power                                                                      | 81 |

| 3.26 | Final MMIC schematic                                                                     | 82 |

| 3.27 | Master frame of the chip compatible with the UMS design                                  |    |

|      | rules                                                                                    | 84 |

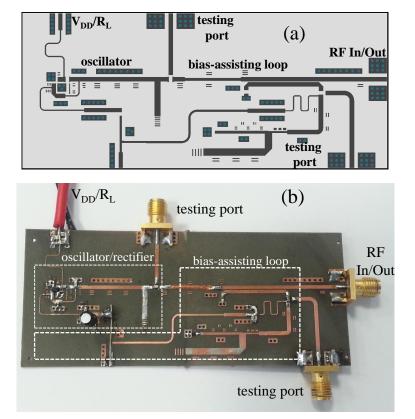

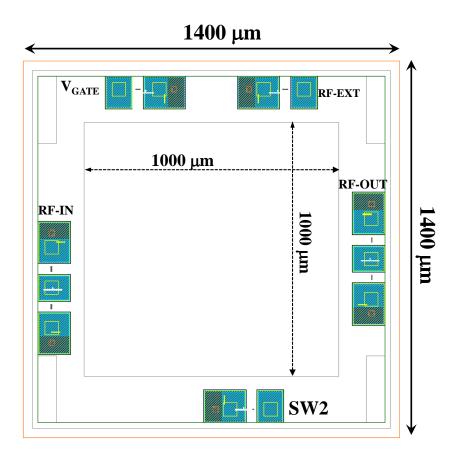

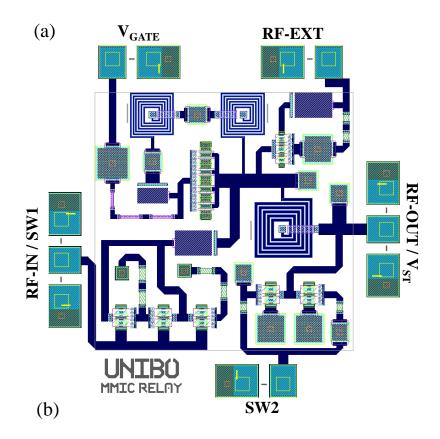

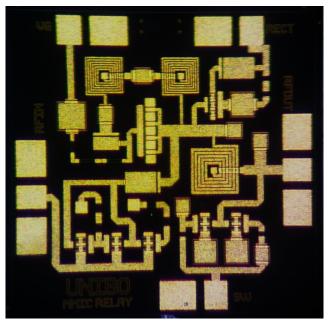

| 3.28 | Final MMIC layout: (a) CAD layout, (b) microscope photo.                                 | 85 |

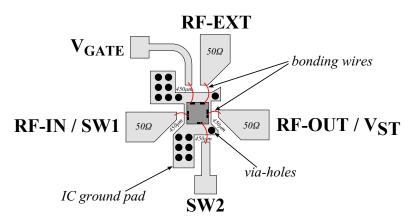

| 3.29 | Adopted MMIC PAD with corresponding bonding wires                                        | 87 |

| 3.30 | Schematic of the Test-Jig board                                                          | 88 |

| 3.31 | Picture of the Test-Jig board                                                            | 88 |

| 3.32 | Set-up used for characterizing the MMIC relay node in                                    |    |

|      | RX mode                                                                                  | 89 |

| 3.33 | Gate self-bias voltage generated by the bias-assisting loop.                             | 90 |

| 3.34 | Measured and simulated RF-to-dc conversion efficiency                 |

|------|-----------------------------------------------------------------------|

|      | (a) and output voltage (b) for the oscillator/rectifier cir-          |

|      | cuit operating in rectifier mode                                      |

| 3.35 | Set-up used for characterizing the MMIC relay node in                 |

|      | TX mode                                                               |

| 3.36 | Measured and simulated dc-to-RF conversion efficiency                 |

|      | (a) and output power (b) for the oscillator circuit operat-           |

|      | ing in oscillator mode, as a function of the drain bias. $\cdot$ . 94 |

| 3.37 | Simulated and Measured oscillator frequency variation                 |

|      | versus drain voltage                                                  |

| 4.1  | Example of application of two near-field PDA devices for              |

| 1.1  | recharging operation (source: www.taptrack.com) 101                   |

|      | recharging operation (source: www.taptrack.com) 101                   |

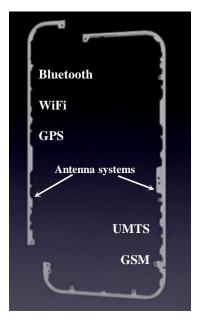

| 4.2  | Example of embedded antenna in modern mobile phones                   |

|      | (source: www.anandtech.com)                                           |

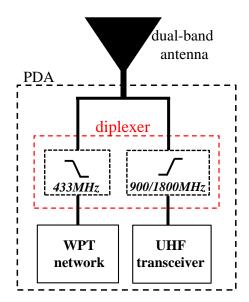

| 4.3  | Schematic block diagram of the PDAs sub-system with                   |

|      | the antenna for simultaneous far-field communication and              |

|      | near-field power transfer                                             |

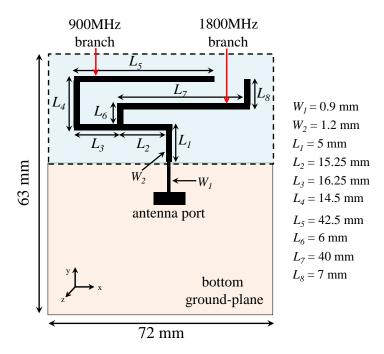

| 4.4  | Layout of the printed dual-band dipole antenna and cor-               |

|      | responding lengths                                                    |

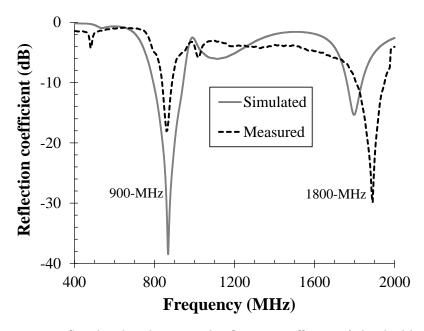

| 4.5  | Simulated and measured reflection coefficient of the dual-            |

|      | band dipole antenna                                                   |

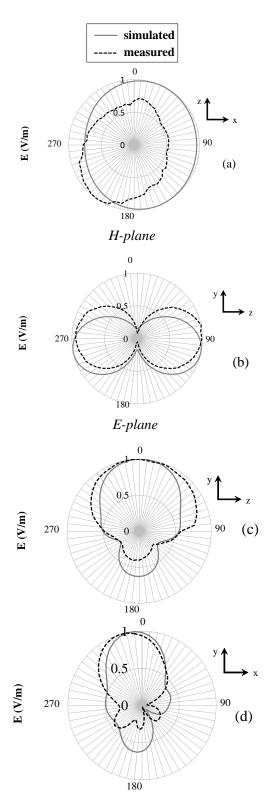

| 4.6  | Simulated and measured normalized E-field radiation pat-              |

|      | terns in H-plane and E-plane of the standalone printed                |

|      | antenna at 900 MHz ((a) and (b)) and 1800 MHz ((c)                    |

|      | and (d)) (linear scale)                                               |

|      |                                                                       |

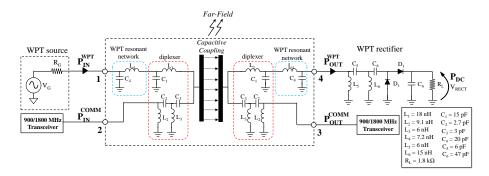

| 4.7  | Circuit schematic of the entire dual-mode sub-system of        |

|------|----------------------------------------------------------------|

|      | two faced PDAs: the three-port diplexers, the compo-           |

|      | nents for a resonant capacitive WPT link, and the rectifier    |

|      | network at the receiving side are put into evidence $109$      |

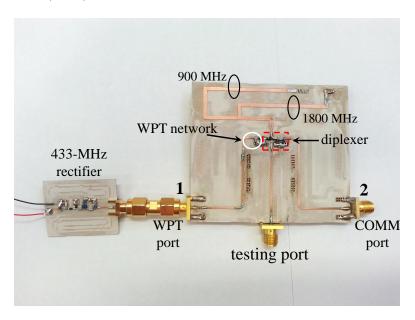

| 4.8  | Prototype of the dual-band planar antenna system ar-           |

|      | ranged for simultaneous data communication and energy          |

|      | transfer: the lumped-element diplexer, the resonant net-       |

|      | work and the rectifier are highlighted                         |

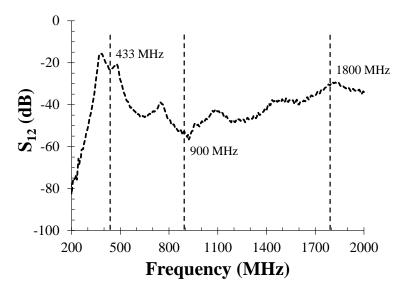

| 4.9  | Measured isolation between ports 1 and 2 of Fig. 4.7 for       |

|      | the standalone antenna                                         |

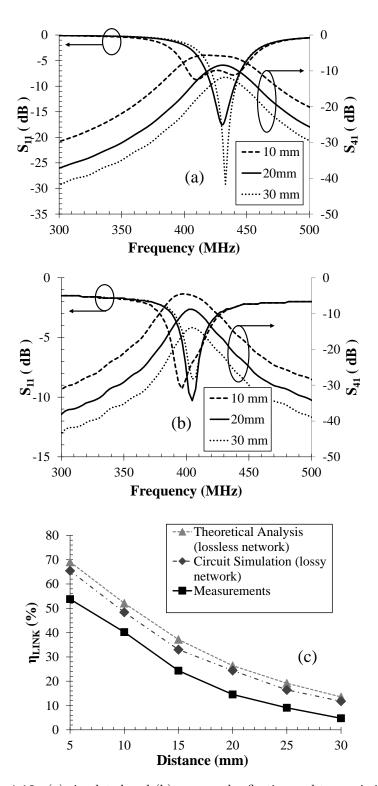

| 4.10 | (a) simulated and (b) measured reflection and transmis-        |

|      | sion coefficients for the two-faced antennas fed by the        |

|      | diplexer network (ports number as in Fig. 4.7). (c) pre-       |

|      | dicted (with and without losses) and measured reactive         |

|      | link efficiencies for variable antenna distances, calculated   |

|      | through (Eq. 4.2)                                              |

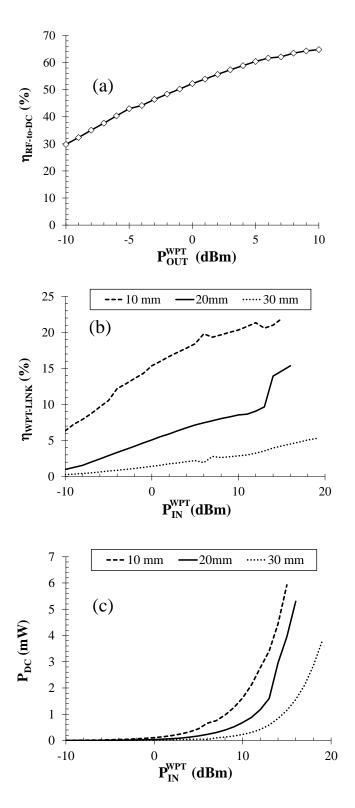

| 4.11 | Measured RF-to-dc efficiency of the rectifier (a), overall     |

|      | system efficiency (b), and dc output power (c) for variable    |

|      | link distances                                                 |

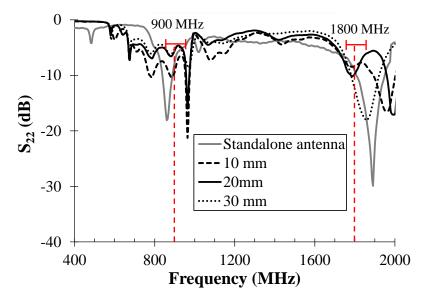

| 4.12 | Input reflection coefficient at port 2 of Fig. 4.7, with stan- |

|      | dalone antenna and with a faced identical one, at different    |

|      | distances                                                      |

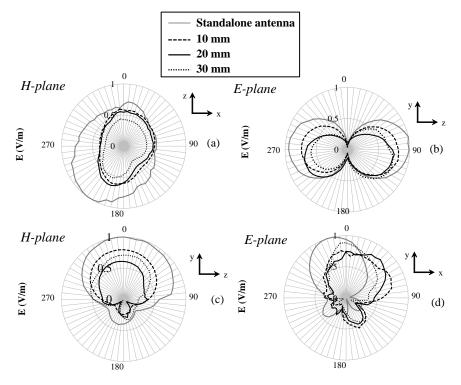

| 4.13 | Antenna radiation patterns in H- and E- plane at 900           |

|      | MHz ((a) and (b)) and 1800 MHz ((c) and (d)) (linear           |

|      | scale) for the standalone antenna and with a faced iden-       |

|      | tical one, at different distances                              |

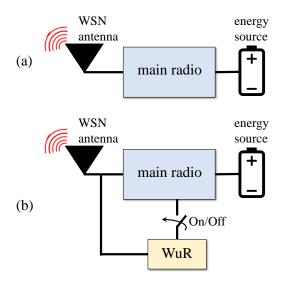

| 5.1  | Comparison of the architecture of a traditional WSN sys-       |

|      | tem (a) and the WuR-based one (b)                              |

|      |                                                                |

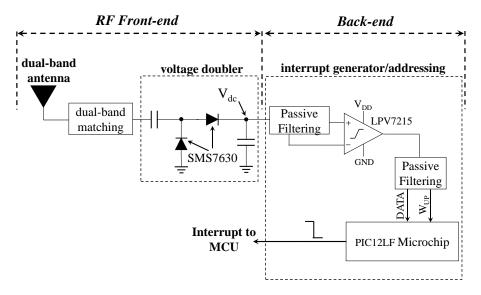

| 5.2  | System Architecture of dual-band Wake-up receiver with                         |

|------|--------------------------------------------------------------------------------|

|      | addressing capability                                                          |

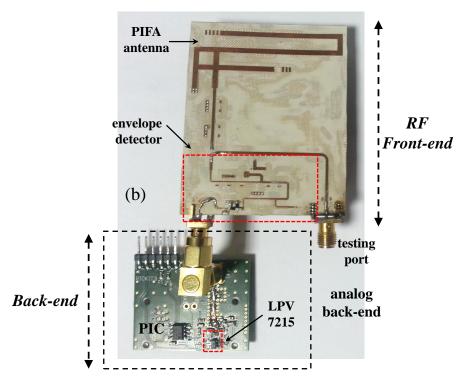

| 5.3  | Picture of the implemented WuR system with illustrated                         |

|      | the RF front-end and the analog back-end 127                                   |

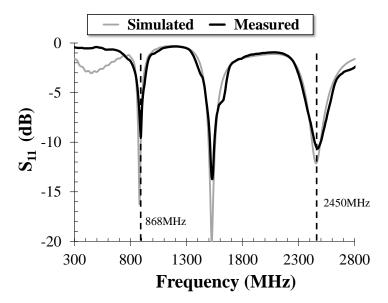

| 5.4  | Simulated and measured antenna reflection coefficient ver-                     |

|      | sus frequency                                                                  |

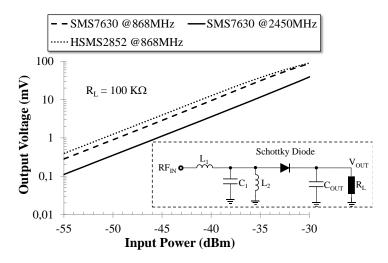

| 5.5  | Sensitivity analysis of two commercial diode with corre-                       |

|      | sponding circuit topology used for the simulations $128$                       |

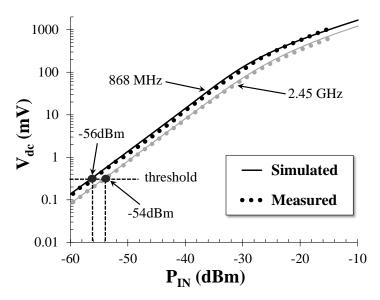

| 5.6  | Simulated and measured WuR detector output voltage                             |

|      | versus input power                                                             |

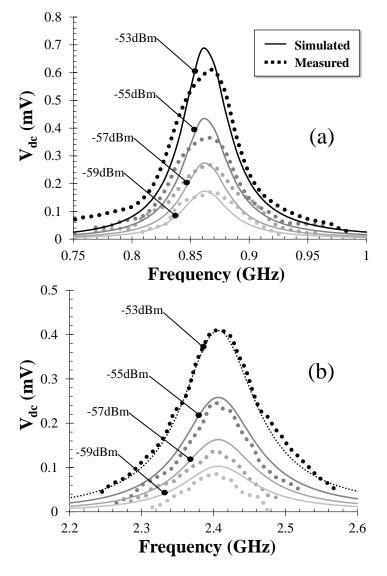

| 5.7  | Predicted and measured dispersive behavior of the detec-                       |

|      | tor output voltage for the two operating bands: (a) 868                        |

|      | MHz and (b) 2.45 GHz                                                           |

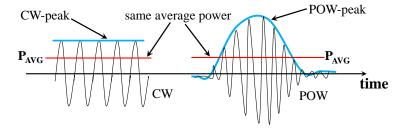

| 5.8  | Example of continuous wave and POW signals 135                                 |

| 5.9  | Simulated behavior of the detector output voltage over                         |

|      | the wide power range of interest, and corresponding be-                        |

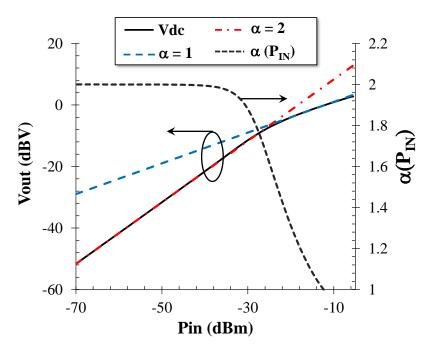

|      | havior of the exponential $\alpha\left(P_{IN}\right)$ : for power values from  |

|      | $-70~\mathrm{dBm}$ to $-35~\mathrm{dBm}$ a quadratic low is confirmed, then    |

|      | it starts decreasing and reaches the 1 value at about $-12$                    |

|      | dBm. The carrier frequency is 868 MHz                                          |

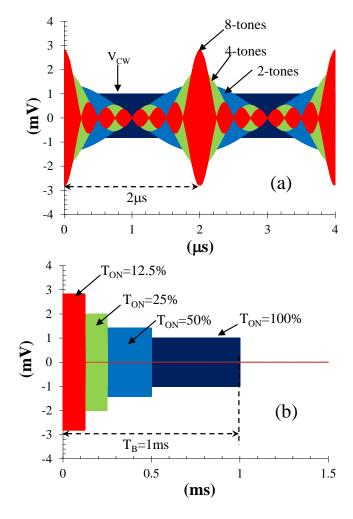

| 5.10 | (a) Multi-sine waveforms with different number of tones,                       |

|      | $500~\mathrm{kHz}$ spaced, with a period of 2 $\mu\mathrm{s},$ and (b) ICW ex- |

|      | citations with different 'ON' intervals. To compute these                      |

|      | excitations an average power per bit of $-50~\mathrm{dBm}$ and a               |

|      | WuR bit rate is 1 kHz are used                                                 |

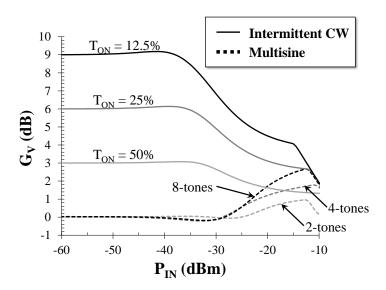

| 5.11 | Simulated results of the voltage gain $\mathcal{G}_V$ using muti-sine          |

|      | and ICW detector excitations                                                   |

## List of Figures

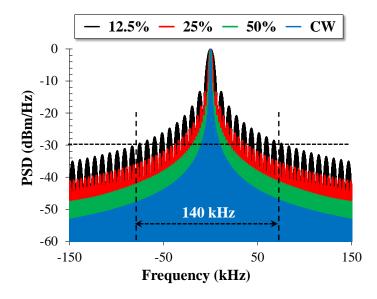

| 5.12 | 2 Simulated spectra of ICW signal with a periodic sequence    |

|------|---------------------------------------------------------------|

|      | of "1" and "0" bits with a bit period $(T_B)$ of 1 ms and for |

|      | different $T_{ON}$                                            |

| 5.13 | Block representation of the experimental set-up 144           |

| 5.14 | 4 Dual-band measured and predicted performance of the         |

|      | RF sub-system, in terms of detector output voltage: (a)       |

|      | for a carrier frequency of 868 MHz, (b) for a carrier fre-    |

|      | quency of 2.45 GHz                                            |

| 5.15 | 5 Dual-band measured and predicted results in terms of ob-    |

|      | tainable detector voltage gain for the selected WuR exci-     |

|      | tation waveforms: (a) for a carrier frequency of 868 MHz,     |

|      | (b) for a carrier frequency of 2.45 GHz 147                   |

| 5.16 | 3 Picture of the experimental set-up                          |

# List of Tables

| 3.1 | Microwave Processes pros Comparison                      | 50  |

|-----|----------------------------------------------------------|-----|

| 3.2 | Logic state command of the switch                        | 73  |

| 3.3 | List of values of the lumped component used in the MMIC. | 83  |

| 5.1 | Measured sensitivity and power consumption for the WuR   |     |

|     | in Fig. 5.2                                              | L33 |

| 5.2 | Summary of the WuR sensitivity with off-the-shelf com-   |     |

|     | ponents.                                                 | 151 |

## **Abbreviations**

APRN Autonomous Power Relay Node

CAD Computer-Aided Design

**CF** Coupling Factor

**CW** Continuous Wave

**EM** Electro-Magnetic

**EH** Energy Harvesting

**FET** Field-Effect Transistor

GaAs Gallium Arsenide

**GaN** Gallium Nitride

**GSM** Global System for Mobile Communication

**HB** Harmonic Balance

**HEMT** High Electron Mobility Transistor

IC Integrated Circuit

ICW Intermittent Continuous Wave

InGaP Indium Gallium Phosphide

**IoT** Internet of Things

**ISM** Industrial Scientific and Medical

MIC Microwave Integrated Circuit

MIM Metal-Insulator-Metal

MMIC Monolithic Microwave Integrated Circuit

**MoM** Method of Moments

#### Abbreviations

**NFC** Near-Field Communication

**N-LOS** Non-Line-of-Sight

**OOK** On-Off Keying

**OW** Optimized Waveform

PAPR Peak-to-Average Power Ratio

**PIFA** Planar Inverted-F Antennas

PDA Personal Digital Assistant

PDK Process Design Kit

**POW** Power Optimized Waveform

**pHEMT** pseudomorphic-HEMT

**RF** Radio Frequency

**RFC** Radio Frequency Choke

**RFID** Radio-Frequency IDentification

**RMS** Root Mean Square

RX Receiving

**SMD** Surface Mounting Device

**SPDT** Single Pole Double Throw

**SWIPT** Simultaneous Wireless Information and Power Transfer

TaN Tantalum Nitride

TiWSi Titanium-Tungsten -Silicon

**TRD** Time-Reversal Duality

TX Transmitting

**UHF** Ultra High Frequency

VNA Vector Network Analyzer

WuR Wake-Up Radio

WuRx Wake-Up Radio Receiver

**WPT** wireless Power Transfer

WSN Wireless Sensor Node

## Chapter 1

## Introduction

Internet of Things (IoT) is an emerging concept which is receiving a lot of interest from industries and researchers. This concept describes a structure where physical objects, each one equipped with a unique and identifiable communication system, are connected to the Internet and they can exchange information everywhere and in anytime. In this scenario long-term and self-sustainability operation of the devices are crucial points and, to date, they still are open items which strongly limit the IoT applications. In order to enable IoT applications even in a pervasive way, new systems and technologies needs to be developed with the objective of obtaining energy-aware devices able to maximize the longevity of the energy source (i.e. battery), or even able to self-sustain their operations. This work is divided in two parts: one dedicated to the optimization of power consumption in IoT devices, and the second one dedicated to the wireless power transfer between objects.

### 1.1 Motivation

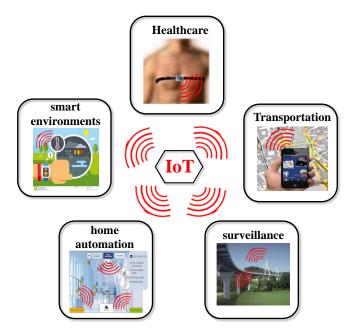

The IoT concept used in this work is constituted by an intelligent infrastructure of devices equipped with radio transceivers connected to the Internet. This way, it is possible to realize a pervasive distribution of Internet [1, 2] to any kind of physical object and this can potentially affect and improve many aspects of user's quality of life. Numerous applications of such a concept can be found such as home automation [3], healthcare [4], surveillance [5], transportation [6] and smart environments [7] (as summarized in Fig. 1.1). Starting from these necessities, many technological solutions have been developed and already available in the market.

$\begin{tabular}{ll} \textbf{Figure 1.1:} Examples of IoT applications. \\ \end{tabular}$

Fig. 1.2 shows some example of these devices that are becoming more and more diffused in our everyday life such as Activity Trackers, Smart Watches and Smart Phones. A typical architecture of IoT devices includes sensors, radio receivers, digital processors and, last but not least, an energy source (i.e. lithium batteries). The major limited factor in making IoT strongly pervasive is associated to the difficulties in supplying adequate energy to the objects to operate within the IoT structure for long time (from few months to years) without compromising the de-

vice's quality of service. For this reason, it becomes very important to improve the efficiency of such devices and extending the node's lifespan connected to the IoT network.

To solve this problem and improve the efficiency, different approaches have been investigated in literature such as using efficient communication protocols [8], or designing optimized embedded batteries for long-term duration [9], and adopting low-power consumption radio transceivers [10]. However, all these solutions are still not enough to guarantee a continuous and long term operation of the devices. In addition, the adoption of batteries can limit the real diffusion of the IoT concept due to i) their dimension which dominates the devices size, and ii) their need of maintenance. Moreover, batteries can discourage the use of wearable devices for medical applications.

Figure 1.2: Examples of commercial IoT devices.

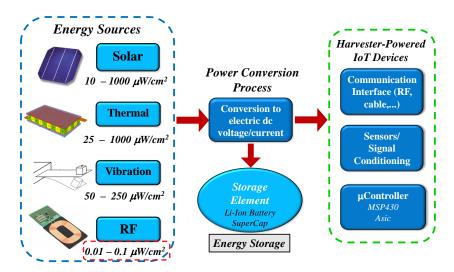

A recent technology trend able to provide a further energy source to the IoT nodes is the Energy Harvesting (EH) [11]. Practically, many energy sources are present in the environment such as Thermal, Solar, Vibration, and Radio Frequency. Scope of an energy harvesting system is to convert these sources into electric energy that can be used from the device itself (Fig. 1.3). The intensity of the aforementioned environmental sources depends on the presence of the corresponding energy source. As stated in [12], the more intense sources are solar  $(10-1000 \ \mu \text{W/cm}^2)$

and thermal (20–1000  $\mu\mathrm{W/cm^2}).$  Less intense sources are the vibration and (50–250  $\mu\mathrm{W/cm^2})$  and Radio Frequency (0.01–0.1  $\mu\mathrm{W/cm^2}).$  It can be noted the significant energy gap between RF sources with respect to the other ones .

Nevertheless, RF energy harvesting (RF-EH) is so far the most promising approach for the emerging IoT. In fact, RF-EH has a fundamental key property that other sources miss: it is wireless by definition. Thus, the energy is readily available in the form of electromagnetic (EM) waves and can be exploited everywhere and at any time.

Due to its importance, from some years researchers, and even the research group I am working with, are investigating solutions to develop intelligent and dedicated RF energy sources (also known as energy shower) able to provide on-demand the needed energy to the IoT nodes [13]. In this different application of the energy harvesting concept, the RF power is intentionally provided to the device and the available power levels are much higher than those stated in Fig. 2.3. A such approach is known as Wireless Power Transfer (WPT). The key benefit in using WPT systems is basically the knowledge of the source and receiver positions and their EM properties. This allows us to optimize the point-to-point link between a source and a receiver, maximizing the power that the node receives. As demonstrated in [14], intelligent beam-forming systems can be adopted to optimize the link in complex IoT scenarios. Of course, the transmissible power in WPT links is limited by the international regulations which defines the maximum transmitting power in standard communication systems.

Figure 1.3: Schematic representation of a generic Energy Harvesting system.

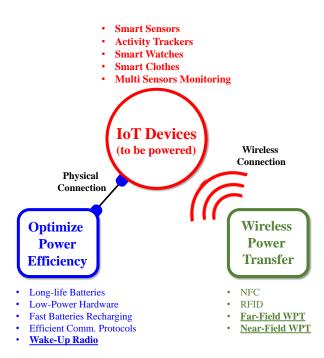

In summary, we can divide the approaches helping to enabling IoT applications in two groups (Fig. 1.4):

- 1. **Optimize Power Efficiency**: Represents the set of techniques aimed to increase the on-board battery life by reducing the power consumption.

- Wireless Power Transfer: Represents a further energy source for the device which can be requested on-demand and provided wirelessly.

Both these solutions can improve the longevity of the batteries. The first group belongs to some of the cited techniques [8, 9, 10]. However, an additional and promising approach is based on the Wake-up Radios (WuR). These radios are secondary radio transceiver (respect to the main radio, responsible for the data communications) implemented to monitor the channel condition so that the main radio can be turned off when there is no communication activity. This way, it is possible to strongly reduce the power consumption of the main radio, which, as well-known, represents the most power-hungry component in a communication node.

Figure 1.4: Techniques used to tackle the IoT energy limitations.

The second group provides a further approach to improve the system efficiency providing energy to the node. Potentially, such energy could also be enough to guarantee the self-sustainability of the device.

The possible implementations of wireless power transfer are Far-Field and Near-Field. The first one is based on electromagnetic wave and for this it is called radiative. The second one is based on inductive or capacitive coupling that can exist between closely-placed systems. In this case, a reactive magnetic or electric field is exploited for transferring the power and no radiation effects exist (non-radiative).

The aim of this work is to develop techniques, systems and circuits able to overcome the energy limitation in the IoT applications. The working areas of my PhD Thesis fall into the aforementioned groups depicted in Fig. 1.4. Specifically, the contributions to the IoT can be listed as follows:

- Radiative Wireless Power Transfer: Study and realization of a battery-less system able to accumulate and generate energy and operate as power relay node. Such a system allows passive devices to increase the operating range respect to the conventional approach.

- Non-Radiative Wireless Power Transfer: Realization of a WPT rechargeable system tailored for PDAs. In this work, the same antenna, designed for data communication purposes, is exploited for simultaneously realizing a WPT link.

- Wake-Up Radio: Development of techniques for increasing the flexibility and sensitivity of WuR radios. In particular, multi-band and Power Optimized Waveforms (POW) methods have been investigated for wake-up radios.

These points will be outlined in the next section where it will be described the scopes of the research activities made in this work.

Finally, this section concludes providing a summary of the main achievements obtained through three years in the Electromagnetic Group of the University of Bologna. As summarized in the section "achievements", during my activity I was able to present my work in a number of different scientific site, namely international conferences (IEEE MTT-S International Microwave Symposium and Wireless Power Transfer Conference) and journal (IEEE Transaction on Microwave Theory and Techniques and Institute of Engineering and Technology), resulting a total of 14 papers. As it will be described in the section dedicated to my PhD activities, I attended a number of international schools and student contests. In some of these contests, I also received awards. For instance, I was appointed as finalist in the student paper competition at IMS 2015, Phoenix. Then, I won the first prize in two student contests:

5<sup>th</sup> Meeting of the EU-COST IC1301 (2015), and at European School of Antennas (ESoA), 2015.

Due to the quantity of materials published in this work, and considering the success that they have received, it has been decided to rework part of the available materials in writing this Ph.D. Thesis.

## 1.2 Research Objective

#### 1.2.1 Radiative Wireless Power Transfer

In the radiative WPT field, this work concentrates on the investigation and development of a power relay node architecture. This relay node is a system which has the objective to receive and store energy from dedicated RF sources, and then using it either for specific operations of node itself or provide this energy to other devices closely-placed. The latter solution has the key benefit of overcoming the limitation due to the free space attenuation, such as the isotropic attenuation, multipath fading and non-line-of-sight (N-LOS) links.

This matter becomes even more important when passive systems operating at high frequency are involved. For instance, in RFID system, the most common tags operate at low frequency (868 MHz). At higher frequency (i.e. ISM bands: 2.45 GHz or 5.8 GHz), tags are at moment difficult to be diffused in the market because of the high attenuation. The aim of this work is to overcome such limitations introducing a power relay between reader and tags focusing on the 2.45 GHz band.

Two implementations of the relay node have been developed: the first based on a hybrid technology (MIC), and the second based on a monolithic technology (MMIC).

#### 1.2.2 Non-Radiative Wireless Power Transfer

Considering the non-radiative WPT technology, this work aims to studying and implementing an architecture, embeddable in the common mobile phone, able to realize a bidirectional power transfer between mobile devices in order to realize an on-demand batteries recharging. This way, any device can be wirelessly recharged or be recharged, everywhere when it is requested. To this scope, a near-field WPT approach is used, and the innovative idea is to create the link by exploiting the existing antennas in the PDAs. Doing so, it is not requested to add further antennas into the system. Obviously, the antenna system is not primarily dedicated to WPT and this limits the maximum obtainable efficiency, but represents a solution to realize a WPT link without any additional antenna.

Of course, special attention must be given to the effects that the WPT link introduces in the far-field properties of the existing antennas, in order not to affect their normal operation.

#### 1.2.3 Wake-Up Radio

The most energy-hungry part of IoT nodes is the radio transceiver due to its high power consumption. To enhance the communication efficiency, the main radio transceiver should be kept in sleep mode, most of the time, and be activated only when the related node is effectively interrogated. Among proposed energy-aware solutions, asynchronous-type transceivers with passive wake-up radio are very promising. Such RF systems have the role of continuously listening to the transmission medium and wake up the main radio upon detection of the incoming message. The aims of this work are:

a) Investigate solutions able to improve the robustness of the commu-

nication in WuR systems,

b) Improve the WuR sensitivity which determines the maximum communication distance.

### 1.3 Thesis Structure

To describe the different contributions introduced in the IoT field, this thesis is divided into two main parts. The first part will be dedicated to the systems developed in the WPT working area, and the second one will discuss the techniques introduced to improve the energy efficiency of the wireless sensor nodes (WSN). The thesis is organized as follows:

#### Part I: Wireless Power Transfer

- Chapter 2: First, it will be analyzed the power relay node architecture with the objective of demonstrating the advantages of this approach. The hybrid design and implementation of the relay node will be divided in sub-blocks and discussed. Then, it will be described the measurement set-up to experimentally validate the ability of the system to behave as a power relay node.

- Chapter 3: This chapter will demonstrate that a monolithic version of the relay node is attainable. After a brief overview about the adopted GaAs technology, the chapter will illustrate the entire general architecture of the MMIC and its sub-blocks. The design procedure of each sub-blocks will be deeply discussed. Finally, experimental results will be shown including the designed Test-Jig and measurement set-up.

- Chapter 4: It will be discussed the architecture of a WPT link established between two PDAs-like devices. Then, it will be illus-

trating the design procedure of the capacitive WPT link as well as the non-linear section. Finally, a detailed discussion on the measurement results will be provided.

## Part II: Wake-Up Radio

• Chapter 5: This chapter shows the results obtained from our work in the WuR systems. First, it will be introduced the multiband concept as a useful approach to obtain a frequency diversity. The designs procedure is then illustrated, and the experimental results shown. Thereafter, an approach based on power optimized waveforms (POW signals) is experimentally investigated to verify the effectiveness of such signals to improve the sensitivity of wake-up radios.

Finally, the thesis will conclude with a summary of the main results obtained during my PhD research.

## Chapter 2

# Autonomous Power Relay Node (APRN)

The work presented in this chapter was stimulated by a joint research issued by Prof. Alessandra Costanzo and Prof. Apostolos Georgiadis during a COST meeting. I was granted with a a Short Term Scientific Mission (STSM) from the COST Action IC1301 entitled "Wireless Power Transmission for Sustainable Electronics (WiPE)" to start the design of a circuit acting at the same time as a power harvesting and a power source module. The time spent abroad was 4 weeks from November  $1^{th}$ , 2014 to December  $1^{th}$ , 2014. The mission was carried out under the supervision of Prof. Apostolos Georgiadis and Ana Collado from Centre Tecnològic de Telecomunicacions de Catalunya (CTTC), in Barcelona, Spain.

The purpose of the mission was to develop an energy autonomous RFID system operating at 2.45 GHz (ISM band) based on a class-F oscillators/rectifier topology. Accordingly, this chapter will describe the development of a fully autonomous bi-directional circuit which starts in rectifying mode in order to harvest RF energy from intentional power

transmission, and after storing the necessary energy, is switched to oscillator mode to wirelessly power devices located in its proximity. The innovation of this works consists of an alternative approach for designing a 2.45 GHz class-F oscillator/rectifier, instead of a amplifier/rectifier approach, that in this way overcomes the need for external dc bias to operate, without degrading the performance of the two states (oscillator and rectifier). In fact, the circuit does not include a dedicated gate bias terminal, and thus eliminates the on-board batteries. This represents an important step with respect to solutions proposed in literature. In addition, the architecture developed and implemented in this chapter results to be a "true" autonomous bidirectional oscillator/rectifier system.

As far as the author knows, this is the only solution with these features available in literature.

The work done at CTTC was divided in tasks as follow:

- Task 1: Analysis and design of a class-F oscillator (1 week).

- Task 2: Optimization of the oscillator and rectifier as a unique system with high efficiency (2 weeks).

- Task 3: Test and debug of the system in both states to obtain the maximum efficiency (1 week).

This work was presented at the *International Microwave Symposium* (IMS) 2015 in Phoenix, Arizona [15]. On this occasion, the paper was also appointed as paper finalist in the framework of the Student context reaching a good score in the reviewer score. After this first version, a significantly extended work was published in the *IEEE Transactions* on *Microwave Theory and Techniques journal* [16]. In addition, from September 24<sup>th</sup> to 25<sup>th</sup> (2015), I attended at the 5th Meeting of the EU-COST IC1301 in Thessaloniki, Greece.

In such meeting, the relay node system was presented, and it won the first place of the student contest session as best poster.

This chapter is partially extracted by the published papers which contains a clear and complete base of the entire work. Thanks to the success of this project, the University of Bologna has decided to enroll myself in developing a monolithic version of the relay node by using a GaAs technology. Next chapter will be dedicated to give details on the MMIC version of the relay node.

The remainder of the chapter is organized as follows. Section 2.1 provides an overview of the system implementation and addresses the main issues to be solved for a successful autonomous power relay node operation. Section 2.2, 2.3 and 2.4 discuss the nonlinear design of the node: starting from the oscillator design, the rectifier topology is then derived; the two subsystem predicted performances are then experimentally validated. Section 2.5 describes the measurement set-up to validate experimentally the ability of the system to behave as an energy-autonomous power relay node. Section 2.6 drives the work conclusions.

## 2.1 System Overview

One of the issues in RF energy harvesting (RF-EH) solutions is the unknown and often variable RF link (rectenna location and polarization), which can threaten the effective use of energy-autonomous wireless systems. Several solutions have been pursued to reduce energy consumption [17, 18], and to enable high-efficiency harvesting capabilities that eliminate the need for battery replacement, thus reducing maintenance cost [19, 20]. In such scenarios, strategically located dedicated RF sources can help increase battery lifetime through wireless power delivery to sensors distributed in the source coverage area. A useful figure of merit

for far-filed wireless power transfer (WPT) links is the total RF-to-dc conversion efficiency, from the input of the transmitting antenna to the output of the receiver dc-dc converter [18]:

$$\eta_{TOT} = \eta_{RF-RF} \cdot \eta_{RF-DC} \cdot \eta_{DC-DC} = \frac{P_{RX}}{P_{TX}} \cdot \frac{P_{DC}}{P_{RX}} \cdot \frac{P_{ST}}{P_{DC}}$$

(2.1)

This consists of the product of three power ratios, based on the RF power available at the transmitting antenna input port  $(P_{TX})$ , the RF power received by the rectenna  $(P_{RX})$ , the dc power converted by the rectenna  $(P_{DC})$  and the dc power  $(P_{ST})$  stored in a dc-dc converter emulating the rectenna optimum load. The transmit-to-receive RF efficiency RF-RF can be maximized by design of both transmit and receive parts of the WPT system only in the case when dedicated (intentional) RF sources are available.

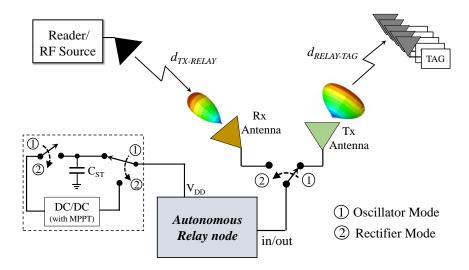

For those devices that are located in areas where these sources would be less efficient, the proposed power relay node can act as an energy repeater. Such a node, capable of bidirectional operation, should be able to harvest sufficient power for its own operation, in addition to providing power to surrounding devices, as illustrated in Fig. 2.1. This figure represents the architecture studied and developed in this work with the objective to extend the powering range of passive tags.

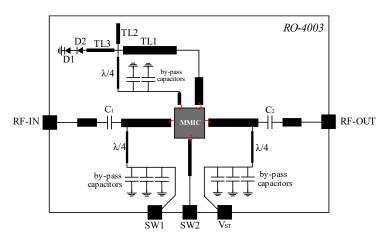

The novelty of this chapter is the alternative circuit solution able to ensure a bidirectional functionality without the need for external batteries, by using the energy stored during the rectifier operation mode. As it will be illustrated, the same nonlinear circuit is used to perform the two operations, where two switches are simultaneously driven to position 1 for oscillator operation, and to position 2 for rectifier operation.

This represents the system developed in this work with the objective to extend the powering range of remote passive tags.

This chapter presents a novel circuit solution with bidirectional functionality and without the need for external batteries, by using the energy stored during the rectifier operation mode. The same nonlinear circuit is used to perform the two operations, where two switches are simultaneously driven to position 1 for oscillator operation, and to position 2 for rectifier operation (Fig. 2.1).

Other bidirectional systems have been proposed in the literature by exploiting the time reversal duality (TRD) [21]. In [22], a 2.4 GHz IM-PATT diode based oscillating rectenna demonstrated 85% RF-to-dc efficiency as a rectifier and 1% dc-to-RF efficiency as an oscillator operating at 3 GHz. This publication highlights the challenges in maintaining a high efficiency in both operating modes as well as controlling the oscillation frequency and rectifier bandwidth. In [23], it is demonstrated that class-F RF power amplifiers exhibit comparable efficiencies and power levels when operated as self-synchronous rectifiers. In [24], this concept is extended to a 2.14 GHz 85% efficiency 10 W class-F-1 rectifier and a Fourier expansion-based theory for various classes of harmonicallyterminated rectifiers (C, F, F-1) is developed. In [25] the concept is extended to 10 GHz in a GaN MMIC, and in [26] to a two-stage GaN MMIC. A reconfigurable mW-level class-E oscillator/rectifier in the UHF band is presented in [27]. Excellent conversion efficiencies (up to 75%) are obtained for both operating modes.

However, the limitation common to all these proposed solutions is that they are strictly dependent on the device bias conditions that need be supplied by external dc batteries. In addition, they have limited power operating range and sensitivity when they operates as rectifier. This work aims to overcome all these limitations realizing a "true" efficient and autonomous bidirectional system.

**Figure 2.1:** System representation of a bidirectional switchable energy autonomous power relay node: switch in state 1 corresponds to oscillator operating mode; switch in state 2 corresponds to rectifier operating mode.

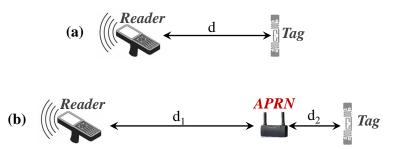

Before to start with the system design, it is necessary to verify the effectiveness of the power relay node approach in a typical RFID scenario. A link budget analysis is presented considering two cases illustrated in Fig. 2.2:

- (a) without relay node, as the conventional reader-tag scenario, and

- (b) with relay node placed between reader and tag.

The link budget analysis of these two scenarios will allow us to confirm that thanks to the relay node presence an improvement in the reading range of tags can be attained. There are several factors that may impact the performance of a radio system such as available and permitted output power, available bandwidth, receiver sensitivity, antenna gains, and environmental conditions.

Due to the nature of the comparison that here we want to illustrate, the following link conditions are adopted:

- Frequency of operations 2.45 GHz.

- The reader in case (a) and (b) is the same (same antenna gain, output power, etc.).

- Directional antenna for the reader is adopted (6 dBi).

- Omnidirectional antennas are considered for the tags (2 dBi).

- The transmitting power is selected in order to respect the maximum power provided by international regulations (EIRP = 2 W).

- The propagation link is unobstructed and it operated with line-ofsight (LOS) conditions without fading effects.

- The sensitivity of he tags is selected equal to -15 dBm (typical for 2.45 GHz tags).

Similarly, specifications must be given for the relay node system. As it will be illustrated, the relay node proposed in this chapter features a receiver simulated sensitivity as low as -8 dBm, and a maximum transmitting power in oscillator mode of about +14 dBm. For this reason, in this link analysis we have adopted the following relay properties:

- Receiving relay antenna can be directive because the reader's position is well-know (10 dBi is assumed).

- Directional antenna is also assumed for the transmitting antenna of the relay (6 dBi, typical value for patch antennas).

- The receiver sensitivity of the relay node in receiver mode is assumed to be -10 dBi.

- The output power of the relay node is 25 mW.

#### Chapter 2. Autonomous Power Relay Node (APRN)

Basically, the link budget consists in analyzing a RF link of the above defined cases by using the well-known Friis formula (note that, this formula is split in two paths for the relay node case):

• case (a)

$$P_{RX}(d) = P_{TX} \cdot G_{READER} \cdot G_{TAG} \cdot L_{PATH}(d)$$

(2.2)

• case (b)

$$P_{RX}(d_1, d_2) = \begin{cases} P_{TX} \cdot G_{READER} \cdot G_{RX-RELAY} \cdot L_{PATH}(d_1) \\ P_{TX} \cdot G_{TX-RELAY} \cdot G_{TAG} \cdot L_{PATH}(d_2) \end{cases}$$

(2.3)

#### Where:

- $P_{TX}$  =Reader transmitting power.

- $G_{READER}$  =Reader antenna Gain.

- $G_{TAG}$  =Tags antenna Gain.

- $G_{TX-RELAY}$  =Transmitting antenna Gain of the relay node.

- $G_{RX-RELAY}$  =Receiving antenna Gain of the of the relay node.

- $L_{PATH}$  =Propagation losses in function of the distance.

- $P_{RX}$  =Power received by the Tags.

Note that, the current analysis has the only objective of evaluating the activation distance of the tag. No considerations have been done in this work about the backscattering communication conditions.

Figure 2.2: Link budget setup: (a) without relay node; (b) with relay node.

However, thanks to the high sensitivity of the available readers (-90 to -120 dBm), the limitation in the operating distance is only related to the tags activation rather than the backscattering communication. Fig. 2.3 shows the maximum reachable distances with and without relay node. According to the results, an improvement of 2 meters (about 50%) is achieved by using a battery-less relay node.

Figure 2.3: Power budget versus distance analyzed without (blue curve) and with (red curve) relay node.

This improvement is reached by taking advantage from the possibility of the relay node to optimize the point-to-point RF link between the relay and the RF source, as well as the ability to regenerate a highpower CW tone at a distance far from the reader (about 4.3 meters in Fig. 2.3). Of course, in order to maximize the reading distance of the tags, the relay node position plays a crucial rule and it has to be carefully considered into the link optimization.

#### 2.2 Oscillator Design and Results

As explained before, the key features of the relay node are the self-sustainability and bidirectionality. These are obtained through a sequence of two optimized operations: first the system is set in rectifying mode to harvest the dc voltage needed to bias the oscillator, and such power can be intentionally provided by well-known RF sources. For this purpose, some recent research has provided the design rules for transmitting ad-hoc RF signals that increase the RF-to-dc conversion efficiency of the receiver [28, 29]. The dc energy can be stored in a super-capacitor or managed for subsequent use. Secondly, the system can switch into transmitting mode using the harvested dc power to start oscillation. In this case, the generated power is intentionally radiated toward the interested area where are placed tags. In this context, the core component in a relay node system is the oscillator. This components must be efficient, robust to  $V_{DD}$  variation and, as it will be illustrated, able to operate as rectifier without requiring complex biasing systems.

The main operating principle of the power relay node introduced in this work is the gate self-biasing of the MESFET [30]. By exploiting this feature, the oscillation start-up and rectifier operations can be accomplished with no need for dc biases. For this purpose, a medium power HEMT with weakly negative threshold voltage is chosen, which allow the device to start its operation from floating gate conditions in both

transmit and power-receive modes. This is done by using the same device and, most important, with the same conversion efficiency. In order to provide a clear description of the design procedure to be followed, it is introduced first the design of the self-biased oscillator, followed by the design of the self-biased rectifier obtained by using the time reversal duality (TRD) principle.

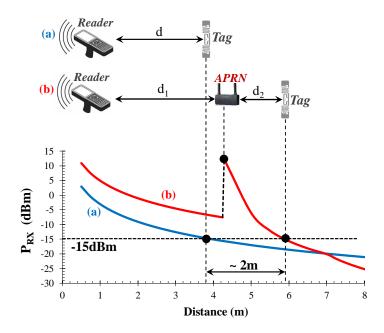

In order to understand the gate self-biasing mechanism, the HEMT transistor model is now analyzed. Fig. 2.4 shows the intrinsic GaAs FET models, including off-chip linear parasitic elements. It is a network composed of a voltage-controlled drain-source current source  $I_{DS}$  ( $V_{GS}$ ,  $V_{DS}$ ), a voltage-dependent gate-source capacitance  $C_{SG}$  ( $V_{GS}$ ) and a Schottky barrier diode gate-source current  $I_{GS}$  ( $V_{GS}$ ).

Figure 2.4: GaAs FET transistor model.

A source-grounded GaAs transistor with the gate terminal kept open in a dc manner (Fig. 2.4) can be self-biased without any external intervention. This can be explained with reference to the nonlinear FET model: as oscillation starts, the gate is floating and the RF signal flows into the gate-source junction through the feed-back drain-gate capacitance  $C_{GD}$ . Due to the Schottky-barrier rectifying property of the gate

#### Chapter 2. Autonomous Power Relay Node (APRN)

junction, the RF gate-source voltage generates a dc gate current and the gate capacitance is charged to a negative voltage, thus obtaining a self-biased transistor. By using the self-bias mode operation, it is possible to build a GaAs oscillator, operable with a single positive dc bias voltage source. In addition, as it will be seen in the next section, the self-bias process is also valid in rectifier mode.

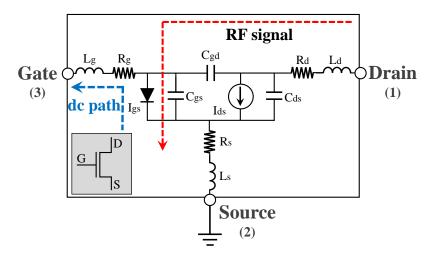

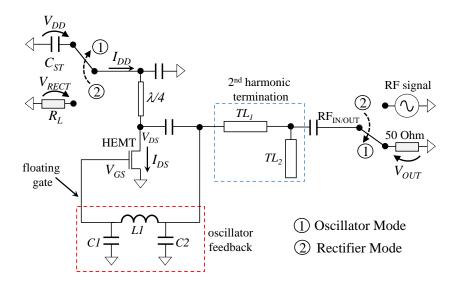

Once decided the biasing mechanism of the active device, an accurate study about the architecture of the oscillator has been done and Fig. 2.5 shows the final oscillator circuit topology (switches in State 1, which represents the oscillator configuration). The proposed architecture represents a 2.45 GHz Class-F oscillator with floating gate for the biasing. The architecture is composed of a Colpitts-like feedback, embedded in a linear sub-network that is optimized to ensure a class-F operation. In this work only the second harmonic has been terminated for obtaining a simple and compact network.

In order to maximize the dc-to-RF efficiency and to operate as oscillator, the drain impedance of the device must satisfy the Class-F harmonic termination condition at each harmonic [31], and simultaneously the feedback network must satisfy the oscillation conditions. For this reason, the HB optimization used in this work was envisioned to simultaneously meet the Barkhausen conditions and the maximum dc-to-RF oscillator conversion efficiency, in a suitable range of drain biases.

Ideally, the latter condition can be searched during the oscillator design by adding the following constraints to the ratio between the drain voltage and current harmonics to the design goals:

$$Z_{h}(V_{DDi}) = \frac{V_{DS,h}(V_{DDi})}{I_{DS,h}(V_{DDi})} = \begin{cases} < \varepsilon & \text{if } h \text{ is even} \\ > M & \text{if } h \text{ is odd} \end{cases}$$

$$V_{DDi} = V_{DD \min}, \dots, V_{DD \max}$$

$$(2.4)$$

where  $V_{DDi}$  is the drain bias spanning in the interval where oscillation condition is met,  $V_{DS,h}$  and  $I_{DS,h}$  are the drain voltage and current harmonic phasors,  $\varepsilon$  and M are low and high thresholds, respectively, h is the harmonic frequency index of the spectrum.

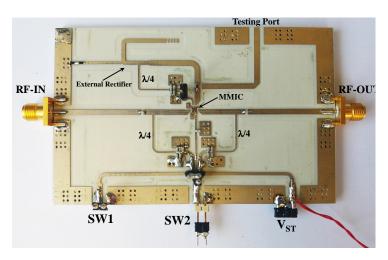

**Figure 2.5:** Circuit schematic of the bidirectional energy autonomous power relay node with  $2^{nd}$  harmonic termination.

In the optimization, the dc component plus 64 harmonics are used, but condition (Eq. 2.4) has been applied only for h = 2. The active device is a JFET Renesas NE3509M04 with a negative threshold voltage of -0.5 V. As can be noted, the advantage of a negative threshold is two-fold:

- the oscillation build-up is possible in the absence of a gate bias, that is, in floating-gate condition; and

- 2. the bias point for optimum conversion efficiency can be reached by gate self-biasing [30].

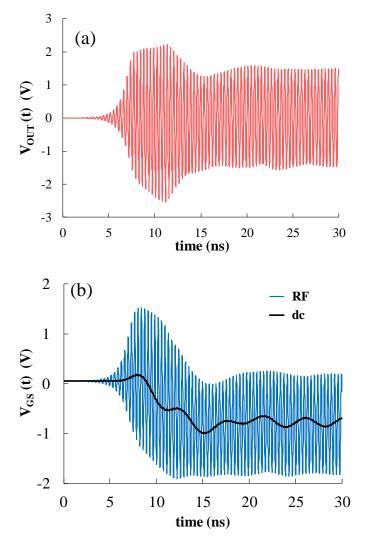

An analysis of the oscillator's transient has been carried out and the results of the oscillator start-up are summarized in Fig. 2.6. Initially, the drain and gate voltages are zero. During oscillation start-up, the self-bias mechanism drives the gate terminal to a negative voltage, the threshold voltage (or lower), thus allowing the oscillator to operate in a high-efficiency region with a reduced conduction angle.

Figure 2.6: Simulated transient behavior of the oscillator: (a) oscillator output voltage waveform; (b) gate voltage waveforms.

This is highlighted in the same figure where the transient behavior

of the dc components of the gate-to-source voltage is superimposed with the time-variable waveform. The shorter the time needed to reach the oscillator class-F steady-state regime, the lower the power dissipated during the oscillator start-up, and the longer the oscillator steady-state operation. This is a critical aspect for energy autonomy of the system, since the energy stored during rectifier operation supports the oscillator steady-state regime.

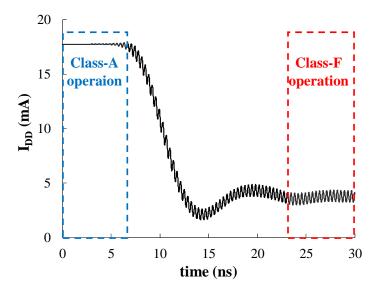

Fig. 2.7 shows the transient behavior of the drain bias current  $I_{DD}$ , representing the transistor transition from a high-loss Class-A to a low-loss Class-F operation. In small-signal condition during start-up, the circuit requires a lot of drain current; after oscillations build-up, the gate terminal is negatively self-biased, and the dc drain current is thus minimized. The dc power consumed to extinguish the oscillator transient is minimized in the present design process and could be further reduced by using a device with shorter channel length.

Figure 2.7: Simulated transient behavior of the oscillator bias current.

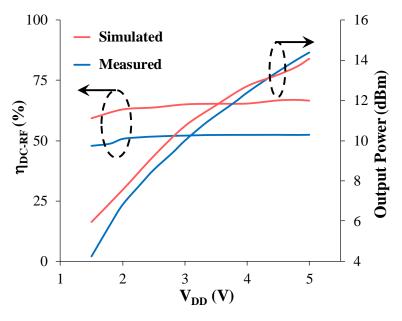

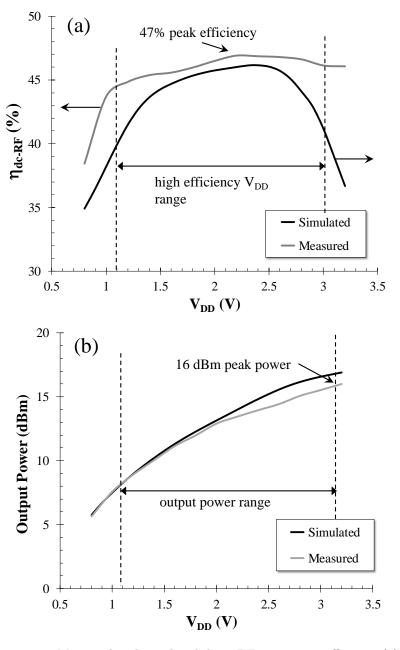

To verify by measurements the circuit in oscillator mode an external bias is used to provide drain polarization (switches of Fig. 2.5 are in State 1). More details on the prototype physical dimensions will be given in the next sections. The oscillator efficiency is over 50% for the entire drain supply range starting from 2 V. The oscillator mode reaches a maximum dc-to-RF conversion efficiency of 52.5% at 4.2 V drain bias voltage and an output power of +14 dBm (Fig. 2.8). Note that, the dc-to-RF efficiency has a very flat behavior over drain voltage, highlighting the robustness of the proposed system.

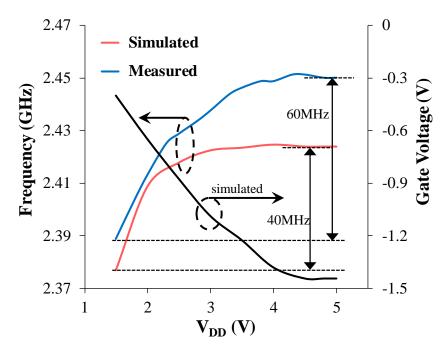

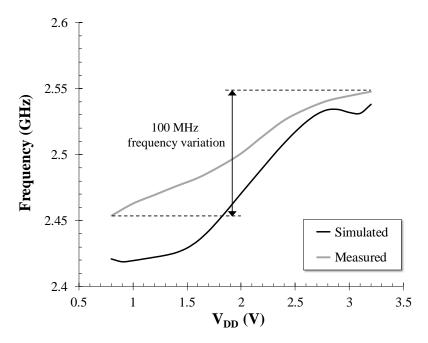

Fig. 2.9 shows the oscillation frequency and gate voltage variations with the drain bias. A measured frequency shift of 60 MHz has been obtained over the entire  $V_{DD}$  range. This is probably due to the inaccuracy of the FET model. In the measured dc-to-RF conversion efficiency and oscillator output power are compared to the simulated ones with varying drain supply voltage. The 15% overestimate in simulations is attributed to the HEMT nonlinear model accuracy.

Figure 2.8: Measured and simulated oscillator dc-to-RF efficiency and output power with respect to drain bias.

**Figure 2.9:** Measured and simulated oscillation frequency and simulated self-bias gate voltage as a function of the input RF power.

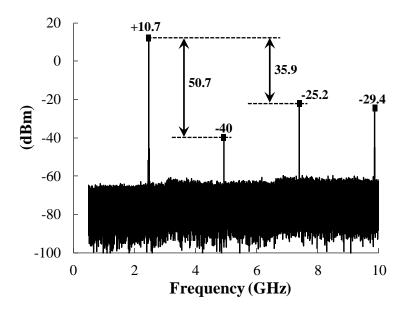

Fig. 2.10 shows the frequency spectrum of the oscillator, for a drain bias of 4.8 V. As expected, the second harmonic is about 50 dB below the other harmonics, confirming the class-F with second harmonic termination operation of the oscillator. The frequency spectrum is measured using an Agilent E4440A PSA spectrum analyzer with a resolution bandwidth of 3 MHz.

A further interesting measurement is the oscillator phase noise shown in Fig. 2.11. A phase noise of  $-80~\mathrm{dBc/Hz}$  at about 100 kHz from the carrier is measured using the Agilent E4448A PSA vector signal analyzer with span 3 MHz and resolution bandwidth of 1 kHz: the instrument noise floors at frequency offsets of 10 kHz, 100 kHz, and 1 MHz are  $-116~\mathrm{dBc/Hz}$ ,  $-122~\mathrm{dBc/Hz}$ , and  $-145~\mathrm{dBc/Hz}$ , respectively. For the phase noise measurements, the circuit was biased with a4.5 V battery in order to eliminate supply noise.

Figure 2.10: Measured oscillator output power spectrum.

Figure 2.11: Measured phase noise of the oscillator circuit in oscillator mode.

## 2.3 Self-Bias Rectifier: Design and Validation

The goal of this section is to describe the design and the simulated performances of the oscillator used as rectifier. By means of the time reversal duality (TRD) principle [23], rectifiers with high RF-to-dc conversion efficiency can be derived in a straightforward manner from the design of high conversion efficiency amplifier [32] and oscillator [33]. In fact, in the TRD concept, the waveforms of one network are time reversed with respect to their counterparts in the dual network. This principle is widely applicable throughout power electronics for designing system able to reverse the power flow. Thanks to this theory, a general design method for amplifiers can also be applied for rectifier design preserving the system efficiency in both the operation modes. However, state-of-the-art solutions usually are not intended for fully autonomous systems and they require for external batteries, to adjust the gate bias in rectifier mode, or adopt a different RF gate termination for the rectifier operation [23].

Here we show a procedure that eliminates the battery and gate termination tuning. Fig. 2.5 shows the external port arrangement of the system of Fig. 2.1 for rectifier mode (switches in State 2). In this case, the drain is disconnected from the dc bias path and loaded by  $R_L$ , which is optimized during the rectifier nonlinear design. The oscillator output port is now fed by the incoming RF signal at 2.45 GHz. Ideally, by means of the TRD principle, according to which the waveforms of a nonlinear device are time reversed versions of their counterparts in the dual device, oscillator and rectifier drain voltage and current are related by equations:

$$\begin{cases} V_{DS}^{OSC}(t) = V_{DS}^{RECT}(-t) \\ I_{DS}^{OSC}(t) = I_{DS}^{RECT}(-t) \end{cases}$$

$$(2.5)$$

thus preserving the intrinsic class-F behavior of the transistor. Consequently, proper device polarization needs to be ensured to provide conversion efficiency in rectifier mode, similar to the one obtained in oscillator mode (Fig. 2.8). However, to pursue the goal of fully energy-autonomous system, thus getting rid of external batteries, two main issues still need be solved:

- i) to reach self-synchronized conditions, between the gate and drain voltages, namely waveforms with opposite-phase;

- ii) to properly select the nonlinear device operating points for several possible RF input power levels, by exploiting the FET self-bias mechanism only.

Indeed, synchronous operation has demonstrated to ensure best rectifier conversion efficiency [33]. In this way a truly seamless switching between the two modes of operation can be performed. Optimization of the rectifier operating modes is performed with HB simulations with optimization goals on the RF-to-dc conversion efficiency. In the present case, an efficiency better than 60% for the optimization is specified as the design goal.

However, an important aspect in time reversal duality systems, is the accuracy of the nonlinear simulation of the FET model. For the rectifier and oscillator analysis, a nonlinear model capable of predicting device behavior in the first and third quadrant of the IV curves is needed, as in [34, 35]. In particular, nonlinear models for gate-source, gate-drain and drain-source capacitances are required to satisfy energy constraints

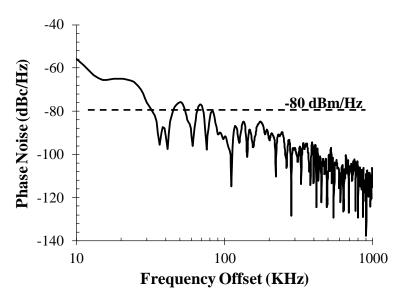

over all drain-source and gate-source voltage variations; the gate-source and gate-drain diodes interchange roles in the two modes of operation. A nonlinear device model from the manufacturer is implemented in Keysight ADS. An acceptable physical consistency with respect to the above mechanisms was tested for the selected device: in Fig. 2.12 the dc characteristics are plotted, parameterized by  $V_{GS}$  for  $V_{DS} > 0$ , and by  $V_{GD}$  for  $V_{DS} < 0$ , showing that the model is able to describe the device symmetry [34]. The dynamic load lines for both the operating modes are given in the same figure: the importance of the third quadrant of the I-V characteristics is evident from the rectifier-mode load line behavior. In fact, a nonlinear device model with accuracy and physical consistencies in the first as well as in the third quadrant of the I-V characteristics is mandatory to simulate the rectifier mode operation of the transistor.

**Figure 2.12:** dc characteristics of the bilateral FET model, parameterized by  $V_{GS}$  for  $V_{DS} > 0$ , and by  $V_{GD}$  for  $V_{DS} < 0$ , and dynamic load lines in both operating modes.

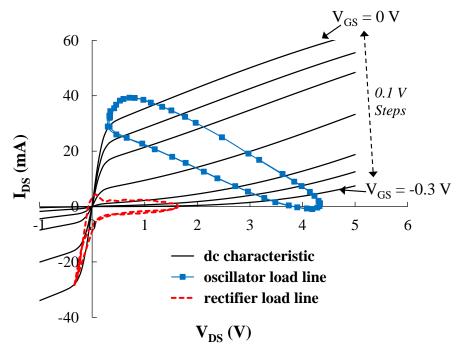

Thus, to meet the self-synchronization conditions [24, 25] and maximize the efficiency, a nonlinear optimization of the same circuit topology for the concurrent maximization of the rectifier performance is carried out. Of course, the load resistance  $R_L$ , represents the optimization variable and plays a crucial role in achieving the best rectifier conversion efficiency. An optimum value of about 680 Ohm is obtained by the optimization. Fig. 2.13 and Fig. 2.14 summarize the results of the nonlinear system optimization for the rectifier operation mode.

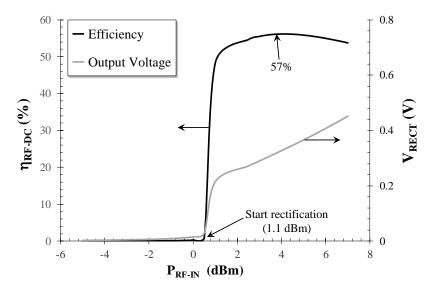

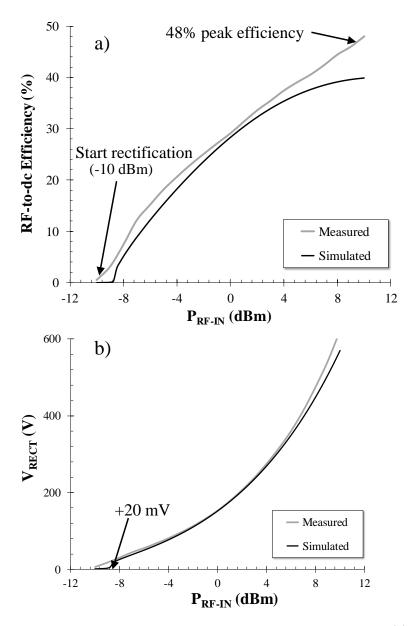

Figure 2.13: Measured and simulated RF-to-dc conversion efficiency (a) and output voltage (b) for the rectifier mode.

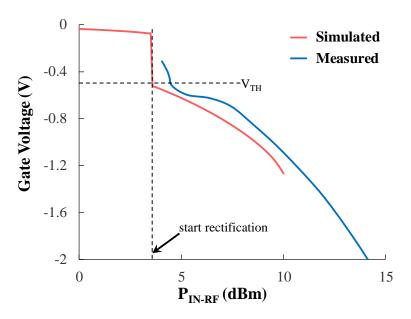

In Fig. 2.13(a) the simulated RF-to-dc efficiency is plotted. Fig. 2.13(b) shows the simulated output dc voltage, across the optimum dc load, resulting from the system nonlinear optimization. These plots predict that the circuit is able to operate with efficiency higher than 60% starting from about +3.8 dBm of input power. This performance is then preserved over a 12 dB RF input power range. From the same plot we get the corresponding dc voltage available at the rectifier output (up to 2 at 12 dBm).

The same figure shows the corresponding measured data: the circuit is able to operate with efficiency higher than 40% starting from input power as low as +4 dBm. This performance is preserved over a 14 dB range in input power. Starting from the floating gate condition  $(V_{GS} \cong 0)$ .

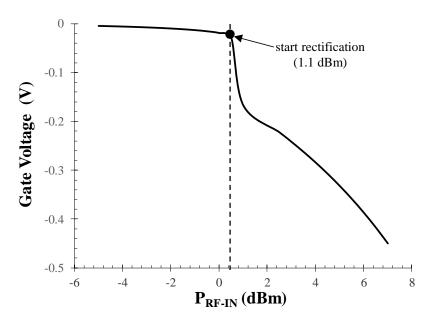

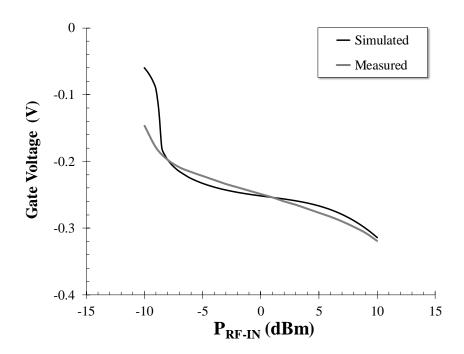

Fig. 2.14 shows the evolution of the dc gate voltage versus input RF power using the self-bias mechanism. At the lower interval of RF power levels,  $V_{GS}$  remains approximately zero; as the power increases, weak rectification is observed up to a selected value at which the dc gate voltage reaches a value lower than the transistor threshold voltage  $(V_{TH})$ . Increasing further the RF power drives the transistor more deeply in the depletion region, but this does not affect the efficiency performances of the rectifier.

Additionally, in Fig. 2.13 it is shown that the circuit operating in the rectifier mode exhibits hysteresis behavior versus input power. Starting from the minimum RF power levels (solid line), rectification is possible only over 4 dBm. For decreasing input power (dashed line), the measured rectifier operates down to +1.1 dBm. This further limit the input power ranges for which the circuit could rectify, since operating in the hysteresis zone between +1.1 dBm and +4 dBm is undesirable.

Of course, this limitation cannot be acceptable for a relay node system.

Thus, in this work we developed a different approach for increasing the sensitivity. Next section will show how we solve this problem by designing a network that acts as a bias-assisting loop in rectifier mode without affecting the oscillator mode.

**Figure 2.14:** Measured and simulated self-bias gate voltage as a function of the input RF power.

# 2.4 Self-Bias Rectifier: Bias-Assisting Loop Approach

The major drawback of using the TRD principle to implement oscillator/rectifier circuits is that, depending on the transistor threshold voltage, a minimum RF input power is needed to start rectifier operation. To overcome this limitation, a simple network based on a matched low-power diode in shunt configuration, is included to bias the gate when the intrinsic transistor mechanism is not active yet. In this way the rectifier sensitivity is extended to lower input power levels with an acceptable RF-to-dc conversion efficiency. The bias assisting loop is optimized to

operate at low input power levels when the self-bias mechanism is not sufficient.

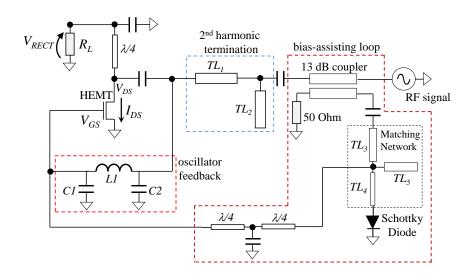

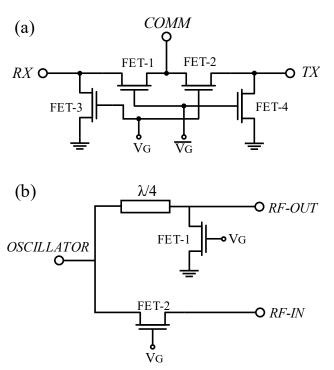

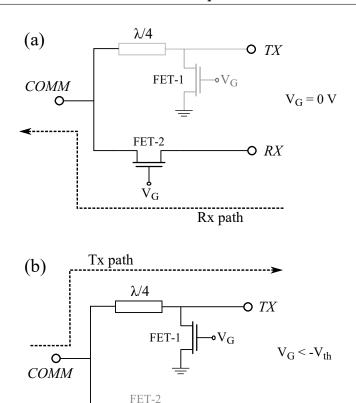

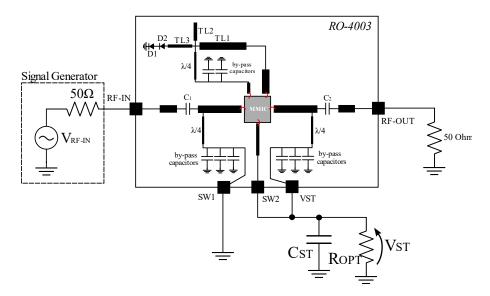

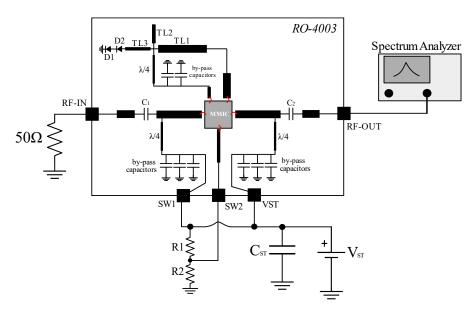

The loop is designed in such a way that it does not affect the oscillator mode of operation, while providing the minimum gate bias to start rectification. Fig. 2.15 shows the modified architecture of the oscillator/rectifier. The bias-assisting loop is connected to the rectifier input (oscillator output) by means of a microstrip coupler, which drives a sample of the incoming RF signal at 2.45 GHz to the diode through a suitably optimized stepped-impedance open-stub matching network.

Figure 2.15: Oscillator/rectifier system schematic with bias assisting loop.

A Schottky diode (Skyworks SMS7630-079) is chosen and is arranged in shunt configuration providing a negative dc voltage at the transistor gate port. The two quarter-wave lines in the assisting loop play the role of RF blocks, thus ensuring isolation between the Class-F oscillator and the bias-assisting loop. In addition, they provide the dc path for the Schottky diode and the transistor gate. Coupling and isolation coefficients of the coupler are designed to reach the best compromise between high isolation between oscillator and bias assisting loop (demanding high

coupler directivity) and minimum power to activate the diode (demanding low coupler directivity).

For the present design, a 13 dB coupling coefficient is chosen, resulting in a directivity of 10 dB and an insertion loss of 0.8 dB at 2.45 GHz. Such insertion loss generates a 5% RF-to-dc efficiency degradation, but the oscillator performance is completely preserved.

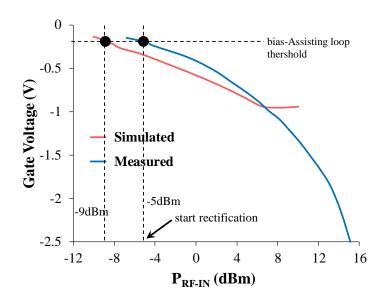

Fig. 2.16 and Fig. 2.17 show the final optimization results for the system of Fig. 2.15. In Fig. 2.16 the dc component of the gate voltage is plotted against input RF power: the minimum activation voltage of -0.3 V is now available at RF input power of -8 dBm.

**Figure 2.16:** Measured and simulated self-bias gate voltage with bias-assisting loop as a function of the input power.

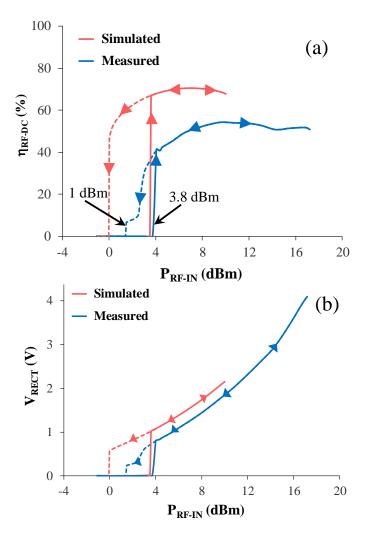

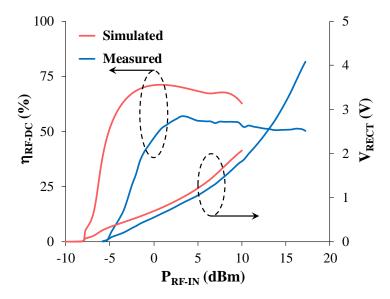

The corresponding simulated RF-to-dc conversion efficiency is shown in Fig. 2.17: an efficiency better than 60% is ensured for RF power levels ranging from -4 to +10 dBm. Note that, for simplicity the same load is used here for all input power levels. We expect possible improvement in efficiency when a proper dc-to-dc converter is designed to dynamically emulate the optimum load, for any possible RF input [20].

To experimentally characterize the circuit in rectifier mode, the drain bias is disconnected and an input RF signal at 2.45 GHz is fed into the RF port (switches in State 2, rectifier mode). The input power levels are varied from -6 dBm up to +18 dBm and the output dc voltage is measured across the output load  $R_L$ . Fig. 2.17 also shows the measured output voltage and RF-to-dc conversion efficiency as a function of input power. The same dc load, equal to the one obtained by circuit simulation, was used for these measurements.

**Figure 2.17:** Measured and simulated RF-to-dc conversion efficiency and output voltage with bias-assisting loop as a function of the input power.

The measured plot shows that the circuit is able to start operating at -4 dBm, but with an efficiency of about 10%; whereas, for an input power of -2 dBm, the achieved efficiency is better than 40% and this performance is preserved over a 20 dB range in input power. Thus, it can be assumed that the rectifier sensitivity is around -4 dBm. Based on this measured performance, the power budget of the link between the RF source and the relay node can be obtained, assuming free-space propagation. Note that numerical convergence was difficult to be ob-

tained during nonlinear circuit simulation for the results of Figs. 2.13, 2.14, 2.16 e 2.17. Indeed, the circuit simulator was able to handle problems up to about +10 dBm of RF powers, while measurements could be carried out up to +18 dBm.

Finally, Fig. 2.18 demonstrates the key role of the bias-assisting loop in enhancing the system performance, by comparing the measured rectifier performance with and without the loop: in the absence of the loop the rectifier operates over a reduced input power range, approximately from +4 dBm to +18 dBm, with 45-50% of efficiency. With the bias-assisting loop, the minimum voltage required to start gate self-biasing is reached with input power levels as low as -4 dBm (8 dB improvement), and, by increasing the power, efficiency values similar to the no-loop case are achieved.

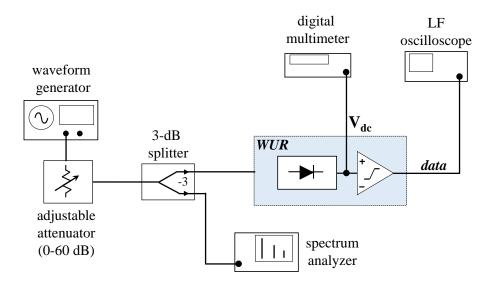

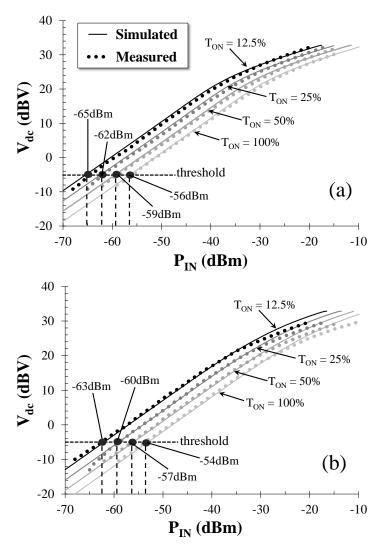

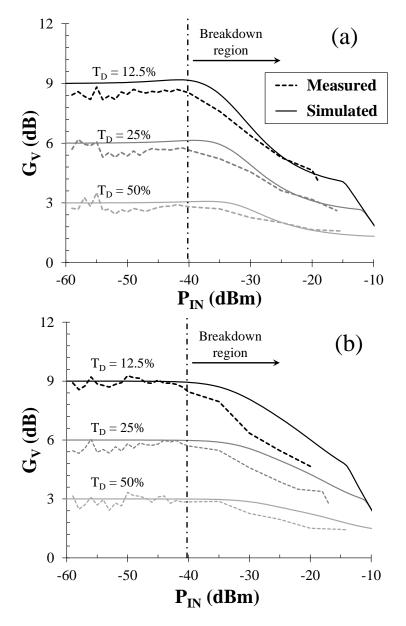

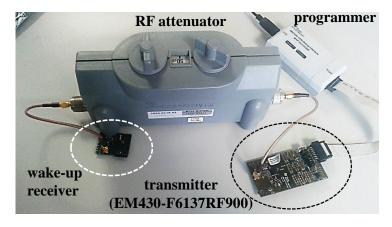

**Figure 2.18:** Measured RF-to-dc conversion efficiency and output voltage, with and without bias-assisting loop, as a function of the input power.