# **University of Bologna**

FACULTY OF ENGINEERING DEPARTMENT OF ELECTRICAL ENGINEERING

Ph.D. in Electrical Engineering XIX Cycle Power Electronics, Electrical Machines and Drives (ING-IND/32)

# Multilevel Converters: Dual Two-Level Inverter Scheme

**Ph.D. thesis of:** Alberto Lega

**Tutor:** Prof. Domenico Casadei

**Ph.D. Coordinator:** Prof. Francesco Negrini

**Final Dissertation on March 2007**

#### To my parents

"Zwei Dinge erfüllen das Gemüt mit immer neuer und zunehmender Bewunderung und Ehrfurcht, je öfter und anhaltender sich das Nachdenken damit beschäftigt: Der bestirnte Himmel über mir, und das moralische Gesetz in mir."

"Two things fill the mind with ever new and increasing admiration and awe, the more often and steadily reflection is occupied with them: the starry heaven above me and the moral law within me"

Kritik der reinen Vernunft (Critique of Pure Reason). I. Kant (1724-1804).

"There are two things that are indefinite to me; the first is the universe, the second is the stupidity of mankind, and I am not sure about the first one."

A. Einstein (1879-1955).

"Patientia est honestatis aut utilitatis causa rerum arduarum ac difficilium voluntaria ac diuturna perpessio."

"Patience is a wilful and constant tolerance of hard and difficult things with purposes of honesty and utility."

*Rhetorica - De Invenzione*. Marcus Tullius Cicero (106 bC-43 bC).

# Acknowledgements

First of all, I want to thank my parents for all the help they gave me, a support both monetary and moral. They have kept me during all my life, even when I was Ph.D. student with the modest grant the government provided to me. Without them, getting the degree would have been really hard, almost impossible.

My gratitude goes also to all my relatives, who will be always alive in my heart. I want to thank my grannies, my grandpas, my uncles and aunts: the cakes they prepared to me were very good to regenerate the energies spent during my work. To be honest, I spent more energy having fun than applying to the thesis, but the cakes were also good.

All the friends of mine deserve a room in my mind. Physically, someone went away and some else arrived, but everyone is always near to me. Many things have changed in the last three years and some friends have new engagements which made our friendship transform. I am referring to Enrico and Elena, to Mauro and Anna, to Federic and Lucia: I wish you all the good things for you and the families you are growing.

Even with other friends the relations have changed during these years, but in a slighter way. We are still meeting every week and we are still doing the same things as three years ago. Different places, different behaviours, but we continue to get fun together and to help one another. Hence, I want to thank all friends at once, because these pages would not be sufficient to contain a punctual description of the reasons why I have to thank each one among the friend of mine.

The experience in Denmark made me meet new people whom I consider friend. They are scattered in the whole Europe, even in Canada. I want to keep in contact with them all, but there are some problem related to the engagements we have that make it difficult. Anyway, their friendship made me grow and helped me during my stay in Aalborg.

To conclude, Domenico Casadei deserves my gratitude for the possibility he gave me to attend Ph.D. courses and for the help he provided to me as my tutor. Moreover, I have to thank Giovanni Serra, Angelo Tani, Gabriele Grandi and Claudio Rossi: without them my Ph.D. thesis would not be written.

Thank to everyone

Alberto

# **Table of contents**

| Acknowl   | edgements                                   | 9  |

|-----------|---------------------------------------------|----|

| Table of  | contents                                    | 11 |

| Preface   |                                             | 17 |

| Survey of | f topologies (Chapter 1)                    | 21 |

| 1.1       | Introduction                                |    |

|           | 1.1.1 Short history                         |    |

|           | 1.1.2 Multilevel concept                    |    |

|           | 1.1.3 Redundant states and voltage vectors  | 23 |

|           | 1.1.4 Multilevel inverter performance       | 25 |

| 1.2       | Diode-clamped                               | 25 |

|           | 1.2.1 Operating principle                   |    |

|           | 1.2.2 Characteristics                       | 27 |

| 1.3       | Flying-capacitor                            |    |

|           | 1.3.1 Operating principle                   |    |

|           | 1.3.2 Characteristics                       |    |

| 1.4       | Cascade H-bridge                            |    |

|           | 1.4.1 Operating principle                   |    |

|           | 1.4.2 Characteristics                       |    |

| 1.5       | Multi Point Clamped (MPC)                   |    |

|           | 1.5.1 Operating principle                   |    |

|           | 1.5.2 Characteristics                       |    |

| 1.6       | Other topologies                            |    |

|           | 1.6.1 Hybrid converter                      |    |

|           | 1.6.2 Soft-switching converter              |    |

|           | 1.6.3 Dual 2-level 3-phase cascade inverter |    |

| Multileve | el modulation (Chapter 2)                   |    |

| 2.1       | Introduction                                | 39 |

|           | 2.1.1 General considerations                |    |

|           | 2.1.2 Modulation classification             |    |

| 2.2       | Fundamental switching frequency modulations |    |

|           | 2.2.1 Space Vector Control (SVC)            |    |

|           | 2.2.2 Selective harmonic elimination        |    |

| 2.3       | Mixed switching frequency modulation        |    |

| 2.0       | 2.3.1 Hybrid multilevel modulation          |    |

| 2.4       | High switching frequency modulations        |    |

| 2.1       | 2.4.1 Space Vector PWM (SVPWM)              |    |

|           | 2.4.2 Phase Shifted PWM (PSPWM)             |    |

|           | 2.4.3 Level Shifted PWM (LSPWM)             |    |

| 2.5       | Multilevel Direct Torque Control (MDTC)     |    |

|           | 2.5.1 Direct Torque Control Principle       |    |

|            | 2.5.2          | Applications of DTC to multilevels                   | . 51 |

|------------|----------------|------------------------------------------------------|------|

| Dual 2-lev | vel invert     | er (Chapter 3)                                       | . 55 |

| 3.1        | Introduc       | tion                                                 | . 55 |

|            | 3.1.1          | Topology description                                 | . 55 |

|            | 3.1.2          | Applications                                         | . 56 |

| 3.2        | Analysis       | s of the system                                      | . 58 |

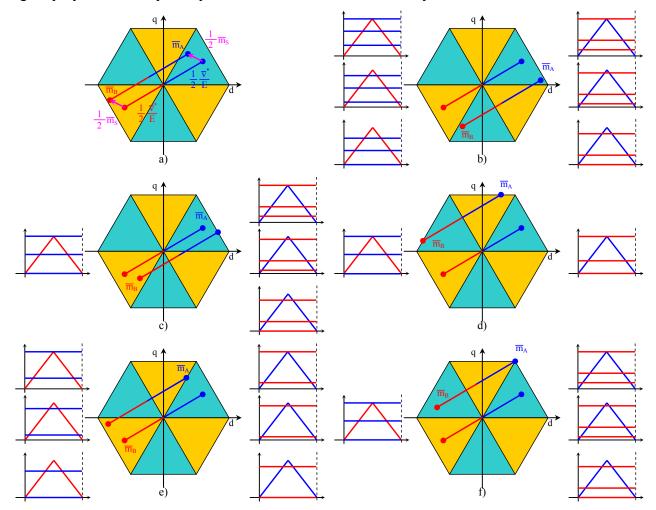

|            | 3.2.1          | Generable voltage vectors                            |      |

|            | 3.2.2          | Relationship between leg states and voltage vectors  |      |

|            | 3.2.3          | Common mode voltage                                  |      |

|            | 3.2.4          | Dual 2-level inverter with different source voltages |      |

| 3.3        | Analytic       | al approach: complex duty-cycles                     | . 70 |

|            | 3.3.1          | Complex duty-cycles definition                       |      |

|            | 3.3.2          | Limits and degrees of freedom                        |      |

|            | 3.3.3          | Determination of DC bus currents                     |      |

| Analogue   | modulat        | ion (Chapter 4)                                      | 79   |

| U          |                | · · · ·                                              |      |

| 4.1        |                | tion                                                 |      |

|            | 4.1.1<br>4.1.2 | Overview                                             |      |

|            |                | Classification                                       |      |

| 4.2        | U              | ar carrier based modulation                          |      |

|            | 4.2.1          | Double reference                                     |      |

|            | 4.2.2          | Two carriers                                         |      |

| 4.3        | -              | carrier based modulation                             |      |

|            | 4.3.1          | Modulation and six-step                              |      |

|            | 4.3.2          | Simulation results                                   | 101  |

| Digital mo | odulation      | n (Chapter 5)                                        | 109  |

| 5.1        | Introduc       | tion                                                 | 109  |

|            | 5.1.1          | Power sharing                                        |      |

|            | 5.1.2          | Power sharing aims                                   |      |

| 5.2        | Power sl       | haring                                               | 110  |

|            | 5.2.1          | Power sharing coefficient                            |      |

|            | 5.2.2          | Duty-cycles determination                            |      |

|            | 5.2.3          | Limits of power sharing coefficient k                |      |

| 5.3        | Multilev       | rel operation                                        |      |

|            | 5.3.1          | Determination of subduty-cycles                      |      |

|            | 5.3.2          | Indefiniteness of Region 2                           |      |

|            | 5.3.3          | Switching table construction                         |      |

| 5.4        | Dead-tin       | nes effects                                          |      |

|            | 5.4.1          | Double commutation effects                           |      |

|            | 5.4.2          | Analysis of different configurations                 |      |

|            | 5.4.3          | Other possibilities                                  |      |

| 5.5        | Six-step       | implementation                                       | 133  |

|            | 5.5.1          | Power sharing achievement                            |      |

|            | 5.5.2          | Analysis of delivered powers                         |      |

|            | 5.5.3          | Limits of delivered power                            |      |

| Power sha | aring simulations (Charter 6)                                                                         | 141 |

|-----------|-------------------------------------------------------------------------------------------------------|-----|

| 6.1       | Introduction                                                                                          | 141 |

|           | 6.1.1 Simulation environment                                                                          | 141 |

|           | 6.1.2 Simulink S-Function                                                                             | 142 |

| 6.2       | Algorithm implementation                                                                              | 143 |

|           | 6.2.1 System overview                                                                                 |     |

|           | 6.2.2 Determination of reference position                                                             |     |

|           | 6.2.3 Schematic description of the system                                                             |     |

|           | 6.2.4 Algorithm analysis                                                                              | 146 |

| 6.3       | Simulation results                                                                                    | 148 |

|           | 6.3.1 Effectiveness of the control                                                                    |     |

|           | 6.3.2 Power sharing effectiveness                                                                     | 152 |

|           | 6.3.3 Performances                                                                                    | 154 |

| Set-up im | nplementation (Charter 7)                                                                             | 155 |

| 7.1       | Introduction                                                                                          | 155 |

| /.1       | 7.1.1 System overview                                                                                 |     |

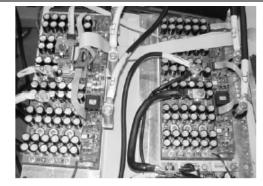

| 7.2       | Hardware                                                                                              |     |

| 1.2       | 7.2.1 Digital signal processor and control hardware                                                   |     |

|           | 7.2.1 Digital signal processor and control hardware                                                   |     |

|           | 7.2.3. Power boards                                                                                   |     |

|           | 7.2.4. Other hardware                                                                                 |     |

| 7.3       | Software                                                                                              |     |

| 1.5       | 7.3.1. Implemented algorithm                                                                          |     |

|           | <ul><li>7.3.1. Implemented algorithm</li></ul>                                                        |     |

|           | <ul><li>7.3.2. Tostilon determination algorithm</li><li>7.3.3. Implemented switching tables</li></ul> |     |

|           | 7.3.4 Compiling process overview                                                                      |     |

|           | 7.3.5 Code analysis                                                                                   |     |

| Europing  |                                                                                                       |     |

| -         | ental results (Charter 8)                                                                             | 107 |

| 8.1       | Introduction                                                                                          | 167 |

|           | 8.1.1 Aim of the experiments                                                                          | 167 |

| 8.2       | Reduced scale converter                                                                               | 167 |

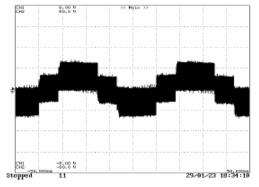

|           | 8.2.1 Common mode voltage                                                                             | 167 |

|           | 8.2.2. Twelve-step implementation                                                                     |     |

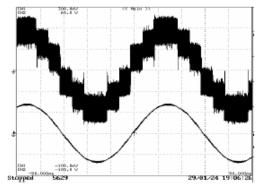

|           | 8.2.3. Six-step and modulation                                                                        | 169 |

| 8.3       | Full scale converter                                                                                  | 170 |

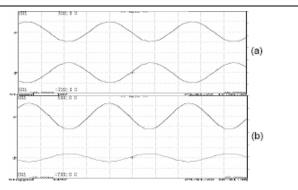

|           | 8.3.1. SVM implementation                                                                             | 170 |

|           | 8.3.2. Power sharing                                                                                  | 171 |

| 8.4       | Conclusion                                                                                            | 172 |

|           | 8.3.1. Conclusion                                                                                     | 172 |

| Appendix  | x 1                                                                                                   | 177 |

| A1.1      | Introduction                                                                                          |     |

| 411.1     | A1.1.1 Standard 3-phase motor drive                                                                   |     |

|           | A1.1.2 Alternative solutions                                                                          |     |

| A2.2      | Analysis of alternative solutions                                                                     |     |

| 112.2     | All                                                               |     |

|           |                                                                                                       |     |

| A1.2.2.    | Double 3-phase solution<br>Dual 2-level inverter solution |     |

|------------|-----------------------------------------------------------|-----|

| A1.2.3.    | Dual 2-level inverter solution                            |     |

| Appendix 2 |                                                           |     |

| Appendix 3 |                                                           | 195 |

| Appendix 4 |                                                           |     |

| Appendix 5 |                                                           |     |

| References |                                                           | 225 |

# Preface

The first attempt of power conversion was made by Pacinotti in 1864 and then Wilde, Varley and Siemens patented the dynamo in 1866-67. With his machine Pacinotti had the possibility to convert mechanical into electrical power and vice versa. Further improvements allowed Ferraris (1885) to create a rotating electro-magnetic field able to make a metallic egg rotate. This principle is the basis of induction machine operation.

Unfortunately, both Pacinotti's and Ferraris' machines were directly connected to the power source; hence they were without any automatic control. Moreover, the problems related to not controlled start-up are relevant and well known.

Power Electronics are a viable solution to these problems and got more and more importance during the years due to the benefits they brought into electrical engineering fields. Power Electronics inherited their foundations from signal amplifier technologies and then developed to drive high powers. There are lots of advantages which Power Electronics brought, but the most meaningful is the possibility to control electrical machine and to manage the flows of electromagnetic power. During Eighties and Nineties, the developments of Power Electronics allowed to implement innovatory systems and to improve the existent ones. Due to Power Electronics it was possible to build drives, active filters, static Var compensators, etc...

Nowadays, the static converter can connect systems with different electrical characteristics: for instance, choppers connect two DC systems with different voltage level, whereas inverters transform power from DC to AC with variable amplitude and frequency.

Unfortunately, the existing converter topologies allow a small margin to further improvements because of the intrinsic limits of semiconductor devices. Indeed, considering the electrical characteristics of switching devices, it can be asserted it will be harder and harder overcome the actual limits imposed by silicon. For instance, only slowest devices can withstand voltages of the order of magnitude of 10 kV.

The multilevel converters were born with the specific aim to overcome the voltage limit of semiconductor devices: one of their first applications was the connection between AC and DC high voltage systems. The main idea at the basis of multilevel converters is to connect more devices in series and clamp the voltages between their pins. The differences among multilevel converter structures derive from how the clamping is done. In cascade H-bridge converters the clamping is done by the batteries, diodes have this task in diode-clamped topologies, and so on.

The first multilevel converter can be attributed to R. H. Baker and L. H. Bannister, who patented the cascade H-bridge in 1975. In 1980 Baker patented diode-clamped topology which can be still considered the most used. In 1992, T. A. Meynard and H. Foch patented the flying-capacitor architecture. In the same year, S. Osagawara, J. Takagali, H. Akagi and A. Nabae proposed a new approach: they considered a standard Current Source Inverter (CSI) and increased the number of current levels instead of voltage ones. From 1992 till now, the research on multilevel converters both perfected original topologies and invented new ones, finding ever new and uncommon applications.

The former use of multilevel converter in high voltage applications is still implemented on high voltage DC transmission lines, to connect the DC side to AC grid. Moreover, low voltage applications for which multilevel are suited were discovered. In particular, multilevel converters

offer a better quality of the output waveforms than standard converters. This peculiarity is very useful to comply with the standards about the energy quality which become stricter and stricter. Moreover, multilevel converters are suited even in drive applications, because sophisticated control algorithms can exploit the high number of levels to improve the performance of the system.

Multilevel converters can bring innovations even in traction applications, a particular niche of drive applications. Considering the state of the art in this technology field, it can be asserted the maximum power limit has been reached. This fact derives both from standards and from economical reasons.

Considering land traction industrial applications, standards limit the maximum voltage of each battery banks at 96 V for safety reasons. On the other hand, standard do not impose this limit to road vehicles, but the market does. The semiconductor switches usually used in this kind of applications are MOSFETs rated 150 V because they have the smallest cost among all the devices. Hence, even if the limit on the voltage is not imposed by an actual law, it is still present in road transport applications too.

One way to overcome this problem was presented by Profumo. He proposed to use a doublewound 3-phase motor, instead of the standard ones. In this way, with two converters and two control systems the power is doubled by the injection of twice the current than a standard solution. Unfortunately, in case of fault in one inverter, the vehicle will be still able to proceed, but at reduced current that means the torque the motor produces is halved. Considering that the vehicle is at full load or in a steep slope, the reduction of the torque will mean the impossibility to move or, even worse, the vehicle will move backward.

Another viable solution to increase the power keeping constant the maximum DC voltage is given by multi-phase converters. Unfortunately, this solution is even more expensive than the previous because both multiphase converter and motor are custom-made. Moreover, even the control system must be designed for the specific number of phases and may require a lot of resources.

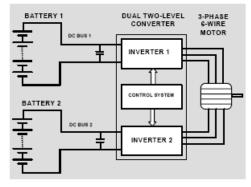

The dual 2-level inverter, the multilevel converter topology studied and proposed in this dissertation, represents the third way to overcome the power limit. Considering battery-fed applications, the two insulated sources can be easily found splitting the battery bank in two parts. Moreover, all the 3-phase machines allow the six-wire open-end connection required by this system. Hence, using only standard components connected in an unusual way, it is possible to twice the power delivered to the load.

The use of standard converters and motors has intrinsic advantages in term of costs and reliability. Furthermore, in case of fault of one inverter, the vehicle will be able to move producing the rated torque, but at half the rated speed because the system will lack voltage instead of current. Hence, the vehicle will move slower, but it will be still able to scour slopes.

For these reasons, dual 2-level inverter is well suited for land traction application, but even other applications can have benefits deriving from the exploitation of the peculiarities of the dual 2-level inverter. In particular naval hybrid traction and active filter applications have been proposed for that converter type.

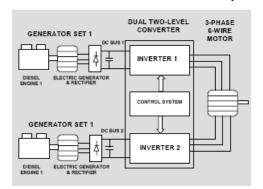

Naval traction can use this converter together with two diesel engines to have two selectable power levels. Indeed some ships, like fishing boats, must operate in two cruise modalities. During fishing operations, the trawl-nets represent a load requiring great torque, but low power: only one inverter and one engine can be used to guarantee the required power and a pretty good efficiency of mechanical system. On the other hand, when the boat is moving, the required power is largely more, and the dual 2-level inverter must be fully used together with the two engines. In this way the overall efficiency of the system can be improved in both cruise modalities.

Regarding active filtering, a possible application of the dual 2-level inverter has been found and it is being currently investigated at the Department of Electrical Engineering of Bologna. Being a quite new application for the dual 2-level inverter, a summary of the benefit brought by the converter is actually a hard job. Anyway the direction assumed by the research is to use two photovoltaic panels to provide power and a 3-phase transformer for the connection to the grid.

The investigation on the dual 2-level inverter is a research theme which offers several prospects because the converter itself has the possibilities to be widely used. It has some advantages proper of the multilevel converters, but does not require any custom-built hardware. Moreover, converter architecture suggests the idea to manage the power flowing throughout the two inverters offering a way to control the discharge of battery banks, for instance.

The following dissertation has the aim to investigate this multilevel topology, starting from the basis. A survey of multilevel topologies and modulation will introduce to the accurate description of the dual 2-level inverter. Two modelling methodology for this converter will be analysed: one is the use of space vectors, the other is based on complex duty-cycle theory. Using these mathematical tools, a power sharing technique will be presented together to the analytical study of its effects during commutations. To conclude, two converter have been built and some experimental results will be shown, proving that power sharing can be realized.

# **Chapter 1**

# **Survey of topologies**

## 1.1. Introduction

#### **1.1.1.** Short history

The concept of utilizing multiple small voltage levels to perform power conversion was presented by an MIT researcher over twenty years ago [1,2]. Advantages of this multilevel approach include good power quality, good Electro-Magnetic Compatibility (EMC), low switching losses and high voltage capability. The main disadvantages of this technique are the larger number of semiconductor switches required than the 2-level solution and the capacitor banks or insulated sources needed to create the voltage steps on the DC busses. The first topology introduced was the series H-bridge design [1]. This was followed by the diode-clamped converter [2-4] which utilises a bank of series capacitors to split the DC bus voltage. The flying-capacitor (or capacitorclamped) [5] topology followed diode-clamped after few years: instead of series connected capacitors, this topology uses floating capacitors to clamp the voltage levels. Another multilevel design, slightly different from the previous ones, involves **parallel connection** of inverter phases through inter-phase reactors [6]. In this design the semiconductors must block the entire voltage, but share the load current. Several combinatorial designs have also emerged [7], implemented cascading the fundamental topologies [8-12]; they are called hybrid topologies. These designs can create higher power quality for a given number of semiconductor devices than the fundamental topologies alone due to a multiplying effect of the number of levels.

In the beginning multilevel converters were introduced to drive high voltages, like in **High Voltage Direct Current (HVDC)** applications to make the front-end connection between DC and AC lines. In this way the limits on the maximum voltage tolerable by the semiconductor switches were overtaken and the converters were able to drive directly the line voltage without a transformer. Nowadays it is possible to find multilevel applications even in low voltage field, like motor drive, because of the high quality of the AC output. In particular back-to-back multilevel systems can drive motors with very good performance concerning the line voltage and current distortions. Multilevel can even improve the converter losses.

Recent advances in power electronics have made the multilevel concept practical [1-19]. In fact, the concept is so advantageous that several major drive manufacturers have obtained patents on multilevel power converter and associated switching techniques [20-26].

#### **1.1.2.** Multilevel concept

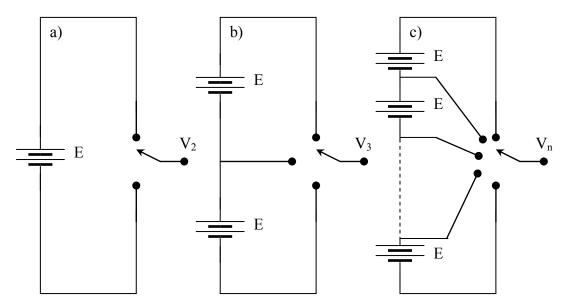

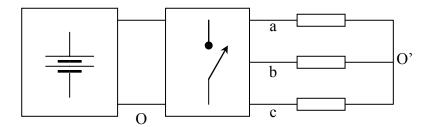

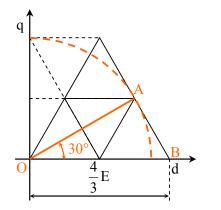

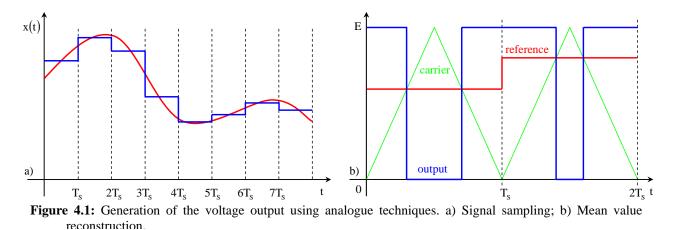

This paragraph has the aim to introduce to the general principle of multilevel behaviour. Figure 1.1 helps to understand how multilevel converters work. The leg of a 2-level converter is represented in Figure 1.1a) in which the semiconductor switches have been substituted with an ideal switch. The voltage output can assume only two values: 0 or E. Considering Figure 1.1b), the voltage output of a 3-level inverter leg can assume three values: 0, E or 2E. In Figure 1.1c) a generalized n-level inverter leg is presented. Even in this circuit, the semiconductor switches have been substituted with an ideal switch which can provide n different voltage levels to the output. In this short explanation some simplifications have been introduced. In particular, it is considered that the DC voltage levels can be different. This introduces a further possibility which can be useful in multiphase inverters, as it will be shown in the following.

A three-phase inverter composed by n-level legs will be considered for the analysis. Obviously the number of phase-to-neutral voltage output levels is n. The number k of the line-to-line voltage levels is given by (1.1).

$$k = 2n - 1. \tag{1.1}$$

Considering a star connected load, the number p of phase voltage levels is given by (1.2).

$$p = 2k - 1. \tag{1.2}$$

For example, considering a 5-level inverter leg, it is possible to obtain 9 line-to-line voltage level (3 negative levels, 3 positive levels and 0) and 17 phase voltage levels.

Higher is the number of levels better is the quality of output voltage which is generated by a greater number of steps with a better approximation of a sinusoidal wave. So, increasing the number of levels gives a benefit to the harmonic distortion of the generated voltage, but a more complex control system is required, with the respect to the 2-level inverter.

Figure 1.1: Inverter phases. a) 2-level inverter, b) 3-level inverter, c) n-level inverter.

#### 1.1.3. Redundant states and voltage vectors

Two or more switching states that produce the same output voltage are called **redundant states**. It is possible to distinguish between two kind of redundant states: **intra-phase** and **joint-phase**. Intra-phase redundant states involve the switching state (or configuration) of only one phase; obviously this kind of redundancy is strictly related to the hardware architecture of the converter. Just to make an example, flying-capacitor converter has intra-phase redundant states; instead diode-clamped does not.

On the other hand, joint-phase redundant states involve the switching state of the whole converter and all multi-phase converters present this phenomenon. Because of the dependency on the architecture, intra-phase redundancy will be analyzed for each single converter presented in this chapter. The aim of this paragraph is to introduce the joint-phase redundancy through the use of Park transform. In order to simplify the discussion, a general three-phase n-level inverter is taken into account as shown in Figure 1.2. Furthermore, the load is supposed to be star-connected and of linear type. In this system it is possible to define three inverter voltages ( $v_{aO}$ ,  $v_{bO}$ ,  $v_{cO}$ ). Assuming that all the voltage steps have the same value E, each inverter voltage can be expressed as:

$$\mathbf{v}_{\mathrm{xO}} = \mathbf{E} \cdot \mathbf{s}_{\mathrm{x}} \,. \tag{1.3}$$

In (1.3),  $v_{x0}$  is the general inverter voltage and  $s_x$  is the state of the generic leg. The values assumed by  $s_x$  are limited between 0 and n-1 (where n is the number of levels). For example, in a 3-level inverter  $s_x$  can assume the values 0, 1, 2.

Assuming  $\overline{\alpha} = e^{j_3^2 \pi}$  and applying Park transform [27] to inverter voltages, the related voltage vector and the common mode voltage can be expressed as follow:

$$\overline{\mathbf{v}} = \frac{2}{3} \left( \mathbf{v}_{a0} + \mathbf{v}_{b0} \overline{\alpha} + \mathbf{v}_{c0} \overline{\alpha}^2 \right)$$

$$\mathbf{v}_o = \frac{1}{3} \left( \mathbf{v}_{a0} + \mathbf{v}_{b0} + \mathbf{v}_{c0} \right)$$

(1.4)

Similarly, it is possible to define three load voltages  $(v_{aO'}, v_{bO'}, v_{cO'})$  and obtain  $\overline{v}'$  and  $v'_o$ , which represent as the load voltage vector and common mode voltage respectively. Because the load is star-connected and linear, the common mode voltage must be zero. Applying Kirchhoff's voltage law to a generic phase x, the following equation is obtained.

$$v_{k0} = v_{k0'} + v_{0'0}$$

. (1.5)

Substituting (1.5) in (1.4) for each phase, yields:

Figure 1.2: General three-phase inverter scheme.

Figure 1.3: Space vectors generated by 2-level, 3-level and 5-level inverters.

$$\overline{\mathbf{v}} = \overline{\mathbf{v}}'$$

$$\mathbf{v}_{o} = \mathbf{v}_{OO}$$

(1.6)

Because the load common mode voltage is always zero, the first of (1.6) implies that the load voltages are not dependent on the common mode component of inverter voltages; in other words each set of voltages  $\{v_{aO}, v_{bO}, v_{cO}\}$  applied by the inverter has the same effect on the load. Anyway, different sets of voltages may have different effects on the sources or on the converter components. For instance, redundant vectors are used in diode-clamped converter to balance the voltage level of DC capacitors.

The number of voltage sets  $n_{vs}$  an inverter can produce and the number of different voltage vector  $n_v$  can be expressed as follow:

$$n_{vs} = n^3 \tag{1.7}$$

$$n_v = 3n(n-1)+1.$$

(1.8)

Moreover, to distinguish among different switching states a converter can assume, it is possible to use the following equation which gives an univocal number  $(n_{sw})$  for each state.

$$n_{sw} = n^2 s_a + n s_b + s_c$$

(1.9)

Given a specific voltage vector and its related leg states set  $\{s_a, s_b, s_c\}$ , the number of joint-phase redundant states  $n_{rs}$  can be expressed as follow:

$$n_{rs} = n - (s_{max} - s_{min}).$$

(1.10)

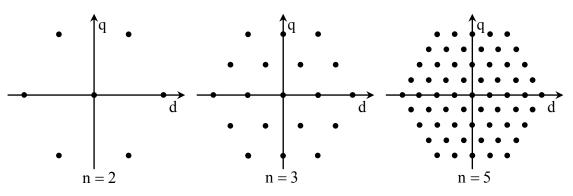

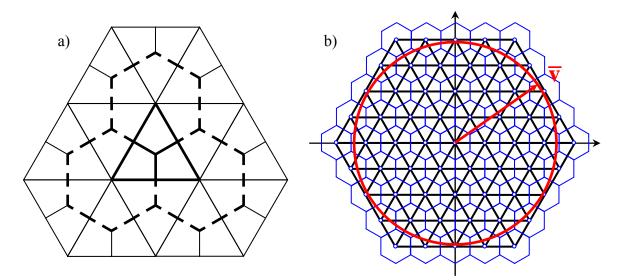

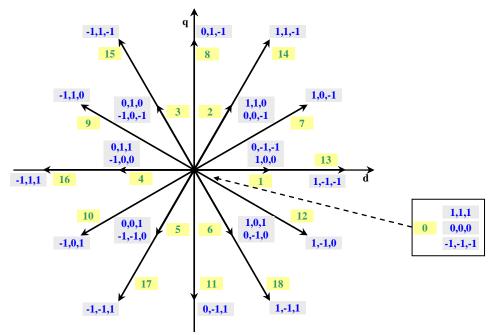

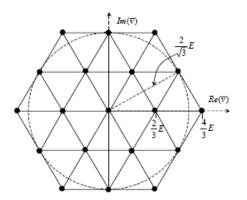

In (1.10),  $s_{max}$  and  $s_{min}$  are the maximum and the minimum among  $\{s_a, s_b, s_c\}$  respectively. The voltage space vectors generated by 2-level, 3-level and 5-level inverters are shown in Figure 1.3. Increasing the number of levels means an increment in the resolution of generable vectors. Obviously the diagrams presented in Figure 1.3 are obtained considering the same voltage step for each level. In case of different level amplitude, the number of generable vector can increase until it reaches the number of voltage sets if proper ratios among the level amplitudes are chosen. In [28-30] there is a better explanation of this use of redundant configuration.

#### 1.1.4. Multilevel inverter performance

The limit of standard three-phase converters is related to the maximum power. Which can be delivered to the load, which is related to the maximum voltage and current of a component. Furthermore, higher is the power of a switch lower is the switching frequency. An initial solution to overcome this problem was to connect several switches in series or in parallel. The series connection of two or more semiconductor devices is really difficult due to the impossibility to perfectly synchronize their commutations. In fact, if one component switches off faster than the others it will blow up because it will be subjected to the entire voltage drop designed for the series. Instead, parallel connection is slightly less complicated because of the property of MOSFETs and more recent IGBTs to increase their internal resistance with the increment of junction temperature. When a component switches on faster than the others, it will conduct a current greater than the current it was designed for. In this way, the component increases its junction temperature and its resistance, so it limits the current which flow through it. This effect makes possible to overcome the problems coming from a delay among gate signals or from differences among real turn on time of the components. Anyway, parallel connection of the switches requires an accurate design of the board.

A modular solution is preferred to increase the power a converter can drive. In this way, a standard three-phase converter is designed with a relatively low power. Then, several converters are paralleled through decoupling inductances to reach the desired power. Even in this system a quite good synchronization among the controls of the converters is required.

Multilevel converters are a viable solution to increase the power with a relatively low stress on the components and with simple control systems. Moreover, multilevel converters present several other advantages. First of all, multilevel converters generate better output waveforms with a lower  $\frac{dv}{dt}$  than the standard converters. Then, multilevel converter can increase the power quality due to the great number of levels of the output voltage: in this way, the AC side filter can be reduced, decreasing its costs and losses. Furthermore, multilevel converter can operate with a lower switching frequency than 2-level converters, so the electromagnetic emissions they generate are weaker, making less severe to comply with the standards. Furthermore, multilevel converters can be directly connected to high voltage sources without using transformers; this means a reduction of implementation and costs.

### **1.2.** Diode-clamped

#### **1.2.1.** Operating principle

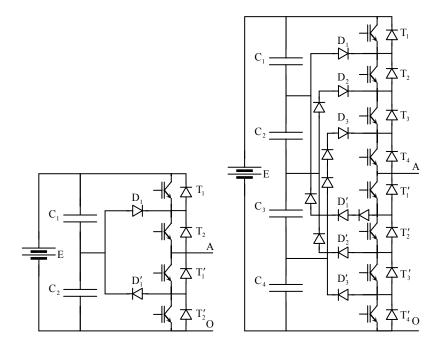

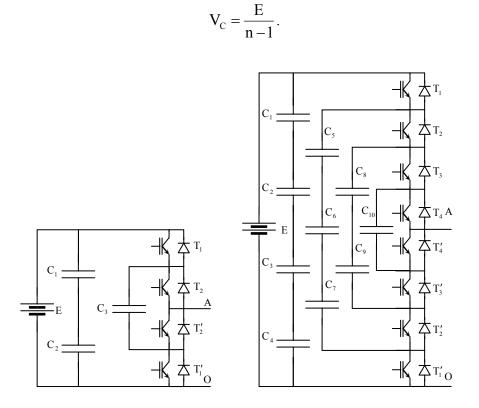

In Figure 1.4, 3-level and 5-level diode-clamped legs are shown; it is easy to extend the scheme to a generic n-level configuration. The DC bus voltage is split in two and four equal steps respectively by capacitor banks. In this way, no extra DC sources are needed with respect to the standard 2-level inverter. The voltage between two switches is clamped through the diodes in the middle of the structure, called **clamping diodes**. Considering the 5-level diode-clamped leg, it is possible to note that the number of diodes required to clamp the voltage changes point by point. For instance  $D_1$  is composed only by one diode, instead  $D'_1$  is the series of three diodes. This does not mean that the diode series connection is needed in the implementation, but it simply means that the reverse voltage drop born by  $D'_1$  is three times the backward voltage drop over  $D_1$ . In the final implementation it is allowed to use either one diode with higher blocking capability or three diodes series connected. Anyway, to better understand how a diode-clamped works, it is preferred to use

series connected diodes; in this way, the reverse voltage drop of all the diodes is the same and is equal to the voltage fixed by a capacitor.

For a generic n-level diode-clamped the diode reverse voltage is given by (1.11):

$$\mathbf{V}_{\mathrm{r}} = \frac{\mathrm{E}}{\mathrm{n}-\mathrm{l}} \,. \tag{1.11}$$

In 3-level diode-clamped it is  $V_r = \frac{E}{2}$  while in 5-level it is  $V_r = \frac{E}{4}$ . Furthermore, this voltage drop is also the reverse voltage each switch has to block. Now it is clear that increasing the levels means a reduction of the stress over the components, considering the same DC bus voltage.

Unfortunately, higher is the number of levels higher is the number of components. Increasing of one level involve the use of one capacitor, two switches and a lot of diodes more. In fact the number of clamping diodes used in a diode-clamped is related to the number of level by the following expression:

$$N_{\text{Diodes}} = (n-1)(n-2).$$

(1.12)

Focusing the attention to the 3-level leg, it is possible to find the relationship between the state of the switches and the output voltage  $V_{AO}$ . Before all consideration, a right switches configuration must avoid every kind of shortcut. So, it is simple to understand that all the switches cannot be

| T <sub>1</sub> | T <sub>2</sub> | T <sub>1</sub> ' | Τ'2 | V <sub>AO</sub> |

|----------------|----------------|------------------|-----|-----------------|

| 1              | 1              | 0                | 0   | Е               |

| 0              | 1              | 1                | 0   | E/2             |

| 0              | 0              | 1                | 1   | 0               |

| 1              | 0              | 0                | 1   | Undefined       |

Table 1.1: 3-level diode-clamped leg relationships between configurations and output voltages.

Figure 1.4: 3-level and 5-level diode-clamped legs.

simultaneously turned on. There are also other dangerous configuration, but they can be avoided switching  $T_1$  and  $T'_1$  in a complementary way. The same has to happen for  $T_2$  and  $T'_2$ . Considering these conditions there are only four possible configurations a 3-level diode-clamped leg can assume and they are shown in Table 1.1 with the agreement to identify switches on-state with 1 and offstate with 0. Not all the four configuration leads to a proper leg output voltage, because when  $T_1$  in on and  $T_2$  is off there is no defined path for the load current because whether  $T_2$  or  $T'_1$  are not conducting, so the current flows throughout the free-willing diodes and the output voltage depends on it. As it is possible to see from Table 1.1, there are no intra-phase redundant states in 3-level diode-clamped.

configurations are allowed for the switches as Table 1.2 shows.

Switches state

Similarly, 5-level diode-clamped leg does not present redundant states and only five different

| <b>T</b> <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | T <sub>4</sub> | T' <sub>1</sub> | T <sub>2</sub> ' | T' <sub>3</sub> | T4 | V <sub>AO</sub> |

|-----------------------|----------------|----------------|----------------|-----------------|------------------|-----------------|----|-----------------|

| 1                     | 1              | 1              | 1              | 0               | 0                | 0               | 0  | Е               |

| 0                     | 1              | 1              | 1              | 1               | 0                | 0               | 0  | 3E/4            |

| 0                     | 0              | 1              | 1              | 1               | 1                | 0               | 0  | E/2             |

| 0                     | 0              | 0              | 1              | 1               | 1                | 1               | 0  | E/4             |

| 0                     | 0              | 0              | 0              | 1               | 1                | 1               | 1  | 0               |

Table 1.2: 5-level diode-clamped leg relationships between configurations and output voltages.

Making some generalization from Table 1.1 and Table 1.2, in a n-level diode-clamped leg there are no intra-phase redundant states and n-1 consecutive switches are conducting. Moving the series of conducting switches from the top to the bottom end of the leg, the output voltage decreases from E to 0.

#### **1.2.2.** Characteristics

Diode-clamped converter presents some peculiarities which other multilevel topologies do not have. First of all, it is quite simple to control. Indeed, a simple extension of a traditional analog PWM control can directly gate the switches without any switching table in between. The main problems related to its control came from the digital controller which are suited for traditional 2-level converters and may not have outputs enough to drive all the semiconductors in the leg. But it is quite easy to implement a digital control system over a diode-clamped with commercial parts only, using some external hardware and designing a proper code.

Unfortunately, the reverse voltage drop changes among the components. The minimum reverse voltage drop is given by (1.11) and it is related to all the switches and some clamping diodes. For instance, considering the 5-level converter in Figure 1.4, the diode  $D'_1$  is subjected to three times the minimum reverse voltage drop when  $T'_2$   $T'_3$  and  $T'_4$  are conducting. Anyway this is not a serious disadvantage because it can be avoided using a series of more diodes or a different kind rated for a greater reverse voltage.

A very serious problem regards the mean current through the switches which is different. Considering the 5-level leg,  $T_1$  is conducting only when the required output voltage is E, while  $T_4$  is always conducting but when the required voltage is 0. Furthermore, the current flowing throughout  $T_4$  is always flowing even through  $T_1$ . So it is possible to assert that  $T_4$  average current is smaller than  $T_1$  average current. Choosing different kind of switches with the same reverse voltage and similar dynamic performances, but with different rated currents is quite difficult among commercial parts. Manufacturers prefer to use the same switch for every position even if they are not fully exploited somewhere in the leg.

Diode-clamped does not require insulated DC sources to create the voltage level, but exploits several capacitors to equally split a single DC source. This is a great advantage because makes the circuitry topology suitable to substitute a traditional system in all kinds of application: to upgrade an existing system it is necessary only to design a proper diode-clamped, take out the old converter and use the new one in its place. Unfortunately, some unbalance of capacitors voltages can take place and the control must keep it into consideration. A single leg can not face this problem because there are no intra-phase redundant states to use for this purpose. In the other hands, multi-phase diode-clamped converter can balance the capacitors voltages using joint-phase redundant states. Furthermore, when this kind of converter is connected in a back-to-back configuration, a proper synchronization between inverter and rectifier controls is sufficient to keep the capacitors balanced.

### **1.3.** Flying-capacitor

#### **1.3.1.** Operating principle

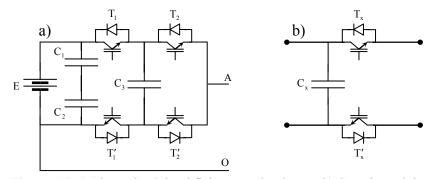

In Figure 1.5, 3-level and 5-level flying-capacitor legs are shown and it can be seen a close similarity with diode-clamped topology. The extension to more than 5 levels is easy even for flying-capacitor. As for the diodes in diode-clamped, the capacitors series are drown to highlight the voltage drop they have to tolerate. Indeed, the voltage over the capacitors nearer to the switches is lower than the voltage over the ones nearer to the source in steady-state. The voltage over each capacitor in Figure 1.5 is given by (1.13).

(1.13)

Figure 1.5: 3-level and 5-level flying-capacitor leg.

Furthermore, these capacitors have the same function of the clamping diodes in diode-clamped converter: they keep constant the voltage drop between the busses to which they are connected. For this reason, they are called **clamping capacitors**. The voltage given by (1.13) is also the reverse voltage drop each switch must bear when all capacitors are fully charged as it can be seen applying Kirchhoff's voltage law to the circuit in Figure 1.5.

Like in every converter, some leg switches configurations are not allowed. For instance, considering the 3-level converter,  $T_2$  and  $T'_2$  cannot be simultaneously closed because this means a shortcut of  $C_3$ . To avoid any problem coming from a possible shortcut of capacitors or sources,  $T_x$  and  $T'_x$  (where the subscript x substitutes the number of a generic switch) must to be in complementary state. In this way the possible configurations for an n-level leg are:

$$N_{conf} = 2^{n-1}$$

. (1.14)

Obviously, flying-capacitor leg presents intra-phase redundancy because the number of allowed configurations is greater than the number of possible voltage output levels. In Table 1.3 the 3-level converter switching table is presented.

| T <sub>1</sub> | T <sub>2</sub> | T <sub>1</sub> ' | Τ'2 | V <sub>AO</sub> |

|----------------|----------------|------------------|-----|-----------------|

| 1              | 1              | 0                | 0   | Е               |

| 1              | 0              | 0                | 1   | E/2             |

| 0              | 1              | 1                | 0   | E/2             |

| 0              | 0              | 1                | 1   | 0               |

| Table 1.3: 3-level flying-capacitor | r leg relationships betweer | n configurations and | l output voltages. |

|-------------------------------------|-----------------------------|----------------------|--------------------|

|                                     |                             |                      |                    |

|                | Switches state |                |                |                  |                  |                 |                  |                 |  |  |  |

|----------------|----------------|----------------|----------------|------------------|------------------|-----------------|------------------|-----------------|--|--|--|

| T <sub>1</sub> | T <sub>2</sub> | T <sub>3</sub> | T <sub>4</sub> | T <sub>1</sub> ' | T <sub>2</sub> ' | T' <sub>3</sub> | T <sub>4</sub> ' | V <sub>AO</sub> |  |  |  |

| 1              | 1              | 1              | 1              | 0                | 0                | 0               | 0                | Е               |  |  |  |

| 1              | 1              | 1              | 0              | 0                | 0                | 0               | 1                | 3E/4            |  |  |  |

| 1              | 1              | 0              | 1              | 0                | 0                | 1               | 0                | 3E/4            |  |  |  |

| 1              | 0              | 1              | 1              | 0                | 1                | 0               | 0                | 3E/4            |  |  |  |

| 0              | 1              | 1              | 1              | 1                | 0                | 0               | 0                | 3E/4            |  |  |  |

| 1              | 1              | 0              | 0              | 0                | 0                | 1               | 1                | E/2             |  |  |  |

| 1              | 0              | 1              | 0              | 0                | 1                | 0               | 1                | E/2             |  |  |  |

| 1              | 0              | 0              | 1              | 0                | 1                | 1               | 0                | E/2             |  |  |  |

| 0              | 1              | 1              | 0              | 1                | 0                | 0               | 1                | E/2             |  |  |  |

| 0              | 1              | 0              | 1              | 1                | 0                | 1               | 0                | E/2             |  |  |  |

| 0              | 0              | 1              | 1              | 1                | 1                | 0               | 0                | E/2             |  |  |  |

| 1              | 0              | 0              | 0              | 0                | 1                | 1               | 1                | E/4             |  |  |  |

| 0              | 1              | 0              | 0              | 1                | 0                | 1               | 1                | E/4             |  |  |  |

| 0              | 0              | 1              | 0              | 1                | 1                | 0               | 1                | E/4             |  |  |  |

| 0              | 0              | 0              | 1              | 1                | 1                | 1               | 0                | E/4             |  |  |  |

| 0              | 0              | 0              | 0              | 1                | 1                | 1               | 1                | 0               |  |  |  |

Table 1.4: 5-level flying-capacitor leg relationships between configurations and output voltages.

For a 3-level flying-capacitor, there are 4 possible leg configurations and two of them gives the same voltage level presenting intra-phase redundancy as expected. These two configuration have different effects on the capacitor  $C_3$ . Indeed, considering an outgoing output current, the configuration with  $T_1$  turned off and  $T_2$  turned on makes  $C_3$  discharging because the capacitor has to feed the load. Whereas, when  $T_1$  is turned off and  $T_2$  is turned off,  $C_3$  and the load are series connected to the source and the current flowing into the capacitor charges it. A proper control can keep the capacitor balanced monitoring its state and choosing the right configuration each time the middle output is required. A similar analysis can be done for the 5-level converter taking into account the effects of all the sixteen configurations shown in Table 1.4.

Considering Table 1.3 and Table 1.4, it is possible to deduce that the voltage applied is proportional to the sum of upper switches states. Assuming that  $T_x$  represents the state of a generic upper switch, (1.15) shows this relationship.

$$V_{AO} = \frac{E}{n-1} \sum_{x=1}^{n-1} T_x .$$

(1.15)

#### **1.3.2.** Characteristics

The main disadvantage of flying-capacitor architecture is capacitors balance. In a 3-level converter there is only one capacitor to keep balanced and the implementation of the control algorithm is quite easy. When the number of level rises, the voltages to keep controlled increase: a greater number of voltage sensors and a more complicated control are needed.

Even for this topology, the switch average currents could be different because they strictly depend on the control choice of redundant states. Some estimations of this value can be done, but is difficult to rate each switch for the exact current value. Like in diode-clamped implementation, a not fully exploitation of some switch is preferred.

The flying-capacitor converter has a very modular circuit as can be seen in Figure 1.6. In Figure 1.6a) an alternative layout for the 3-level converter is shown. This representation highlights the modules making up the flying-capacitor and one of them is separately shown in Figure 1.6b). The only difference among converter modules is the voltage born by the capacitor. After a module has been designed, making up the hardware for a n-level converter is quite easy and fast. Also the maintenance has its own benefits coming from this characteristic.

Another important peculiarity of this converter is the high portability. Indeed the flyingcapacitor can substitute a standard 2-level converter even more easily than the diode-clamped because the DC bus capacitor is still present and correctly rated, so there is no need to change it.

Figure 1.6: a) Alternative 3-level flying-capacitor layout, b) Generic module.

### **1.4.** Cascaded H-bridge

#### **1.4.1.** Operating principle

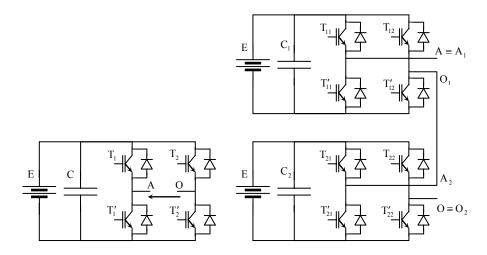

Figure 1.7 shows 3-level and 5-level cascaded H-bridge legs. As usual, the 3-level converter analysis is the simplest and lets understand the operating principle of the modules composing the leg of a generic n-level converter; these modules are often called **cells**. It is well known that H-bridge converters can be modulated with 2-level or 3-level output. In this kind of multilevel converter, all the possible cell output levels are exploited. Some switches configurations are harmful for the converter and they must be avoided; for instance, the switches  $T_1$  and  $T'_1$  are not allowed to be turned on at the same time because this situation causes a shortcut of the source. Table 1.1Table 1.5 shows the relationship between the allowed switches configurations and the output of a 3-level cascaded converter.

| T <sub>1</sub> | T <sub>2</sub> | T <sub>1</sub> ' | T'2 | V <sub>AO</sub> |

|----------------|----------------|------------------|-----|-----------------|

| 1              | 0              | 0                | 1   | Е               |

| 1              | 1              | 0                | 0   | 0               |

| 0              | 0              | 1                | 1   | 0               |

| 0              | 1              | 1                | 0   | - E             |

**Table 1.5:** 3-level cascaded H-bridge leg relationships between configurations and output voltages.

It can be seen that even cascaded converter presents an intra-phase redundancy because there are two different ways to obtain the level 0. Moreover, considering the same DC source voltage, the output level amplitude and the switches reverse voltage drop (given by (1.16)) are greater here than in the diode-clamped or flying-capacitor.

$$V_r = E$$

. (1.16)

In order to increase the number of levels more cells have to be cascaded. High and low couple of switches can be defined in the respect of voltage output direction. Considering Figure 1.7, the couple of switches composed by  $T_1$  and  $T'_1$  is the high one, whereas  $T_2$  and  $T'_2$  constitute the low couple. The high output of one cell is shortcut to the low output of another one to realize a cascade

Figure 1.7: 3-level and 5-level cascaded H-bridge leg.

|                 | Switches state  |                 |                 |           |                  |                   |                  |                 |  |  |  |

|-----------------|-----------------|-----------------|-----------------|-----------|------------------|-------------------|------------------|-----------------|--|--|--|

| T <sub>11</sub> | T <sub>12</sub> | T <sub>21</sub> | T <sub>22</sub> | $T'_{12}$ | T' <sub>12</sub> | $T_{21}^{\prime}$ | T' <sub>22</sub> | V <sub>AO</sub> |  |  |  |

| 1               | 0               | 1               | 0               | 0         | 1                | 0                 | 1                | 2E              |  |  |  |

| 1               | 1               | 1               | 0               | 0         | 0                | 0                 | 1                | Е               |  |  |  |

| 1               | 0               | 0               | 0               | 0         | 1                | 1                 | 1                | Е               |  |  |  |

| 1               | 0               | 1               | 1               | 0         | 1                | 0                 | 0                | Е               |  |  |  |

| 0               | 0               | 1               | 0               | 1         | 1                | 0                 | 1                | Е               |  |  |  |

| 1               | 1               | 1               | 1               | 0         | 0                | 0                 | 0                | 0               |  |  |  |

| 1               | 1               | 0               | 0               | 0         | 0                | 1                 | 1                | 0               |  |  |  |

| 1               | 0               | 0               | 1               | 0         | 1                | 1                 | 0                | 0               |  |  |  |

| 0               | 1               | 1               | 0               | 1         | 0                | 0                 | 1                | 0               |  |  |  |

| 0               | 0               | 1               | 1               | 1         | 1                | 0                 | 0                | 0               |  |  |  |

| 0               | 0               | 0               | 0               | 1         | 1                | 1                 | 1                | 0               |  |  |  |

| 0               | 1               | 1               | 1               | 1         | 0                | 0                 | 0                | - E             |  |  |  |

| 0               | 0               | 0               | 1               | 1         | 1                | 1                 | 0                | - E             |  |  |  |

| 0               | 1               | 0               | 0               | 1         | 0                | 1                 | 1                | - E             |  |  |  |

| 1               | 1               | 0               | 1               | 0         | 0                | 1                 | 0                | - E             |  |  |  |

| 0               | 1               | 0               | 1               | 1         | 0                | 1                 | 0                | - 2E            |  |  |  |

connection between two cells. Each cell in the cascade adds 2 levels more to the output waveform as Table 1.6 shows for a 5-level leg.

Table 1.6: 5-level cascaded H-bridge leg relationships between configurations and output voltages.

Applying Kirchhoff's voltage law to the 5-level leg, the total output voltage  $V_{AO}$  results to be the sum of single cell output voltages as (1.17) shows for a converter composed by m cells each one supplying an output voltage  $V_{AO}$ .

$$V_{AO} = \sum_{j=1}^{m} V_{AOj}$$

(1.17)

Unfortunately, one more insulated source is required for each cell in the cascade to eliminate possible shortcuts. For example, considering a 5-level converter and the last configuration of Table 1.6, switches  $T'_{21}$  and  $T'_{12}$  make a shortcut of the lowest source if it is not insulated from the upper one.

A direct comparison between this cascaded converter and other multilevel topologies presented till here cannot be done because of different level amplitude. Imagining a substitution of the converter in an existing system, the better comparison hypothesis is to adapt the DC bus for the new converter keeping the same voltage value and splitting it. In this way, the voltage step amplitude for a n-level diode-clamped or flying-capacitor is given by (1.13) where E is the total bus DC voltage. Whereas the voltage step amplitude of a cascade converter is given by (1.18).

$$\frac{2E}{n-1}$$

. (1.18)

The cascade H-bridge was the founder of cascade converter family and the simplest one. Each type of single-phase multilevel converter can be cascaded to obtain a leg. In this way, the levels each cell adds increase and is a good compromise between the required insulated sources and the number of output levels.

#### **1.4.2.** Characteristics

Cascade H-bridge converter is a very modular solution based on a wide commercialized product. This has a good repercussion on the reliability and the maintenance of the system since the cells have high availability, intrinsic reliability and a relatively low cost.

The main disadvantage of this converter consists in requiring several insulated sources that are not available in all applications. For instance, there are high costs in making insulated sources for induction motor drive systems because it requires isolation transformers. At the same time, this disadvantage makes cascade converters more suitable for photovoltaic or battery fed applications than the other types. Indeed, photovoltaic panels can easily be rearranged in several insulated sources to feed cascade H-bridge cells. A similar operation can even be done with battery banks.

Moreover, the insulated sources can be substituted with capacitors when the converter is used as active filter. In such kind of applications, the active power through the converter is theoretically zero, so there is no need to have power sources. Anyway, the converter has its own losses and the capacitors have to supply a little active power that discharges them. A simple control, sensing the voltage of each capacitor and exploiting either the intra-phase or joint-phase redundancies, can be done to avoid this problem. In this way, the active power to feed the converter is absorbed from the net and the capacitors feed reactive power only.

There are other several application dependent ways to exploit intra-phase redundancy proper of this converter. As an example, considering a three-phase system and a vector modulation, control can choose among the redundant configurations the one which needs the fewest commutations to be reached.

While there are no limitations on the level of diode-clamped or flying-capacitor, which can be even or odd, cascade H-bridge can have only odd numbers of levels; indeed the first cell gives three levels whereas the others always add two levels more.

### **1.5.** Multi Point Clamped (MPC)

#### **1.5.1.** Operating principle

**Multi Point Clamped** (**MPC**) are so called since in their architecture there are several points clamped to specific voltages using some components. Even diode-clamped converter belong to this family because the bus between two switches is clamped by a clamping diode. Furthermore, when

Figure 1.8: 3-level and 5-level Multi Point Clamped leg.

the number of voltage level is odd, the converters are called **Neutral Point Clamped (NPC)** because the neutral point is clamped. For the purpose of this book, MPC is used to univocally refer to the converters presented in Figure 1.8. In [31], a 4-level MPC converter is presented for UPS application showing a comparison with a 4-level diode-clamped. The 3-level leg is identical to a 3-level diode-clamped and Table 1.1 gives its modulation law. The two topologies can be told apart only when the output levels are more than three. As Figure 1.8 shows, the 5-level leg is completely different: in MPCs the voltages are clamped using couples switch-diode instead of using a simple diode.. Anyway, given a number of levels, the number of switches needed by MPC is the same needed by diode-clamped. The control of MPC leg is more complicated in the respect of other topologies. Even this kind of converter allows to find complementary couples of switches, as shown in Figure 1.8. The constrain so introduced is not physiologically necessary, but it is a simple way to simplify the control scheme and the switching table.

| $T_1$ | T <sub>2</sub> | T <sub>3</sub> | $T_4$ | $T_1'$ | T <sub>2</sub> ' | T <sub>3</sub> ' | T4 | V <sub>AO</sub> |

|-------|----------------|----------------|-------|--------|------------------|------------------|----|-----------------|

| 1     | 1              | 1              | 0     | 0      | 0                | 0                | 1  | Е               |

| 1     | 1              | 0              | 1     | 0      | 0                | 1                | 0  | 3E/4            |

| 1     | 0              | 1              | 0     | 0      | 1                | 0                | 1  | E/2             |

| 1     | 0              | 0              | 1     | 0      | 1                | 1                | 0  | E/2             |

| 0     | 0              | 1              | 0     | 1      | 1                | 0                | 1  | E/4             |

| 0     | 0              | 0              | 1     | 1      | 1                | 1                | 0  | 0               |

Table 1.7: 5-level MPC leg relationships between configurations and output voltages.

Furthermore, to avoid shortcut,  $T_3$  and  $T_4$  must be complementary controlled. The same must happens for  $T'_3$  and  $T'_4$ . Table 1.7 is a possible switching table for a 5-lrvel MPC leg; there is an intra-phase redundancy only for the middle level. Anyway, it is better to have  $T_4$  turned on in order to limit the reverse voltage drop upon  $T_2$ . In this way, Table 1.7 looses one configuration.

The study of the modulation of this leg is quite complicated and introduces particular switching functions fully discussed in [32, 33]. Dependently on the switching table used, the maximum reverse voltage drop over the components changes and a preliminary analysis must be done to choose the suitable component. Moreover, the switches in the middle of the leg must carry twice the voltage of the others.

#### **1.5.2.** Characteristics

The main disadvantage of MPC is complex control they require. A specific hardware is necessary to implement the control: for instance a multilevel PWM comparator (analog or digital) can give the level required, but a proper switching table, implemented in a E<sup>2</sup>PROM, must convert it in gate signals which define the leg configuration.

On the other hand, given a number of output levels, the number of components required for MPC is the lowest among all multilevel converters. This has a good repercussion on its production and maintenance costs.

Moreover, a comparison between MPC and diode-clamped can be done considering the path of the load current. Considering the scheme of 5-level converter presented in Figure 1.4, the load current has always to flow through four components among diodes and switches. In 5-level MPC of Figure 1.8 the greatest number of components through which the load current has to flow is three. There is a difference of one component which can be significant in the computation of losses and efficiency.

Regarding the portability, this converter is fully equivalent to a diode-clamped because the two topologies present the same DC bus structure.

### **1.6.** Other topologies

#### 1.6.1. Hybrid converter

All the multilevel converters presented in this paragraph are derived from the basic topologies. They are called hybrid topologies because they are a mongrel between two basic topologies or they are even composed by the same topology, but with different modulations of the stages.

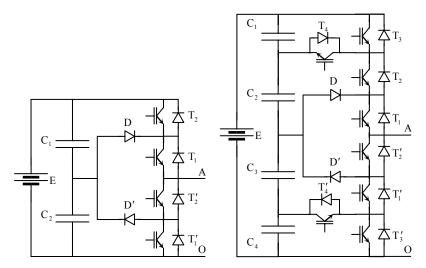

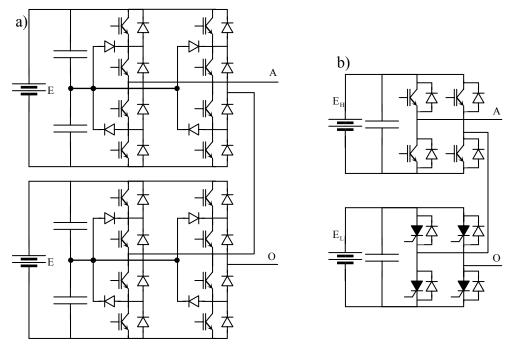

**Mixed-level hybrid multilevel cells** [29] belong to this family. In this kind of converter, the Hbridge cells of cascaded leg are substituted by diode-clamped or flying-capacitor. Mixed-level hybrid multilevel cells converter is well suited for high-voltage high-power applications because of the reduction of required insulated sources in the respect of a cascade H-bridge with the same number of output levels. Figure 1.9a) shows a 9-level converter implemented using two diodeclamped cells.

When the cells have different DC bus voltages, the converter is called **asymmetric hybrid multilevel cells** [29]. In this way, the cells can also have different switching frequencies allowing the use of low frequency devices like GTO. A 5-level converter composed by one IGBTs and one GTOs H-bridge cell is presented in Figure 1.9b). Considering the leg presented, the lowest cell is modulated with a low frequency, but drives the greatest voltage. In this way, its output is kept constant for a long time in the period, switching only four times. The upper cell is used to compensate the output to obtain the reference. This structure works properly only if (1.19) is complied.

$$E_{L} = 2E_{H}.$$

(1.19)

Figure 1.9: Hybrid converters; a) Mixed-level cells; b) Asymmetric cells.

#### **1.6.2.** Soft-switching converters

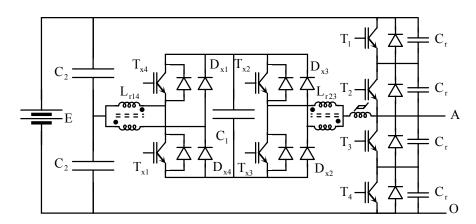

Soft switched multilevel inverters are presented in literature [29, 33-46] considering several different implementations. The aim of soft-switch inverters is to reduce the switching losses increasing the efficiency of multilevel converters. For the cascade inverter, because each inverter cell is a 2-level circuit, the implementation of soft-switching is not at all different from that of conventional 2-level inverters. For diode-clamped or flying-capacitor inverters, however, the choices of soft-switching circuit can be found with different circuit combination [34-40]. Although, zero-current switching is possible [41], most literature proposed zero-voltage-switching types including Auxiliary Resonant Commuted Pole (ARCP), coupled inductor with Zero-Voltage Transition (ZVT) and their combinations. Figure 1.10 shows an example of combining the ARCP and coupled-inductor ZVT techniques for a flying-capacitor 3-level inverter.

The auxiliary switches  $T_{x2}$ ,  $T_{x3}$ ,  $D_{x2}$  and  $D_{x3}$  are used to assist the inner main switches  $T_2$  and  $T_3$  to achieve soft-switching. With  $L_{r23}$  as coupled inductor, the bridge-type circuit formed by  $T_{x2}$ ,  $T_{x3}$ ,  $T_2$  and  $T_3$  forms a 2-level coupled-inductor ZVT. The basic principle of a 2-level ZVT can be found in [42-46]. For the outer main switches, the soft-switching relies on  $T_1$ ,  $T_4$ ,  $T_{x1}$ ,  $T_{x4}$ ,  $D_{x1}$  and  $D_{x4}$ , coupled inductor  $L_{r14}$  and split-capacitor pair  $C_2$  to form an ARCP type soft-switching inverter. Detailed soft-switching circuit operation for inner and outer devices can be found in [34-36].

Figure 1.10: Zero-voltage-switching flying-capacitor inverter circuit.

#### **1.6.3. Dual 2-level 3-phase cascade inverters**

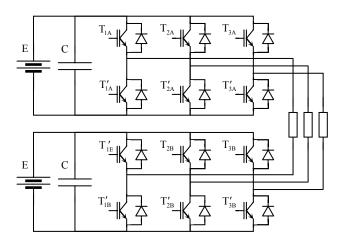

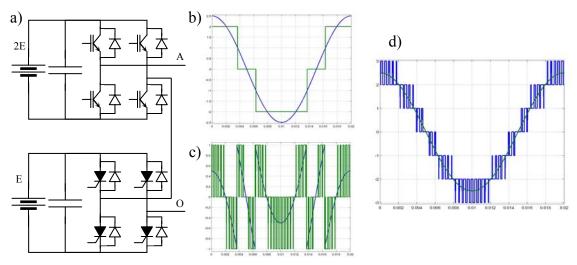

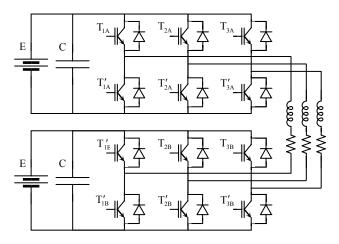

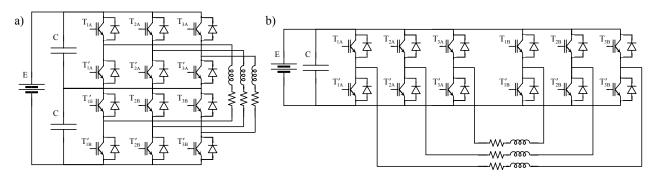

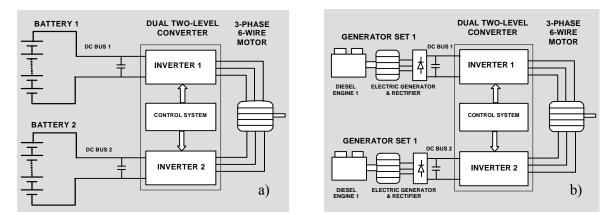

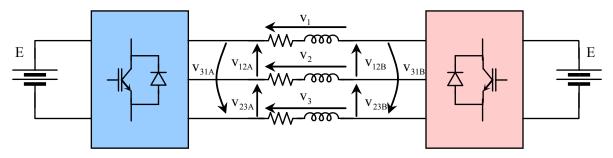

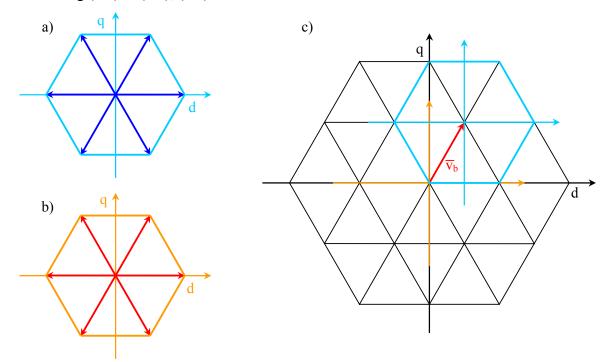

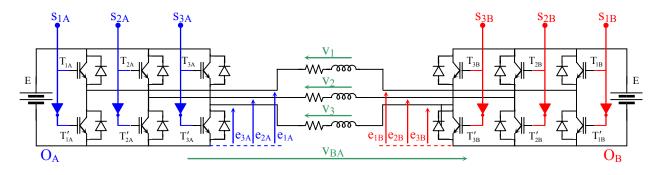

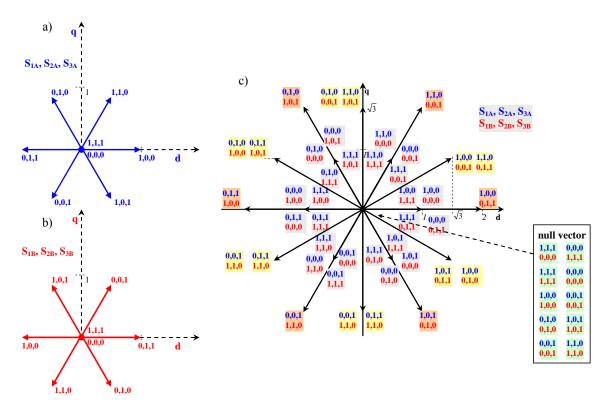

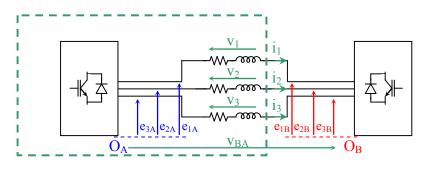

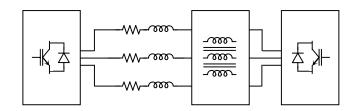

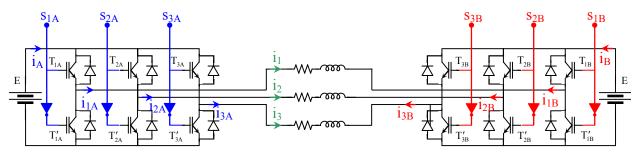

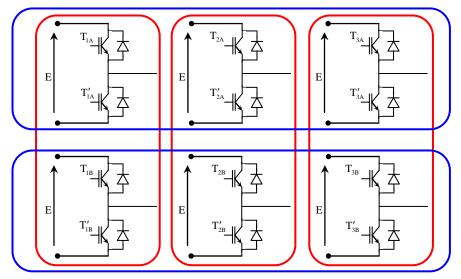

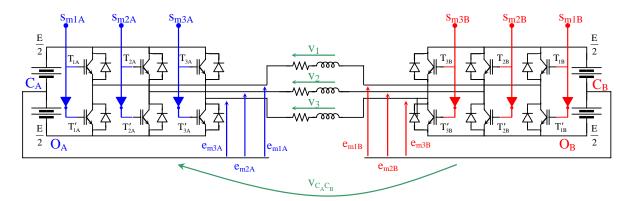

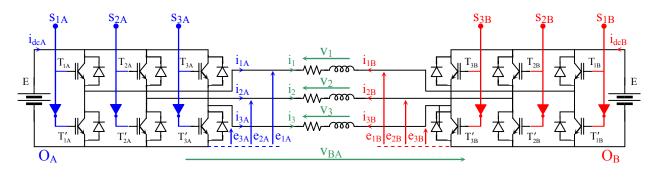

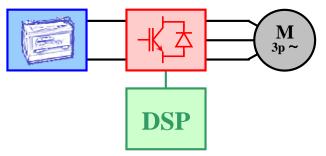

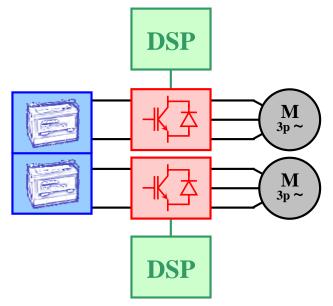

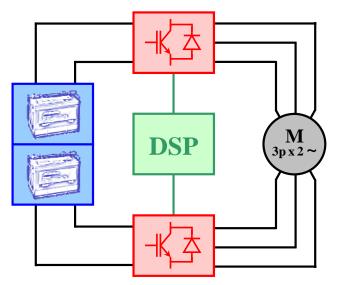

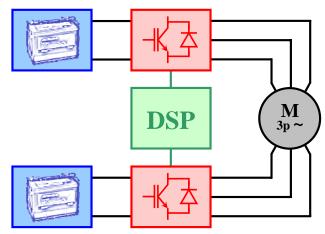

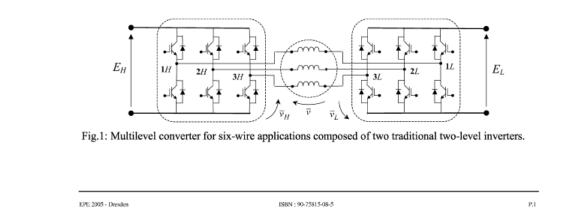

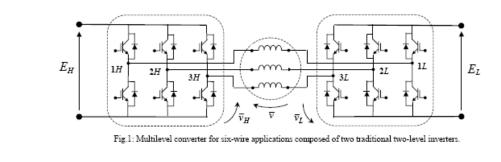

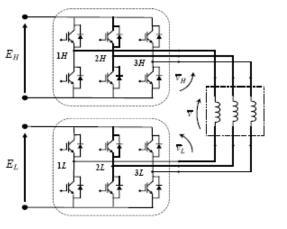

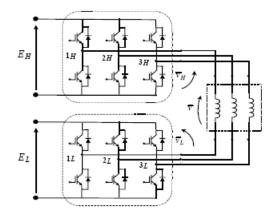

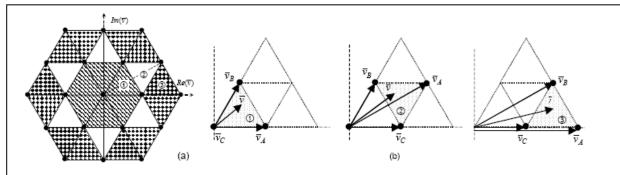

In Figure 1.11, another interesting multilevel topology is implemented cascading two standard 3-phase inverters with a six-wire open-end load in between [47-50]. It is equivalent to a 3-level 3-phase converter which will require three insulated sources if it is implemented as cascade H-bridge. In this way, the required insulated sources are only two. Moreover, the converter is composed by wide commercialized and very reliable parts which make its implementation quite easy. It is well suited for automotive applications in which splitting the batteries bank is possible.

A commercial DSP can easily drive this architecture which requires only six independent gate signals provided by microcontrollers designed for standard back-to-back applications.

Unfortunately, the number of levels can not be increased because there is no way to cascade more than two 3-phase inverters. Furthermore, the insulation between the two sources is critical for

Figure 1.11: Dual 2-level 3-phase cascade converter.

the correct multilevel operation of the system because the common mode current flow must be avoided.

In [47] a solution to cut off one sources is presented. However four auxiliary switches are needed to break the common mode current path when the applied voltage has a common mode component; obviously, the control became more sophisticated. Another possibility to avoid common mode current flow, when the inverter is fed by only one source, is presented in [49]. The modulation applies only 3-phase voltages with zero common mode. In this way the available output vectors coincide with the vertices of a hexagon, like for standard 3-phase inverters, but they are doubled: there is an augmentation of the delivered power, but the quality of the output does not better.

# Chapter 2

# **Multilevel modulation**

## 2.1. Introduction

#### 2.1.1. General considerations

In this chapter, several multilevel modulation strategies are discussed to introduce the reader in this charming world which is grooving more and more. The high number of switches composing a multilevel converter may lead to the conclusion that complex algorithms are necessary. Fortunately, all the modulation used for standard 2-level converters can be easily adapted to multilevel converters.

The modulation algorithm used to drive the multilevel converter has to be aimed to give the voltage level required for each leg; the translation in the proper switches configuration is done by other algorithms which can be hardware or software implemented. For instance, an inverter application using a MPC converter can be considered; furthermore it is supposed that the output voltage level is given by an analogue multilevel PWM (Section 2.4). The modulating signals can not directly drive the switches because they are not logically compatible, but they can be considered like a ROM address and used to get back stored configurations. In this way, all the modulation algorithm presented in this chapter can be used in all multilevel applications.

Actually, there are some modulation algorithms which produce outputs suited for particular multilevel topologies like the **multi-carrier based PWM** (Section 2.4) and the diode-clamped converters: in this case, the modulating signals are logically compatible with the required switches configuration which can be directly driven.

Moreover, the selection among redundant configuration is not a duty of the modulation algorithm. First of all, the aim of redundant configurations must be defined for the application. After determining the voltage applied to the load, the control system can choose among all the possible configurations the best one to accomplish the defined purpose. The aims of redundant configurations choice are many: it is possible to balance capacitors charges, to improve the switching pattern, to balance the current flowing through the switches and so on. Nevertheless redundant configurations by them selves represent the same state of the converter and their choice must be secondary in the respect of applying the correct output voltage, even when it is critical.

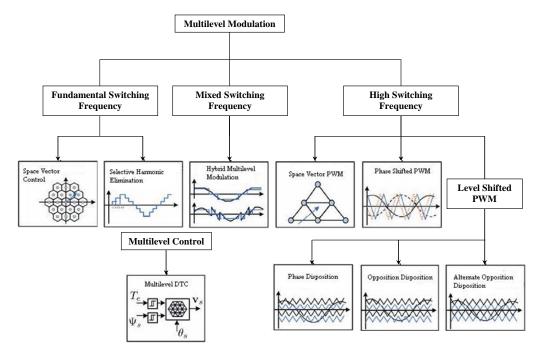

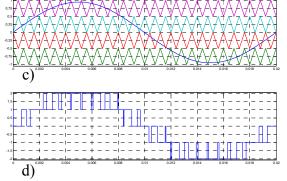

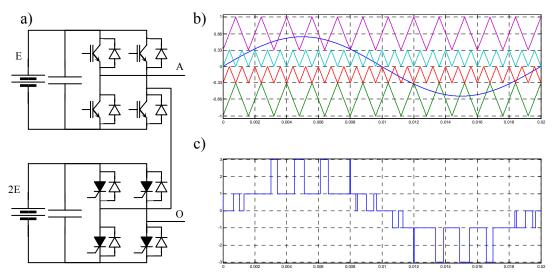

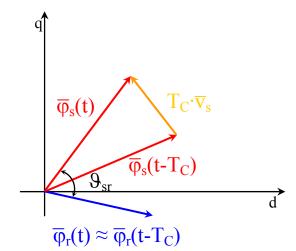

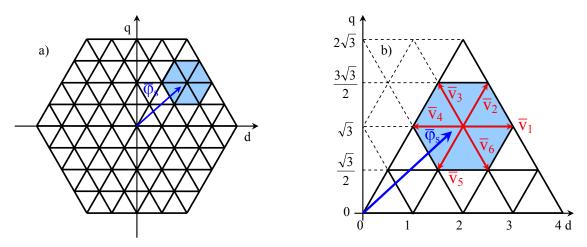

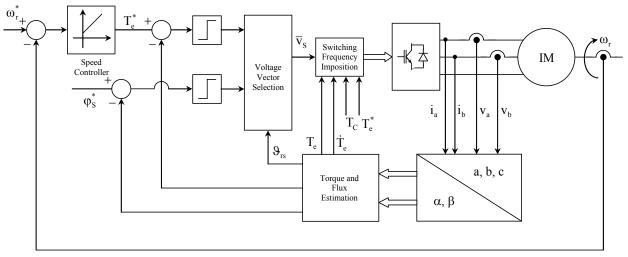

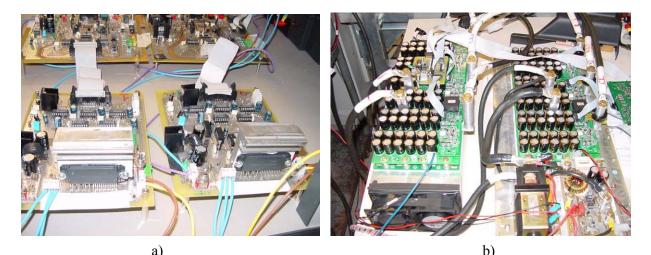

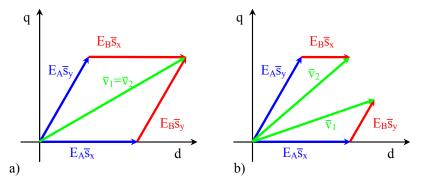

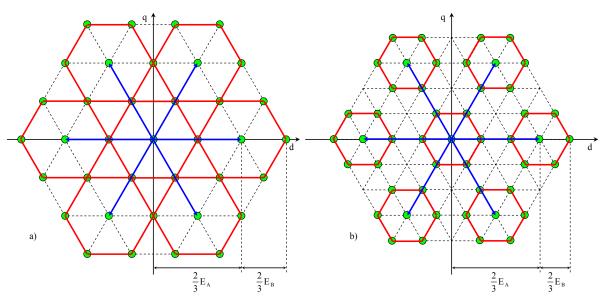

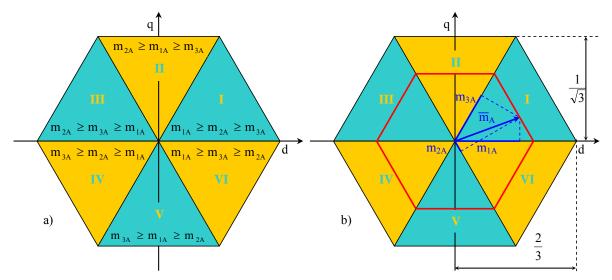

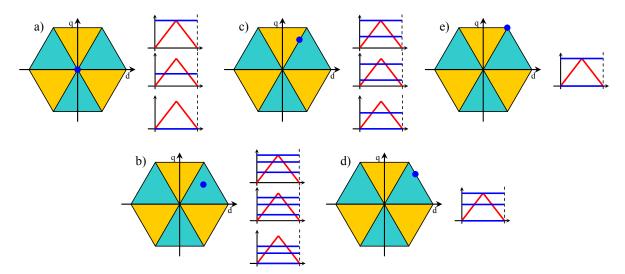

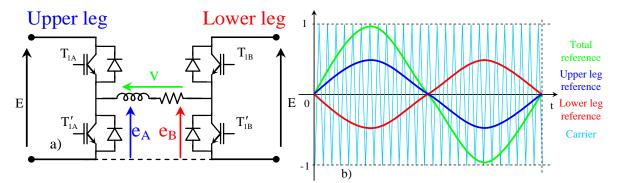

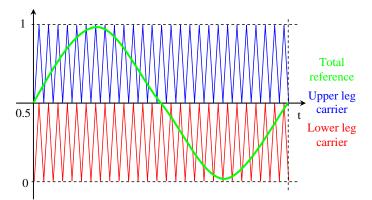

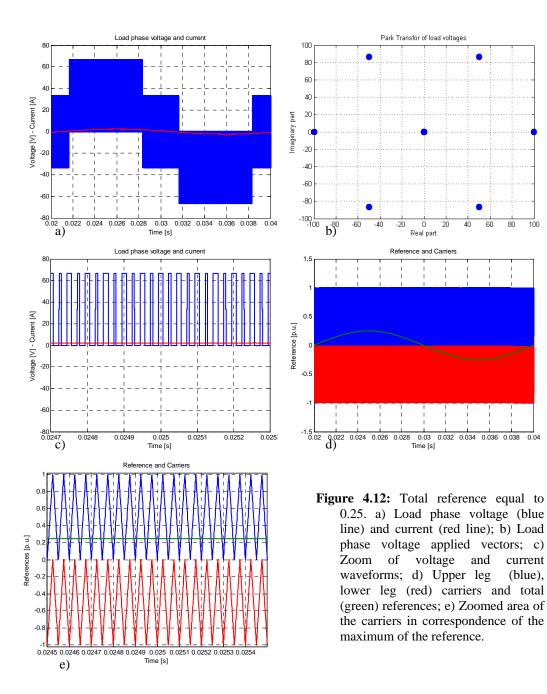

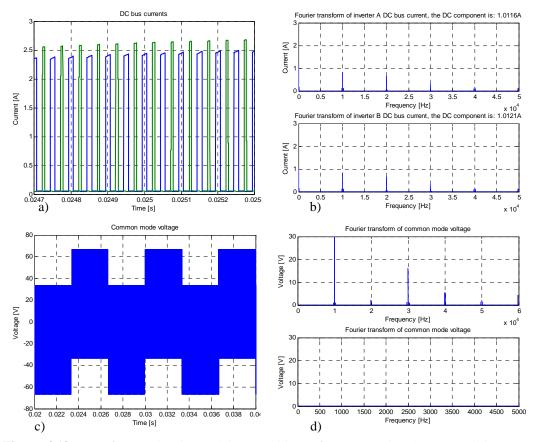

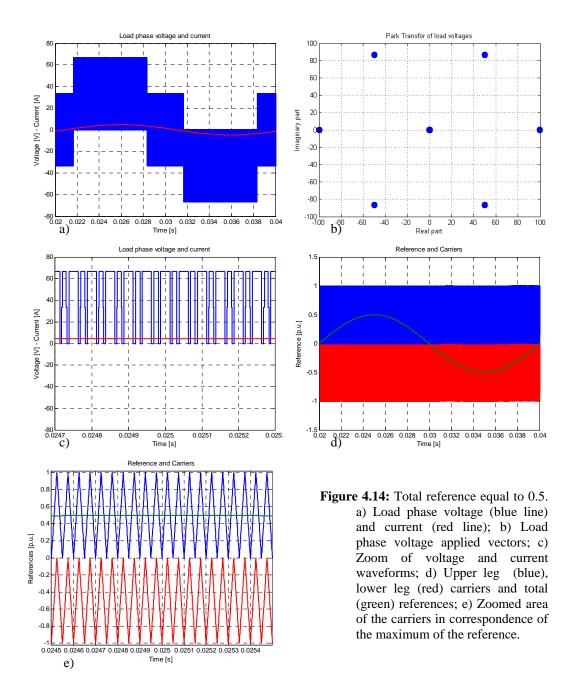

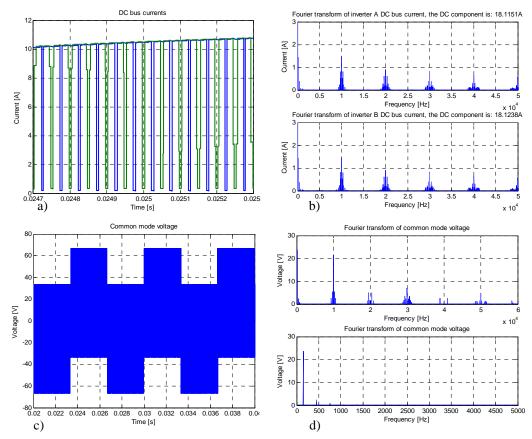

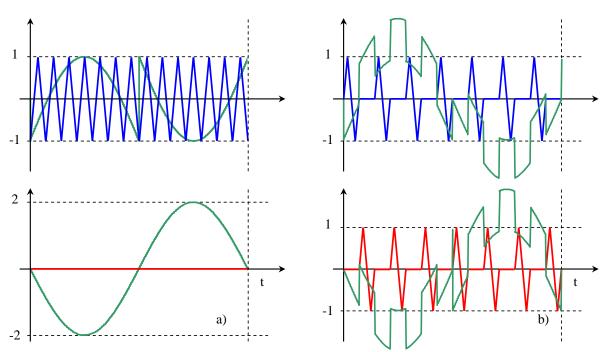

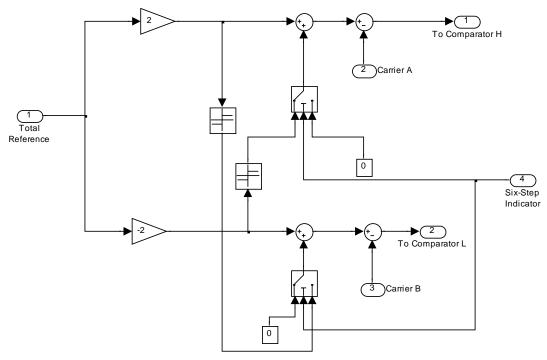

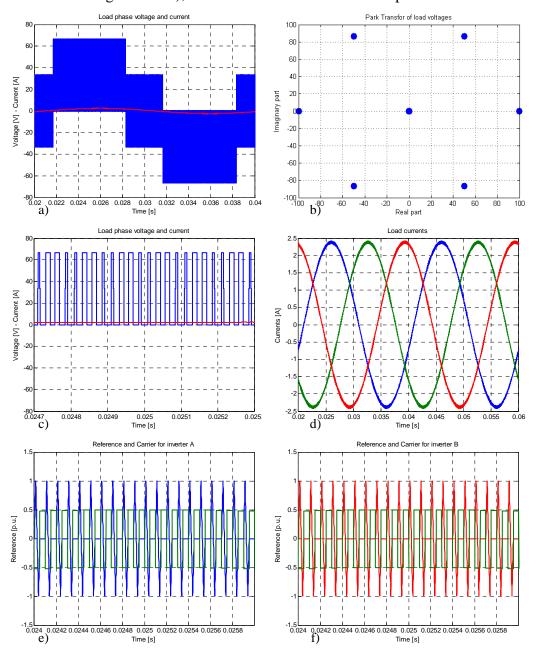

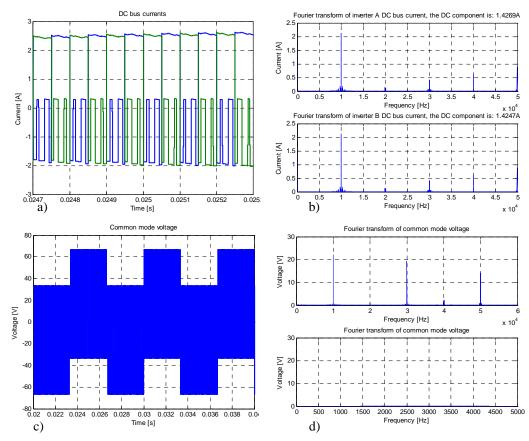

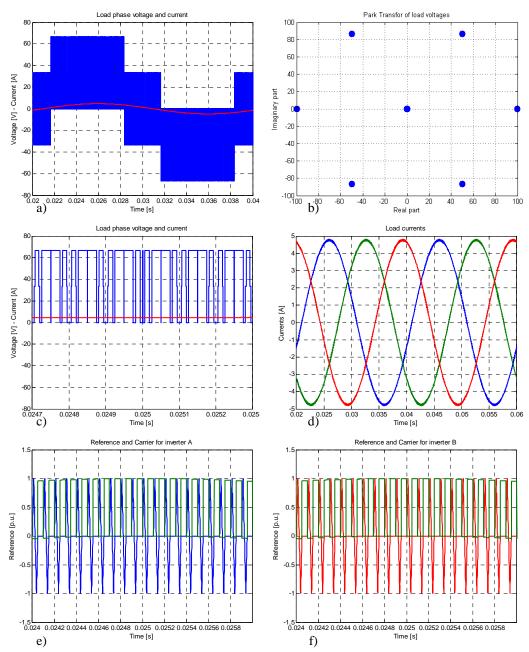

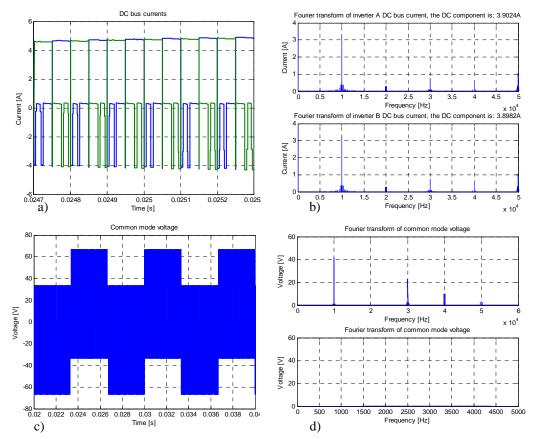

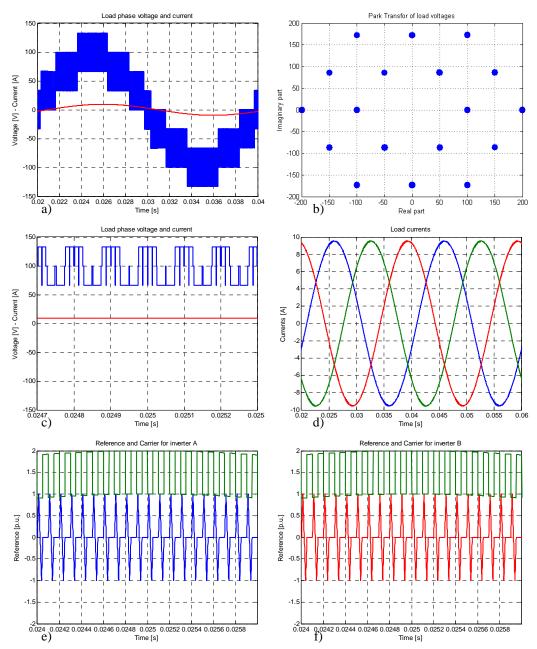

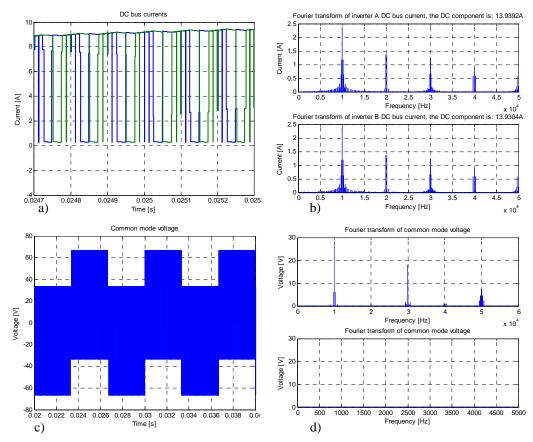

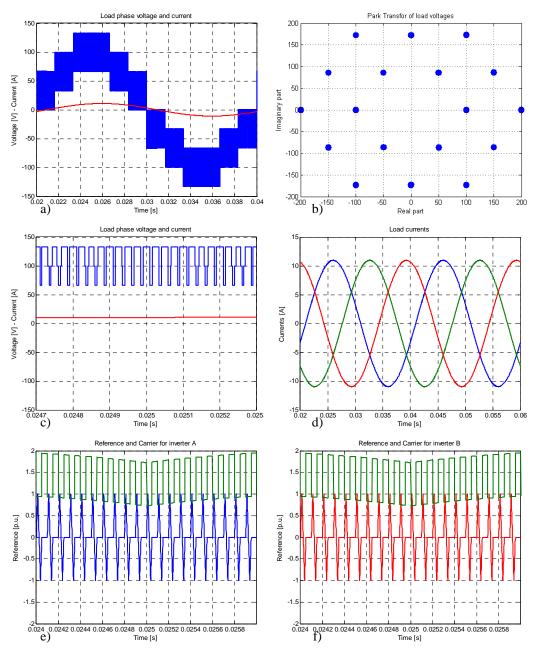

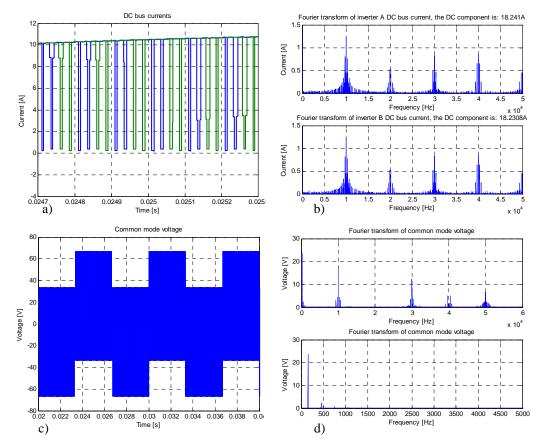

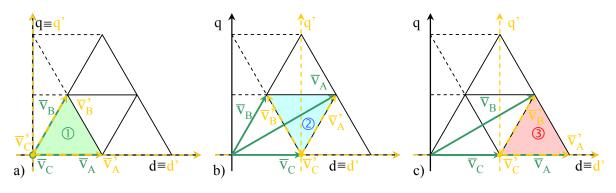

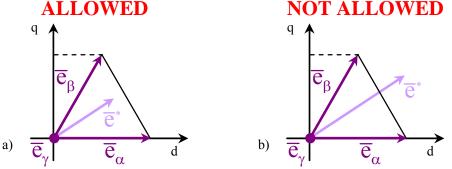

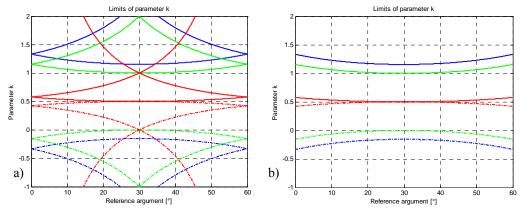

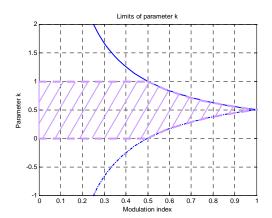

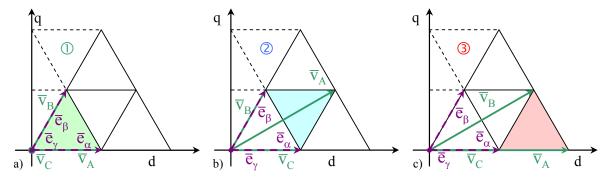

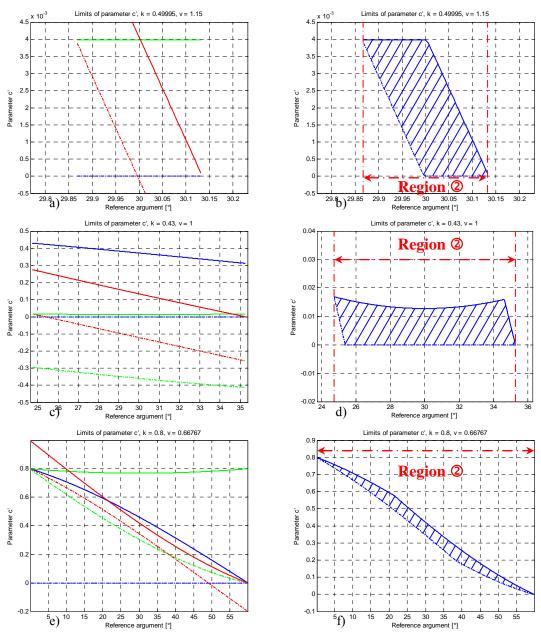

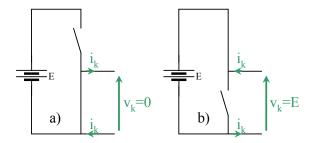

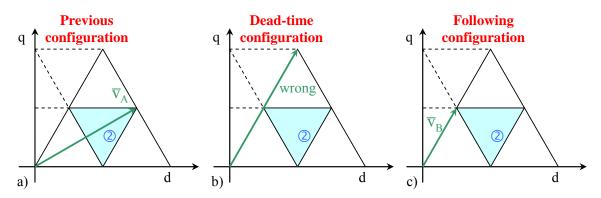

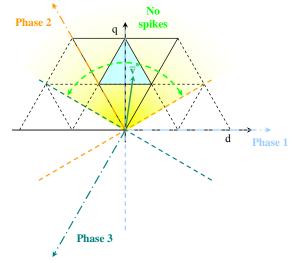

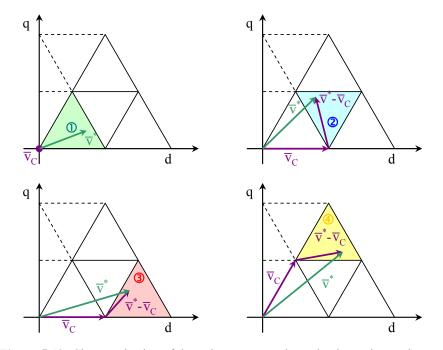

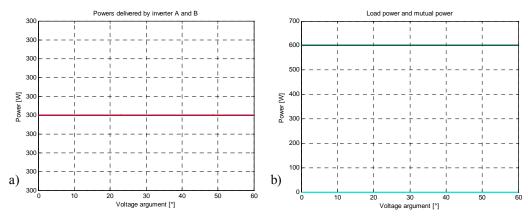

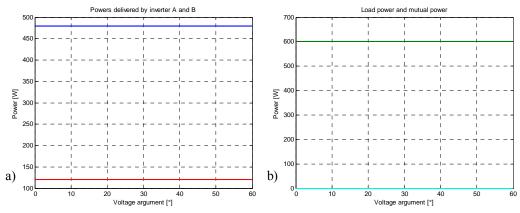

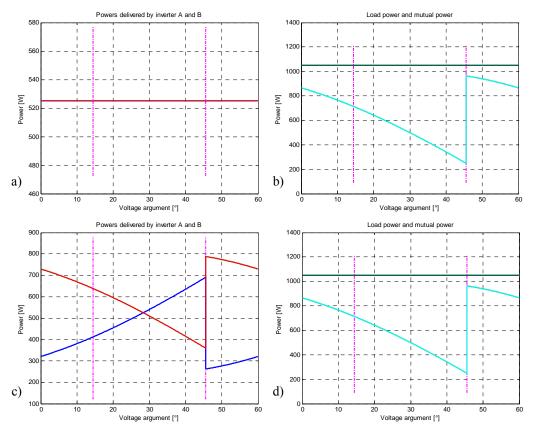

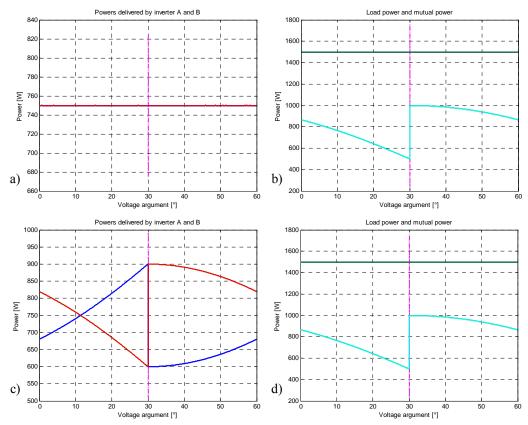

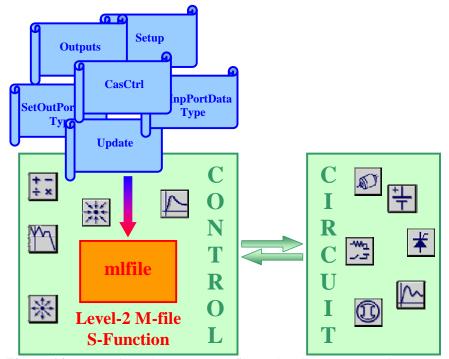

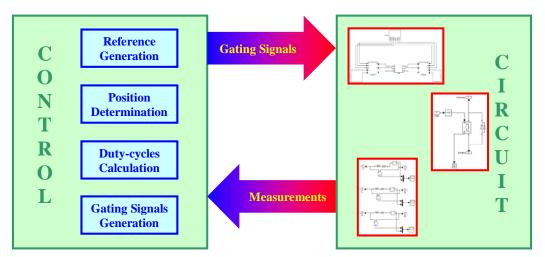

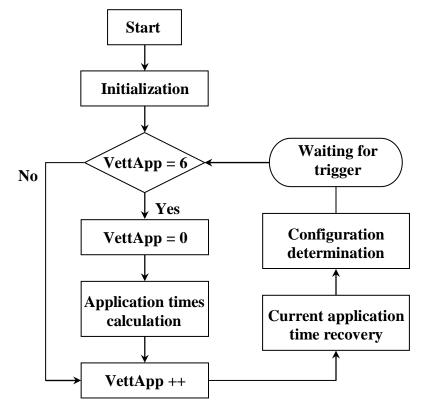

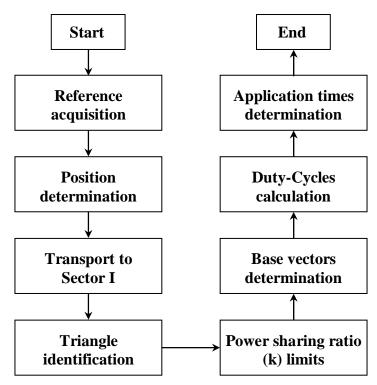

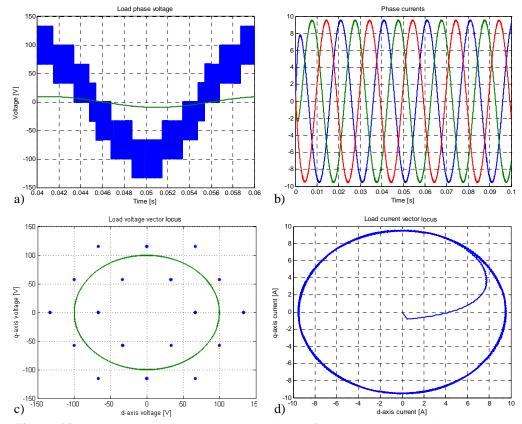

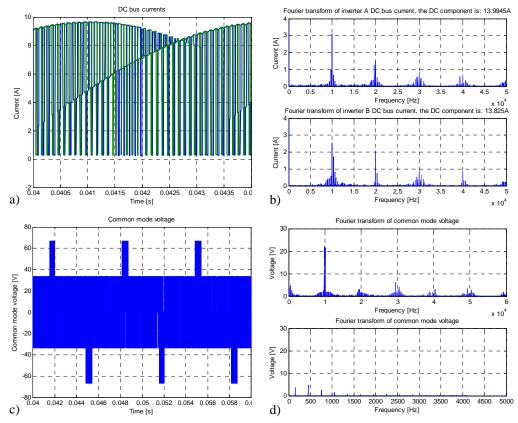

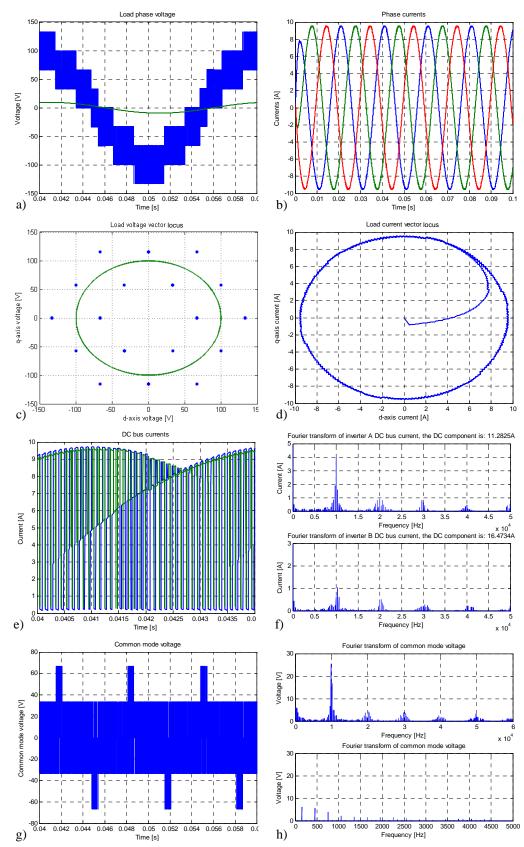

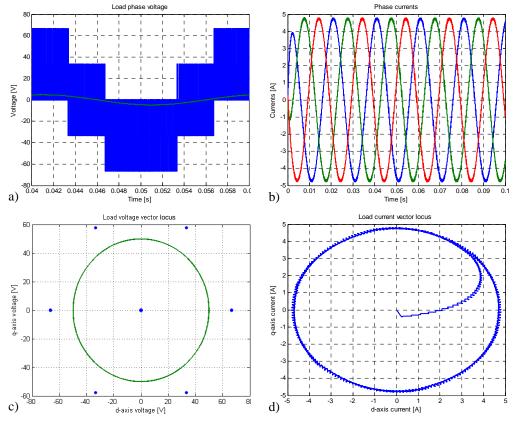

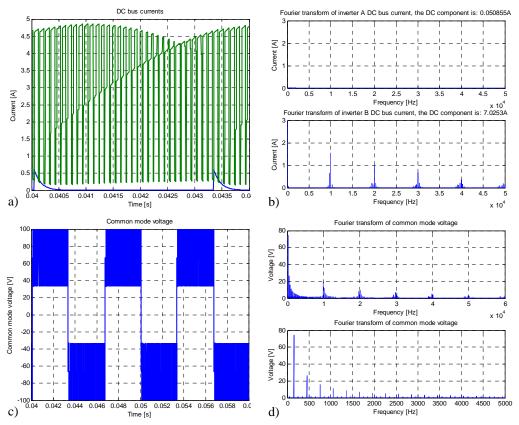

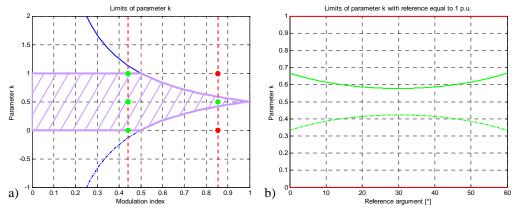

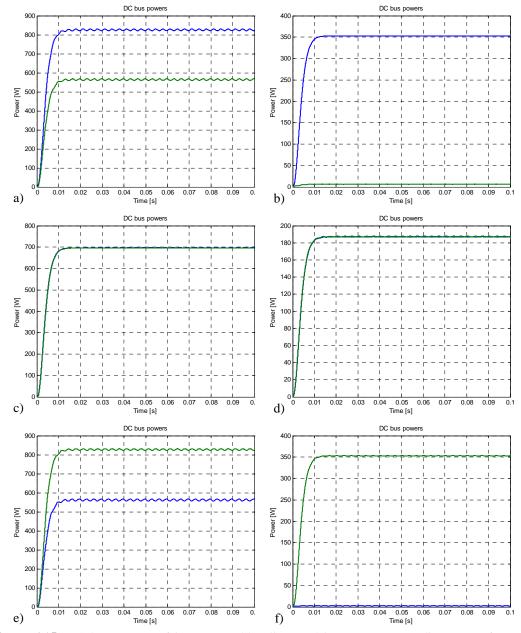

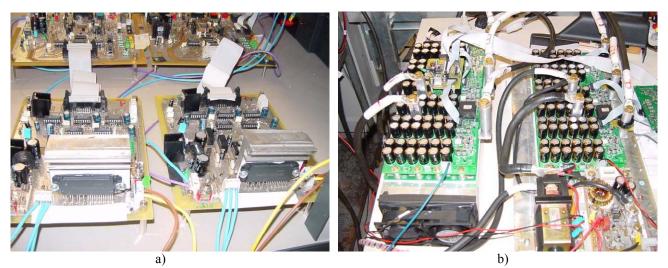

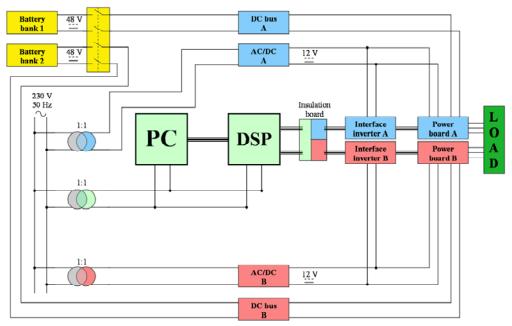

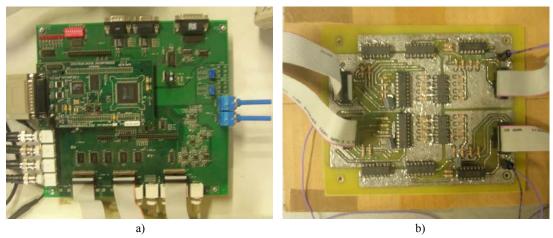

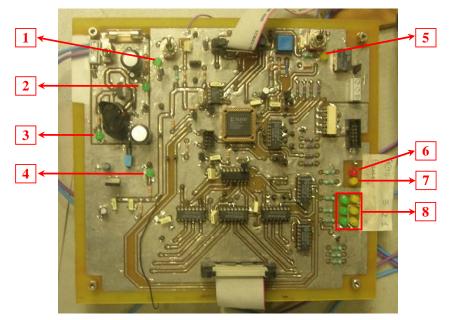

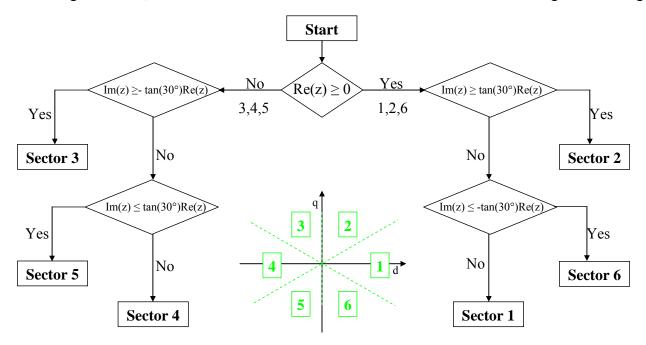

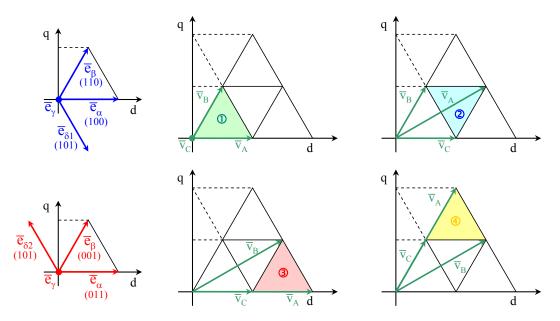

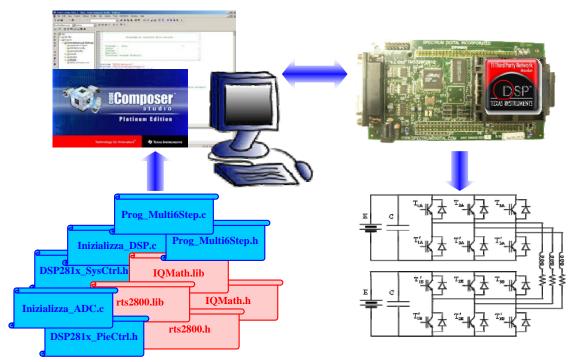

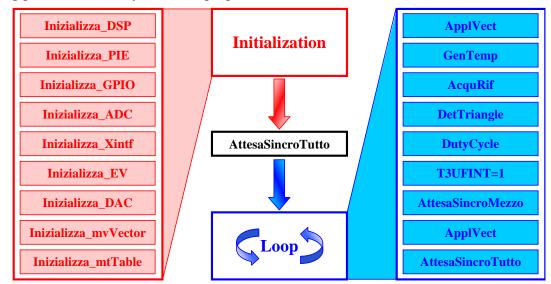

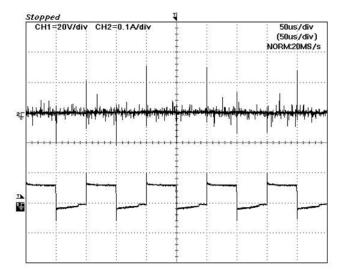

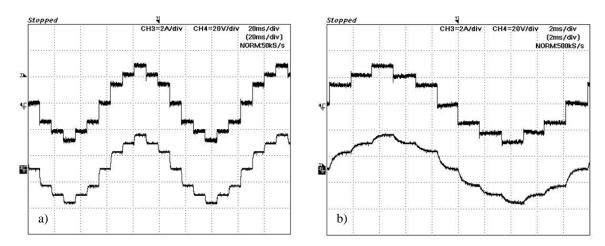

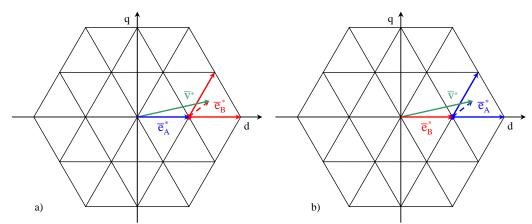

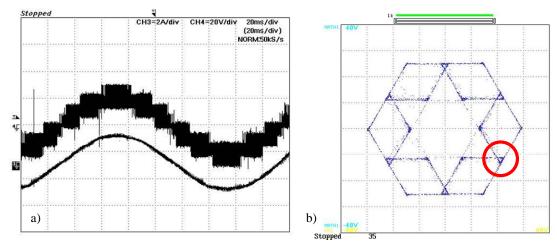

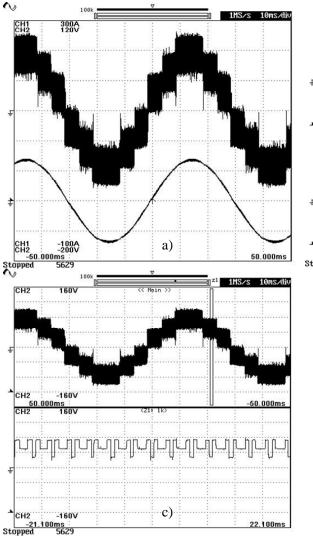

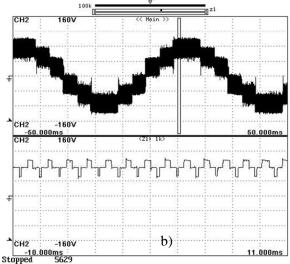

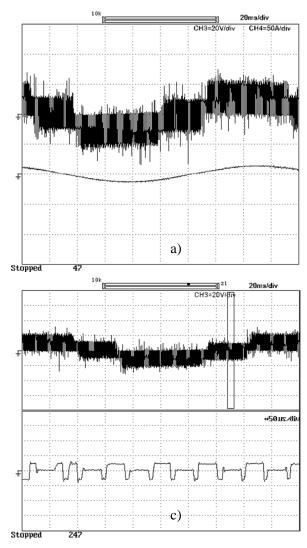

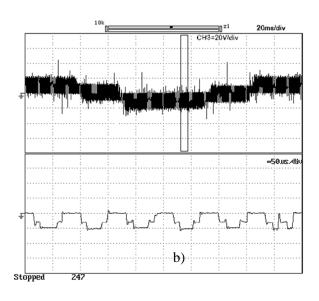

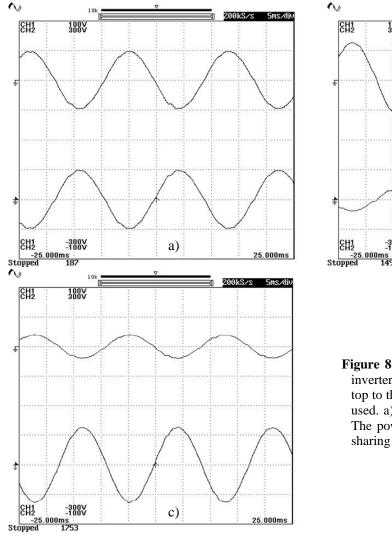

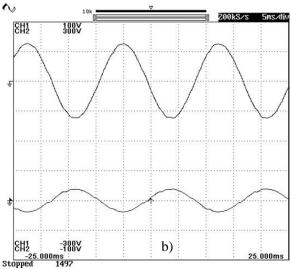

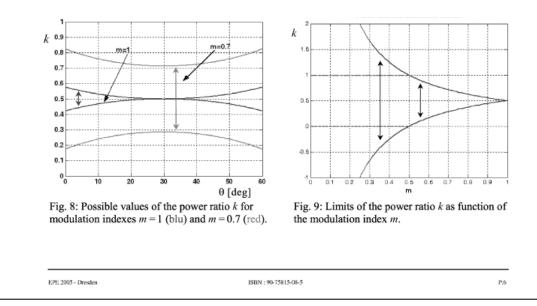

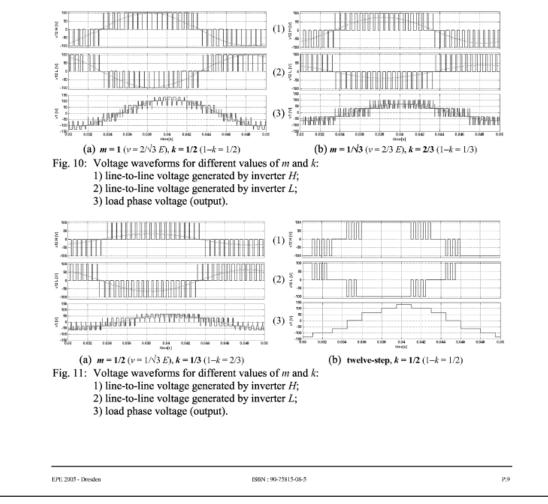

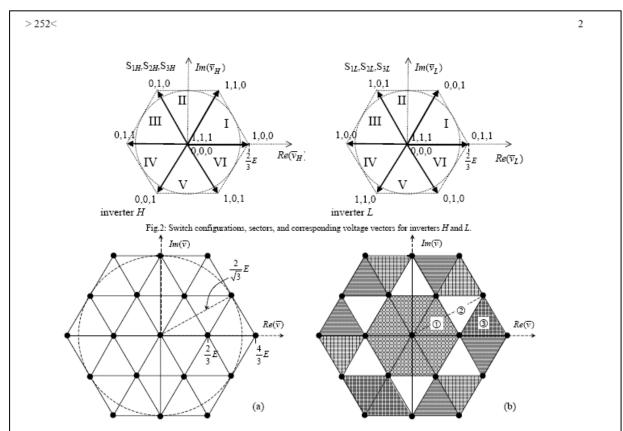

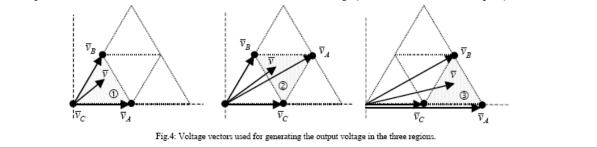

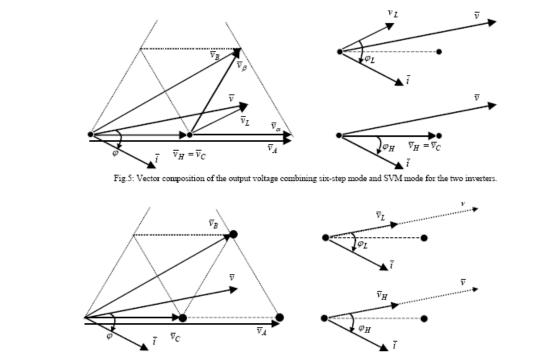

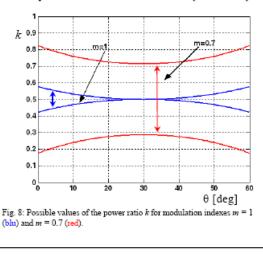

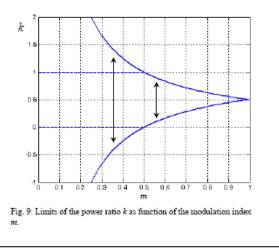

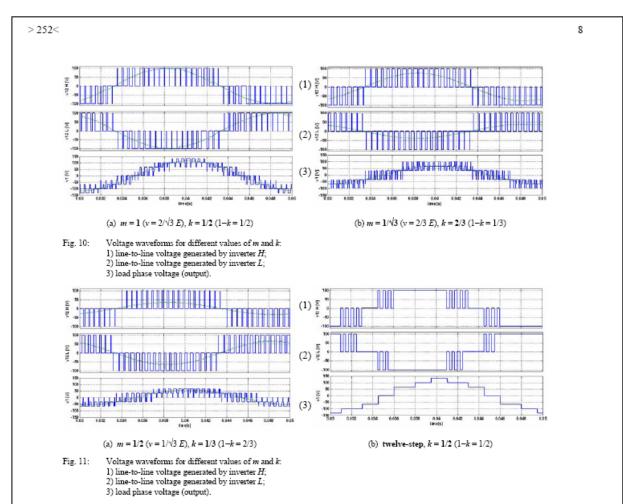

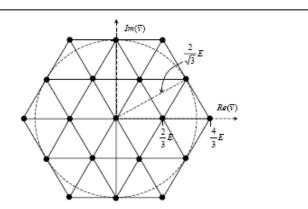

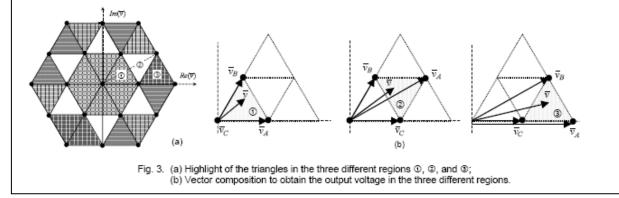

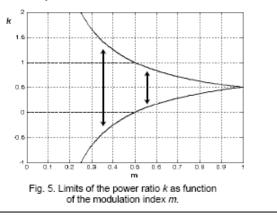

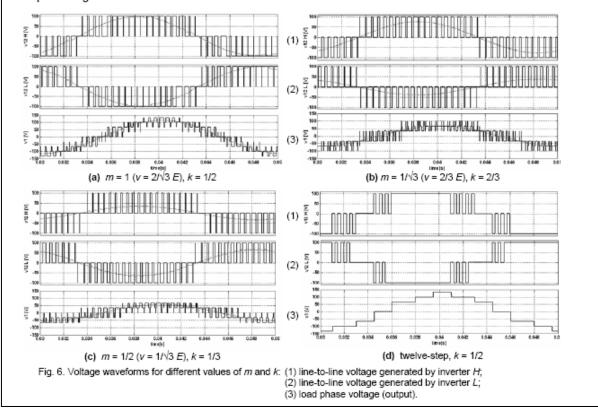

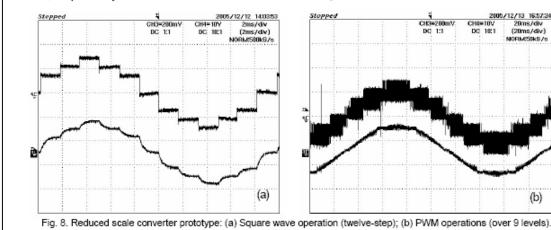

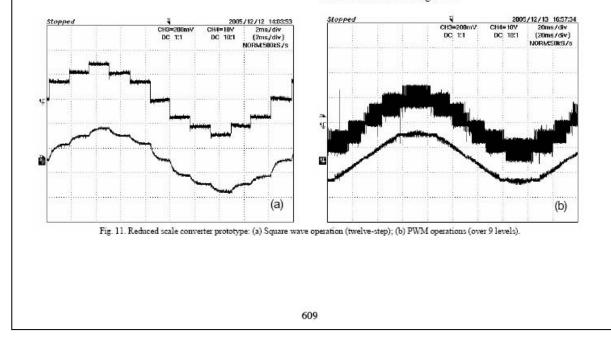

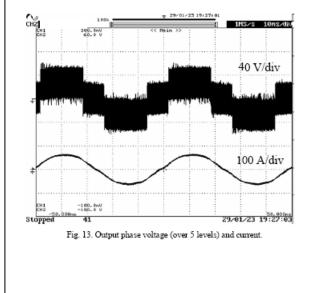

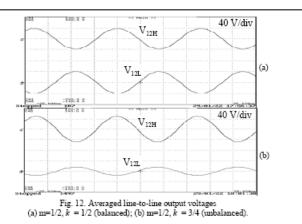

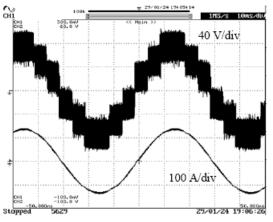

#### 2.1.2. Modulations classification