#### DOTTORATO DI RICERCA IN

# INGEGNERIA ELETTRONICA, TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE

Ciclo 37

Settore Concorsuale: 09/E3 - ELETTRONICA

Settore Scientifico Disciplinare: ING-INF/01 - ELETTRONICA

#### EFFICIENT SOLUTIONS FOR GAN POWER AMPLIFIERS

Presentata da: Simone Cangini

Coordinatore Dottorato Supervisore

Davide Dardari Alberto Santarelli

Co-supervisore

Corrado Florian

### Abstract

Over the past decade, wireless applications have grown exponentially, driven by demand across sectors like cellular networks, vehicular communication, and industrial systems. The affordability of sensors and improvements in energy efficiency have fueled the deployment of billions of connected devices. At the same time, the rise of smartphones and wireless internet has created challenges for higher data rates and broader coverage. The transition from 4G to 5G technology has addressed these needs, with 5G offering enhanced reliability, low latency, and cost-effective solutions. The introduction of millimeter-wave frequencies is mandatory to achieve the gigabit-level wireless traffic required. However, mm-wave signal attenuation requires increased power amplification, which adds to network power consumption.

RF power amplifiers (PAs), essential for boosting signals, face challenges with high peak-to-average-power-ratio (PAPR) signals common in modulated transmissions used to maximize spectral efficiency. This issue is particularly critical for 6G technology, which demands extreme linearity, power efficiency, and thermal management to operate in terahertz (THz) bands and deliver speeds up to 1 Tbps. New semiconductor technologies are expected to address these challenges, particularly Gallium Nitride (GaN), which offers an overall high power density, particularly promising when high integration is of interest. In combination with that, the ability to dynamically adjust the power amplifier performances or the possibility to let the PA operate at multiple bands is desirable for modern standards. Many topologies and clever solutions already address this objective but when more bandwidth or higher frequencies are employed, more challenges prevent these solutions from breaking through the market.

This Thesis addresses these challenges by investigating two key areas to improve the efficiency of GaN PAs. First, it delves into the impact of trapping effects, which can significantly degrade device performance, particularly with modern high-modulation schemes. A new characterization technique is developed, based on drain current transient (DCT) measurements, to assess figures of merit such as gate and drain lag, trap activation energy, cross-section, and carrier density reduction. This approach reduces ii ABSTRACT

characterization time while providing valuable insights into the relationship between the physical structure of HEMTs and their susceptibility to trapping effects. This allows for more informed decisions when selecting GaN devices for specific applications.

The second area of focus is the integration of varactor devices into the output matching network of PAs to achieve reconfigurable amplifier architectures. To fulfill this goal, a preliminary characterization is required before new devices can be adopted. This study is conducted over existing diodes in GaN-on-SiC technology to assess the use of integrated solutions instead of discrete ones to reduce the impact of parasitics. After this preliminary research, the extraction of suitable models to allow CAD simulations is required. A novel automatic modeling procedure, employing vector network measurements, is developed to accurately characterize and model varactor device behavior. This procedure generates a lumped-element circuit representation, facilitating the simulation and optimization of the matching network for improved PA efficiency and adaptability. A matching network integrating varactors is also proposed and a preliminary evaluation of PAs with modified varactor devices is presented.

## Acknowledgments

Pursuing my Ph.D. was a challenging yet profoundly enriching experience.

I had the opportunity to engage with many individuals who provided both professional guidance and meaningful conversations. Real gratitude goes to Prof. Alberto Santarelli and Prof. Corrado Florian for their patient supervision and constant motivation. Beyond the scientific advice, their support in navigating bureaucratic and financial matters was crucial throughout the entire period. I would also like to thank Prof. King and Prof. Martín-Guerrero for their valuable comments and feedback, which were instrumental in improving this thesis.

The Electronic Design and Measurement for RF and Industrial Applications (EDM) research group has been a great source of inspiration during my Ph.D., particularly thanks to the dedicated colleagues I had the pleasure of working with. I would like to mention Gian Piero and Alberto, who served as diligent and competent day-to-day mentors. Their experience and practical advice were essential in steering my work in the right direction. Other people were part of the everyday coffee-time, Maurizio, Rudi, Alessio and Alessandro, with a special mention to Mattia and Irene for making everyday moments more enjoyable with casual-talks and jokes.

Through my tutoring experience, I had the pleasure of meeting many students who, in turn, helped shape me both professionally and personally.

Collaborating with leading institutions in the microwave field was equally rewarding, offering valuable insight into the broader research and industry ecosystem. My time with the Ferdinand-Braun-Institut (FBH) in Berlin, Germany, and the Microwave Electronics for Communications (MEC) group in Bologna, Italy, led to productive collaborations and meaningful scientific growth. I am thankful to all colleagues from Berlin-Olof, Alessandro, and Domenico-as well as Francesco and Andrea from MEC.

A special mention goes to my family and my girlfriend, Francesca, for their constant support throughout this journey. Their patience, encouragement, and understanding, especially during the most intense periods, were paramount for achieving this goal.

## Contents

| $\mathbf{A}$ | bstra | ct     |                                                 | i    |

|--------------|-------|--------|-------------------------------------------------|------|

| $\mathbf{A}$ | cknov | wledgr | nents                                           | iii  |

| $\mathbf{C}$ | onter | nts    |                                                 | v    |

| Li           | st of | Figur  | es                                              | ix   |

| Li           | st of | Table  | ${f s}$                                         | xvii |

| $\mathbf{A}$ | crony | /ms    |                                                 | xix  |

| 1            | Intr  | oduct  | ion                                             | 1    |

|              | 1.1   | Teleco | ommunication industry and technologies          | 1    |

|              |       | 1.1.1  | Telecommunication trends                        | 1    |

|              |       | 1.1.2  | Semicondutor technologies for telecommunication | 3    |

|              |       | 1.1.3  | GaN technology                                  | 4    |

|              | 1.2   | Radio  | -frequency power amplifiers                     | 6    |

|              |       | 1.2.1  | Overview                                        | 6    |

|              |       | 1.2.2  | Reconfigurable PAs                              | 7    |

|              |       | 1.2.3  | High-efficiency PAs                             | 9    |

|              | 1.3   | Varac  | tor devices                                     | 12   |

|              | 1.4   | On-wa  | afer measurements                               | 16   |

|              | 1.5   | This v | work                                            | 18   |

|              |       | 1.5.1  | Objective                                       | 18   |

|              |       | 1.5.2  | Organization of the text                        | 19   |

| 2            | Gal   | N HEN  | MT characterization                             | 21   |

|              | 2.1   | Introd | luction                                         | 21   |

|              | 22    | Trann  | ing phenomena                                   | 22   |

vi

|   | 2.3 | Extrac  | ction strategy                           | . 23 |

|---|-----|---------|------------------------------------------|------|

|   |     | 2.3.1   | Overview                                 | . 23 |

|   |     | 2.3.2   | Static IV                                | . 24 |

|   |     | 2.3.3   | Gate and drain lag                       | . 26 |

|   |     | 2.3.4   | Thermal resistance                       | . 27 |

|   |     | 2.3.5   | Trap Activation Energy and Cross Section | . 29 |

|   |     | 2.3.6   | Density of Trapped Carriers              | . 32 |

|   | 2.4 | Measu   | rement setup                             | . 33 |

|   | 2.5 | Measu   | rement results                           | . 36 |

|   | 2.6 | Buffer  | r-free devices                           | . 39 |

|   |     | 2.6.1   | Overview                                 | . 39 |

|   |     | 2.6.2   | Measurement results                      | . 40 |

|   | 2.7 | Conclu  | usion                                    | . 42 |

| 3 | Var | actor o | characterization                         | 45   |

|   | 3.1 | Introd  | luction                                  | . 45 |

|   | 3.2 | Figure  | es of merit                              | . 46 |

|   | 3.3 | Experi  | imental results                          | . 47 |

|   |     | 3.3.1   | Experimental setup and devices           | . 47 |

|   |     | 3.3.2   | Comparison with MIM capacitor            | . 49 |

|   |     | 3.3.3   | Layout considerations                    | . 50 |

|   |     | 3.3.4   | Evaluation at multiple frequency bands   | . 52 |

|   |     | 3.3.5   | Large signal evaluation                  | . 53 |

|   | 3.4 | Island  | varactors                                | . 54 |

|   | 3.5 | Conclu  | usions                                   | . 58 |

| 4 | Var | actor I | Modeling                                 | 61   |

|   | 4.1 | Introd  | luction                                  | . 61 |

|   | 4.2 | Tradit  | tional modeling approaches               | . 63 |

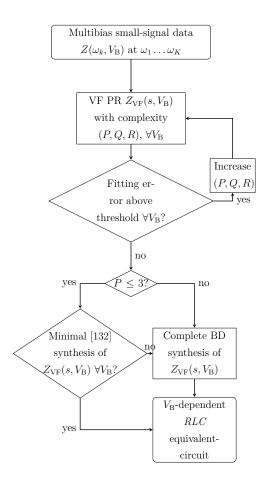

|   | 4.3 | New E   | Behavioral modeling approach             | . 64 |

|   |     | 4.3.1   | Rational fitting                         | . 64 |

|   |     | 4.3.2   | Network Synthesis                        | . 67 |

|   |     | 4.3.3   | Complete modeling application            | . 70 |

|   | 4.4 | Experi  | imental results                          | . 72 |

|   | 4.5 | CAD i   | implementation and validation            | . 75 |

|   | 4.6 |         | l scaling                                |      |

|   | 4.7 |         | ling of complex structures               |      |

| vii |

|-----|

|     |

|     |

|    | 4.8           | Conclusions                                   | 85  |

|----|---------------|-----------------------------------------------|-----|

| 5  | $\mathbf{RF}$ | Power Amplifier design techniques             | 89  |

|    | 5.1           | Introduction                                  | 89  |

|    | 5.2           | Design experience at MEC                      | 91  |

|    | 5.3           | Output matching network design with varactors | 92  |

|    |               | 5.3.1 Implementation with shunt varactor      | 95  |

|    |               | 5.3.2 Implementation with series varactor     | 100 |

|    | 5.4           | Conclusion                                    | 103 |

| 6  | Con           | nclusions                                     | 105 |

|    | 6.1           | Main achievements                             | 105 |

|    | 6.2           | Future work                                   | 107 |

| Bi | bliog         | graphy                                        | 108 |

# List of Figures

| 1.1 | Survey of published works on PA per operational frequency and satu-                     |    |

|-----|-----------------------------------------------------------------------------------------|----|

|     | rated power [1]                                                                         | 4  |

| 1.2 | Cross section of common GaN HEMT                                                        | 5  |

| 1.3 | Schematic representation of a RF PA                                                     | 7  |

| 1.4 | Visual representation of bias points for class A, B, AB                                 | 9  |

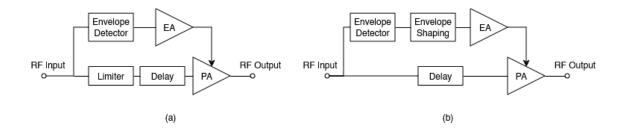

| 1.5 | (a) Block diagram of EER amplifier; (b) block diagram of ET amplifier.                  | 11 |

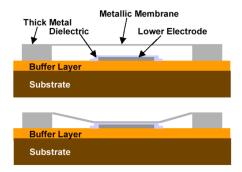

| 1.6 | Cross-section representation of MEMS varactor from [2]. Two different                   |    |

|     | states are highlighted, exhibiting different capacitance                                | 13 |

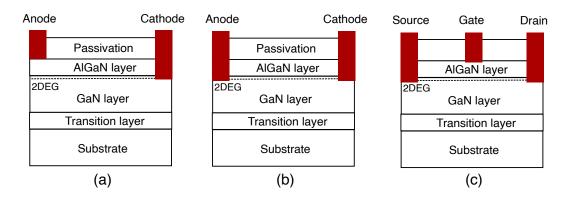

| 1.7 | (a) Cross section of lateral Schottky diode; (b) lateral Schottky diode                 |    |

|     | with recessed contact; (c) HEMT device exploited as Schottky diode. $$ .                | 15 |

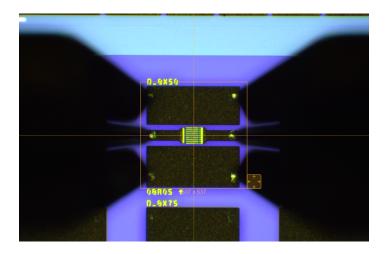

| 1.8 | Microscope image of an MMIC diode with coplanar connections. The                        |    |

|     | black shapes on both the left and right sides are ground-signal-ground                  |    |

|     | (GSG) probes                                                                            | 16 |

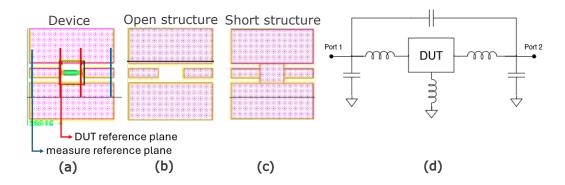

| 1.9 | Structures for open-short de-embedding procedure. (a) Structure with                    |    |

|     | device; (b) open structure; (c) short structure. (d) Parasitic elements                 |    |

|     | extracted with the procedure                                                            | 17 |

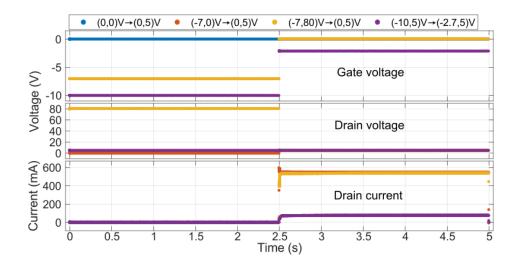

| 2.1 | 50%-duty-cycle acquired waveforms for different configurations of gate/drain            | n  |

|     | voltage and corresponding drain current (top to bottom). Full recovery                  |    |

|     | of the drain current transient is guaranteed by adopting a period $T=5~\mathrm{s}.$     | 23 |

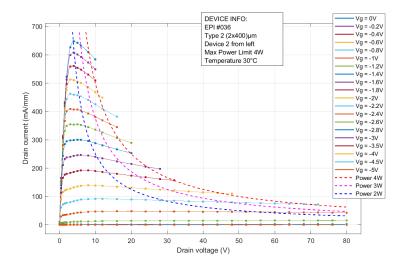

| 2.2 | Static IV extraction for one sample performed at 30°C $ \ldots  \ldots  \ldots  \ldots$ | 25 |

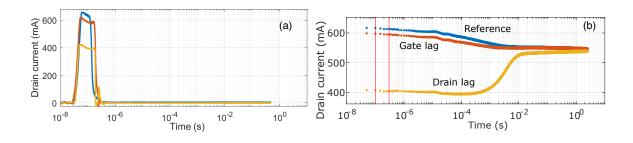

| 2.3 | Example of current waveforms for the gate- and drain-lag extraction                     |    |

|     | based on (a) classical pulsed characterization and (b) DCT extraction.                  |    |

|     | With DCT only the first 200 ns are sampled and averaged                                 | 27 |

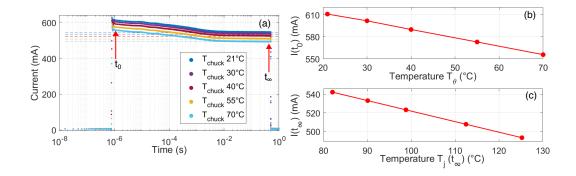

| 2.4 | (a) Waveforms acquired at multiple base<br>plate temperatures for $R_{th}$ ex-          |    |

|     | traction. (b) Sampling of drain current for each waveform at $t_0$ . (c)                |    |

|     | Extrapolation of junction temperature $\theta_j$ based on interpolation in (b).         | 28 |

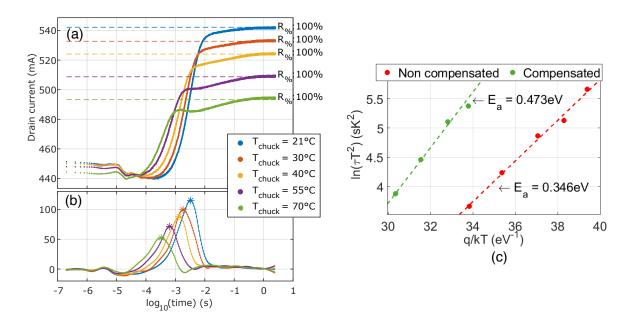

| 2.5  | (a) Drain current waveforms acquired at multiple baseplate temperatures for transition $(V_{GS}, V_{DS}) = (-7, 80) \text{ V}$ to $(V_{GS}, V_{DS}) = (0, 5) \text{ V}$ |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | and (b) the extracted time-derivative where selected de-trapping time                                                                                                   |    |

|      | constants are highlighted with a star. (c) Arrhenius plot with and with-                                                                                                |    |

|      | out temperature compensation                                                                                                                                            | 32 |

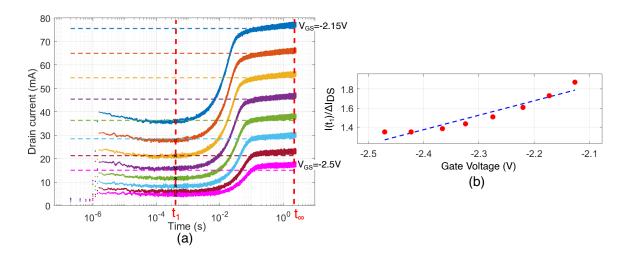

| 2.6  | (a) Current waveforms for $V_{GS}$ from -2.5 V to -2.15 V and $V_{DS} = 5$ V.                                                                                           |    |

|      | The current is sampled at $t_1$ and $t_{\infty}$ . Dashed lines indicate the ex-                                                                                        |    |

|      | pected current from dc characterization. (b) Extracted current ratio as                                                                                                 |    |

|      | in Eq. 2.9 towards gate voltage for same range in (a)                                                                                                                   | 33 |

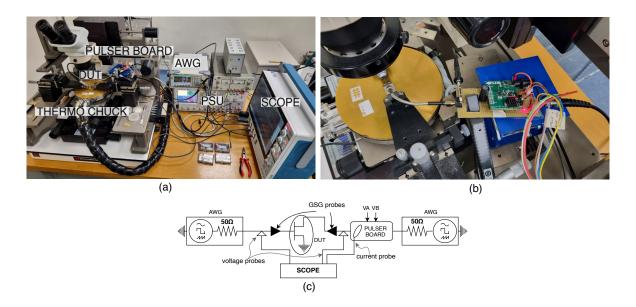

| 2.7  | (a) Photo and (c) schematic representation of the measurement setup                                                                                                     |    |

|      | used for transient characterization. (b) Close up of the custom pulser                                                                                                  |    |

|      | board                                                                                                                                                                   | 34 |

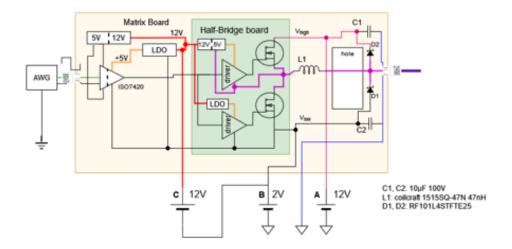

| 2.8  | Schematic representation of the custom board visible in Fig. 2.7(b)                                                                                                     | 35 |

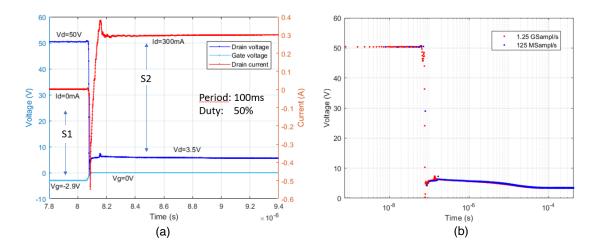

| 2.9  | (a) Voltage and current waveforms for an excitation from $(-2.9, 50)$ V                                                                                                 |    |

|      | to $(0,3.5)$ V. (b) Alignment of two acquisitions performed at different                                                                                                |    |

|      | sampling rates for the accurate acquisition of the edge                                                                                                                 | 36 |

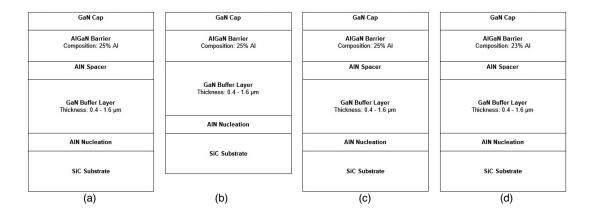

| 2.10 | Cross sections of the available samples                                                                                                                                 | 37 |

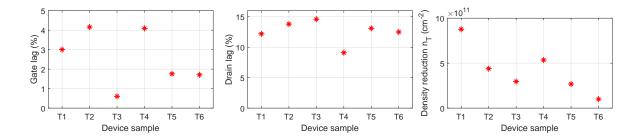

| 2.11 | Gate lag, drain lag and carrier density reduction extracted for all sam-                                                                                                |    |

|      | ples available                                                                                                                                                          | 38 |

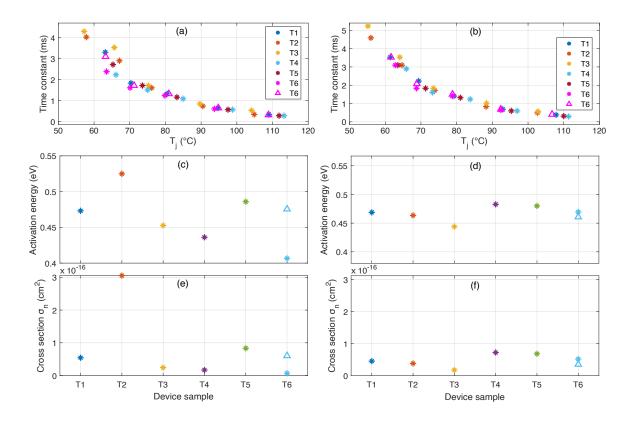

| 2.12 | (a) Detrapping time, (c) activation energy $E_A$ and (e) cross section $\sigma_n$                                                                                       |    |

|      | for pulses with $V_{DS}=50V$ . (b) Detrapping time, (d) activation energy                                                                                               |    |

|      | $E_A$ and (f) cross section $\sigma_n$ for pulses with $V_{DS} = 80V$                                                                                                   | 38 |

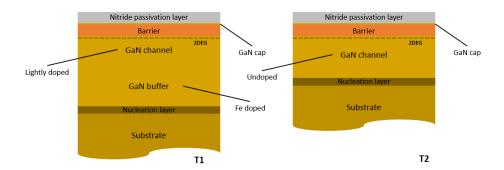

| 2.13 | Cross section of the two technologies. T1 is the structure of GaN $\operatorname{HEMT}$                                                                                 |    |

|      | with Fe-doped buffer, while T2 is the structure of the 'buffer-free' device                                                                                             | 40 |

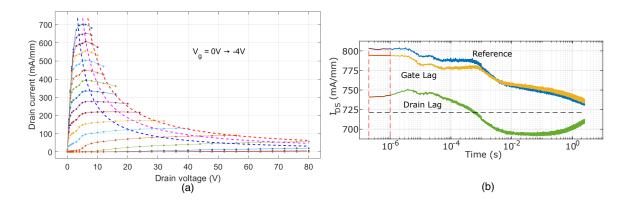

| 2.14 | (a) DC characterization of buffer-free device. (b) Reference, gate lag and                                                                                              |    |

|      | drain lag waveforms obtained from transitions $(V_{GS}, V_{DS}) = (0, 0) \text{ V} \rightarrow$                                                                         |    |

|      | $(0,5) \text{ V}, (V_{GS}, V_{DS}) = (-7,0) \text{ V} \rightarrow (0,5) \text{ V} \text{ and } (V_{GS}, V_{DS}) = (-7,50) \text{ V} \rightarrow$                        |    |

|      | (0,5) V respectively                                                                                                                                                    | 41 |

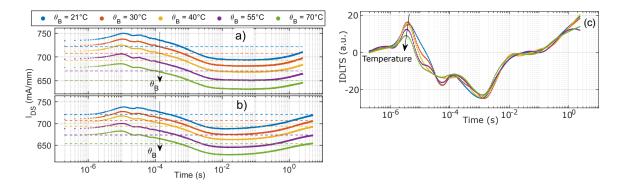

| 2.15 | DCT measurements of (a) $T=5~\mathrm{s};$ (b) $T=10~\mathrm{s}$ period of 'buffer-                                                                                      |    |

|      | free' device acquired at baseplate temperatures $\theta_B = 21^{\circ}\text{C} - 70^{\circ}\text{C}$ .                                                                  |    |

|      | The same voltage transition applied for all temperature is $(V_{GS}, V_{DS}) =$                                                                                         |    |

|      | $(-7,50) \text{ V} \rightarrow (0,5) \text{ V}$ . Dashed lines indicate the corresponding static                                                                        |    |

|      | values from dc. (c) Extraction of time constants                                                                                                                        | 41 |

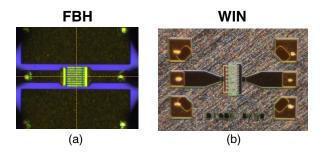

| 3.1  | Microphotographs of varactor diodes by (a) FBH foundry, (b) WIN                                                                                                         |    |

|      |                                                                                                                                                                         | 47 |

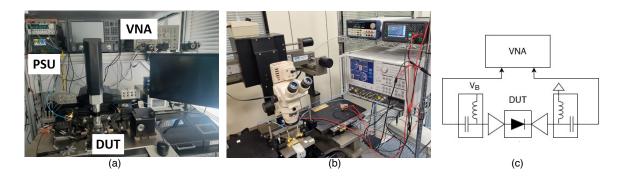

| 3.2  | Photos of small-signal setups for varactor characterization at (a) FBH                                    |    |

|------|-----------------------------------------------------------------------------------------------------------|----|

|      | and (b) EDM Lab. (c) Schematic representation of the setup                                                | 48 |

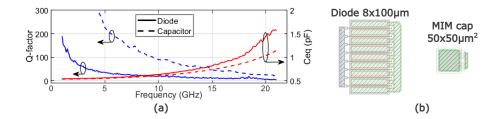

| 3.3  | (a) Q-factor and capacitance extracted for a $50 \times 50 \ \mu \text{m}^2$ MIM capacitor                |    |

|      | and a $8\times100~\mu\mathrm{m}$ Shottky diode for bias $V_{\mathrm{B}}=-5~\mathrm{V}$ in WIN technology. |    |

|      | (b) Layouts of the diode (left) and capacitor (right)                                                     | 49 |

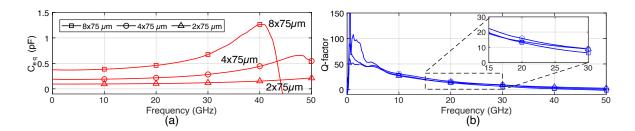

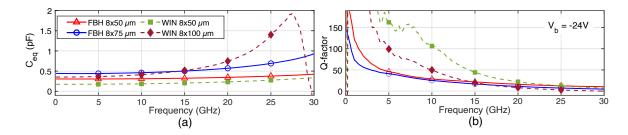

| 3.4  | (a) Equivalent capacitance and (b) Q-factor extracted at $V_{\rm B}=-30~{\rm V}$                          |    |

|      | for 3 devices from FBH with increasing finger number and fixed width                                      |    |

|      | of 75 $\mu m$                                                                                             | 51 |

| 3.5  | (a) Equivalent capacitance and (b) Q-factor extracted at $V_{\rm B}=-24~{ m V}$                           |    |

|      | for two Schottky diodes of size $8\times50~\mu\mathrm{m}$ and $8\times75~\mu\mathrm{m}$ in FBH technol-   |    |

|      | ogy (solid), and for two Schottky diodes of size $8\times50~\mu\mathrm{m}$ and $8\times100~\mu\mathrm{m}$ |    |

|      | in WIN technology (dashed)                                                                                | 51 |

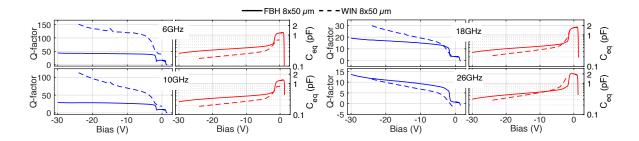

| 3.6  | Equivalent capacitance and Q-factor extracted at $V_{\rm B}=-24~{ m V}$ for two                           |    |

|      | Schottky diodes of size $8\times50~\mu\mathrm{m}$ and $8\times75~\mu\mathrm{m}$ in FBH technology         |    |

|      | (solid), and for two Schottky diodes of size $8\times50~\mu\mathrm{m}$ and $8\times100~\mu\mathrm{m}$ in  |    |

|      | WIN technology (dashed)                                                                                   | 52 |

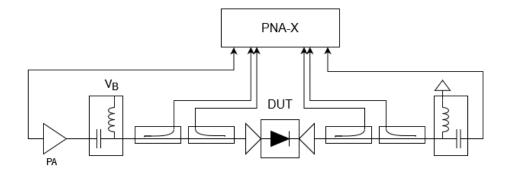

| 3.7  | Setup adopted for the large-signal characterization                                                       | 53 |

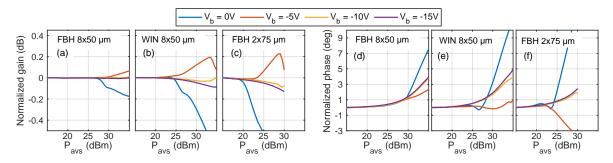

| 3.8  | (a)-(c) AM/AM and (d)-(f) AM/PM normalized characteristics for three                                      |    |

|      | Schottky diode devices extracted at 18 GHz for multiple bias voltages                                     | 54 |

| 3.9  | Schematic representation of 2x2 island varactor cell                                                      | 55 |

| 3.10 | Schematic representation of island varactor structures connected in (a)                                   |    |

|      | parallel and (b) series. Layout of (c) parallel and (d) series structures                                 | 55 |

| 3.11 | Complete island structures from layout with pads for measurement.                                         |    |

|      | (a) Basic 2x2 cell; (b) series structure; (c) parallel structure. The top                                 |    |

|      | connection is only meant for providing bias voltage and includes a series                                 |    |

|      | resistance of 2 k $\Omega$                                                                                | 56 |

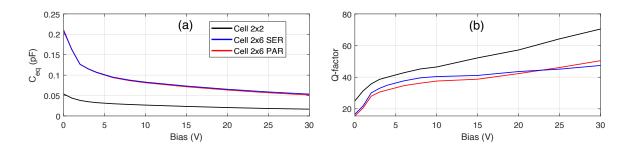

| 3.12 | Equivalent capacitance and quality factor for multiple bias voltages of                                   |    |

|      | (a)-(b) 2x2 island structure; (c)-(d) 2x6 series structure; (e)-(f) 2x6                                   |    |

|      | parallel structure                                                                                        | 57 |

| 3.13 | (a) Equivalent capacitance and (b) quality factor for all structures ex-                                  |    |

|      | tracted at 10 GHz for full bias range                                                                     | 57 |

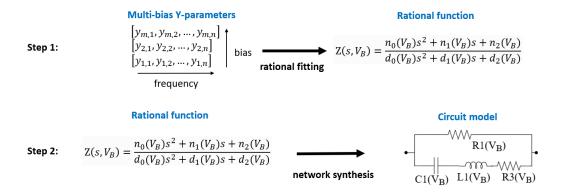

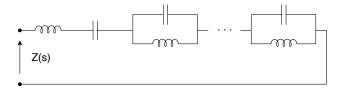

| 4.1  | Conceptual steps of the proposed modeling procedure. Step 1 is sum-                                       |    |

| _    | marized as the rational fitting procedure while step 2 consists on the                                    |    |

|      | network synthesis starting from the rational function extracted                                           | 63 |

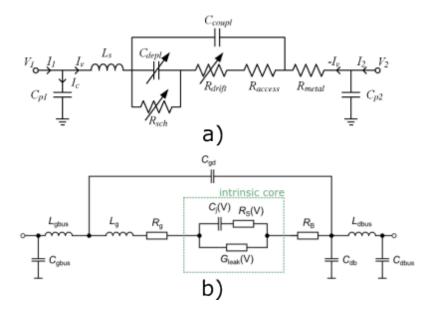

| 4.2  | Equivalent-circuit topologies for Schottky diode varactors reported in                                    |    |

|      | a) [3] and b) [4]                                                                                         | 64 |

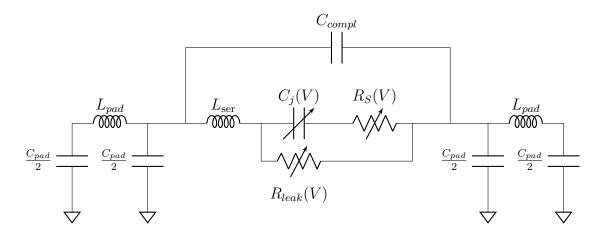

| 4.3  | Example of minimal network for varactor diode extracted from literature.                                                                                                                                                                                                                                   | 65 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

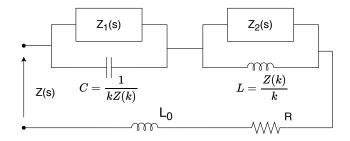

| 4.4  | Network example of Brune synthesis                                                                                                                                                                                                                                                                         | 68 |

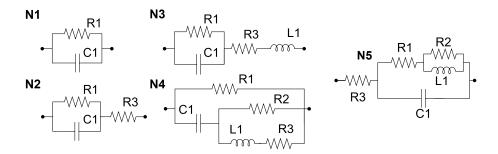

| 4.5  | First step of the Bott-Duffin synthesis procedure. $Z_1(s)$ and $Z_2(s)$ de-                                                                                                                                                                                                                               |    |

|      | note two networks having lower complexity than $Z(s)$                                                                                                                                                                                                                                                      | 69 |

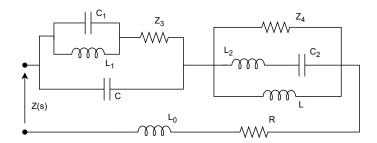

| 4.6  | Synthesized networks for fitting complexities $(P, Q, R) = (1, 0, 0)$ ( <b>N1</b> ), $(P, Q, R) = (1, 1, 0)$ ( <b>N2</b> ), $(P, Q, R) = (1, 1, 1)$ ( <b>N3</b> ), and $(P, Q, R) = (1, 1, 1)$                                                                                                             |    |

|      | (2,1,0) ( <b>N4</b> and <b>N5</b> )                                                                                                                                                                                                                                                                        | 70 |

| 4.7  | Flow chart for the proposed equivalent-circuit model extraction from small-signal data                                                                                                                                                                                                                     | 71 |

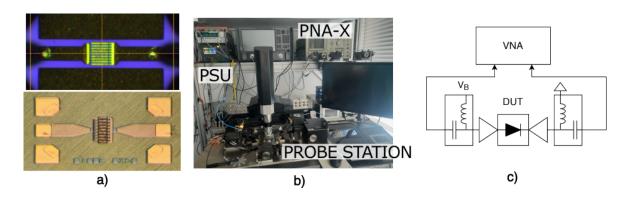

| 4.8  | (a) Microphotographs of $8\times50~\mu\mathrm{m}$ Shottky diode by FBH (top); $8\times50~\mu\mathrm{m}$ Shottky diode by WIN semiconductors (bottom). (b) Photo and (c) block diagram of the measurement setup for performing S-parameter                                                                  | 70 |

|      | characterization                                                                                                                                                                                                                                                                                           | 72 |

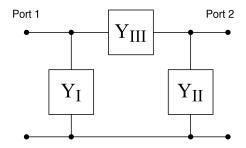

| 4.9  | Partitioning of varactor device in three bipoles. The decomposition is valid if $Y$ -parameters are considered                                                                                                                                                                                             | 73 |

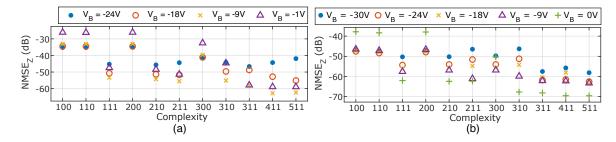

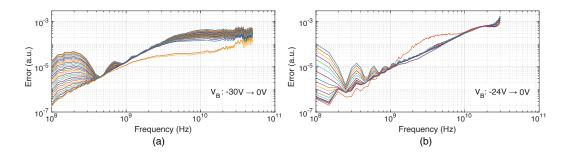

| 4.10 | Error computed as in Eq. 4.7 for (a) WIN device and (b) FBH device                                                                                                                                                                                                                                         |    |

|      | for multiple bias voltages at increasing complexity                                                                                                                                                                                                                                                        | 73 |

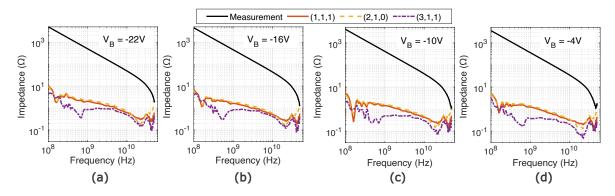

| 4.11 | Measured $ Z_{\rm III} $ impedance (black line) and absolute error across frequency between $Z_{\rm III}$ and its vector-fitted version $Z_{\rm VF}$ for the 8x50 $\mu$ m diode by WIN. The extraction is performed at three different complexities for $V_{\rm B}=$ -22V (a), -16V (b), -10V (c), -4V (d) | 74 |

| 4.12 | Measured $ Z_{\rm III} $ impedance (black line) and absolute error across frequency between $Z_{\rm III}$ and its vector-fitted version $Z_{\rm VF}$ for the 8x50 $\mu{\rm m}$ diode by FBH. The extraction is performed at three different complex-                                                       |    |

|      | ities for $V_{\rm B} = -22 {\rm V}$ (a), $-16 {\rm V}$ (b), $-10 {\rm V}$ (c), $-4 {\rm V}$ (d)                                                                                                                                                                                                            | 74 |

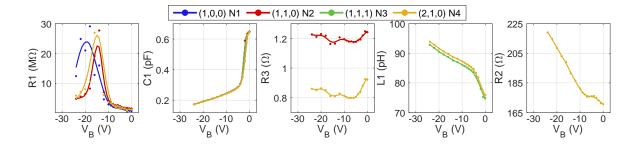

| 4.13 | Network elements for the $8\times50~\mu\mathrm{m}$ varactor by WIN, with component names referring to Fig. 4.6 (not all components are present for every network). Each dot corresponds to a given bias value, whereas solid lines are spline approximations across all bias values                        | 75 |

| 111  |                                                                                                                                                                                                                                                                                                            | 10 |

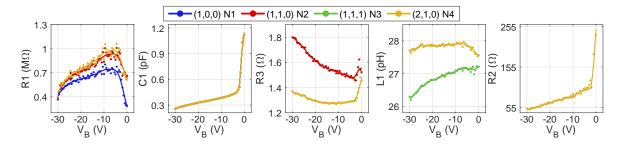

| 4.14 | Network elements for the $8\times50~\mu\mathrm{m}$ varactor by FBH, with component names referring to Fig. 4.6 (not all components are present for every                                                                                                                                                   |    |

|      | network). Each dot corresponds to a given bias value, whereas solid lines are spline approximations across all bias values                                                                                                                                                                                 | 75 |

| / 1¤ |                                                                                                                                                                                                                                                                                                            | 10 |

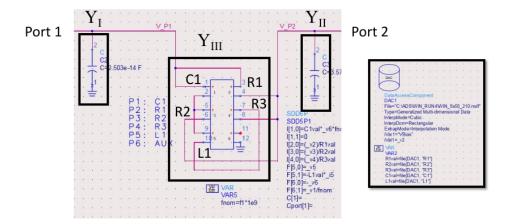

| 4.10 | Implementation of varactor model for complexity $(2, 1, 0)$ in ADS environment                                                                                                                                                                                                                             | 76 |

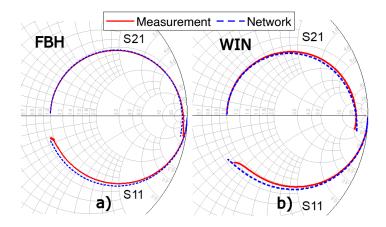

| 4.16 | Comparison between modeled and measured S-parameters at $V_{\rm B}=-20{\rm V}$ for $8\times50~\mu{\rm m}$ by (a) FBH and (b) WIN | 77 |

|------|----------------------------------------------------------------------------------------------------------------------------------|----|

| 4.17 | Modeling error $E_S$ on the two-port S-parameters for (a) FBH 8×50 $\mu \mathrm{m}$                                              |    |

|      | device and (b) WIN $8\times50~\mu\mathrm{m}$ device across frequency for all available                                           |    |

|      | bias voltages                                                                                                                    | 77 |

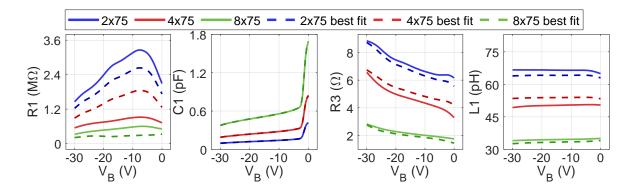

| 4.18 | Network elements fitting (solid lines) for complexity $(1, 1, 0)$ for varac-                                                     |    |

|      | tors in FBH technology with different finger numbers but fixed width                                                             |    |

|      | (75 $\mu$ m). Values are linearly interpolated for each bias and the evalu-                                                      |    |

|      | ation of the best fitting function is reported in dashed lines. Element                                                          |    |

|      | names are referred to network <b>N3</b> in Fig. 4.6                                                                              | 79 |

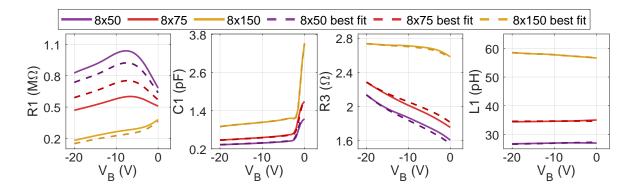

| 4.19 | Network elements fitting (solid lines) for complexity $(1,1,0)$ for var-                                                         |    |

|      | actors in FBH technology with 8 fingers and multiple finger widths.                                                              |    |

|      | Values are linearly interpolated for each bias and the evaluation of the                                                         |    |

|      | best fitting function is reported in dashed lines. Element names are                                                             |    |

|      | referred to network <b>N3</b> in Fig. 4.6                                                                                        | 79 |

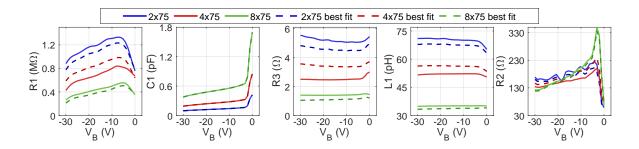

| 4.20 | Network elements fitting (solid lines) for complexity $(1,1,0)$ for varac-                                                       |    |

|      | tors in FBH technology with different finger numbers but fixed width                                                             |    |

|      | (75 $\mu m$ ). Values are linearly interpolated for each bias and the evalu-                                                     |    |

|      | ation of the best fitting function is reported in dashed lines. Element                                                          |    |

|      | names are referred to network $N3$ in Fig. 4.6                                                                                   | 80 |

| 4.21 | Network elements fitting (solid lines) for complexity $(2,1,0)$ for variators                                                    |    |

|      | in FBH technology with 8 fingers and multiple finger widths. Values                                                              |    |

|      | are linearly interpolated for each bias and the evaluation of the best                                                           |    |

|      | fitting function is reported in dashed lines. Element names are referred                                                         |    |

|      | to network $\mathbf{N4}$ in Fig. 4.6                                                                                             | 80 |

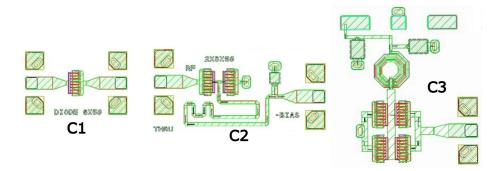

| 4.22 | Varactor cells under test. $C1$ Single diode; $C2$ two diodes in antiseries                                                      |    |

|      | configuration; C3 $2x2$ island configuration                                                                                     | 82 |

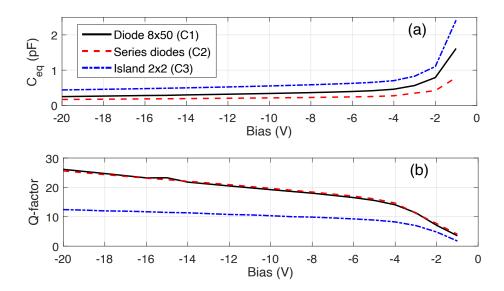

| 4.23 | (a) Equivalent capacitance and (b) quality factor of the three cells in                                                          |    |

|      | Fig. 4.22 at 18 GHz                                                                                                              | 83 |

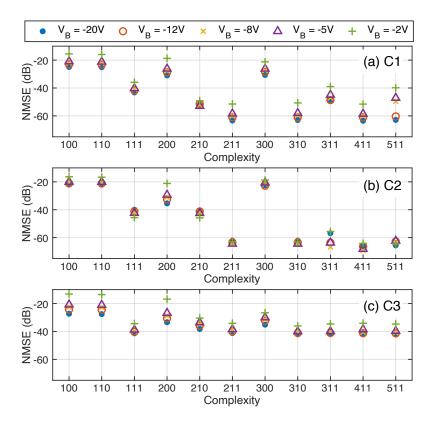

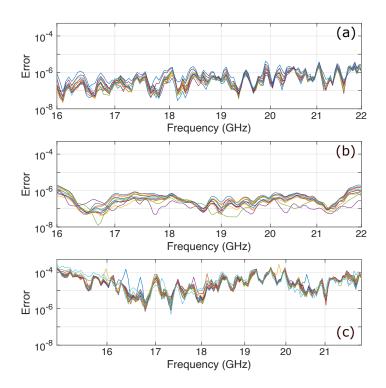

| 4.24 | Fitting errors for five bias voltages at increasing complexities for (a)                                                         |    |

|      | C1, (b) C2 and (c) C3 cells in Fig. 4.22 over the available frequency                                                            |    |

|      | range of 16 GHz - 22 GHz                                                                                                         | 84 |

| 4.25 | Network resulting after the application of BD network synthesis for                                                              |    |

|      | complexity $(2,1,1)$                                                                                                             | 85 |

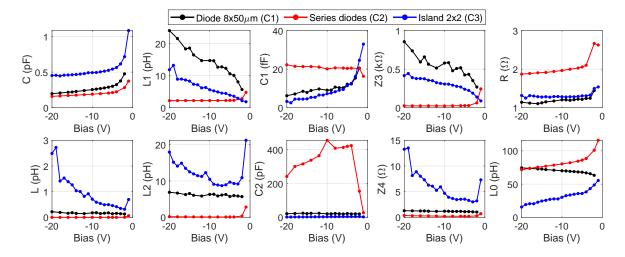

| 4.26 | Elements value for BD extraction performed on the three cells. Network                                                           |    |

|      | element names refer to components in Fig. 4.25                                                                                   | 85 |

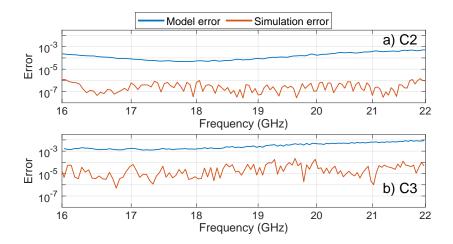

| 4.27       | Error on $S$ -parameters for (a) single diode, (b) series diodes, (c) island diodes                                                                                                                                                                                                                            | 86  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.28       | Error on $S$ -parameters computed for model and simulation for a) series diodes, b) island diodes                                                                                                                                                                                                              | 87  |

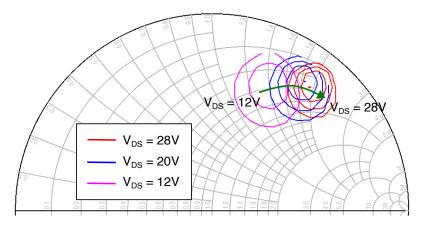

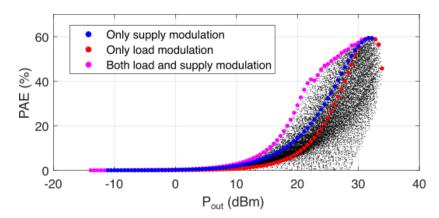

| 5.1        | PAE contours for $4\times50~\mu\mathrm{m}$ device at 16.5 GHz for three bias voltages.                                                                                                                                                                                                                         | 92  |

| 5.2        | PAE performance extracted at 16.5 GHz for HEMT stage in common-<br>source configuration. Efficiency envelope obtained with a fixed load but<br>multiple $V_{\rm DS}$ is represented with blue dots; red dots are obtained with<br>a fixed $V_{\rm DS}=28$ V but different loads; pink dots highlight the ideal |     |

| <b>F</b> 0 | condition achieved by selecting the best load for each tested $V_{\rm DS}$                                                                                                                                                                                                                                     | 93  |

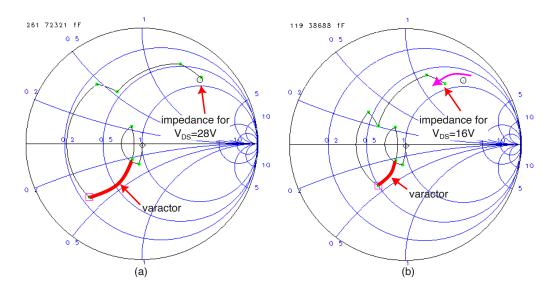

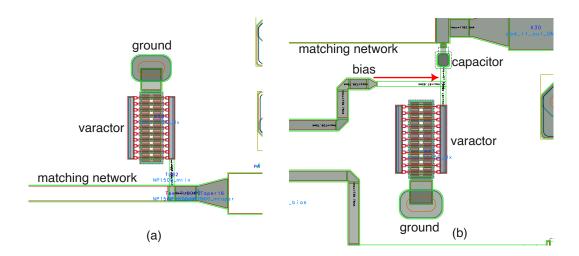

| 5.3        | Impedance synthesized with the matching network and impact of capacitance variation of the varactor element for (a) maximum capacitance                                                                                                                                                                        |     |

|            | and (b) minimum capacitance                                                                                                                                                                                                                                                                                    | 95  |

| 5.4        | Possible implementation of varactor in the matching network: (a) direct connection providing both dc and RF signals; (b) decoupling capacitor                                                                                                                                                                  |     |

|            | and independent bias connection                                                                                                                                                                                                                                                                                | 96  |

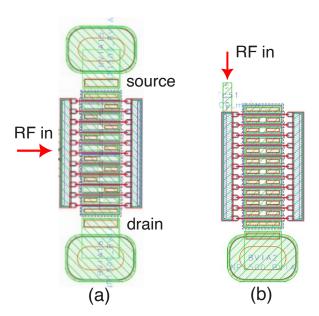

| 5.5        | (a) Original layout of the switch device with source and drain grounded through backvias. (b) Switch layout modified to allow for only one                                                                                                                                                                     |     |

|            | backvia connection                                                                                                                                                                                                                                                                                             | 97  |

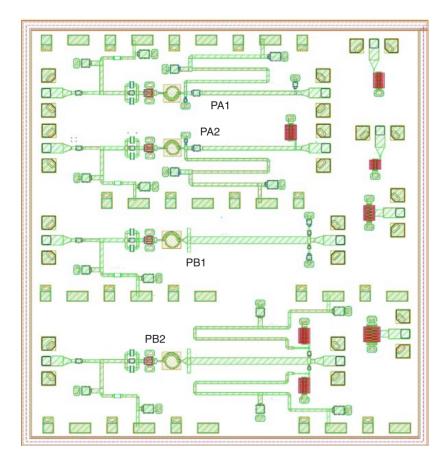

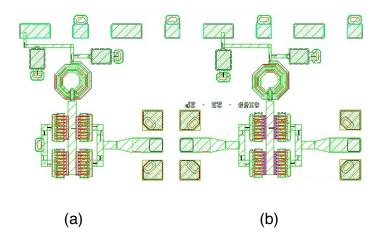

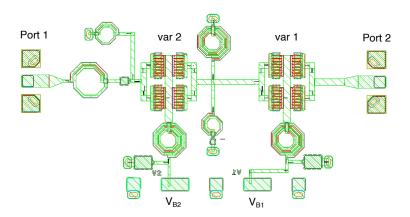

| 5.6        | Layout of the complete manufactured chip containing the four amplifiers implementing varactors in the OMN                                                                                                                                                                                                      | 98  |

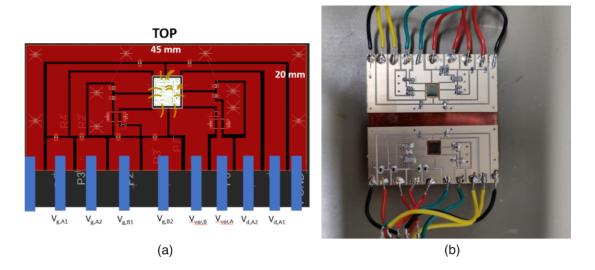

| 5.7        | (a) Schematic representation of PCB fixture for delivering bias voltage up to the dc pads. (b) Photo of the complete fixture with two PCB                                                                                                                                                                      |     |

|            | boards and amplifier chip accommodated on a copper block                                                                                                                                                                                                                                                       | 99  |

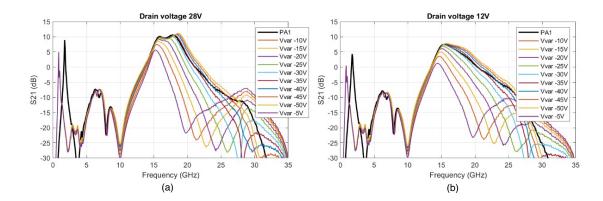

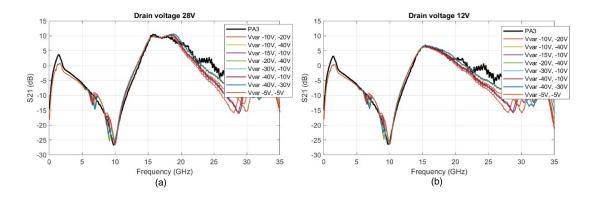

| 5.8        | $S_{21}$ performances of <b>PA1</b> and <b>PA2</b> as in Fig. 5.6 for two drain bias voltages of (a) $V_{\rm DS} = 28$ V and (b) $V_{\rm DS} = 12$ V and multiple varactor                                                                                                                                     |     |

|            | biases                                                                                                                                                                                                                                                                                                         | 99  |

| 5.9        | $S_{21}$ performances of <b>PB1</b> and <b>PB2</b> as in Fig. 5.6 for two drain bias voltages of (a) $V_{\rm DS}=28$ V and (b) $V_{\rm DS}=12$ V and multiple varactor                                                                                                                                         |     |

|            | biases                                                                                                                                                                                                                                                                                                         | 100 |

| 5.10       | Test structures for the realization of MN with series varactors. Cell with configuration of 2x2 varactors is realized in (a) shunt version and                                                                                                                                                                 |     |

|            | (b) 2-port version                                                                                                                                                                                                                                                                                             | 101 |

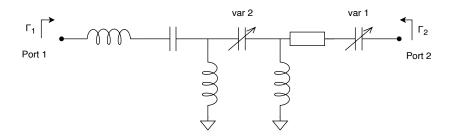

| 5.11       | Schematic representation of the realized matching network including the varactor cells                                                                                                                                                                                                                         | 101 |

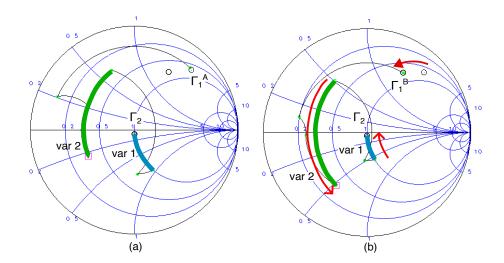

| 5.12 | Reflection coefficient $\Gamma_1$ synthesized by the matching network at port 1            |     |

|------|--------------------------------------------------------------------------------------------|-----|

|      | with the topology in Fig. 5.11. The effect of the two varactor cells (var1                 |     |

|      | and var2) is highlighted by reporting two extremal tuning configurations                   |     |

|      | in (a) and (b), respectively.                                                              | 102 |

| 5.13 | Layout of the designed tunable matching network. The target impedance                      |     |

|      | is realized at port 1, while port 2 is to be terminated to the 50 $\Omega$ load.           |     |

|      | The two pads at the bottom allow to provide independent bias voltages                      |     |

|      | to the two varactor cells                                                                  | 102 |

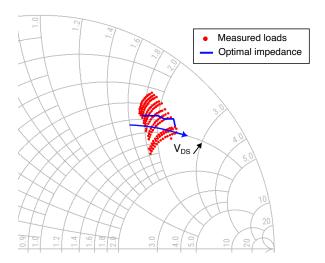

| 5.14 | Loads extracted for all combination of varactor biases (red dots) ex-                      |     |

|      | tracted at 16.5 GHz and best impedance trajectory (blue line) extracted $$                 |     |

|      | from load-pull simulations with $V_{DS}$ swept from 18 V to 28 V                           | 103 |

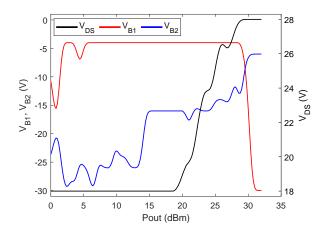

| 5.15 | Control voltages for $V_{DS}$ , $V_{B1}$ and $V_{B2}$ across output power $P_{\text{out}}$ | 104 |

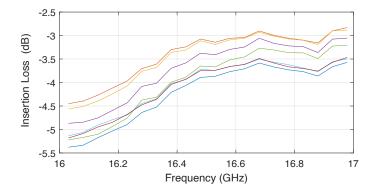

| 5.16 | Insertion loss of the designed tunable matching network extracted from                     |     |

|      | small-signal measurements at selected varactor bias voltages                               | 104 |

## List of Tables

| 1.1 | Qualitative performances for three varactor technologies                                                                                                                                        | 13 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Measurement plan for complete HEMT characterization. Voltage couples expressed as $(V_{GS}, V_{DS})$ V. $V_G^{\text{dens}}$ indicates many gate voltages as described in Sec. 2.3.6             | 37 |

| 3.1 | Tuning range and Q-factor at multiple frequency ranges for FBH and WIN diode technologies, where $V_{\rm B}=-24$ V for $C_{min}$ and $Q_{max}$ and $V_{\rm B}=-5$ V for $C_{max}$ and $Q_{min}$ | 53 |

| 4 1 | $\bar{F}_{\rm g}(V_{\rm p})$ in dB as from (4.10) at two selected bias voltages                                                                                                                 | 78 |

## Acronyms

5G Fifth Generation Mobile Communications Standard

CAD Circuit Aided Design

**CMOS** Complementary Metal-Oxide Semiconductor

CW Continuous Wave

**DCT** Drain Current Transients

GaN Gallium nitride

**HEMT** High Electron Mobility Transistor

IMN Input matching network

**IoT** Internet of Things

LTE Long Term Evolution

MEMS Microelectromechanical Systems

MIM Metal Insulator Metal

MMIC Microwave monolithic integrated circuit

$\mathbf{MN}$  Matching Network

MOS Metal Oxide Semiconductor

**NVNA** Nonlinear Vector Network Analyzer

**OMN** Output Matching Network

PA Power amplifier

PAE Power Added Efficiency

XX ACRONYMS

$\mathbf{PDK}$  product design kit

**PIV** Pulsed IV

${f RF}$  Radio-frequency

**SOLT** Short Open Load Thru

${f TR}$  Tuning Range

$\mathbf{VNA}$  Vector Network Analyzer

## Chapter 1

### Introduction

### 1.1 Telecommunication industry and technologies

#### 1.1.1 Telecommunication trends

Over the last ten years, wireless applications have witnessed exponential growth due to increasing demand across various sectors such as cellular networks, vehicular communication, and industrial systems. Advances in semiconductor technology facilitate new paradigms that were unimaginable a few decades ago. These cutting-edge technologies have seamlessly integrated into daily life, proving their utility in diverse domains. For instance, the Internet of Things (IoT) has gained momentum in areas like agriculture, environmental monitoring, and smart metering, where it now plays a critical role [5]. The driving forces behind this widespread adoption are the affordability of connected sensors and consistent improvements in energy efficiency. These developments have enabled the deployment of many battery-powered, cable-free devices. Current estimates suggest that tens of billions of devices [6] are now connected to the network, prompting IoT standards to evolve to handle the increasing density of wireless connections. Simultaneously, the proliferation of smartphones and wireless internet connectivity has introduced new challenges. These include the need for higher data rates and better network coverage, both in rural areas and densely populated urban centers. The fourth-generation (4G) system, also known as Long-Term Evolution (LTE), has been the dominant standard for telecom data and voice traffic. By 2022, 4G surpassed the older third-generation (3G) standard, leading network operators to shut down 3G base stations in favor of the more advanced fifth-generation (5G) technology. 5G has now become a well-established commercial solution for wireless communication, designed to meet the diverse and demanding requirements of modern applications. These requirements include reliability, mobility, low latency, and cost-effectiveness. The versatility and superior performance of 5G are achieved by leveraging various advanced radio frequency (RF) techniques. These include Time Division Duplex (TDD) and Frequency Division Duplex (FDD), which were already employed in LTE, alongside a more sophisticated Orthogonal Frequency Division Multiplexing (OFDM) modulation scheme. Furthermore, novel approaches like Generalized Frequency Division Multiplexing (GFDM) [7] and Filtered-Orthogonal Frequency Division Multiplexing (f-OFDM) [8] have been explored to enhance spectral efficiency. These techniques reduce out-of-band emissions, thereby increasing the overall power spectral density and ensuring that 5G can meet the challenges of modern wireless communication.

5G network architecture relies on the deployment of femtocells, a new network structure scheme that makes use of multiple smaller base stations to address frequency reuse and denser layouts [9, 10]. These cells integrate massive MIMO antennas operating at millimeter-wave frequencies [11] to be able to deliver gigabit-level wireless traffic. The new frequency range 2 (FR2) makes available K- and Ka-bands for telecommunication with the advantage of more link capacity but lower range coverage, due to the degradation of millimeter-wave (mm-wave) signals with the propagation distance. To be able to maintain the same LTE signal strength, the transmitting power of the base station must be increased and multiplied for all concurrent amplifiers, which could be up to 64 [12]. This power consumption cannot be easily tolerated without adopting smart resource allocation based on network requirements and scheduling algorithms [9].

An important slice of the 5G network power consumption is drained by the RF power amplifiers driving the antennas. RF power amplifiers (PA) are vital components of telecommunication infrastructures, with the role of boosting signals to the levels needed for efficient long-distance transmission while maintaining signal quality and minimizing power losses. While the trend of the number of possible applications is increasing, the frequency bands available for new standards struggle to grow at the same rate. It is then of main importance to exploit at best the reserved bandwidth. In order to address these requirements, modulated signals are widely adopted for increasing data rates while exploiting the same spectral occupation. This usually comes with the generation of signals with high peak-to-average-power-ratio (PAPR), creating challenges for PAs. This is especially true with new sixth-generation (6G) technology that requires very advanced linearity performances to fulfill the requirements [13]. Looking at the future of telecommunication, the next 6G is expected to operate in the terahertz (THz) frequency bands and deliver speeds of up to 1 Tbps with ultra-low

latency. The shift to such high frequencies will demand unprecedented power efficiency, thermal management, and robustness from PAs to ensure reliable performance. New semiconductors aim to address the new requirements as will be explored in Sec. 1.1.2 and 1.1.3.

#### 1.1.2 Semicondutor technologies for telecommunication

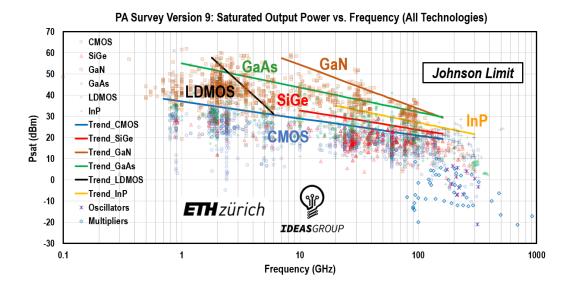

When looking at the state-of-the-art, several semiconductor technologies are available for the design and fabrication of telecommunication PAs and indeed the first step when target performances are provided is the technology selection. The output power required from the overall amplifier and the operation frequency are the two main drivers for the selection of the best solution optimizing the tradeoff between performances and costs. For low frequency applications, well-established technologies like CMOS and LDMOS offer good solutions and allow for low production costs and overall reliability [14]. On the other side, when high output power is required and the operation frequency enters the mm-wave domain, III-V semiconductors are usually adopted, as could be seen in Fig. 1.1 [1], thanks to the intrinsic advantages of the technology. From the late 20th century, Silicon Germanium (SiGe) became the most promising solution for telecommunication, offering the required processing maturity and yield, which makes it comparable with conventional Si solutions [15]. Gallium arsenide (GaAs) rapidly dominated the RF PA scenario because of its higher cut-off frequencies than silicon due to its high low-field mobility.

While the designers exploit all the performances of GaAs technology, the research industry started to look at Gallium Nitride (GaN) compound that theoretically can offer game-changing performances. Despite the promising results, the high production costs, due to a generally low yield, and the reliability problems arising with this new fabrication process, led to late optimization for the high-frequency operation and, instead, the high-power applications were privileged [16]. This is reasonable when considering that a PA operating at mm-wave frequencies needs a well-predictable manufacturing process, and large areas could be required to also implement all the passive structures, hence further reducing the yield of the process. In order to fully assess the advantages of GaN semiconductor and the current technological challenges, a deep analysis of the stack layer is presented in the following section.

Figure 1.1: Survey of published works on PA per operational frequency and saturated power [1].

#### 1.1.3 GaN technology

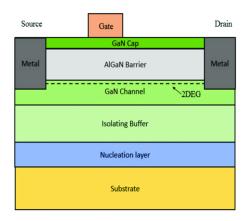

Many design strategies are investigated to improve the performance of GaN devices for specific applications. While GaN-on-Si vertical devices are widely adopted for lowfrequency power applications, lateral heterojunction field-effect transistors (HFETs), also known as high electron mobility transistors (HEMTs), are usually adopted for high-frequency applications. The advantage of this structure lies in a reduced distance between drain and source contacts, lowering the resistance that electrons must counteract. The principal feature of this structure is the AlGaN/GaN heterojunction that creates a thin layer of electrons known as "two-dimensional electron gas" (2DEG). This layer is created as a result of the different crystal polarities, namely spontaneous and piezoelectric polarizations, and creates a conductive path between drain and source even when no voltage is applied to the device. Spontaneous polarization originates from the difference in the electronegativity of the group III and V elements, which creates polar Ga-N bonds. Piezoelectric polarization shows its impact by applying a stress to the material that, for the HEMT case, comes from the contact of two layers (AlGaN and GaN layers) with different lattice constants. Devices with this property are usually denoted as normally-ON devices because the HEMT is fully conductive when no bias is applied to the gate port. Therefore, no doping is required to create a fully functional device with this structure, and the threshold voltage  $(V_{\rm th})$  is only dictated by material properties.

The 2DEG electron density could be actively controlled by the gate terminal that

Figure 1.2: Cross section of common GaN HEMT.

acts like a Schottky junction. Applying a negative voltage with respect to source potential causes the electrons at the GaN-AlGaN interface to deplete, reducing the carrier concentration and hence the device conductivity. A thin cap layer, usually realized in silicon-nitride (SiN), could be added on top of AlGaN barrier to help reducing current collapse [17] and gate leakage current and avoiding the oxidation of the AlGaN, despite slightly reducing the 2DEG concentration.

A common layer stack for GaN HEMTs is depicted in Fig. 1.2, and a detailed description of layers is provided below.

#### Substrate

The substrate is the structural element of the whole chip, accommodating all layers composing the final device. In addition to physical strength properties, Traditionally, silicon (Si) is used as the main substrate material due to its low production costs while its physical strength allows the realization of wafers with a diameter of up to 200 mm. Despite these advantages, Si is not the preferred choice for GaN technology. Since the GaN layer should be deposited on top of the substrate to realize the HEMT channel, the lattice mismatch plays an important role. The difference in lattice constants of Si and GaN forces the latter to break the regular structure and adapt to the material below. Defects originating from this physical adaptation may induce vertical (drain to substrate) breakdown and reliability degradation. Moreover, Si has poor thermal performance, being a limitation for the high power density that GaN solutions address.

One no-brainer solution is to fabricate the entire wafer in GaN so that no defects are expected when the buffer layer is grown. Moreover, GaN material also offers good thermal conductivity, as expected from the substrate. Unfortunately, this alternative turns out to be prohibitively high in realization costs, and its physical properties are not as good as the Si counterpart, as far as robustness is concerned. In order to obtain a compromise between the two alternatives, different materials are proposed, like sapphire, silicon carbide (SiC), and Al<sub>2</sub>O<sub>3</sub>. In particular, SiC offers a very low lattice mismatch compared to that of GaN and a reasonably low thermal mismatch, with a thermal conductivity higher than that of both GaN and Si substrates. Even if the realization cost is fairly high, it is a common adoption from foundries offering GaN-on-SiC technologies.

#### Buffer

The buffer layer is of great importance in reducing the number of physical defects in the GaN channel layer that affect the 2DEG conduction. Electrical properties are also affected, as the buffer should isolate the channel from the underlying substrate, preventing substrate current leakages and improving the off-state breakdown voltage [18]. It has been demonstrated that current-collapse effects can occur when hot-carriers are injected into the buffer and then trapped by the lower layers [19].

Intentionally introducing defects in the buffer helps improve its performance, particularly at RF frequencies. The undoped GaN deposited for the channel creation typically exhibits unintentional n-type doping characteristics, probably due to the deposition process and the influence of impurities like Si and oxygen (O) [20]. To compensate for this effect, acceptor-doping impurities like carbon (C) [21] or iron (Fe) could be used, demonstrating improvements in buffer charge confinement but worsening the trapping effects exhibited [22].

In addition to doping compensation, other strategies can be employed to enhance carrier confinement, like the introduction of buffer layers of different composition. One of these approaches consist in the introduction of an AlGaN back-barrier layer on top of the substrate. The additional potential barrier created helps to confine the 2DEG carriers [23], avoiding the need for a doped GaN buffer. Substantial improvements are observed at RF with this additional layer [24] despite other properties could be penalized, like thermal dissipation [25].

### 1.2 Radio-frequency power amplifiers

#### 1.2.1 Overview

Since the introduction of the 4G standard, reconfigurable PAs have become key components of wireless front-ends. This reconfigurability was initially intended as

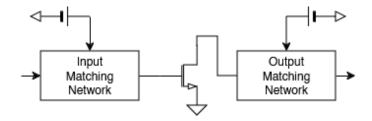

Figure 1.3: Schematic representation of a RF PA.

the ability to adapt the operative frequency of the amplifier, enabling the support of a variety of global services with multiple band licenses. Due to the required performance of the 4G standard, the ability to adapt the bandwidth of the amplifier in addition to the operational frequency was desirable. The number of available bands in the LTE technology makes it impossible to include many RF front-ends, each one devoted to a single carrier. Since designing wide-band circuits is increasingly hard as the frequency becomes higher [26], the inclusion of reconfigurable elements in the PA design is mandatory.

The typical block structure of an RF PA is reported in Fig. 1.3. The active element in the center is the main enabler of the overall structure, dictating the maximum performance we could expect from the amplifier and the technology to be used for the fabrication. The IMN and OMN blocks serve to adapt the input and output impedance, respectively, to the optimal impedance of the active element. In order to extract the values of those optimal impedances, measurements tailored to the specific selected device should be conducted. This is usually performed by the manufacturer, which provides a PDK that can be imported into the design software. If those data are not available, load- and source-pull setups can be exploited for the complete characterization [27].

The input and output matching networks usually contain a combination of passive elements, like resistors, capacitors, inductors, or microstrip lines, as well as active elements such as diodes or switches to achieve the required impedance adaptation. These last are exploited to achieve reconfigurable capabilities employing an external control signal (either current or voltage) directly affecting the circuit. In the next Section the topic of reconfigurable PAs is addressed, while in Sec. 1.2.3 state-of-theart strategies to enhance the amplifier efficiency are presented.

### 1.2.2 Reconfigurable PAs

Reconfigurability for power amplifiers can be achieved in different ways, depending on the target application. Multiband operation is widely adopted in telecommunications and refers to the ability to operate at multiple central frequencies [28] in a non-concurrent manner, reducing the number of distinct amplifier circuits required to cover all operative bands. Since the number of transmitting elements is usually kept low due to space constraints and a single transmitting antenna is adopted, this solution allows for a reduction in the size of the switching matrix required for all amplifiers to operate on a single output connection. Although clever solutions can be adopted to achieve multiband operation [29], active elements are typically required to obtain the desired behavior.

In this context, many passive elements in the matching networks-such as resistors or inductors-are targeted for replacement in favor of reconfigurable implementations [30], exploiting the active elements available in the same technology. In this way, all PA components can be integrated on the same chip, reducing parasitics, which are particularly impactful at high frequencies. This approach is not always straightforward, as the selected technology may not support these circuit elements, or they may not be accurately modeled. In [31], RF diodes are integrated into the originally static output matching network to selectively include or exclude discrete components such as capacitors or resistors. Switches derived from transistor topologies can also be used to selectively isolate sections of the matching network, as seen in switched-capacitor topologies [32].

Frequently, difficulties in integrating diodes or switches in PAs arise from poor isolation or conduction performance, due to trade-offs made during the design phase. In particular, when the device is expected to be fully conductive, the lowest possible parasitic resistance is required, leading to design optimizations such as maximizing the number of fingers. Conversely, when the device is deactivated, it should behave as transparently as possible, approximating an open circuit. This requirement often leads to minimal device sizing to reduce leakage currents that would otherwise degrade performance. The insertion loss of the device should be critically evaluated, as it must remain controlled during both on- and off-states.

Reconfigurability in MIMO applications is essential, as the ability to control the beam steering of an antenna array is of increasing interest in telecommunications. Circuits such as phase shifters are extensively adopted in MIMO systems, where the phase of the input signal must be accurately controlled across the transmitting antennas. Reconfigurable phase shifters [33] can then be integrated before the PAs and controlled by an external signal to properly steer the transmitted beam.

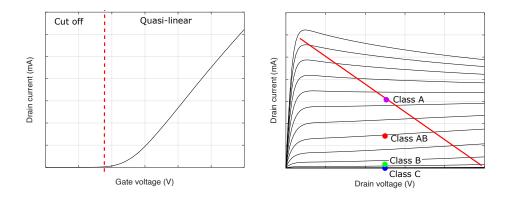

Figure 1.4: Visual representation of bias points for class A, B, AB.

#### 1.2.3 High-efficiency PAs

In the last section, the reconfigurability of PAs is analyzed with the advantage of reducing the space occupation of the transmitter front-end when multiple bands should be supported. In addition to this aspect, the optimization of the amplifier efficiency should also be considered. Similarly to the results drawn in Sec. 1.1 for the network infrastructure, also in hand-held devices, the RF transmitter stage is the main energy-consuming element. Moreover, all the power not employed in wireless communication is converted to heat that needs to be extracted from the chip, usually drying out more space from the device.

Classical MMIC PA designs focus on achieving the best power-added efficiency (PAE) at the peak of the output power that the amplifier should provide. While this reduces the power loss where the maximum consumption is expected, with modern signal modulations, the peak output power is rarely achieved. This is particularly true when the amplifier is operated in class A, B, or AB. In these modes, the bias point provided to the amplifiers goes in the direction of achieving high linearity performances, penalizing the power efficiency. As visible in Fig. 1.4, class A bias point is selected in order to have a current conduction angle of  $\theta = 2\pi$ , therefore producing the maximum output voltage-current swing. In contrast, class B operation moves the bias point at a lower current, corresponding to a current conduction angle of  $\theta = \pi$ , slightly reducing linearity performances but with substantial power reduction. The ideal efficiencies expected from the two topologies are 50% and 78.5% for classes A and B, respectively, which are insufficient for modern PAs.

Several advancements have been made in PA technology to address these challenges, usually involving additional hardware to adapt the power amplifier to the input signal, dynamically changing its configuration. Among these, innovations in circuit design, such as Doherty amplifiers [34], Envelope Tracking [35], and Outphasing techniques,

have been explored to enhance the efficiency and linearity of RF PAs under dynamic operating conditions, usually linked to the instantaneous power of the input signal. Two techniques, in particular, are the object of study in this thesis; therefore, a detailed analysis is provided below.

#### Load modulation

At its core, load modulation refers to the dynamic variation of the load impedance seen by a power amplifier as a function of its output power or signal characteristics. In traditional fixed-load power amplifiers, the impedance of the load remains constant, tuned for delivering the optimal performance at the highest output power. While this approach simplifies design, it often results in inefficiencies, especially for signals with high peak-to-average power ratios (PAPR). For instance, when the output power is low, the load impedance can be increased, reducing the current through the device and thereby minimizing power dissipation. Conversely, at higher output powers, the impedance is lowered to allow maximum power transfer while maintaining efficiency. This adaptability enhances overall efficiency across the amplifier's operational range.

One of the most prominent implementations of load modulation is the Doherty power amplifier, originally presented in [36], which employs multiple active devices to modulate the load impedance. In a Doherty architecture, a main amplifier operates continuously, while one or more auxiliary amplifiers activate only at higher power levels. The interaction between these amplifiers adjusts the effective load impedance seen by the main amplifier, allowing efficient operation across a wide dynamic range.

Other techniques, such as outphasing PA [37] split the input signal in two paths, each one with its own amplifier, and exploit the phase difference of the output current of the two amplifiers. The combination of the two impacts the load exhibited to the two amplifiers, adapting the loadline to the desired output power. Despite outphasing PAs demonstrate better performances than Doherty counterparts, many implementation drawbacks prevent the diffusion of these solutions in wireless systems. Wide input signal bandwidth are required, necessitating wideband amplifiers for the two stages, and the mismatches on the circuit layout could impact heavily on the losses, particularly on the output combiner.

#### Supply modulation

Traditional PA design methodologies focus on impedance matching at the maximum power the amplifier can provide, targeting the worst-case scenario the amplifier might face. On one hand, this helps to limit the heat generated when maximum current

Figure 1.5: (a) Block diagram of EER amplifier; (b) block diagram of ET amplifier.

is drawn, but on the other, it reduces efficiency when lower power levels are required. Adaptively changing the power supply-thus limiting the maximum power the amplifier can deliver-improves performance, especially when modulated signals are involved. Two architectures are known to achieve this goal, namely Envelope Elimination and Restoration (EER) [38] and Envelope Tracking (ET). Both designs make use of two amplifiers, one of which feeds the supply input of the other.

In EER systems, the input signal is split into two separate paths: one carrying the phase information with a constant envelope, and the other containing only the amplitude (envelope) information [Fig. 1.5.(a)]. This separation allows the amplification process to be optimized for efficiency. The phase-modulated path is handled by a highly efficient non-linear power amplifier, such as a Class D or Class E amplifier, which excels at amplifying constant-envelope signals. Meanwhile, the envelope path is processed by a second amplifier, known as the supply modulator, which modulates the supply voltage or bias of the main amplifier. This process reintroduces the original amplitude variations into the amplified signal. While EER provides significant efficiency benefits, particularly at high output power levels, it does come with challenges. One major issue arises at low RF output power, where the envelope amplifier (EA) can suffer from reduced efficiency, depending on the specific implementation. EA performance is further constrained by the need for high switching frequencies and strict linearity requirements, as it must accurately reproduce the signal envelope. As signal bandwidth increases, the output filter design becomes more complex, often requiring higher-order filters that are sensitive to variations in load impedance. Moreover, the constant-envelope phase-modulated RF signal can exhibit a bandwidth up to ten times greater than that of the original input signal, demanding the main amplifier to operate at significantly higher performance levels. To mitigate these issues, the EA can be combined with a linear amplifier, which enhances low-power performance at the cost of increased complexity and reduced overall efficiency. Alternatively, hybrid operating modes have been developed in which the EER amplifier operates in its standard configuration for high-power signals but switches to linear behavior at low envelope levels [39]. Digital control solutions for the EA have also been introduced [40], improving efficiency by dynamically adjusting the amplifier's operation. However, these digital approaches increase system complexity, requiring more silicon area and high-speed control circuitry. Additionally, the increased complexity can degrade synchronization between the EA and the main amplifier, introducing distortion in the output signal. This balance between efficiency, complexity, and performance highlights the trade-offs inherent in EER designs, particularly as modern communication systems demand higher bandwidths and more stringent performance requirements.

In ET architectures, the supply voltage of the main amplifier is dynamically adapted according to the instantaneous power of the input RF signal (Fig. 1.5(b)). For this technique, the main amplifier typically operates in linear classes, such as Class AB or Class B, in order to preserve the required linearity performance. The supply voltage is continuously adjusted following the envelope of the input signal, allowing the main amplifier to operate closer to its saturation region, thereby improving overall efficiency while maintaining acceptable linearity. Unlike EER, where the envelope and phase components of the signal are separated and handled by two different amplifier paths, ET maintains a single RF path and modulates only the supply voltage. This simplifies the signal reconstruction process and reduces the synchronization challenges commonly associated with EER.

Although ET introduces increased circuit complexity and design challenges, virtually all modern base stations implement power amplifiers composed of more than one basic amplifier [41]. In particular, ET is considered one of the most promising candidates due to its superior performance in covering large bandwidths, especially when compared to narrower-band solutions such as the Doherty amplifier. Moreover, ET proves advantageous in real-world scenarios where the output power can vary significantly over time, such as during different periods of the day.

#### 1.3 Varactor devices

Variable capacitors, also referred to as varactors, represent a valuable choice for obtaining continuously tunable circuits to achieve PA adaptability. Varactors are designed to act as non-linear passive components used in replacement of fixed capacitors. They represent the main component in voltage-controlled oscillators (VCOs) [42] where an input voltage control is responsible for tuning the oscillator frequency. Other applications include patch antennas [43], filters [44] and phase-shifters [45].

Looking at the qualitative performance reported in Table 1.1, it is evident that

|      | Tunability | RF losses (Q) | Control  | Tuning           | Power    |

|------|------------|---------------|----------|------------------|----------|

|      |            |               | voltage  | $\mathbf{speed}$ | handling |

| GaAs | High       | Moderate      | < 20 V   | Fast             | Low      |

| BST  | Moderate   | Moderate      | 10-20 V  | Fast             | High     |

| MEMS | Low        | Very good     | 50-100 V | Slow             | High     |

Table 1.1: Qualitative performances for three varactor technologies.

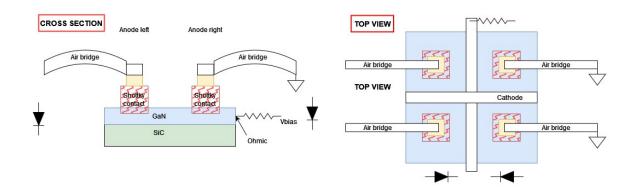

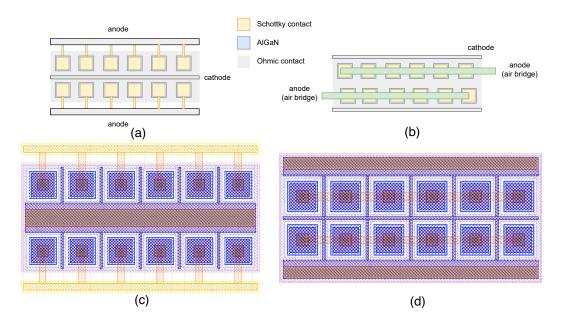

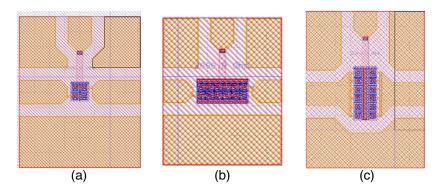

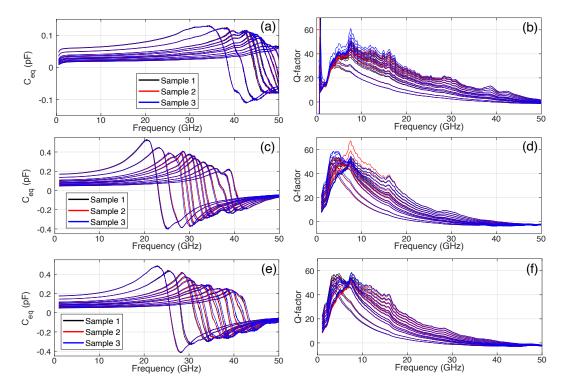

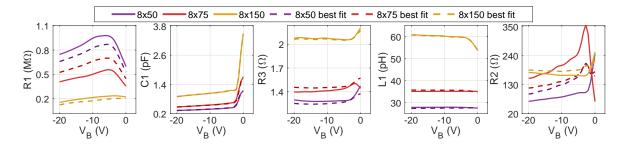

Figure 1.6: Cross-section representation of MEMS varactor from [2]. Two different states are highlighted, exhibiting different capacitance.