## DOTTORATO DI RICERCA IN

# Ingegneria Elettronica, Telecomunicazioni e Tecnologie dell'Informazione

#### Ciclo XXXVII

Settore Concorsuale: 09/H1 - SISTEMI DI ELABORAZIONE DELLE INFORMAZIONI

Settore Scientifico Disciplinare: ING-INF/05 - INFORMATICA

Optimized Algorithms and Machine Learning Techniques for Biosignal Processing on Ultra-Low-Power Computing Platforms

Presentata da: BENEDETTA MAZZONI

Coordinatore Dottorato Supervisore

Prof. DAVIDE DARDARI Prof. LUCA BENINI

Esame finale anno 2025

### ALMA MATER STUDIORUM - UNIVERSITY OF BOLOGNA

# Optimized Algorithms and Machine Learning Techniques for Biosignal Processing on Ultra-Low-Power Computing Platforms

by

Benedetta Mazzoni

A thesis submitted for the degree of Doctor of Philosophy

$\label{eq:Faculty} \mbox{ in the } \\ \mbox{ Faculty of Engineering } \\ \mbox{ Department of Electrical, Electronic, and Information Engineering (DEI)}$

February 2025

## Acknowledgments

I wish to thank Prof. Luca Benini for the opportunity to pursue my Ph.D. in his research group and for his constant guidance. I specifically appreciated Prof. Giuseppe Tagliavini and Prof. Simone Benatti for their persevering supervision, their teachings, and the motivation they gave me. I thank them for the support and independence they gave me.

I thank Prof. Andrea Cossettini for welcoming me and following my work to his PULP group at ETH for a visiting research period.

I also thank GreenWaves Technologies for the preview access to the GAP SDK.

In closing, I would like to express my gratitude to all my colleagues at the EEES Lab for creating an enjoyable and inspiring environment.

## **Abstract**

In recent years, advancements in electronic systems have driven the development of implantable and wearable devices that facilitate continuous health monitoring through the extraction of physiological parameters from biosignals, such as Electrocardiogram (ECG) and Electroencephalogram (EEG). Biosignal-based applications have become central to various fields, ranging from fitness to medical-grade diagnostics. However, implementing biosignal processing presents significant challenges, notably in achieving a balance between computational power and energy efficiency, which is essential for extended battery life in portable devices.

This thesis contributes to this field by presenting a framework of end-to-end methodologies designed to optimize energy efficiency in executing computationally intensive signal processing tasks on resource-constrained embedded devices. Through a combination of optimized system architectures, low-power processing strategies, and machine learning-based algorithms, the thesis offers novel solutions for achieving high-performance ExG signal analysis within strict energy budgets. Key aspects include the design of Analog Front Ends (AFEs) to ensure high-fidelity signal capture with minimal energy draw, as well as optimizing digital processors to handle complex operations such as filtering, feature extraction, and pattern classification within limited memory and processing power. Additionally, this research explores the adaptation of machine learning algorithms, such as CNNs and TCNs, for edge-based biosignal processing, emphasizing model compression to reduce computational overhead.

The research demonstrates a sustainable solution for real-time biosignal processing on ultra-low-power (ULP) parallel platforms, offering significant advantages over traditional MCUs in both energy efficiency and processing capability. To validate the proposed methodologies, the thesis investigates two primary case studies. The first focuses on ECG signal processing and classification, showcasing how on-device computation minimizes data transmission and latency, thereby improving privacy, energy efficiency, and responsiveness. The second evaluates ear-EEG as a promising alternative to conventional, full-scalp EEG, demonstrating its viability in mobile health applications.

This dissertation advances the design of energy-efficient biosignal processing systems for wearable and implantable devices, emphasizing the synergy between optimized hardware, low-power digital processing, and machine learning algorithms to enable real-time, on-device biomedical analysis.

## Contents

| A  | ckno   | wledgr | nents                                                      | iii        |

|----|--------|--------|------------------------------------------------------------|------------|

| A  | bstra  | ıct    |                                                            | iv         |

| Li | ist of | Figur  | es                                                         | vi         |

| Li | ist of | Table  | s<br>S                                                     | ix         |

| 1  |        | roduct |                                                            | 1          |

|    | 1.1    | Contr  | ibutions & Thesis Structure                                | . 3        |

| 2  | Bac    | kgrou  | nd                                                         | 7          |

| -  | 2.1    | _      | edical Applications based on ECG and EEG Signals           |            |

|    |        | 2.1.1  | Electrocardiogram (ECG)                                    |            |

|    |        | 2.1.2  | Electroencephalogram (EEG)                                 |            |

|    | 2.2    | Time-  | Series Biosignal Data Analysis                             |            |

|    |        | 2.2.1  | Biosignal Processing: Methodology                          |            |

|    |        | 2.2.2  | Challenges in Edge Computing                               | . 18       |

|    |        | 2.2.3  | ECG and EEG analysis on the edge: an Overview              | . 19       |

|    | 2.3    | Micro  | controllers of Interest                                    | . 20       |

|    | 2.4    | Embe   | dding Networks: Compression & Deployment                   |            |

|    |        | 2.4.1  | Quantization                                               | . 24       |

|    |        | 2.4.2  | Frameworks and tools for embedded neural inference         | . 25       |

| 3  | FC     | C Apr  | olications - Efficient Transforms and Heart Rate Detection | 2          |

| J  |        | orithm |                                                            | <b>2</b> 8 |

|    | 3.1    |        | -<br>Description and Acquisition                           |            |

|    | 3.2    |        | ent Transforms                                             |            |

|    |        | 3.2.1  | Related Work                                               |            |

|    |        | 3.2.2  | Algorithms Design                                          |            |

|    |        | 3.2.3  | Results                                                    | . 32       |

|    | 3.3    | Optim  | nized Heart Rate Detection System                          | . 37       |

|    |        | 3.3.1  | Related Work                                               | . 38       |

|    |        | 3.3.2  | System Architecture                                        | 40         |

|    |        | 3.3.3  | Algorithm Description                                      | 41         |

|    |        | 3 3 /  | Evaluation                                                 | 43         |

*Contents* vi

|    |       | 3.3.5 Implementation on the PULP platform         | 44             |

|----|-------|---------------------------------------------------|----------------|

|    |       | 3.3.6 Performance analysis and energy consumption | 46             |

|    |       | 3.3.7 Algorithm Accuracy                          | 46             |

|    |       | 3.3.8 Discussion                                  | 47             |

| 4  | ECC   | G Applications - ML approach                      | 49             |

|    | 4.1   | ML approach for ECG inference                     | 49             |

|    |       | 4.1.1 Related Work                                | 53             |

|    | 4.2   | CNN Methodology                                   | 55             |

|    |       | 4.2.1 Hardware platform                           | 55             |

|    |       |                                                   | 56             |

|    |       | 4.2.3 1-D CNN architecture                        | 56             |

|    |       | 4.2.4 Dataset                                     | 58             |

|    |       |                                                   | 59             |

|    | 4.3   | <u> </u>                                          | 60             |

|    |       | 1                                                 | 61             |

|    |       |                                                   | $\frac{1}{62}$ |

|    | 4.4   |                                                   | 62             |

|    | 4.5   |                                                   | 65             |

|    |       |                                                   | 65             |

|    |       |                                                   | 65             |

|    | 4.6   |                                                   | 69             |

|    | 4.7   |                                                   | 70             |

| 5  | EEC   | G Applications                                    | 72             |

|    | 5.1   | **                                                | 72             |

|    | 5.2   | •                                                 | 73             |

|    | 5.3   | Methodology                                       |                |

|    | 0.0   |                                                   | 74             |

|    |       |                                                   | 75             |

|    | 5.4   |                                                   | . o<br>76      |

|    | 0.1   | •                                                 | . o<br>77      |

|    |       |                                                   | <br>78         |

|    | 5.5   |                                                   | . o<br>79      |

|    | 0.0   |                                                   | . o<br>79      |

|    |       |                                                   | 80             |

|    |       |                                                   | 81             |

|    | 5.6   |                                                   | 82             |

|    |       |                                                   |                |

| 6  | Con   | aclusion 8                                        | <b>84</b>      |

| Ri | hliog | raphy 8                                           | 86             |

## List of Figures

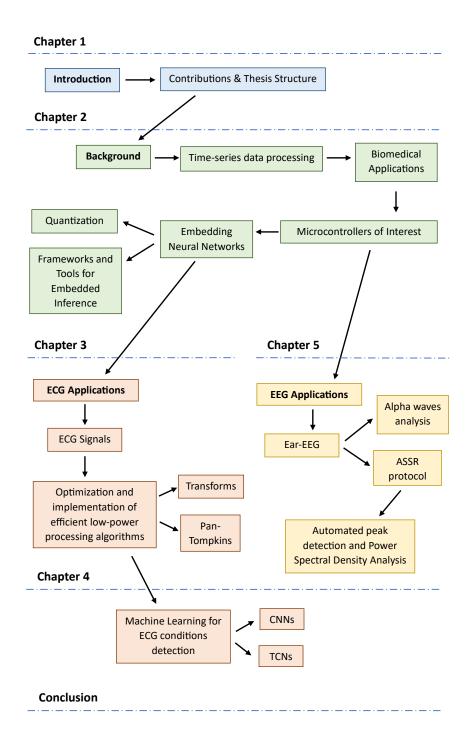

| 1.1  | Scheme of the contents of this thesis.                                                                                                              |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

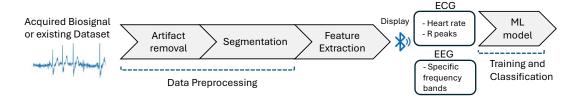

| 2.1  | Design methodology on wearable devices applied in this dissertation                                                                                 |

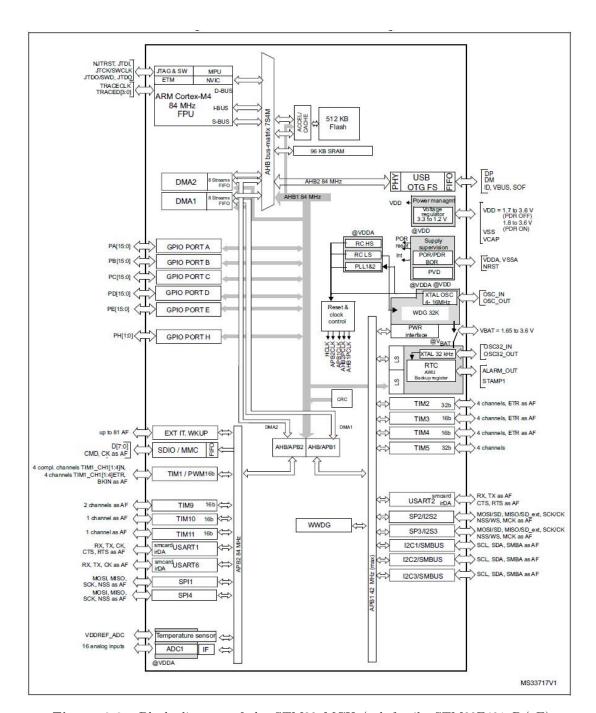

| 2.2  | Block diagram of the STM32 MCU (sub-family STM32F401xD/xE). Image source: [115]                                                                     |

| 2.3  | Block diagram of the GWT GAP8 microcontroller. Image source: [117].                                                                                 |

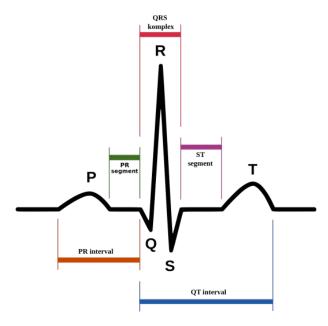

| 3.1  | The PQRST wave represents the complete electrical cycle of a single heartbeat. Image source: [152]                                                  |

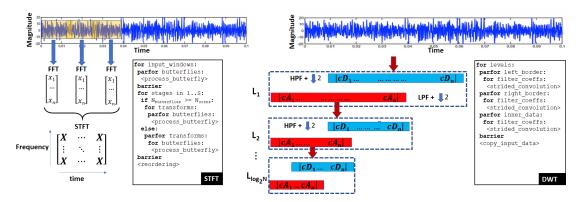

| 3.2  | Structural and working flow diagrams of STFT and DWT                                                                                                |

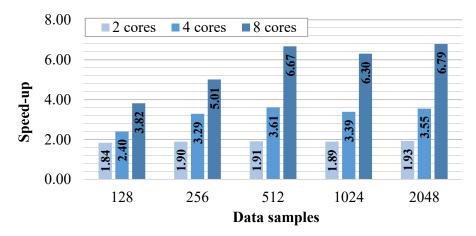

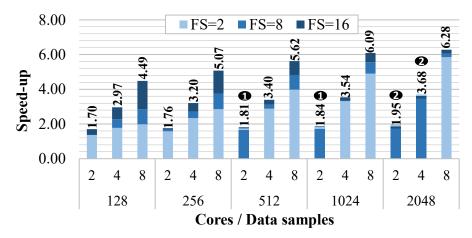

| 3.3  | Speed-up of STFT varying the number of cores and the input size                                                                                     |

| 3.4  | Speed-up of DWT varying the number of cores, the input size, and the                                                                                |

|      | filter size $(FS)$                                                                                                                                  |

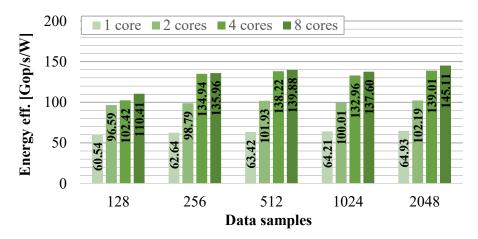

| 3.5  | Energy efficiency of STFT varying number of cores and input size                                                                                    |

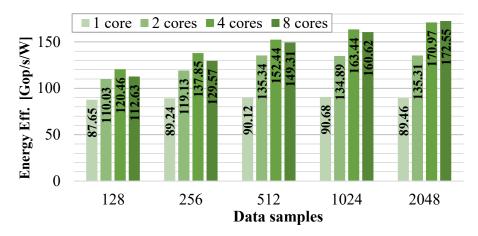

| 3.6  | Energy efficiency of DWT varying number of cores and input size                                                                                     |

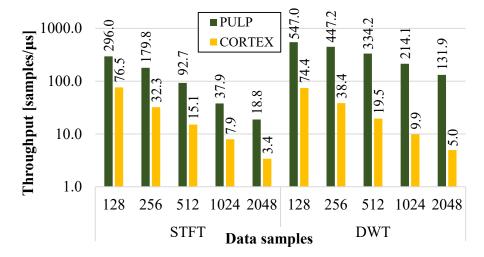

| 3.7  | STFT and DWT throughput on PULP / Cortex-M4 varying input size                                                                                      |

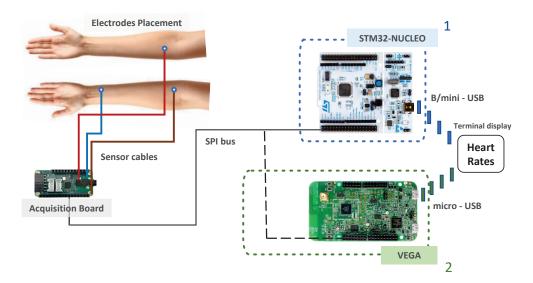

| 3.8  | Hardware diagram of the proposed system. The active electrodes are                                                                                  |

|      | located on each forearm and one on a wrist, setting Lead I for the col-                                                                             |

|      | lected data. Single-channel ECG is acquired with a custom AFE board                                                                                 |

|      | (MAX30003), which sends data via SPI to the platform for processing.                                                                                |

|      | We consider two alternative designs: (1) STM32NUCLEO for the initial                                                                                |

|      | setup and (2) Vega for ULP optimization. Output and communication                                                                                   |

|      | are managed via a B/mini-USB and a micro-USB cable, respectively, that                                                                              |

| 0.0  | leads the platform to a terminal to visualize the HR values                                                                                         |

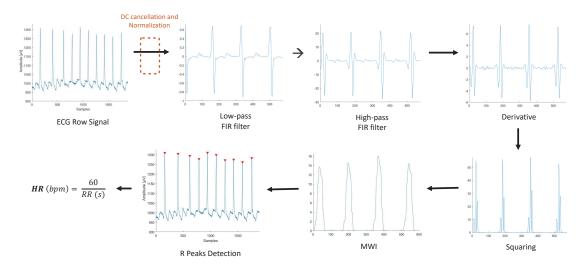

| 3.9  | Signal processing steps based on PT technique: (1) Cancellation of DC                                                                               |

|      | component and addition of Normalization; (2) Band-pass filter that combines the low- and the high-pass filters; (3) Derivative function; (4) Squar- |

|      | ing function; (5) Moving window integrator (MWI); (6) R peaks detection.                                                                            |

|      | In the last step, we compute the HR in beats per minute                                                                                             |

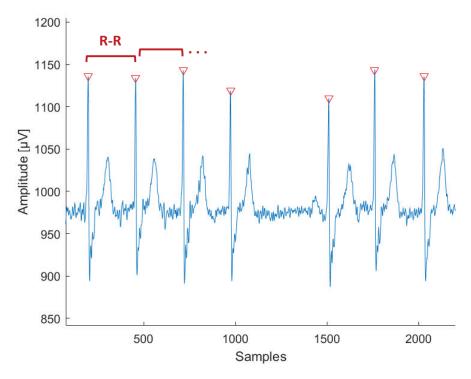

| 3 10 | Output result of the proposed R peaks detection and R-R intervals method                                                                            |

| 0.10 | from a segment of record 232 characterized by the supraventricular ectopic                                                                          |

|      | beats from the MIT-BIH database                                                                                                                     |

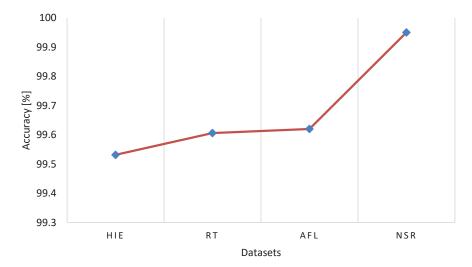

| 3.11 | Accuracy evaluation on four different datasets: High-Intensity Exercise                                                                             |

|      | (HIE) [174], acquired ECG signal in real-time (RT) with the proposed                                                                                |

|      | system design, Atrial Flutter (AFL) [173], and Normal Synus Rhythm                                                                                  |

|      | (NSR) [173]                                                                                                                                         |

| 11   | C                                                                                                                                                   |

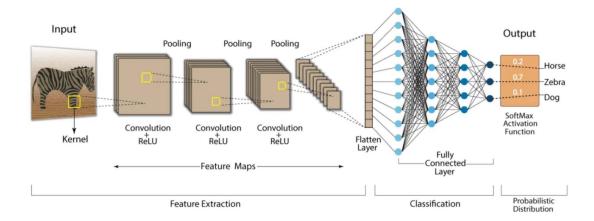

| 4.1  | Complete CNN representation. Image source: [183]                                                                                                    |

| 4.2  | TALE ALCHITECHITE GIARTAIL                                                                                                                          |

List of Figures viii

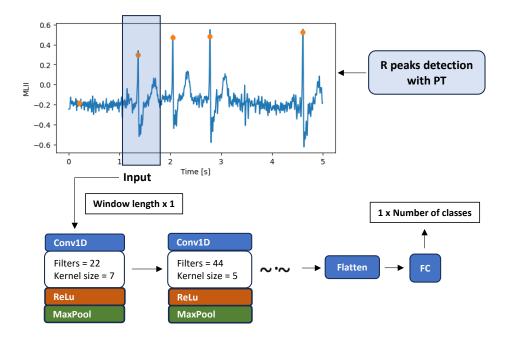

| 4.3  | Processing pipeline for ECG signal classification. The input is a window of 256 samples (one heartbeat) centered on the R peak. The CNN design includes multiple sub-blocks, progressively increasing the number of filters and reducing the kernel size, followed by a dimensional flattening and a |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | fully connected (FC) layer                                                                                                                                                                                                                                                                           | 56 |

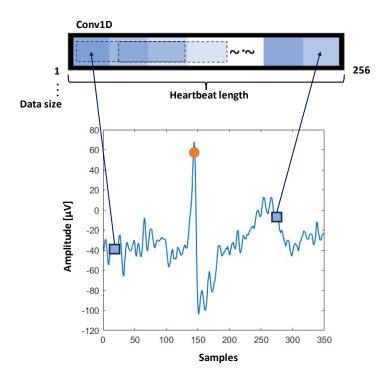

| 4.4  | The details of the Conv1D kernel processing a single heartbeat segment (256 samples), with the R peak of the heartbeat highlighted. The dashed squares illustrate the sliding windows used in the convolution process                                                                                | 58 |

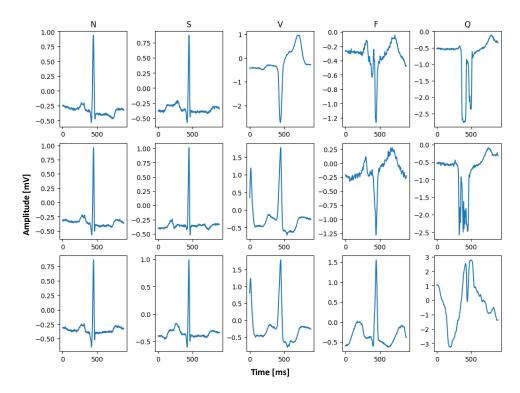

| 4.5  | Variations in heartbeat patterns across five classes in three subjects taken randomly from the MIT-BIH Arrhythmia Database                                                                                                                                                                           | 60 |

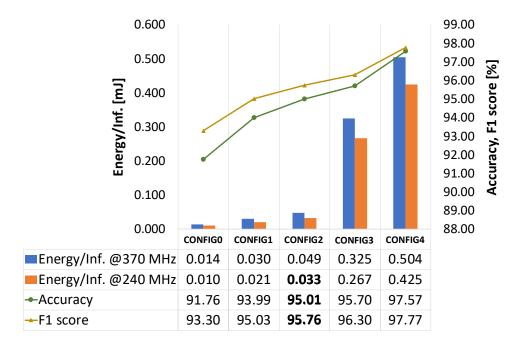

| 4.6  | Energy consumption across five configurations with <i>INT8-NE16</i> . At 240 MHz, CONFIG2 is the best trade-off between energy and accuracy                                                                                                                                                          | 61 |

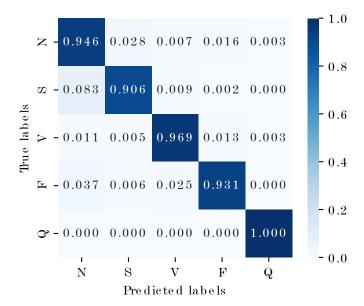

| 4.7  | Confusion matrix that displays the probability of true positives within the test set for CONFIG2 with INT8-NE16                                                                                                                                                                                      | 63 |

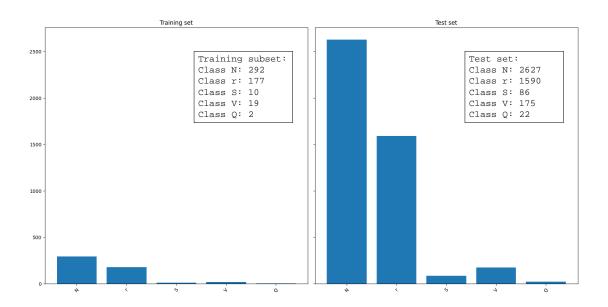

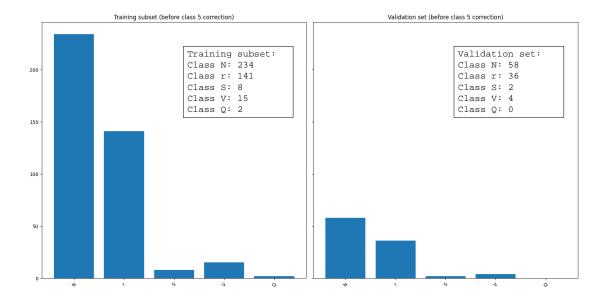

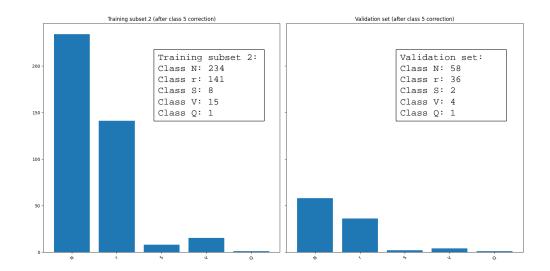

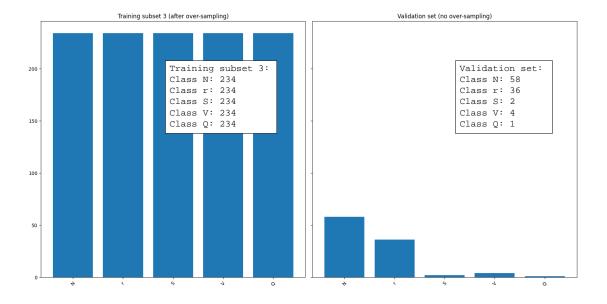

| 4.8  | Oversampling and mapping of dataset labels. Train data and test data                                                                                                                                                                                                                                 | 66 |

| 4.9  | Oversampling and mapping of dataset labels. Training data is split into training subset and validation data                                                                                                                                                                                          | 66 |

| 4.10 | Oversampling and mapping of dataset labels. Class 5 (Q) correction. Class 5 is in the training subset and validation data                                                                                                                                                                            | 67 |

| 4.11 | Oversampling and mapping of dataset labels. Oversampling on the training subset                                                                                                                                                                                                                      | 67 |

| 5.1  | Ear-EEG electrode fabricated by Dätwyler Schweiz AG and connected to an active buffering PCB                                                                                                                                                                                                         | 74 |

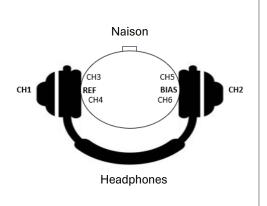

| 5.2  | Channels placement and electrodes configuration on a test subject                                                                                                                                                                                                                                    | 75 |

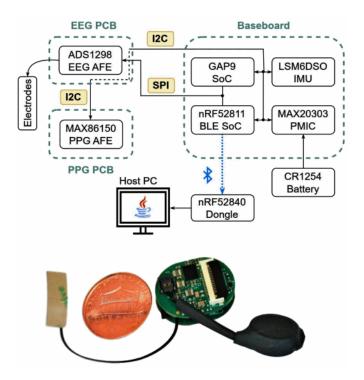

| 5.3  | System diagram (top) and photo (bottom) of the BioGAP platform next to a one-cent coin. Image source: [228]                                                                                                                                                                                          | 77 |

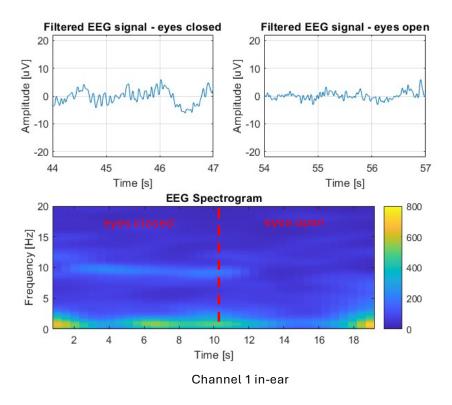

| 5.4  | Measurement of the alpha wave activity in eyes closed vs eyes open condition of CH1 in-ear. Filtered signal in the time domain (TOP) and spectrogram (BOTTOM)                                                                                                                                        | 78 |

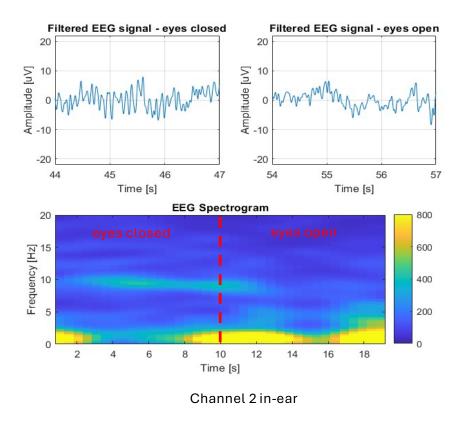

| 5.5  | Measurement of the alpha wave activity in eyes closed vs eyes open condition of CH2 in-ear. Filtered signal in the time domain (TOP) and                                                                                                                                                             |    |

| F C  | spectrogram (BOTTOM)                                                                                                                                                                                                                                                                                 | 79 |

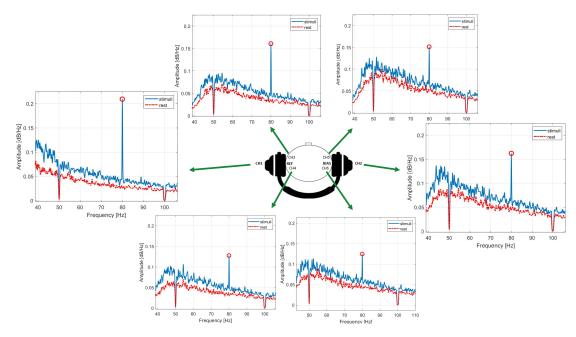

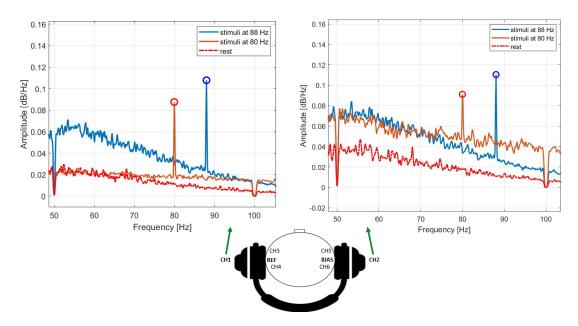

| 5.6  | Power spectra at 80 Hz AM stimuli across all channels. CH1 and CH2 represent the in-ear channels of primary interest                                                                                                                                                                                 | 81 |

| 5.7  | In-ear CH1 and CH2 power spectra comparison at 80 and 88 Hz AM stimuli.                                                                                                                                                                                                                              | 82 |

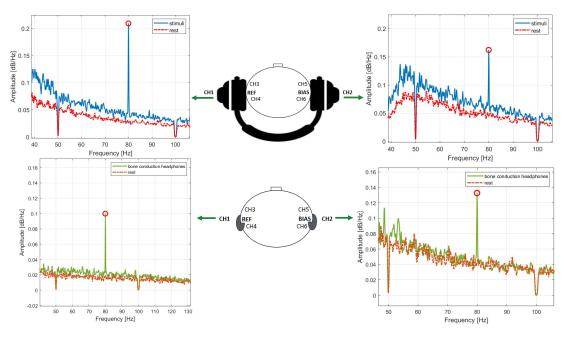

| 5.8  | In-ear CH1 and CH2 signal power spectra comparison at 80 and 86 Hz AM seminin. In-ear CH2 and CH2 signal power spectra comparison between over-the-ear (TOP) and bone-conduction headphones (BOTTOM) at 80 Hz AM                                                                                     | 02 |

|      | stimuli and rest condition                                                                                                                                                                                                                                                                           | 83 |

## List of Tables

| 3.1 | Instructions, hardware stalls, synchronizations occurrences, and through-                                                                      |   |     |  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|--|

|     | put (execution on 8 cores, 2048 data samples)                                                                                                  | , | 33  |  |

| 3.2 | Comparison with GSL and Kiss FFT on 8-core PULP (cycles)                                                                                       |   | 36  |  |

| 3.3 | Cycles for each sample, Instructions, Energy Efficiency, Throughput, and Time executing on the target platforms (average values on a 25 s time |   | 4.0 |  |

|     | window)                                                                                                                                        |   | 46  |  |

| 3.4 | Energy consumption of different SoA solutions for R peak detection (av-                                                                        |   |     |  |

|     | erage values on a 25 s time window).                                                                                                           |   | 46  |  |

| 3.5 | Comparison of R peaks accuracy.                                                                                                                |   | 47  |  |

| 4.1 | Comparison of the performance across data types                                                                                                |   | 57  |  |

| 4.2 | Performance comparison with the SoA                                                                                                            |   | 64  |  |

| 4.3 | Accuracy, Balanced Accuracy, and Number of Parameters on SoA                                                                                   |   | 69  |  |

| 4.4 | Energy consumption compared with SoA solution considering one heart-                                                                           |   |     |  |

|     | beat as input of the network.                                                                                                                  |   | 71  |  |

| 5.1 | Electrodes allocation and types                                                                                                                |   | 76  |  |

## Chapter 1

## Introduction

Rapid advances in miniaturized and efficient electronic systems fuel the development of discrete, implantable, and wearable devices, [1]. leading to exciting new applications. Small-sized devices have gained popularity in healthcare and commercial applications due to their portability [2]. These systems facilitate continuous monitoring of health conditions by extracting physiological parameters from biosignal analysis [3]. The body's physiological activity generates biosignals, such as Electrocardiogram, Electroencephalogram, and Electrooculographic (ExG), which provide information on biomedical parameters directly related to a person's health status or enable pattern extraction for direct communication with the external environment.

The growing trend of small form factor devices is pushing the development of wearables, driven by systems such as health patches and trackers [4], [5]. In the fitness and healthcare area, these systems facilitate remote and continuous monitoring of wellness conditions, extracting physiological parameters from the analysis of biosignals [6].

Biosignal-based applications are beneficial in various fields, from consumer electronics (e.g., fitness) [7] to medical-grade equipment (e.g., patient monitoring) [8]. For instance, fitness-focused smartwatches (e.g., Apple Watch Series, KardiaMobile, and QardioCore), pacemakers [9], and Holter monitors [10] use Electrocardiogram (ECG) analysis for heart rate monitoring and detection of general heart disease [11]. Electroencephalogram-based systems are also gaining popularity in wearable applications for the treatment of neurological disorders such as Parkinson's disease [12], [13], epilepsy [3], and hearing dysfunction [14], as well as for detecting drowsiness [15] and other conditions [16]. However, implementing these techniques requires significant computational power while maintaining low energy consumption, a challenge that has only recently become feasible for wearable devices. In fact, the main limitation of wearable sensor nodes is the need to

perform computationally demanding tasks with high energy efficiency to extend battery life

Examples of low-power digital design and efficient computational architectures [17], [18] have enabled the development of real-time systems capable of executing complex algorithms such as filtering [19], augmentation [18], and pattern identification [20].

Designing efficient real-time systems for processing biosignals presents several chal-The development of Analog Front Ends (AFEs) is crucial, as they must ensure accurate signal capture while minimizing power draw. For example, [21] propose ultra-low-power AFEs designed to reduce energy consumption during continuous ECG monitoring while maintaining signal fidelity. Optimizing digital processors for real-time ExG signal processing is also essential. These processors must perform computationally intensive tasks such as filtering, feature extraction, and classification, often with limited memory and processing power. This condition requires novel approaches in system-level architecture design, including power management strategies that extend battery life during continuous monitoring [22]. Algorithmic design also plays a significant role. Algorithms like the Pan-Tompkins algorithm for ECG signal processing have been optimized for real-time, low-power execution on embedded systems [23]. In recent years, machine learning (ML) is constantly gaining traction in biosignal processing by enhancing the accuracy, efficiency, and reliability of detection and diagnosis because of its ability to identify patterns and relationships within large and noisy datasets, which may not be apparent through traditional methods. However, applying advanced ML techniques (e.g., CNNs or TCNs) for feature extraction and classification introduces additional computational overhead, making it critical to adapt and compress these models for edge devices [24]. Addressing these challenges requires a holistic approach integrating advancements in AFEs, low-power digital processing, system architecture, and optimized algorithms to create efficient real-time systems for ExG signal processing.

Modern multi-core platforms designed for ultra-low power processing can handle computationally intensive algorithms while meeting real-time requirements, with power consumption limited to just a few milliwatts through power management techniques and near-threshold computing (NTC). NTC operates with supply voltages close to the transistor threshold, which can significantly reduce dynamic and static power consumption. This technique enables processors to achieve substantial energy efficiency by sacrificing clock speed in favor of increased parallelism. The target device used for the experimental assessment of this thesis work is the RISC-V Parallel Processing Ultra-Low Power (PULP) many-core platform. Compared to commercial MCUs (e.g., ARM Cortex M4), PULP-based architectures have demonstrated substantial computational power while

staying within an ultra-low power budget, making them suitable for various applications.

#### 1.1 Contributions & Thesis Structure

The contribution of the research presented in this thesis is the development of optimized end-to-end methodologies to achieve high energy efficiency in executing computationally intensive signal processing workloads for biomedical applications on resourceconstrained embedded devices. Specifically, this thesis describes novel system-level designs for leveraging architectural features through software and hardware optimizations, including parallel programming, specialized hardware, and memory management strategies. Multicore architectures can distribute tasks across cores, allowing faster data processing and helping meet real-time constraints in applications like ExG signal analysis. When a single processing unit can meet latency constraints, multiple cores running at lower frequencies can significantly reduce energy consumption, as demonstrated in low-power, multicore systems optimized for biomedical signal processing [25], [26], [25]. Additionally, general-purpose architectures benefit from specialized hardware accelerators, such as DSP or AI accelerators, designed to perform specific operations in a few clock cycles. These accelerators can substantially enhance latency and energy efficiency by offloading computationally intensive tasks from the main processor. By combining these methods, parallel and accelerator-based computing architectures enable new performance levels for real-time biomedical applications on constrained devices [27], [28]. Memory management in embedded systems is challenging due to limited resources, multi-level hierarchies, and stringent power and latency requirements, especially in applications with frequent data transfers. Efficient handling of these transfers is crucial to maintain performance and energy efficiency, as excessive data movement can drain power and increase delays, affecting real-time capabilities. Real-time applications of biosignal processing must orchestrate data movements to minimize latency and power consumption. In architectures with memory hierarchies, employing efficient data transfer strategies, such as data prefetching, memory tiling, and buffer management, can help reduce latency and minimize overhead, especially in resource-constrained environments [29], [30], [31], [32]. Techniques like Direct Memory Access (DMA) are also commonly used to offload data transfer tasks from the main processor, enhancing overall system performance and energy efficiency [33], [34],[35].

As a first case study, this thesis addresses the challenge of processing and classifying ECG signals directly on embedded systems, which offers significant advantages over traditional online processing with an external device, as is often required [36], [37].

Localized ECG processing reduces latency and data transmission requirements, which is advantageous for privacy, energy efficiency, and responsiveness in real-time applications [38]. These benefits make on-device processing especially suitable for wearable or implantable devices operating autonomously and maintaining reliable performance [39], [40]. The primary contribution in this context is the creation of a HW/SW co-design that supports inference on the edge. Current wearable devices on the market are reasonably reliable and accurate in providing heart rate data and detecting basic irregularities, such as atrial fibrillation (e.g., Fitbit Charge 5). However, their signal processbing typically relies on remote servers rather than on-device (edge) processing, necessitating a data connection for comprehensive analysis. While some advanced algorithms and ML techniques achieve high accuracy, they often involve memory usage that exceeds the capabilities of these devices and fail to report energy consumption values as in [41], [42], [43], [44].

As a second case study, this thesis considers Electroencephalogram (EEG) signals, particularly highlighting the advantages of ear-EEG over the traditional, full-scalp EEG configuration. While standard EEG systems typically require multiple electrodes positioned across the entire scalp to capture comprehensive brain activity, ear-EEG offers a promising alternative, enabling convenient, unobtrusive monitoring through electrodes embedded in or around the ear canal. This design reduces the discomfort and setup time associated with full-scalp EEG, thus making it especially suited for wearable devices and prolonged monitoring in everyday settings [45]. Kappel and Kidmose [46] conducted a comparative study between a dry-contact ear-EEG electrode and a scalp EEG wet electrode. Additionally, ear-EEG has shown comparable reliability in specific tasks such as sleep monitoring and auditory attention detection [47]–[49], suggesting it is a viable approach for tasks like audiometric characterization in mobile health applications [48], [50]. This study aims to leverage these advantages by evaluating ear-EEG's feasibility for audiometric assessment, a step toward integrating simplified, non-invasive brain-signal monitoring into compact wearable technology.

The contributions outlined above are elaborated in the following chapters as follows:

Chapter 2 presents the background of the research topics. It includes an in-depth description of the architectures explored in this dissertation (ARM Cortex and the PULP), with an insight into the quantization and deployment tools adopted for ML workloads. This chapter also introduces an overview of the current SoA for time-series data elaboration. Finally, the chapter describes the parallel programming methodology, focusing on the main concepts provided by the hardware abstraction layer (HAL).

Chapter 5 exposes the contribution of ear-based Electroencephalogram (EEG). The target is a wireless, parallel ultra-low-power data acquisition platform (BioGAP) paired

with in-ear EEG electrodes (SoftPulseTM, Datwyler Schweiz AG) to explore auditory-based EEG protocols. Validating the signal quality from the ear-EEG electrodes by analyzing alpha-wave responses and performing quantitative comparisons to standard wet-electrodes (positioned behind the ear), this work demonstrates that the in-ear electrodes allow the acquisition of high-quality EEG signals. It also includes the development of an Auditory Steady-State Response (ASSR)-based experimental protocol with a Python-based stimuli generator (sinusoidal tones with a carrier at 4 kHz and AM modulation at 80 Hz and 88 Hz) that delivers sounds to headphones. BioGAP was used to acquire EEG data from the ear-based electrodes, and an offline data analysis extracted the corresponding EEG response in the frequency domain. The analyses successfully detected the ASSR response from ear-EEG electrodes for multiple modulation frequencies (80 Hz and 88 Hz) and multiple stimulation setups (over-the-ear headphones and bone-conducting headphones). Additionally, the experiments proved the response comparable to the one from standard wet electrodes positioned behind the ear.

Finally, Chapter 6 concludes the presented research.

Figure 1.1: Scheme of the contents of this thesis.

## Chapter 2

## Background

This chapter will present the fundamental concepts that form the basis of the work discussed in this dissertation. Specifically, we will start with an overview of biomedical applications and then explain the fundamental principles of time-series biosignal data processing, which are essential for the biomedical applications discussed in the text. We will explore key techniques such as signal preprocessing, feature extraction, and classification methods. The chapter will highlight the SoA approaches, focusing on the emerging edge computing trend for biosignal analysis and machine learning models in this domain. Finally, the challenges associated with deploying complex biosignal processing systems on resource-constrained edge devices will be addressed, providing a comprehensive background for understanding the contributions made in this dissertation. Next, it will outline the categories of microcontrollers relevant to this thesis. The chapter will overview the tools and techniques for deploying ML models on embedded systems.

## 2.1 Biomedical Applications based on ECG and EEG Signals

Historically, human body signal monitoring was conducted in laboratories under medical supervision. However, advancements have enabled the development of devices that independently generate reliable data outside clinical settings. These devices allow continuous monitoring, with healthcare providers later analyzing the data to track health status or detect events, providing immediate feedback when necessary. Offline data processing also offers deeper insights into human physiological behaviors. Despite technological progress, there are still scenarios requiring improvement in biomedical devices. This dissertation explores efficient ECG arrhythmia detection and the feasibility of ear-based EEG. Before delving into detailed discussions in subsequent chapters, we

provide an overview of these application scenarios to highlight potential challenges and issues.

## 2.1.1 Electrocardiogram (ECG)

Electrocardiogram (ECG) monitoring is a widely used method for detecting cardiac arrhythmias, which are abnormal heart rhythms that can lead to severe health conditions, such as stroke, heart failure, or sudden cardiac arrest. The increasing prevalence of cardiovascular diseases and the need for early detection have driven advancements in ECG arrhythmia detection systems [51]. Efficient ECG detection systems are crucial for continuous monitoring and early diagnosis. Traditionally, ECG data has been collected using clinical-grade equipment, which requires patients to visit a healthcare facility and be monitored by a medical professional. However, with the rapid development of wearable technology and mobile health platforms, it is now possible to perform continuous ECG monitoring outside clinical environments. These systems detect irregular heart rhythms in real time, enabling timely intervention and reducing the risk of life-threatening events.

Typical components of an ECG arrhythmia detection system include:

- Wearable ECG sensors: Lightweight, portable devices that can be worn on the body to capture electrical signals from the heart.

- Signal processing algorithms: Techniques used to filter and preprocess ECG signals, removing noise and artifacts that may distort the data.

- Machine learning models: Algorithms designed to classify arrhythmias based on patterns in the ECG signals, enabling automated detection and diagnosis.

In wearable applications, ECG arrhythmia detection systems must balance accuracy, power consumption, and user comfort. Their success relies not only on accurate arrhythmia detection but also on continuous operation in resource-constrained environments [52]. While ECG arrhythmia detection systems have the potential to revolutionize cardiac care, several challenges remain in ensuring their efficiency and reliability. As a result, developers and researchers face various key issues when designing these systems.

ECG signals can be affected by various external factors, including motion artifacts, electromagnetic interference, and body positioning. Wearable sensors are particularly susceptible to noise due to movement and environmental influences. Therefore, one of the primary challenges is maintaining high-quality signal acquisition and preprocessing.

Effective noise-reduction techniques, including advanced filtering methods and adaptive algorithms, are crucial for minimizing distortions and enhancing signal clarity [53], [54].

For ECG arrhythmia detection systems to be effective, they must operate in real-time, continuously monitoring heart activity and providing immediate feedback. Real-time processing is particularly challenging for low-power wearable devices with limited computational resources since detection algorithms must be computationally efficient and accurate enough to avoid false positives or missed arrhythmias [55]. Changing the operational mode, the same algorithms can be applied in an offline processing scenario, which involves the post-acquisition analysis of ECG data over longer periods, providing insights that may not be immediately apparent. Moreover, continuous monitoring generates vast amounts of data, creating challenges for data compression and storage. Advanced machine learning algorithms can be highly beneficial in managing these datasets without losing critical information. Offline processing is valuable for retrospective studies, helping refine detection models by identifying subtle arrhythmias that might not trigger immediate alarms, providing insights for personalized treatments. The challenge is to ensure that offline methods are efficient, minimizing delays while maintaining high accuracy [56].

Machine learning models for arrhythmia detection require extensive datasets to accurately identify a broad range of arrhythmias [57]. However, ECG signals can vary widely due to individual differences such as heart anatomy, age, gender, and medical history. Ensuring models generalize well across diverse patient populations is a challenge, requiring fine-tuning to manage both common and rare arrhythmias while minimizing false alarms, which could lead to unnecessary interventions or patient anxiety.

Energy efficiency is essential for wearable ECG sensors to operate continuously without frequent recharging. This aspect is especially important for long-term monitoring in

patients with chronic conditions or those at high risk for cardiac events. Developers must

optimize power consumption while maintaining detection accuracy [58]. Since wearable

ECG systems are intended to be used over long periods, user comfort is an important

consideration. Devices that are too bulky or uncomfortable may lead to poor patient

compliance, reducing the effectiveness of the monitoring system. Developers must design discreet, comfortable, and easy-to-use sensors, such as armband devices [59], while

ensuring high signal quality.

Efficient ECG arrhythmia detection systems hold great promise for improving cardiac care by enabling continuous, real-time monitoring and early detection of heart abnormalities. However, the development of these systems is not without its challenges. Issues such as signal noise, real-time processing, model accuracy, energy efficiency, and

user comfort must be addressed to create reliable, user-friendly devices that can be deployed in everyday settings. As wearable technology advances, future research should focus on developing robust algorithms, improved signal processing techniques, and enhanced power management solutions. With these improvements, ECG arrhythmia detection systems will be instrumental in reducing mortality and improving the quality of life for millions with heart conditions.

#### 2.1.2 Electroencephalogram (EEG)

Advances in cognitive neuroscience have allowed us to interface directly with the human brain. Thanks to its effectiveness, low cost, and portability, the electroencephalography (EEG) signal is one of the most used techniques for investigating brain function and pathology, both in clinical settings and scientific research [60], [61], [62]. Among diagnostic and screening techniques, EEG analysis and instrumentation is an established standard, since it directly records the electrical field generated by neural activity. The most popular method uses a set of electrodes distributed on the head surface (scalp) [63]. However, other techniques and setups are being explored to enhance comfort and usability, such as ear-EEG systems. Ear-EEG employs sensors embedded in earphones or placed around the ear to capture brain signals in a more discreet and user-friendly manner [49].

This approach offers several advantages over traditional scalp EEG. First, ear-EEG is much more comfortable and non-invasive, allowing for prolonged use without the discomfort associated with scalp electrodes. It is also less obtrusive, making it suitable for real-world monitoring outside clinical environments. The compact and user-friendly design of ear-EEG systems makes them ideal for portable applications, enabling continuous brain activity monitoring during daily activities. Additionally, since ear-EEG systems can be integrated into common earphones, they provide a low-profile solution for neurophysiological monitoring, which may enhance user compliance and make long-term monitoring feasible. Despite these benefits, ear-EEG systems still face challenges in terms of signal quality and spatial resolution, as the signals recorded from the ear are generally weaker than those from the scalp. However, ongoing advancements in sensor technology and signal processing are working towards overcoming these limitations, making ear-EEG a promising option for applications such as auditory processing research, sleep monitoring, and cognitive workload assessment.

Electroencephalography (EEG) is a widely used method for non-invasively measuring electrical activity in the brain, providing insight into neural processes by capturing the voltages generated by synchronized neural activity at the scalp. Originating from the

firing of brain neurons, EEG signals are primarily the result of postsynaptic potentials rather than action potentials, which create measurable voltage changes that propagate through the brain tissue, skull, and scalp to reach the electrodes on the skin's surface [63], [64].

**EEG Signal Properties** EEG signals are characterized by oscillations across different frequency bands related to specific cognitive and physiological states. These include delta (0.5-4 Hz), theta (4-7 Hz), alpha (7-13 Hz), beta (13-30 Hz), and gamma (30+ Hz) bands, each associated with distinct types of brain activity. For instance, alpha waves are often linked to relaxation, while beta waves indicate active cognitive processing. However, EEG signals are inherently low-amplitude (between 10-100  $\mu$ V) and highly susceptible to noise, which can arise from various sources such as muscle movements, electrical interference, and impedance fluctuations at electrode sites [65], [66].

EEG Acquisition Techniques EEG acquisition typically employs electrodes placed on the scalp, arranged according to standardized positioning systems such as the 10-20 or 10-10 system, which enables consistent recording locations across individuals and studies [67]. Modern EEG systems may use either wet electrodes, requiring conductive gel for lower impedance, or dry electrodes, which allow for faster setup but with higher contact impedance that can reduce signal quality [68]–[70]. The selection of electrode type depends on the trade-off between signal quality and user comfort, especially in wearable or portable applications [71]. Advanced EEG systems, such as in-ear or ear-EEG devices, have also been developed to address specific application needs. These designs, which house electrodes in the ear canal or outer ear, offer a discrete and convenient form factor for monitoring brain activity, potentially suitable for long-term wearable use [72], [73]. Although they tend to capture a more localized signal than full-head systems, studies indicate that ear-EEG can still provide meaningful data for applications in sleep monitoring [47], [74], drowsiness [75], epilepsy [76]–[80] and auditory perception analysis [48], [49].

Challenges in EEG Acquisition One of the primary challenges in EEG acquisition is maintaining signal quality despite interference. Noise sources can include physiological artifacts (e.g., eye blinks and muscle contractions) and environmental noise, which can mask or distort the brain signals of interest. Strategies to mitigate these issues involve preprocessing techniques like artifact removal, filtering, and adaptive noise cancellation [81], [82]. Additionally, achieving a low-noise signal requires careful electrode placement and skin preparation to reduce impedance, which can be labor-intensive in

traditional systems. EEG acquisition faces additional constraints in embedded and low-power applications, which demand energy efficiency. Processing the signals in real-time with low latency while minimizing power consumption presents significant challenges, of-ten necessitating the integration of specialized signal processing techniques and machine learning algorithms optimized for energy-efficient hardware [83], [84].

EEG Applications A typical use case for EEG analysis is the examination of brain responses to specific stimuli. In particular, EEG has been widely used in Auditory Steady State Response (ASSR), significantly enhancing the understanding of how the brain processes auditory stimuli [85]. ASSR refers to the brain's continuous response to auditory stimuli presented at a fixed frequency, making it a valuable tool for assessing auditory system function. This is especially relevant in clinical contexts, such as diagnosing hearing impairments, auditory pathway dysfunctions, or brainstem anomalies. EEG is particularly well-suited for capturing ASSRs due to its non-invasive nature and high temporal resolution, enabling real-time analysis of auditory information processing. ASSR is elicited using repetitive auditory stimuli, typically pure tones or modulated sounds presented at specific frequencies (e.g., 40 Hz, 80 Hz) [86], [49]. These stimuli evoke periodic electrical responses, captured through EEG, as neural oscillations phase-lock to the stimulus frequency, creating a consistent pattern of brainwave activity. By analyzing these signals, researchers can assess the integrity of the auditory pathways and the brain's sound-processing capabilities.

ASSR is particularly valuable for estimating hearing thresholds in populations where behavioral responses are difficult, such as infants or individuals with cognitive impairments [50]. ASSR provides an objective measurement that can be used to determine hearing sensitivity across different frequencies. Clinicians use EEG-based ASSR to evaluate the integrity of auditory pathways from the cochlea to the auditory cortex, identifying specific dysfunctions and providing detailed insights into auditory processing deficits [87]. It is also useful in assessing hearing aid and cochlear implant effectiveness, enabling clinicians to fine-tune devices based on individual responses. In the research, ASSR studies help explore neural mechanisms underlying auditory perception, speech processing, and sound localization by analyzing brain responses to modulated sounds.

**EEG Analysis** To analyze EEG signals in the ASSR domain, estimating the Power Spectral Density (PSD) plays a critical role in measuring the brain's response to auditory stimuli. Several methods are commonly used, each with advantages and limitations.

1. The Welch method: a well-established technique in spectral analysis, it is widely used in ASSR studies to quantify EEG responses. It divides the EEG signal into

overlapping segments, applies a window function to each segment, and averages the resulting periodograms. This process reduces variance, providing a smooth and accurate PSD estimate, making it ideal for noisy, non-stationary EEG signals. The Welch method offers a balanced trade-off between spectral resolution and noise reduction, making it particularly effective for steady-state responses, where precise frequency analysis is crucial.

- 2. Multitaper method: this technique enhances spectral concentration by using multiple orthogonal tapers, improving variance reduction compared to single-taper approaches [88]. However, the fixed design of the orthogonal tapers used in multitapering can be less flexible compared to the wide range of window functions available in the Welch method.

- 3. Burg method: this method utilizes autoregressive modeling to estimate the PSD, offering high-frequency resolution and better handling of short data segments [89]. However, the estimated autoregressive model makes it less reliable for EEG signals that often contain noise from sources like muscle activity or electrical interference.

- 4. Thomson's multitaper method: this method applies multiple orthogonal tapers to achieve an unbiased and consistent PSD estimate [90]. The choice of the number of tapers and bandwidth parameters in Thomson's multitaper method can be more challenging to tune compared to the straightforward segment length and overlap settings of the Welch method. Furthermore, the multiple tapers can sometimes lead to over-smoothing of the power spectrum, which may obscure subtle frequency components in the ASSR signal, particularly when precision in distinguishing peaks is necessary.

Welch Method The Welch method is particularly effective in analyzing steady-state responses, such as those elicited by periodic auditory stimuli in ASSR experiments. This approach is ideal for EEG signals, which are typically noisy and non-stationary. By dividing the EEG signal into overlapping segments, applying a window function to each segment, and averaging the resulting periodograms, the Welch method enhances the accuracy and reliability of the spectral estimates, providing a balanced trade-off between spectral resolution and noise reduction. The EEG data recorded during an ASSR experiment are divided into overlapping segments. This segmentation is critical to reduce noise and improve the estimate's stability. A window function, such as a Hamming or Hann window, is applied to each segment to reduce spectral leakage. This smooths the edges of the segment, ensuring that discontinuities do not introduce artifacts into the frequency analysis. For each windowed segment, the power spectrum is calculated using the Fast Fourier Transform (FFT). The periodogram for each segment represents the

distribution of power across different frequencies. The periodograms of all segments are averaged to obtain a final PSD estimate. This averaging reduces the variance of the spectral estimate, providing a more accurate representation of the brain's response to the auditory stimulus. The method provides good frequency resolution, making it well-suited for ASSR studies where precise frequency analysis is essential. Since ASSRs are typically elicited at specific modulation frequencies, the Welch method ensures that the power at these frequencies can be accurately measured. The Welch method, by averaging across multiple segments, helps to account for these changes, providing more stable spectral estimates compared to single-segment approaches. In ASSR studies, the Welch method is typically used to measure the EEG response at the frequency of the auditory stimulus and its harmonics. By analyzing the power at these specific frequencies, researchers can determine whether the brain has successfully phase-locked to the stimulus. This analysis helps assess auditory function and detect abnormalities in neural processing. For instance, in a typical 80 Hz ASSR study, the EEG response is analyzed using the Welch method to estimate the power at 80 Hz. A strong peak in the power spectrum at 80 Hz indicates that the brain is successfully entraining to the auditory stimulus, suggesting normal auditory processing. Conversely, reduced or absent power at this frequency may indicate auditory dysfunction.

While the Welch method is highly effective in analyzing EEG responses to auditory stimuli, there are some challenges to consider. These include the selection of appropriate window length and overlap, which can impact the frequency resolution and the ability to detect the ASSR. Additionally, high noise levels in EEG signals may require advanced artifact removal techniques before applying the Welch method to ensure accurate results.

## 2.2 Time-Series Biosignal Data Analysis

Time-series data, particularly biosignals such as ECG and EEG, play a crucial role in modern healthcare. The ability to process biosignals effectively has led to the development of advanced diagnostic tools, wearable health monitors, and personalized medicine. Despite these advancements, processing biosignals in real-time and on-device (i.e., edge computing) remains a significant challenge. Most SoA systems rely on cloud-based processing, where raw or minimally processed data is transmitted to a central server for analysis, which introduces latency, data privacy concerns, and high energy consumption. This chapter discusses the SoA approaches in time-series biosignal data processing and highlights the limitations and challenges associated with edge computing for real-time biosignal analysis.

Figure 2.1: Design methodology on wearable devices applied in this dissertation.

#### 2.2.1 Biosignal Processing: Methodology

Time-series biosignal data are dynamic, often non-stationary, and exhibit noise due to physiological and environmental factors. Consequently, processing such data involves various pre-processing, feature extraction, and classification techniques. Historically, biosignal processing has been dominated by techniques focused on analyzing the frequency domain. In recent years, ML methods have gained momentum, with neural network architectures achieving SoA results in classification and prediction.

The process depicted in Figure 2.1, follows a pipeline consisting of:

- 1. Preprocessing: Removal of noise and artifacts using filters or preprocessing algorithms, such as the Pan-Tompkins algorithm. This step also involves *Segmentation*, which divides the time-series data into manageable windows or segments.

- 2. Feature Extraction: Deriving useful metrics, such as heart rate, PQRST wave characteristics in ECG, or specific frequency bands in EEG.

- 3. Training and Classification: Identifying patterns using ML algorithms or statistical methods.

This dissertation explores the benefits of implementing algorithms on edge parallel ultra-low-power (PULP) architectures, leveraging parallel computing inside a general-purpose multi-core accelerator (called *cluster*) along with extensive software and hardware optimizations. The goal is to maximize energy efficiency (i.e., prolong battery life) while ensuring high accuracy and low latency. The target embedded architectures are resource-constrained to enhance compactness and minimize energy consumption. A methodology must be applied to optimize resource utilization to fully exploit these architectures. Key considerations include achieving a high degree of parallelism in many-core implementations, optimizing execution through software or hardware enhancements, and effectively managing the available memory on the SoC. Since the cluster processing elements are general-purpose independent cores and execute separate instruction flows, the programming interface supports the single-program multiple-data (SPMD) paradigm.

The PULP HAL [91] provides two main concepts: core identifiers and barriers. The core identifier is a fundamental mechanism to split the workload among multiple execution flows (parallel orchestration). For instance, programmers can employ loop-level parallelism using core identifiers in the control expressions (i.e., initialization, condition check, and increment). A barrier is a HAL function that stops a core until all other cores arrive at the same execution point. Barriers are synchronization points that guarantee data consistency between adjacent code regions (before and after the barrier). The event unit [92] is a dedicated hardware component providing low-overhead support for barriers and enabling power-saving policies when cores are waiting.

To effectively implement an application on an embedded device, the initial step involves conducting a thorough feasibility study on both the application and the potential target architectures. This process can be achieved by breaking the application down into smaller components (kernels), analyzing each kernel individually along with the available resources on the architectures, and identifying which parts can be optimized and any potential challenges that may arise. Another crucial factor to consider is the optimal representation of the data. This analysis helps determine whether an integer implementation is suitable for our processing needs or if floating-point (FP) operations are necessary. In cases where the architecture lacks a Floating Point Unit (FPU), we must assess the impact of software-based FP simulations on performance, particularly for kernels that involve intensive FP computations. With these considerations in mind, we can make an informed decision regarding the architecture to target for our processing chain.

A recommended practice is to first implement the entire processing chain using a scripting tool (such as MATLAB) to create a golden model. This allows for a thorough verification of the theoretical accuracy of our implementation (including numerical results and overall precision) and enables comparison with the outcomes from the embedded implementation. The subsequent step involves transitioning to the actual implementation, where we examine the results of each kernel that makes up the final application in C code. During this phase, we should consider all potential optimizations and structure the code accordingly. This approach facilitates easier adaptation of the code to the targeted architecture. Once we have a stable version, we can begin the porting process to the target architecture, focusing on various optimizations to enhance execution speed.

Furthermore, for initial setup and algorithm tuning, the STM32Cube IDE provides a GUI that allows users to program STM32 MCUs to execute the code, also exploiting ARM CMSIS [93] kernels for the comparison of the results.

Techniques for Biosignal Pre-Processing and Inference This subsection explores the most common techniques in biosignal processing and inference. Traditional methods of biosignal processing have long been the foundation of biosignal analysis, enabling the extraction of meaningful features from raw data. Among these techniques, the Fourier Transform (FT) and Wavelet Transform (WT) are frequently used to analyze the spectral content of biosignals.

In ECG analysis, Fast Fourier Transform (FFT) is typically used to decompose heart rate signals into their constituent frequency components, which can provide insights into heart rhythm abnormalities [53] [94]. Wavelet-based methods have also been extensively applied to ECG signals for arrhythmia detection. Choi [95] highlighted how multi-level wavelet decomposition can isolate ECG signal features indicative of specific heart conditions. Zidelmal [96] applied DWT for ECG signal denoising, achieving superior results in noise suppression compared to traditional frequency-domain methods. Wavelet-based techniques also offer flexibility in handling non-stationary signals like ECGs, where the frequency content changes over time. For instance, Addison [97] showed how DWT can help identify different types of heartbeats by analyzing the ECG signal across multiple frequency scales. Additionally, ECG processing often involves multiple stages, including noise reduction. Techniques like band-pass filtering are applied to remove baseline wander and powerline interference, which can obscure critical ECG features. Arif et al. [98] discuss how filtering enhances the accuracy of subsequent ECG analysis.

To detect a person's alertness/drowsiness, Chen et al. [99] proposed a system that includes the decomposition of EEG data into wavelet frequency sub-bands and FFT-based spectral analysis for comparison. Then, they apply a single-hidden layer of feed-forward neural networks for the recognition. In another study [100], the authors focused on decoding the subjective perception of task difficulty to enhance operator performance by automatically optimizing task difficulty levels. The study used a protocol with two tasks, flying and visual recognition, to induce different difficulty levels and analyzed EEG signals to distinguish between compound cognitive states.

More recently, ML models have emerged as powerful tools for biosignal processing. Machine Learning models, such as CNNs, have demonstrated the ability to automatically learn features from raw time-series data, significantly reducing the need for manual feature engineering. For instance, the authors of [101] applied a 1D-CNN architecture for automatic ECG classification, achieving SoA performance on the MIT-BIH Arrhythmia dataset. Other ML models, such as Recurrent Neural Networks (RNNs), particularly LSTMs, have been effective in modeling the temporal dependencies inherent in biosignal data. Liu et al. [102] leveraged LSTMs for EEG-based emotion recognition, showcasing the potential of ML for decoding complex biosignals in real-time. Zhang et al. [103]

introduced the adaptive exponential smoothing (AES) technique for smoothing ECG and EEG signals in combination with a bounded support vector machine (BSVM) to classify different levels of operator mental workload.

Despite their effectiveness, the ML approaches require significant computational resources, making them unsuitable for real-time analysis on resource-constrained edge devices. Although these models achieve high accuracy, their deployment on edge devices remains limited due to large model sizes, high computational power demands, and substantial memory requirements. As a result, most current approaches still rely on cloud-based servers for model inference, with biosignal data being offloaded from the edge to the cloud.

## 2.2.2 Challenges in Edge Computing

Edge computing has emerged as a potential solution to address the limitations of cloud-based processing by moving computation closer to the data source. In an edge computing framework, biosignals are processed directly on the device, offering several advantages, including reduced latency, improved data privacy, and lower energy consumption due to reduced transmission of data. However, edge computing for biosignal processing has not yet been widely adopted. There are several technical and computational challenges associated with deploying complex biosignal processing algorithms on edge devices, which are typically constrained by limited processing power, memory, and energy capacity.

Resource Constraints Edge devices, such as wearable systems or portable health monitors, are often battery-operated and have limited computational resources. Running ML models on such devices requires significant model compression or hardware accelerators, which is still an evolving area of research. Sarkar et al. [104] showed that pruning and quantization techniques can reduce the size of neural networks, but there is often a trade-off between accuracy and computational efficiency.

**Energy Consumption** Most ML models for biosignal processing are computationally intensive. For edge devices, managing the energy consumption of these models is crucial to prolong battery life. The energy-efficient CNN-based approach for real-time ECG classification on edge devices proposed in [105] reduces energy consumption by 3x compared to traditional methods.

**Real-Time Processing**: Time-series biosignals, particularly in critical health applications, require real-time processing to provide immediate feedback (e.g., detecting abnormal heart rhythms in ECG). Attaran et al. [106] demonstrated a real-time system using edge computing, but the proposed method only detects stress conditions.

### 2.2.3 ECG and EEG analysis on the edge: an Overview

While the literature on edge computing for biosignal processing is still nascent, some notable works are paving the way.

Tsai et al. [107] developed edge-based techniques for QRS complex detection using a low-power ARM Cortex M4 processor. Their system, while the accuracy is not reported, demonstrated the feasibility of on-device processing for biosignals in resource-constrained environments. De Giovanni et al. [52] proposed a software-based methodology that implements a Bayesian filter, normalization, and a clustering technique to optimize the R peak detection for low-power platforms. However, the authors do not consider the aspects related to real-time signal acquisition due to the use of an existing system (BIOPAC) that requires a 9 V battery and is not energy efficient. Nguyen et al. [108] focused on EEG monitoring from wearable sensors. They applied the Welch method for the power spectral analysis as a preprocessing stage. To detect drowsiness, the authors employed two NN models (Multi-Layer Perceptron and CNN) and apply quantization techniques to reduce the computational complexity at the expense of negligible reduction in accuracy.

A convolutional autoencoder model is proposed in [109] for denoising single-lead ECG signals, optimized for low-power edge devices. It aims to reduce noise and motion artifacts in ECG data, improving the accuracy of detecting conditions like atrial fibrillation. Betti et al. [110] developed a system of wearable physiological sensors, including ECG and EEG, to capture human stress and evaluate if the detected changes in these physiological signals correlate with salivary cortisol levels, a reliable stress biomarker. A support vector machine (SVM) classification algorithm was used for statistical analysis. In [111], the authors propose a robust seizure detection method for wearable platforms, tested on the CHB-MIT Scalp EEG database, achieving a sensitivity of 0.966, specificity of 0.925, and a 34.7% reduction in false alarms. It demonstrates the system's capability to function for up to 40.87 hours on a single battery charge, showing potential for real-time use.

Zanetti et al. [112] presented a methodology based on the Random Forest classifier to implement cognitive workload monitoring (CWM) on resource-constrained wearable devices using four peripheral EEG channels. It includes a data processing strategy such

as artifact removal along with a band-pass filter, as well as feature extraction for processing data in small batches to reduce memory requirements. The challenge of balancing performance and power consumption in wearable EEG applications such as epileptic seizure detection by introducing a novel Knowledge Distillation (KD) methodology is presented in [113]. The goal is to reduce the number of EEG channels, and thus the computational and memory requirements, without compromising performance. The method involves training a high-performing model (teacher) on data from all channels and then training a simpler model (student) on a reduced set of channels using the teacher's soft labels. Risso et al. [57] uses a TCN-based solution to classify the ECG arrhythmia and a Neural Architecture Search (NAS) methodology to optimize the network parameters.

The shift toward processing biosignals on the Edge offers several promising opportunities. The research needs to address the issues such as model compression and optimization. Chapter 3 will delve into the acquisition and preprocessing of the ECG signals, as well as the application of ML, which are central to the focus of this work.

#### 2.3 Microcontrollers of Interest

The increasing demand for portable, small-sized devices has led to significant advancements in healthcare and commercial applications. Microcontroller Units (MCUs) have been pivotal in this shift, enabling compact devices with capabilities such as sensor integration and real-time data processing. However, integrating complex data analysis on embedded platforms poses challenges, requiring a balance between computational efficiency and energy consumption. This dissertation focuses on optimizing biosignal processing pipelines and machine learning (ML) techniques for deployment on MCUs. The primary microcontrollers explored include the STM32F4 and the PULP-based GAP8 and GAP9, which represent two distinct Instruction Set Architectures (ISAs): ARM for the STM32F4 and RISC-V for the GAP series.

The STM32F4 microcontroller, developed by STMicroelectronics, features an ARM Cortex-M4 core [114]. It is engineered to optimize computational performance while maintaining low power consumption, making it suitable for general-purpose computing. A detailed block diagram is provided in Figure 2.2. The MCU features both data and instruction caches, which significantly improve performance by reducing the time required to fetch instructions and load data into registers. However, this performance gain comes at the cost of increased energy consumption.

The ARM Cortex-M4 processor in this MCU supports frequencies up to 84 MHz with a power consumption of 20 mW. Additionally, the STM32F4 offers various peripherals,

Figure 2.2: Block diagram of the STM32 MCU (sub-family STM32F401xD/xE). Image source: [115].

including a Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I<sup>2</sup>C), and Analog-to-Digital Converters (ADCs) for sensor data acquisition.

Unlike the ARM ISA, the RISC-V ISA is open-source, allowing for the development of various public extensions, such as those for Digital Signal Processing (DSP). This flexibility has enabled the creation of new architectural designs based on the RISC-V ISA for general-purpose MCUs, incorporating specialized components to accelerate tasks like deep learning. Advances in this area include the integration of specialized accelerators and hierarchical memory systems that exploit data regularity.

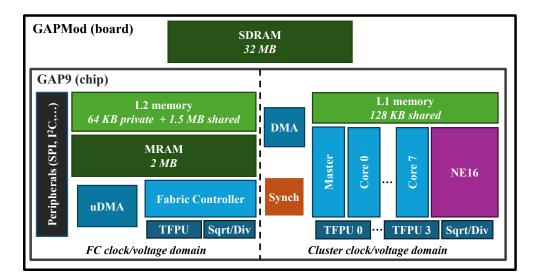

A notable example is the Parallel Ultra-Low Power (**PULP**) computing platform, which leverages near-threshold computing to achieve high energy efficiency and utilizes parallelism to mitigate performance degradation at low voltages. The PULP architecture focuses on optimizing the RISC-V ISA for DSP and Deep Neural Networks (DNNs), heterogeneous parallel acceleration where different compute units are assigned to distinct tasks, and manually controlled memory hierarchies. Key extensions to the ISA include Single Instruction Multiple Data (SIMD) Multiply-and-Accumulate (MAC) operations—central to DNN computations—as well as load/store instructions with post-increment, which streamline memory operations by automatically updating indices. Most current implementations of the PULP paradigm utilize a SoA single-core MCU, known as *fabric controller*, which includes a standard set of peripherals. It offloads computation-intensive tasks to a programmable parallel accelerator referred to as *cluster*, which contains multiple cores and operates within its own voltage and frequency domain.

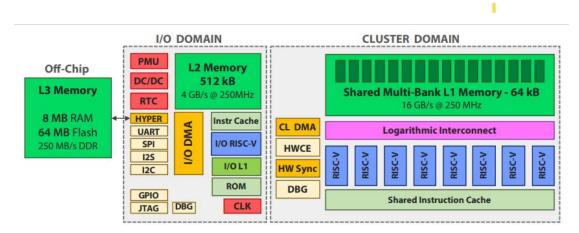

A commercial embodiment of the PULP architecture is GreenWaves Technologies' (GWT) GAP8 [116], depicted in Figure 2.3. The GAP8 features nine RISC-V cores (one I/O core and an 8-core cluster), making it one of the most advanced MCUs with dedicated optimizations for ML workloads. The GAP8 cluster comprises eight RI5CY cores with a four-stage in-order single-issue pipeline [118], utilizing the RISC-V RV32IMCXpulpV2 instruction set architecture (ISA). The XpulpV2 extension is designed specifically for domain-specific applications, optimizing DSP performance through features such as hardware loops, post-modified load/store access, and SIMD instructions supporting vector operands as small as 8 bits. All cores in the cluster share a unified first-level memory, consisting of a 64 kB multi-banked L1 Tightly-Coupled Data Memory (TCDM), which is accessible through a high-bandwidth logarithmic interconnect with single-cycle latency [118]. Data transfers between the L1 TCDM and the second-level 512 kB L2 memory are managed by a cluster DMA [34], providing bandwidth up to 2 GB/s and a latency of 80 ns at peak frequency. The L2 memory acts as a scratchpad and resides in the SoC domain. Additionally, an autonomous I/O subsystem, the I/O

Figure 2.3: Block diagram of the GWT GAP8 microcontroller. Image source: [117].