# DOTTORATO DI RICERCA IN INGEGNERIA BIOMEDICA, ELETTRICA E DEI SISTEMI

Ciclo 37

Settore Concorsuale: 09/E2 - INGEGNERIA DELL'ENERGIA ELETTRICA

$\textbf{Settore Scientifico Disciplinare:} \ IIND-08/A-CONVERTITORI, MACCHINE \ E\ AZIONAMENTI$

**ELETTRICI**

## POWER ELECTRONICS SOLUTIONS AND ARCHITECTURES FOR INDUSTRIAL AND HIGH-POWER APPLICATIONS

Presentata da: Riccardo Antonino Testa

Coordinatore Dottorato Supervisore

Prof. Michele Monaci Prof. Luca Zarri

Co-supervisori

Ing. Riccardo Morici

Ing. Gaetano Longo

## Table of Contents

| Table of  | Contents                                                  | 1  |

|-----------|-----------------------------------------------------------|----|

| Index of  | Figures                                                   | 5  |

| Index of  | Tables                                                    | 11 |

| Abstract. |                                                           | 13 |

| Preface   |                                                           | 15 |

| Chapter 1 | Energy Storage For Marine Applications                    | 19 |

| 1.1       | Introduction                                              | 19 |

| 1.1.      | Current State of Decarbonization Efforts                  | 19 |

| 1.1.2     | 2 Challenges Faced                                        | 20 |

| 1.2       | Legislative Framework                                     | 21 |

| 1.3       | The Role of Energy Storage Systems in Marine Applications | 22 |

| 1.3.      | Types of Energy Storage Technologies                      | 23 |

| 1.4       | Poseidon project                                          | 26 |

| 1.4.      | 1 Context                                                 | 26 |

| 1.4.2     | 2 Main Goals                                              | 27 |

| 1.4.3     | Fast-Response Energy Storage System (FRESS)               | 28 |

| 1.4.4     | 4 EESS Design                                             | 33 |

| 1.4.5     | Global thermal simulation model                           | 49 |

| 1.4.0     | 6 Containerized Solution                                  | 51 |

| 1.5       | Conclusions                                               | 52 |

| Chapter 2 | Optimizing Power Supplies for PF Coils                    | 55 |

| 2.1       | Introduction                                              | 55 |

| 2.2       | Role and Operation of Poloidal Field Coils in Tokamaks    | 58 |

| 2.2.      | Overview of Tokamak Magnetic Systems                      | 58 |

| 2.2.2     | Current and Voltage Profiles for PF Coils             | 60 |

|-----------|-------------------------------------------------------|----|

| 2.3 Int   | egrating Energy Storage into PF Coil Systems          | 61 |

| 2.3.1     | Benefits and Features of Supercapacitors              | 63 |

| 2.3.2     | Applying the Ragone Plot to Tokamak Energy Needs      | 65 |

| 2.4 Op    | otimization Parameters and Their Limitations          | 65 |

| 2.5 Op    | otimization Approaches and Criteria                   | 68 |

| 2.5.1     | Analytical Formulas for Optimizing PF Coils           | 69 |

| 2.5.2     | Establishing Minimum Voltage for DC Link Design       | 71 |

| 2.5.3     | Simplified Method Using Half-Voltage Cycles           | 71 |

| 2.5.4     | Scenario-Based Optimization in the Time Domain        | 72 |

| 2.5.5     | Compensating for System Losses                        | 73 |

| 2.6 Le    | veraging Complementary Power Demands of PF Coils      | 74 |

| 2.6.1     | Determining Equivalent Parameters for Shared DC Links | 76 |

| 2.7 Sir   | mulations                                             | 77 |

| 2.7.1     | Circuital Models                                      | 77 |

| 2.7.2     | Simulation Campaign                                   | 80 |

| 2.7.3     | Main Simulation Outcomes                              | 83 |

| 2.7.4     | Impact on Physical Layout and Size                    | 84 |

| 2.7.5     | Optimizing Input Power from the Grid                  | 85 |

| 2.8 Co    | nclusions                                             | 88 |

| Chapter 3 | High Voltage Pulse Generators                         | 93 |

| 3.1 Int   | roduction                                             | 93 |

| 3.1.1     | Historical Development of Pulsed Power                | 93 |

| 3.1.2     | Core Principles of Pulsed Power Systems               | 94 |

| 3.1.3     | Advancements in HVPG Technology                       | 95 |

| 3.1.4     | Applications of HVPGs                                 | 96 |

| 3.2 De    | sign of a 20 MW Peak Power Generator Prototype              | 96  |

|-----------|-------------------------------------------------------------|-----|

| 3.2.1     | Selection of the Architecture                               | 97  |

| 3.2.2     | Core components                                             | 106 |

| 3.2.3     | Signal generation                                           | 108 |

| 3.2.4     | Layout optimization                                         | 110 |

| 3.2.5     | Operation                                                   | 112 |

| 3.3 Ex    | perimental Tests                                            | 112 |

| 3.3.1     | Setup                                                       | 113 |

| 3.3.2     | Test at 5kV                                                 | 116 |

| 3.3.3     | Test at 10kV                                                | 116 |

| 3.3.4     | Test at 15kV                                                | 117 |

| 3.3.5     | Test at 20kV                                                | 117 |

| 3.3.6     | Test at 25 kV                                               | 118 |

| 3.4 An    | alysis of Test Results and Future Paths                     | 119 |

| Chapter 4 | New Theoretical Framework for Modular Multilevel Converters | 121 |

| 4.1 Int   | roduction                                                   | 121 |

| 4.1.1     | MMC Applications                                            | 121 |

| 4.1.2     | Challenges in MMC Operation                                 | 122 |

| 4.1.3     | Advancements in MMC Control Strategies                      | 123 |

| 4.1.4     | Focus of the Chapter                                        | 124 |

| 4.2 MM    | MC Topologies                                               | 124 |

| 4.3 Ma    | thematical Model of the MMC                                 | 128 |

| 4.4 De    | coupled control                                             | 132 |

| 4.4.1     | Control of the Capacitor Voltages                           | 132 |

| 4.4.2     |                                                             |     |

| 4.4.2     | Two Time-Scale Analysis                                     | 133 |

| 4.     | 4.4    | Reciprocal Functions                                              | 137      |

|--------|--------|-------------------------------------------------------------------|----------|

| 4.     | 4.5    | Differential Current and Total Energy Ripple                      | 138      |

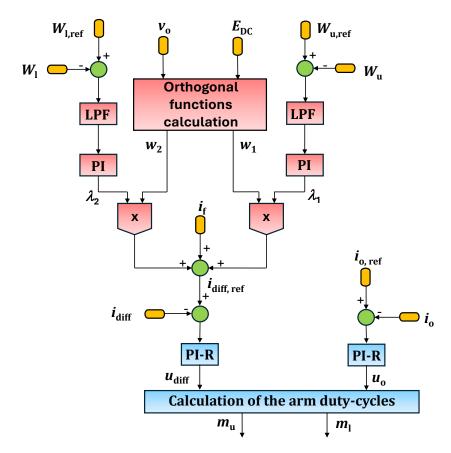

| 4.5    | Cor    | ntrol Structure                                                   | 140      |

| 4.6    | Sin    | nulations                                                         | 142      |

| 4.7    | Exp    | perimental tests                                                  | 146      |

| 4.8    | Coı    | nclusions                                                         | 151      |

| Chapte | er 5   | Modulation Strategies for Losses Minimization in Matrix Rectifier | s153     |

| 5.1    | Intr   | roduction                                                         | 153      |

| 5.2    | Mo     | odulation Techniques for Performance Optimization                 | 155      |

| 5.     | 2.1    | Mathematical Modeling of Input-Output Dynamics                    | 157      |

| 5.     | 2.2    | Space Vector Representation of Input-Output Equations             | 158      |

| 5.3    | Out    | tput Voltage Control Boundaries                                   | 161      |

| 5.4    | Spa    | ace Vector Modulation                                             | 164      |

| 5.5    | Imp    | provement in Switching Losses                                     | 168      |

| 5.     | 5.1    | General Expression of the Switching Losses                        | 168      |

| 5.     | 5.2    | Optimal Zero-Sequence Component for Minimizing Switching Lo       | sses 170 |

| 5.     | 5.3    | Graphical Representation of the Switch States                     | 172      |

| 5.     | 5.4    | Optimal Expression of the Switching Losses                        | 174      |

| 5.6    | Exp    | perimental Results                                                | 174      |

| 5.7    | Cor    | nclusions                                                         | 183      |

| Conclu | isions |                                                                   | 185      |

| Refere | nces   |                                                                   | 187      |

# Index of Figures

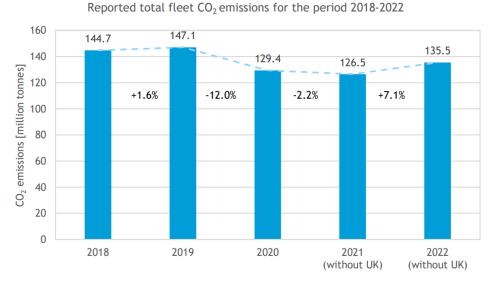

| Figure 1.1 – Reported total fleet CO2 emissions; 2018-2022 [2]            | 19       |

|---------------------------------------------------------------------------|----------|

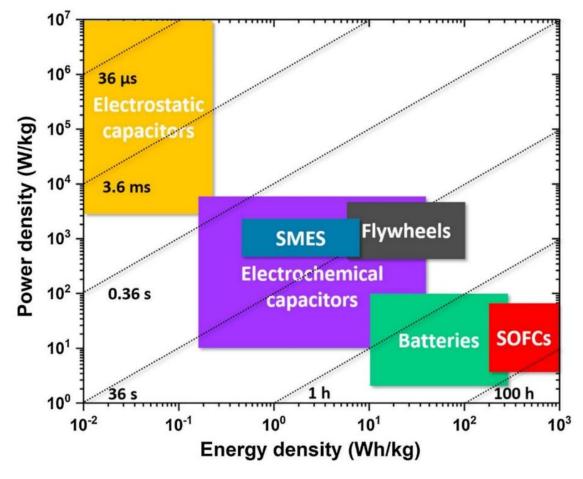

| Figure 1.2 - Ragone ESS technologies [12].                                | 23       |

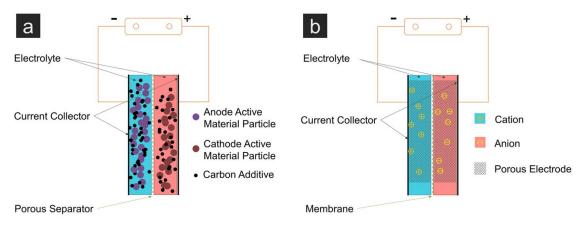

| Figure 1.3 - Li-ion battery vs Supercap [15]                              | 25       |

| Figure 1.4 - Balearia's ferry.                                            | 28       |

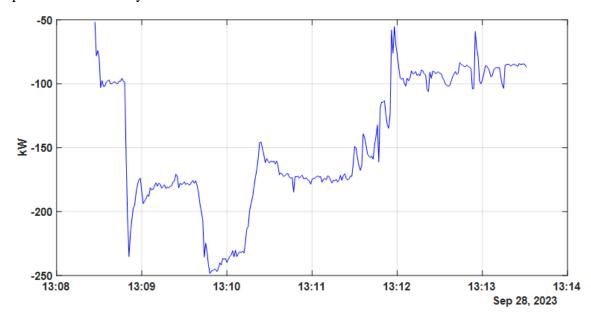

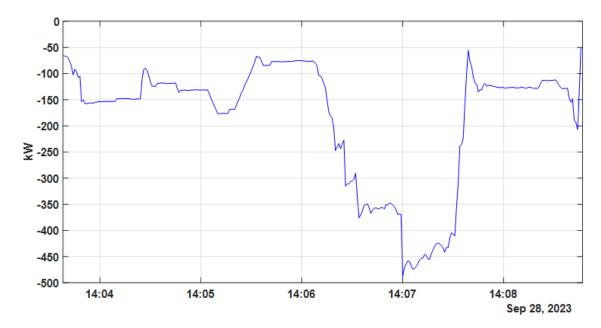

| Figure 1.5 - Power demand during port approach.                           | 29       |

| Figure 1.6 - Power demand during port departure.                          | 29       |

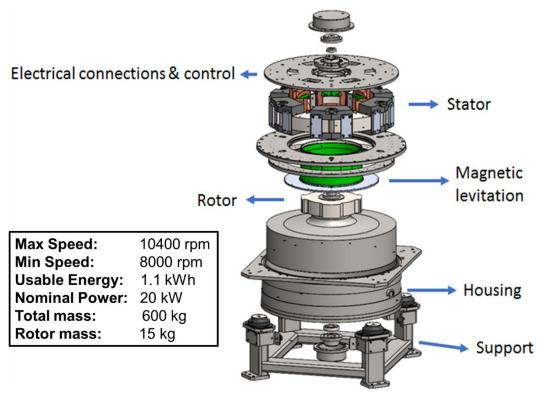

| Figure 1.7 - KESS 3D.                                                     | 31       |

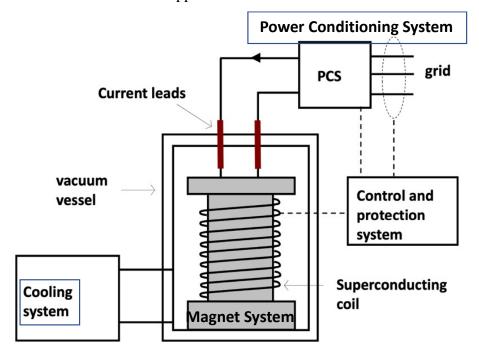

| Figure 1.8 - SMES block scheme.                                           | 32       |

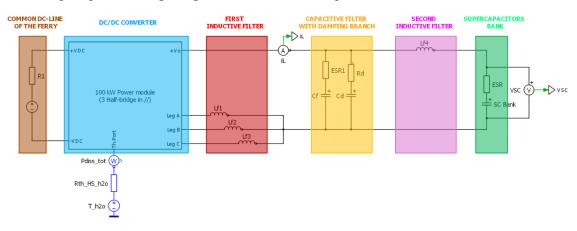

| Figure 1.9 – General scheme of the model.                                 | 33       |

| Figure 1.10 – Filter diagram.                                             | 35       |

| Figure 1.11 – Control blocks.                                             | 36       |

| Figure 1.12 – Main Outcomes.                                              | 37       |

| Figure 1.13 – Comparison between converter current and SC Bank current    | 38       |

| Figure 1.14 – Energy stored in the EESS.                                  | 38       |

| Figure 1.15 – Main data of Mitsubishi CM600DX-34T                         | 39       |

| Figure 1.16 - IGBT thermal model CM600DX-34T: a) Turn on Losses; b) T     | Γurn off |

| Losses; c) Conduction Losses                                              | 39       |

| Figure 1.17 - Diode thermal model CM600DX-34T: a) turn off losses; b) con | nduction |

| losses                                                                    | 40       |

| Figure 1.18 – Thermal network built in the simulation model.              | 40       |

| Figure 1.19 – Main outcomes from thermal simulations.                     | 41       |

| Figure 1.20 – Triumf Generation Power Module (TGPS).                      | 42       |

| Figure 1.21 – CapTop CTM 00165C0 0054V0 NN00 Power Brick                  | 43       |

| Figure 1.22 - Ducati DCH 85C series.                                      | 43       |

| Figure 1.23 – Control architecture based on CompactRIO                    | 45       |

| Figure 1.24 – CAD 3D model of the EESS for Poseidon.                      | 48       |

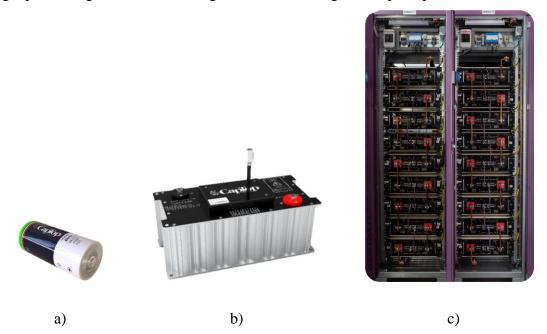

| Figure 1.25 - EESS a) Cell b) Module c) Cabinet.                          | 49       |

| Figure 1.26 – Thermal model of the FRESS                                  | 50       |

| Figure 1.27 - Arrangement of the various ESS inside the container         | 52       |

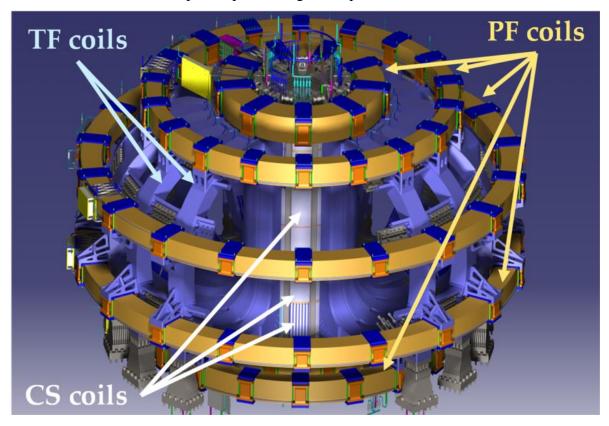

| Figure 2.1 - Basic structure of a tokamak (DTT) emphasizing the magnetic systems59                |

|---------------------------------------------------------------------------------------------------|

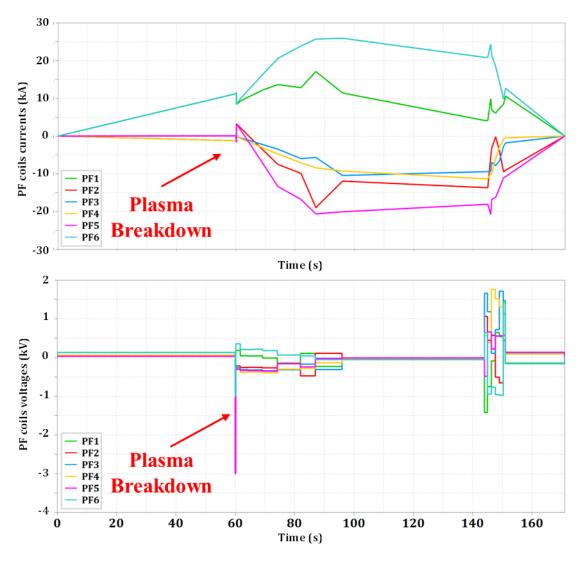

| Figure 2.2 - Currents and voltages of PF coils in the DTT reference scenario, detailing           |

| transient phenomena and stages such as plasma breakdown, plasma ramp-up, the L-H mode             |

| transition, and the H-L mode transition60                                                         |

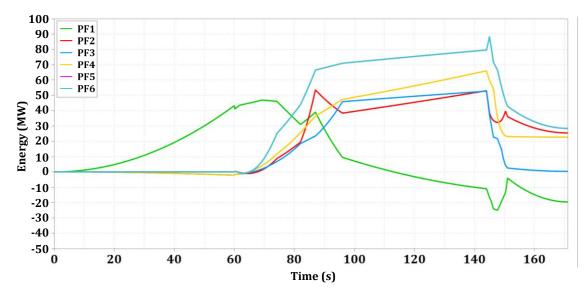

| Figure 2.3 - Powers delivered to the PF coils in the DTT reference scenario62                     |

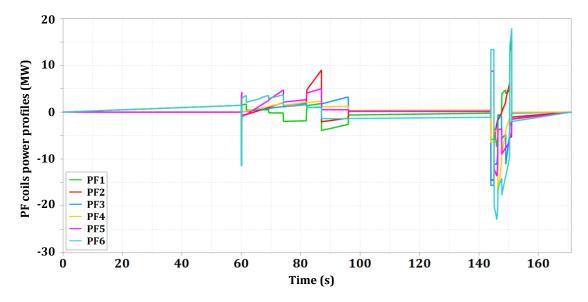

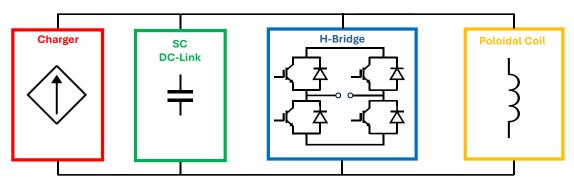

| Figure 2.4 - Ragone plot comparing the main energy storage technologies and some                  |

| typical durations of their operations. To support the analysis of this study, some characteristic |

| times of the DTT PF power supply system are also reported for discussion64                        |

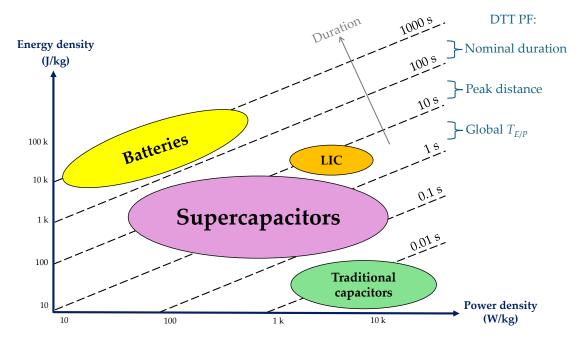

| Figure 2.5 - General topology of the PF coil PS used for the design and optimization66            |

| Figure 2.6 - Energies delivered to the PF coils in the DTT reference scenario69                   |

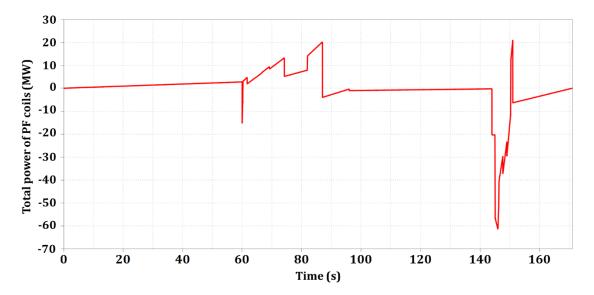

| Figure 2.7 - Sum of the instantaneous powers of the six PF coils shown in Figure 2.374            |

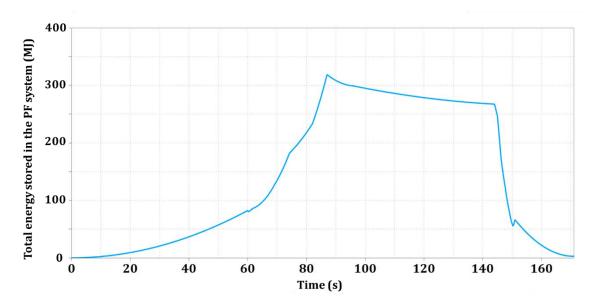

| Figure 2.8 - Total energy stored in the load coils, including equivalent mutual couplings.        |

| 75                                                                                                |

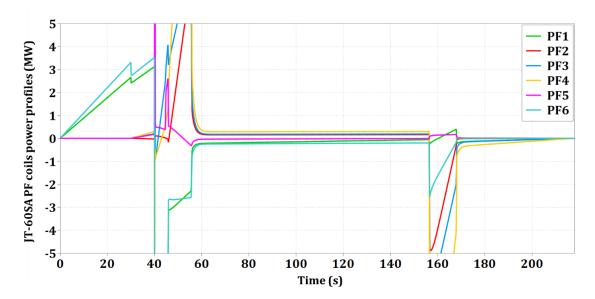

| Figure 2.9 - Example of complementarity in the powers delivered to the PF coils in the            |

| JT-60SA reference scenario [48] (coil names adjusted to match those of the DTT)76                 |

| Figure 2.10 - Block diagram of the control algorithm used to emulate the mutual coupling          |

| effect79                                                                                          |

| Figure 2.11 - Logic diagram of the controlled current source representing the charger in          |

| circuit simulations80                                                                             |

| Figure 2.12 - Block diagram of the H-bridge control algorithm80                                   |

| Figure 2.13 - Basic circuit configuration for a shared DC link (using the PF1 and PF2 pair        |

| as an example)81                                                                                  |

| Figure 2.14 - Comparison between the scenarios where the PF1 and PF2 power supplies               |

| share the DC storage and where the same DC storage feeds only the PF2 power supply83              |

| Figure 2.15 - CapTop CTM 00165C0 0054V0 NN00 supercapacitor module, rated at 54 V                 |

| and 165 F85                                                                                       |

| Figure 2.16 - Instantaneous power drawn from the grid by the PF1 & PF2 pair87                     |

| Figure 3.1 – Marx generator built in 1961, currently at the High Voltage laboratory of the        |

| Technische Universität Darmstadt [51]94                                                           |

| Figure 3.2 – Block scheme of generic pulsed power generating system95                             |

| Figure 3.3 – Pulse waveform                                                                       |

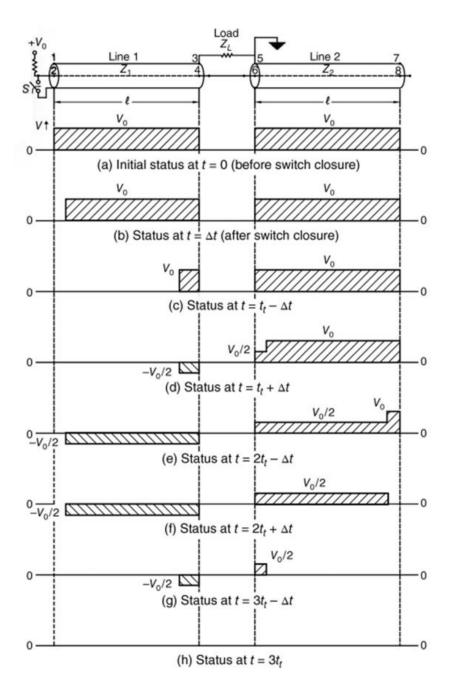

| Figure 3.4 – General scheme of Marx generator                                                     |

| Figure 3.5 – Voltage wave dynamics across a Blumlein transmission line with matched      |

|------------------------------------------------------------------------------------------|

| impedance [49]                                                                           |

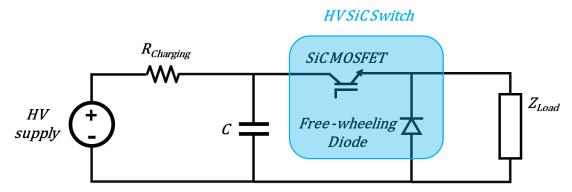

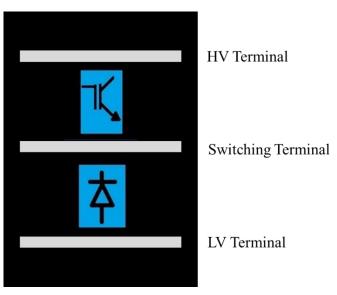

| Figure 3.6 - Conceptual scheme of the single stage architecture with HV SiC Switch.104   |

| Figure 3.7 – Example of HV Switch during the manufacturing                               |

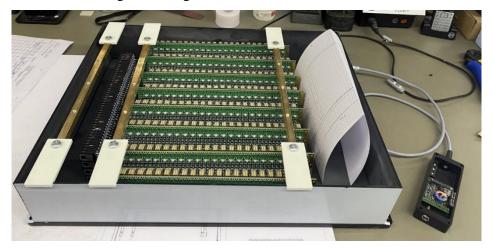

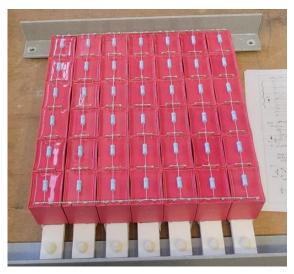

| Figure 3.8 - Storage Bank made of 42 capacitors each with a paralleled resistor 106      |

| Figure 3.9 – HV SiC switch with its separated control unit                               |

| Figure 3.10 - Conceptual diagram of the HV SiC Switch                                    |

| Figure 3.11 - Spellman SL70P1200/FG/ESL/230                                              |

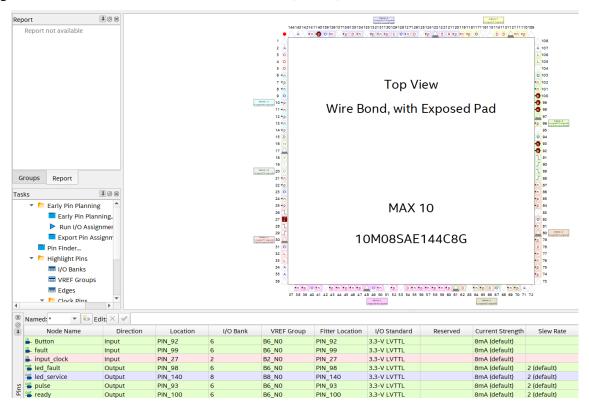

| Figure 3.12 – FPGA board Intel MAX 10                                                    |

| Figure 3.13 – Quartus screenshot                                                         |

| Figure 3.14 - Control architecture: on the left the crate encompassing a 24V supply, the |

| FPGA board and the internal buffer board; on the right the external buffer board109      |

| Figure 3.15 – HV Switch with DC storage frame                                            |

| Figure 3.16 – HV SiC Switch with snubber and Distributed load at its terminals 111       |

| Figure 3.17 – Aluminum mass plane.                                                       |

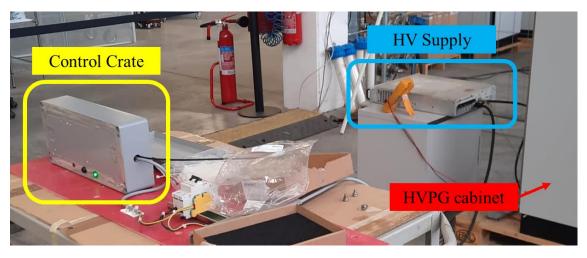

| Figure 3.18 – Test setup.                                                                |

| Figure 3.19 – HVPG cabinet                                                               |

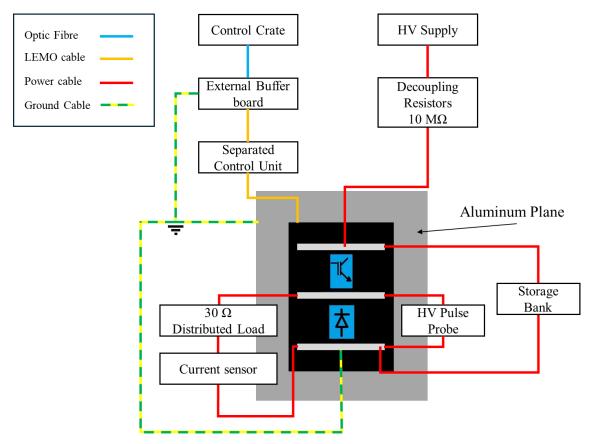

| Figure 3.20 – Block scheme of testing layout                                             |

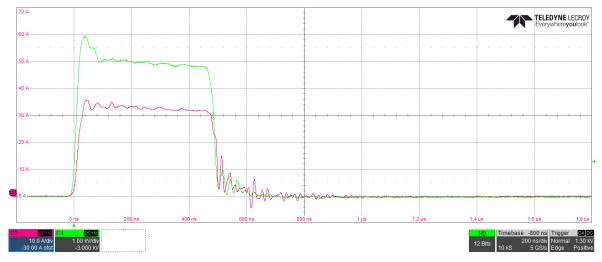

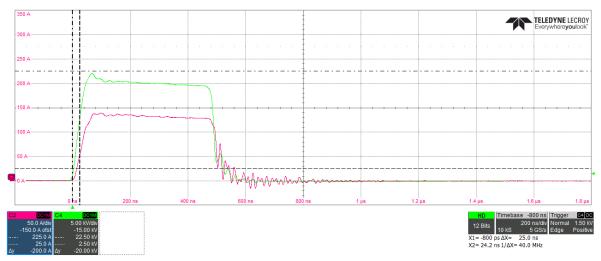

| Figure 3.21 – 5kV pulse voltage (green) and current (red). 200 ns/div116                 |

| Figure 3.22 – 10kV pulse voltage (green) and current (red). 200 ns/div116                |

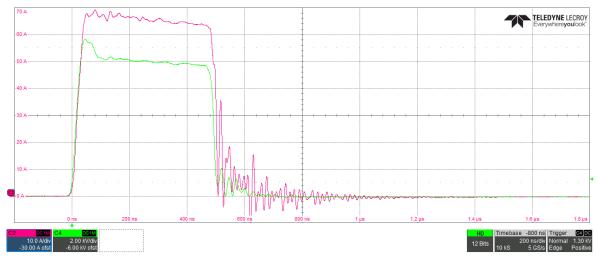

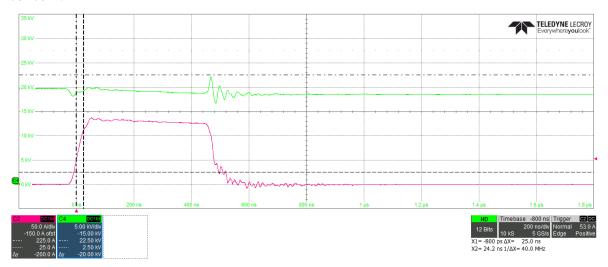

| Figure 3.23 – 15kV pulse voltage (green) and current (red). 200 ns/div117                |

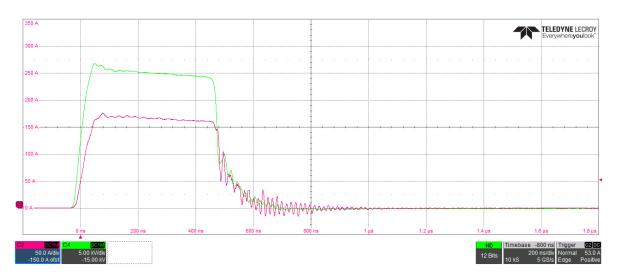

| Figure 3.24 – 20kV pulse voltage (green) and current (red). 200 ns/div117                |

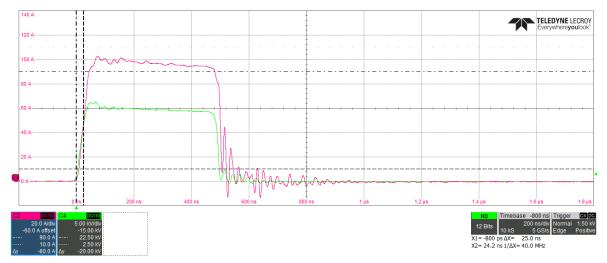

| Figure 3.25 - 20kV pulse switch opening voltage (green) and current (red). 200 ns/div.   |

| 118                                                                                      |

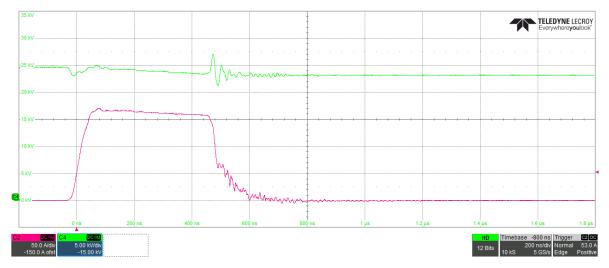

| Figure 3.26 – 25kV pulse voltage (green) and current (red). 200 ns/div119                |

| Figure 3.27 - 25kV pulse switch opening voltage (green) and current (red). 200 ns/div    |

| 119                                                                                      |

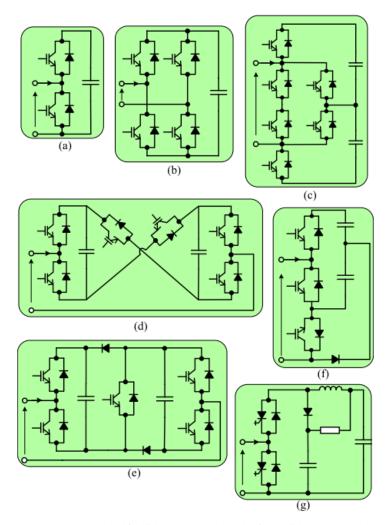

| Figure 4.1 - MMC submodules: (a) half-bridge submodule, (b) full-bridge submodule, (c)   |

| modified ANPC submodule, (d) cross-connected submodule (CCSM), (e) clamped double        |

| submodule (CDSM), (f) single-clamped submodule (SCSM), and (g) IGCT submodule [88].      |

|                                                                                          |

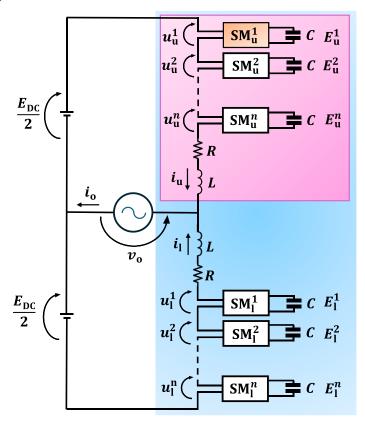

| Figure 4.2 – Basic topology of one phase MMC                                             |

|                                                                                          |

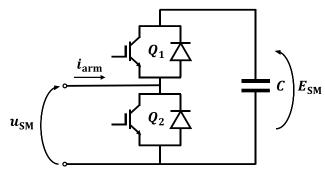

| Figure 4.3 - Sub-module topology with a half bridge connected in parallel to a capacitor.                          |

|--------------------------------------------------------------------------------------------------------------------|

|                                                                                                                    |

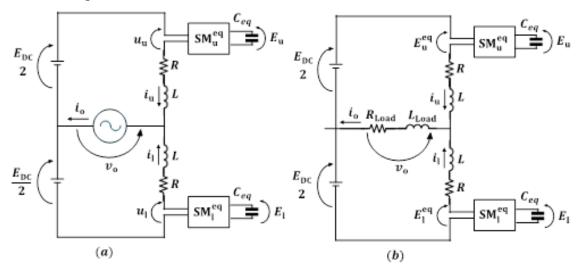

| Figure 4.4 - Simplified scheme of an MMC. (a) The converter is connected to a sinusoidal                           |

| voltage source. (b) The converter is connected to a passive load                                                   |

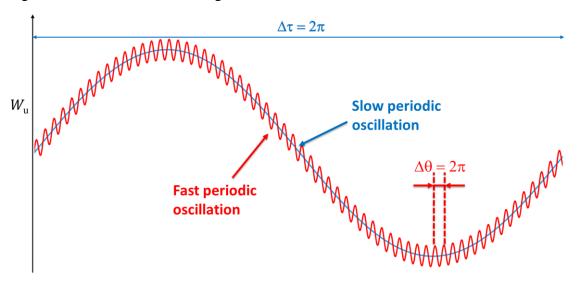

| Figure 4.5 - Fast and slow time scales                                                                             |

| Figure 4.6 - MMC control block diagram                                                                             |

| Figure 4.7 - Reduction of the total energy ripple in response to the injection of the                              |

| component if                                                                                                       |

| Figure 4.8 – Response of arms currents and voltages to the injection of the component if.                          |

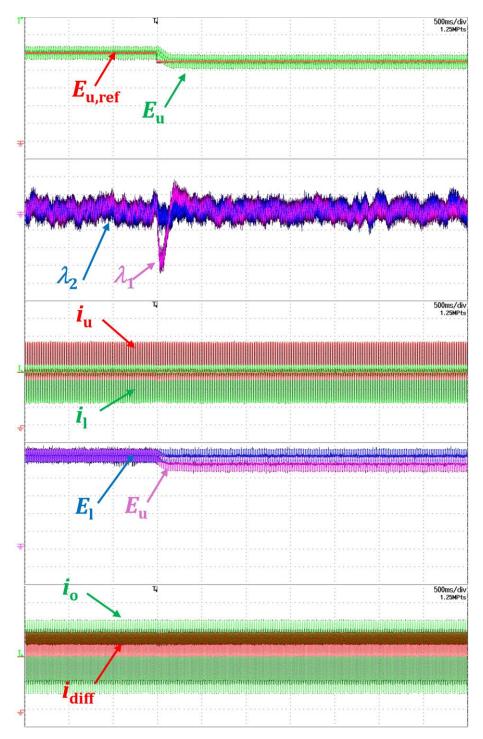

| Figure 4.9 – Response of the converter to a step decrease in the setpoint Eu, ref by                               |

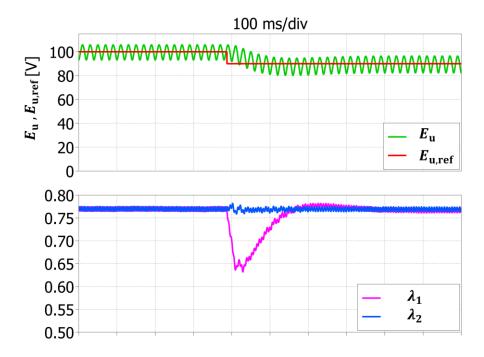

| 10%. Waveforms of Eu, ref, Eu, ref (upper traces) and $\lambda 1$ , $\lambda 2$ (lower traces)144                  |

| Figure 4.10 – Waveforms of io, idiff (upper traces) and vo (lower trace) at a steady state.                        |

| Figure 4.11 - MMC prototype, encompassing six SMs, used for experimental tests146                                  |

| Figure 4.12 – Individual SM board146                                                                               |

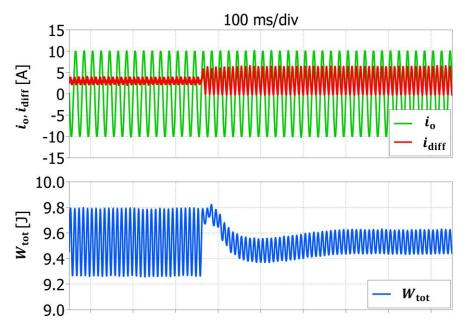

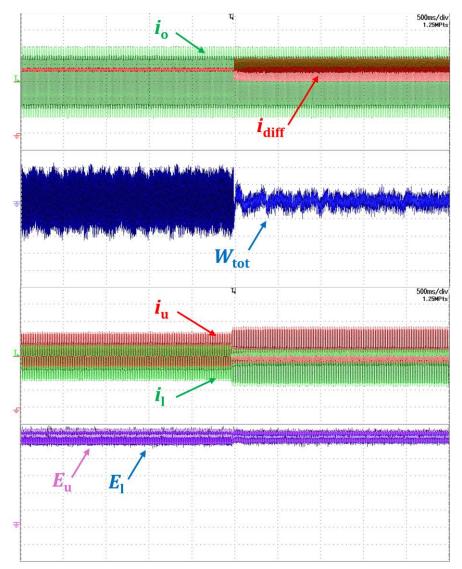

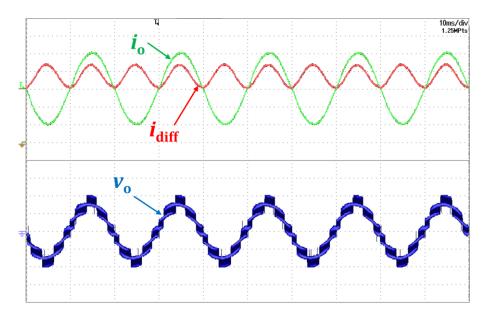

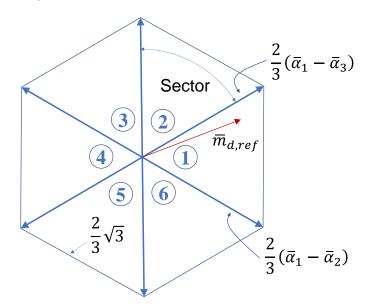

| Figure 4.13 - System response to if injection. From top to bottom: output current io(in                            |

| green, 5 A/div); differential current idiff (in red, 5 A/div); total energy Wtot (in blue, 200                     |

| mJ/div, AC coupling); upper arm current iu (in red, 5 A/div); lower arm current il (in green,                      |

| 5 A/div); upper arm voltage Eu (in purple, 20 V/div); lower arm voltage El (in blue, 20 V/div).                    |

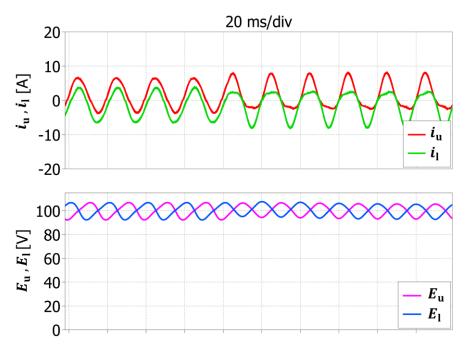

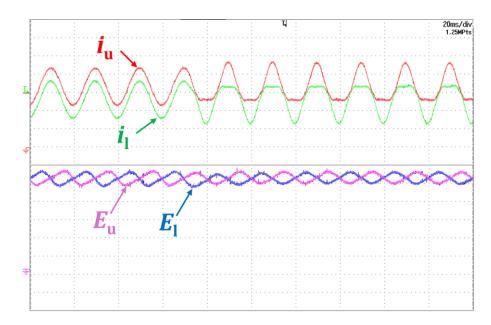

| Figure 4.14 - Detail of system response to if injection, from top to bottom: upper arm                             |

| current iu (in red, 5 A/div); lower arm current il (in green, 5 A/div); upper arm voltage Eu                       |

| (in purple, 20 V/div); lower arm voltage El (in blue, 20 V/div)148                                                 |

| Figure 4.15 - Response of the system to a step variation in Eu, ref, from top to bottom:                           |

| upper arm voltage reference Eu, ref (in red, 20 V/div); upper arm voltage Eu (in purple, 20                        |

| $V/div$ ); $\lambda 1$ (in purple, 0,05/div, AC coupling); $\lambda 2$ (in blue, 0,05/div, AC coupling); upper arm |

| current iu (in red, 5 A/div); lower arm current il (in green, 5 A/div); upper arm voltage Eu                       |

| (in purple, 20 V/div); lower arm voltage El (in blue, 20 V/div); output current io (in green, 5                    |

| A/div); differential current idiff (in red, 5 A/div)                                                               |

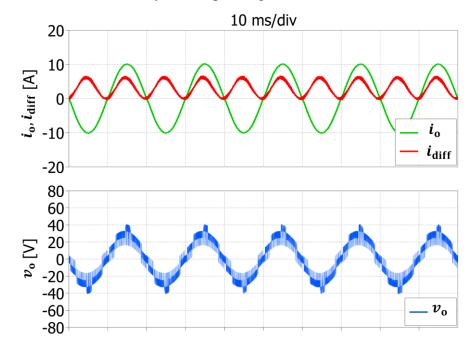

| Figure 4.16 - Steady-state condition, from top to bottom: output current io (in green, 5                           |

| A/div); differential current idiff (in red, 5 A/div); output voltage vo (in blue, 20 V/div)150                     |

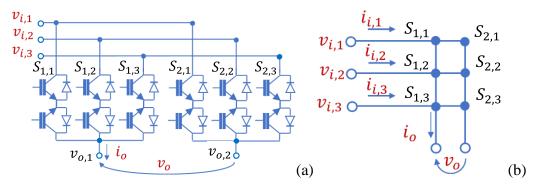

| Figure 5.1 - Basic layout of a three-phase AC-DC matrix converter. (a) Converter                                   |

|--------------------------------------------------------------------------------------------------------------------|

| architecture. (b) Matrix representation in simplified form                                                         |

| Figure 5.2 - Admissible instantaneous values of md and repartition of the plane into six                           |

| sectors                                                                                                            |

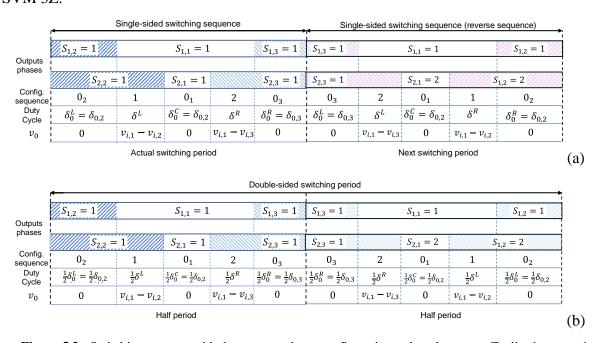

| Figure 5.3 - Switching patterns with three zero-voltage configurations when the vector md                          |

| lies in sector 1. Single-sided (a) or double-sided (b)                                                             |

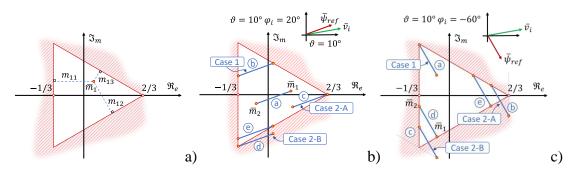

| Figure 5.4 - Geometrical representation of m1 and m2. a) Graphical meaning of m1. b)                               |

| Typical positions of the segment connecting m1 and m2 with an input power factor greater                           |

| than 0.866 c) Typical positions of the segment connecting m1 and m2 with an input power                            |

| factor lower than 0.866.                                                                                           |

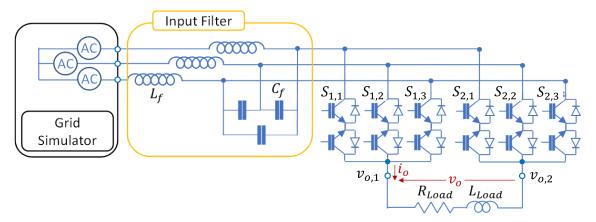

| Figure 5.5 - Basic diagram of the AC-DC conversion system                                                          |

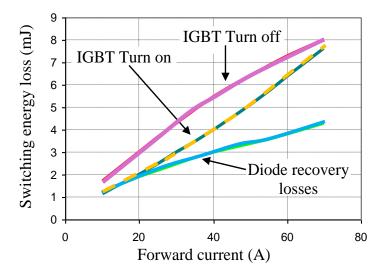

| Figure 5.6 - Switching losses of the converter's IGBTs and diodes at a test voltage of 600                         |

| V and a junction temperature of 25°C.                                                                              |

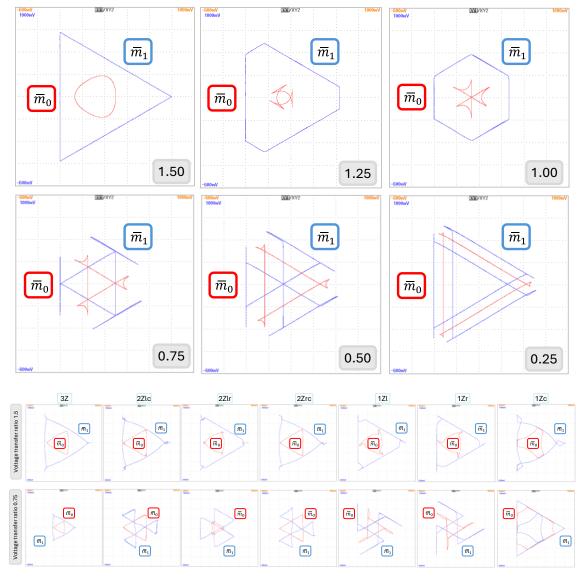

| Figure 5.7 - Trajectories in the complex plane of m1 and m0 for Case 1 (a) and for                                 |

| conventional SVM strategies (b)                                                                                    |

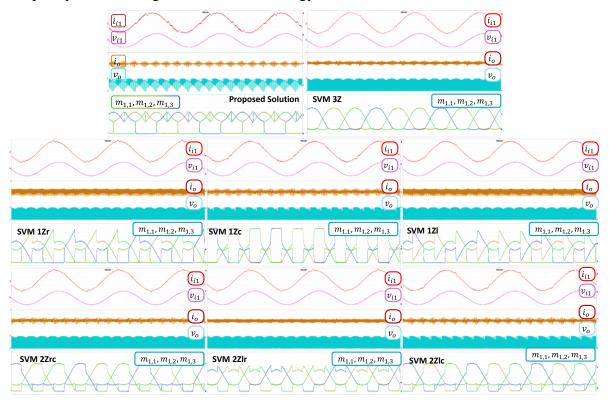

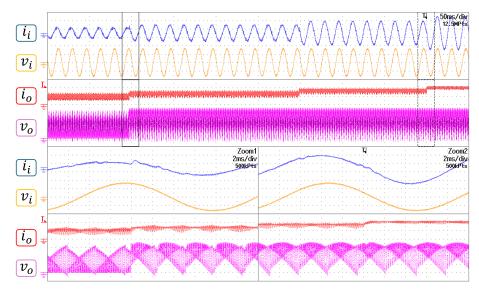

| Figure 5.8 - Experimental performance of the AC-DC matrix converter with various                                   |

| modulation strategies at an input power factor of 1 and a voltage transfer ratio of 0.9. Input                     |

| current $i_{i1}$ (5 A/div), input voltage $v_{i1}$ (100 V/div), load current $i_0$ (2 A/div), output voltage $v_0$ |

| (50 V/div), modulating signals $m_{1,1}$ , $m_{1,2}$ , $m_{1,3}$ (0.2/div). Time scale: 5 ms/div                   |

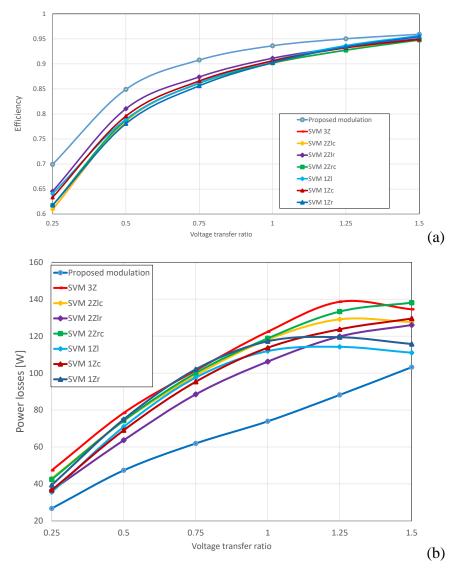

| Figure 5.9 - Performance of the AC-DC matrix converter under eight different modulation                            |

| strategies with an input power factor of 1. (a) Efficiency. (b) Power losses179                                    |

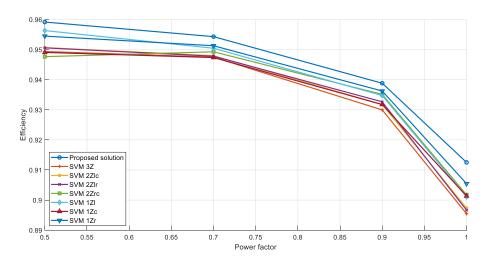

| Figure 5.10 - Efficiency of the AC-DC matrix converter for eight different modulation                              |

| strategies at the maximum voltage transfer ratio (1.5)                                                             |

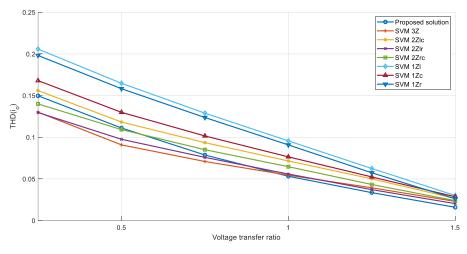

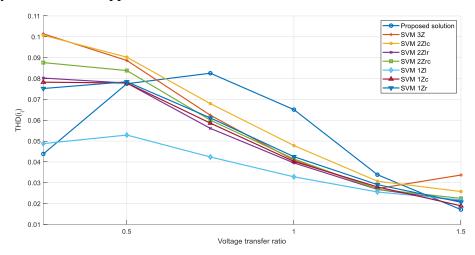

| Figure 5.11 - Measured THD of the output current as a function of the voltage transfer                             |

| ratio when the input power factor is 1                                                                             |

| Figure 5.12 - Measured THD of the input current as a function of the voltage transfer ratio                        |

| when the input power factor is 1                                                                                   |

| Figure 5.13 - Transient response of the converter during three step changes in the voltage                         |

| transfer ratio (0.75, 1, 1.25, 1.5). From top to bottom: input current (5 A/div), input voltage                    |

| (100 V/div), output current (5 A/div), output voltage (80 V/div)                                                   |

## Index of Tables

| Table 2.1 - Self-inductance and energy values for DTT PF coils70                           |

|--------------------------------------------------------------------------------------------|

| Table 2.2 - SC bank design results from time-domain optimization73                         |

| Table 2.3 - Summary of differences in voltage, capacitance, and energy of SC banks for     |

| independent and shared DC-links under various grid power limits                            |

| Table 2.4 - Achieved efficiencies for PF pairs, assessed using the two different proposed  |

| definitions86                                                                              |

| Table 2.5 - Comparison of SC bank sizes, expressed as the number of reference cabinets     |

| and configurations, for shared and independent dc storage under various grid power limits. |

|                                                                                            |

| Table 3.1 – Main pulse parameters                                                          |

| Table 4.1 – Main simulation parameters                                                     |

| Table 5.1 - Configurations of the AC-DC Matrix Converter                                   |

| Table 5.2 - Sequence of Vectors for SVM (with reverse order possible)167                   |

| Table 5.3 - Modulation Strategies Based on Zero Configurations                             |

| Table 5.4 - Values of the Zero-Sequence Components                                         |

| Table 5.5 - Coefficients for Case 1, 2-A and 2-B.                                          |

| Table 5.6 - Experimental Parameters                                                        |

### **Abstract**

This PhD thesis is part of a high-level apprenticeship (Dottorato in Apprendistato di Alta Formazione e Ricerca) conducted in collaboration between OCEM Power Electronics and the University of Bologna. The research focuses on the development of power electronics solutions and architectures for industrial and high-power applications, addressing the growing need for more efficient, scalable, and flexible systems in these sectors. The thesis combines both practical industrial applications and theoretical advancements, demonstrating the importance of power electronics in managing complex, high-demand energy environments.

The thesis is structured into five chapters, with the first three detailing the work carried out at OCEM Power Electronics and the last two chapters covering research conducted at the University of Bologna.

In the first chapter it is introduced the Poseidon Project, an EU-funded initiative that addresses energy storage for marine environments through the development of a Fast-Response Energy Storage System. This system integrates advanced technologies to provide reliable, efficient power delivery while significantly reducing fuel consumption and emissions in maritime operations. This chapter highlights how hybrid energy storage solutions can meet dynamic power demands while contributing to sustainable maritime practices.

The second chapter presents a collaborative study on Poloidal Field (PF) coils conducted with ENEA Frascati, which focuses on optimizing the power supply systems for poloidal field coils used in tokamak fusion reactors. Supercapacitors were used to enhance the rapid energy release needed for plasma stabilization, reducing the system's physical and energy footprint. The results demonstrate how power electronics can provide responsive and efficient solutions for the high-power demands of fusion reactors.

The third chapter deals with the design and testing of a high-voltage pulse generator prototype. While the prototype achieved the required technical specifications, delivering 25 kV pulses with fast rise times, further refinements are suggested to enhance the reliability and performance of the system.

The second part of the thesis focuses on theoretical advancements in power electronics, with research conducted at the University of Bologna. Chapter four explores Modular Multilevel Converters, which are increasingly used in many different fields due to their modularity and scalability. The research introduces novel theoretical framework based on two-time scale analysis, improving the performance of the converter.

Chapter five investigates matrix rectifiers as an alternative to conventional rectifiers, providing direct AC-to-DC conversion with greater efficiency due to a tailored control strategy for losses reduction. This work highlights the potential of matrix rectifiers in industrial applications.

## Preface

The field of power electronics has become a cornerstone of modern technology, playing a pivotal role in a wide range of applications that demand efficient, reliable, and scalable solutions for energy conversion and management. As industries continue to evolve and the demand for electrical power grows, power electronics solutions are increasingly required to handle not only high power levels but also the complex operational dynamics of large-scale systems. The need for effective power electronics architectures is particularly acute in industrial and high-power applications, where operational efficiency, system flexibility, and sustainability are critical to maintaining competitiveness and meeting environmental regulations.

Power electronics involves the conversion and control of electrical energy using semiconductor devices to manage power flow between sources and loads. Its applications are diverse, ranging from energy distribution in industrial settings to renewable energy integration, transportation, and scientific research. The ability to precisely manage power at various levels, whether converting AC to DC, managing voltage levels, or improving energy efficiency, makes power electronics essential to the performance and reliability of modern energy systems.

In industrial and high-power applications, the challenges are amplified. Systems often operate at very high power levels, requiring robust and scalable solutions that can withstand demanding operational conditions. These applications include large manufacturing plants, electrical grids, transportation systems, and specialized research facilities that rely on advanced power conversion systems. The focus in these environments is on delivering consistent, reliable performance while minimizing energy losses, improving overall system efficiency, and reducing environmental impact.

As the demand for energy continues to grow, there is also an increasing emphasis on sustainable energy solutions. This has led to the exploration of new energy storage technologies, renewable energy integration, and the development of more efficient power conversion systems that can support the shift towards cleaner energy. In high-power applications, such as those found in industrial environments or large-scale infrastructure, the role of power electronics is not only to improve efficiency but also to ensure that systems can

adapt to changing operational conditions, manage peak power demands, and integrate with renewable energy sources.

In this context, power electronics architectures are developed to optimize the interaction between energy sources, conversion systems, and storage technologies. These architectures must be flexible enough to support a wide range of operating conditions, from steady-state energy conversion to handling transient peaks in power demand. Additionally, they must be scalable, allowing for expansion as systems grow or as energy demands increase. The development of innovative architectures that integrate new energy storage systems and efficient converter designs is crucial to meeting these challenges.

This PhD thesis, titled "Power Electronics Solutions and Architectures for Industrial and High Power Applications", investigates these challenges. It is the culmination of a high-level apprenticeship (Dottorato in Apprendistato di Alta Formazione e Ricerca) conducted in collaboration between OCEM Power Electronics (a division of Energy Technology S.r.l.) and the Alma Mater Studiorum University of Bologna. This thesis explores these challenges and presents solutions aimed at addressing the increasing complexity of power systems in industrial and high-power environments.

This work is divided into two primary sections, focusing first more on the practical applications of power electronics within OCEM Power Electronics, while dealing more later with theoretical aspects and control strategies developed at the Department of Electrical, Electronic, and Information Engineering (DEI) at the University of Bologna. Each section presents distinct but interconnected contributions to the overall theme of optimizing power electronics solutions for high-demand environments.

At OCEM Power Electronics, the focus was on developing solutions that could meet the immediate challenges of industrial applications. One of the major projects undertaken during this research was the Poseidon project, a project that is part of the Horizon EU research & innovation framework programme, which aimed to create a Fast-Response Energy Storage System for marine applications. In marine environments, power demands can fluctuate rapidly, particularly during critical operations such as port maneuvers or dynamic positioning. The Poseidon Project addressed these challenges by integrating three advanced energy storage technologies: Kinetic Energy Storage Systems, Superconducting Magnetic Energy Storage, and Electrostatic Energy Storage Systems. These systems, when combined, provide the ability to deliver high bursts of power instantly, while also storing energy

efficiently for extended periods. The research demonstrated how these integrated systems could significantly reduce fuel consumption and emissions in maritime operations, aligning with global efforts toward decarbonization.

Another key area of research conducted at OCEM was the collaborative study with ENEA Frascati, which focused on the power supply systems for poloidal field coils used in tokamak fusion reactors. PF coils are responsible for shaping and stabilizing the plasma within the reactor, and their power systems must be highly responsive to the dynamic power requirements of the fusion process. This study explored the use of supercapacitors to optimize energy storage for these systems, providing rapid power delivery while reducing the physical footprint of the energy storage units. The ability to manage power peaks and reduce strain on the external power grid was a central challenge addressed in this work.

A further project focused on the development of a high-voltage pulse generator for industrial applications. High-voltage pulse generators are widely used in research facilities for processes like particle acceleration, which require precise and powerful pulses. The pulse generator designed in this project was a compact, high-performance prototype capable of delivering 25 kV pulses with a fast rise time, addressing the need for efficient and reliable pulse generation in space-constrained environments. The research highlighted the importance of optimizing the generator's design to minimize parasitic inductance and ensure reliable performance under high-voltage conditions.

The second part of the thesis transitions to the theoretical work conducted at the University of Bologna. Here, the focus shifted toward the development of advanced power conversion systems that could meet the future demands of high-power applications. One of the key areas of research was on Modular Multilevel Converters, a technology that has gained prominence for its use in high-voltage direct current transmission systems. MMCs offer distinct advantages in terms of scalability and efficiency, making them ideal for large-scale energy transmission. The research in this area introduced new control strategies, particularly through the development of two-time scale analysis methods, which enhance the performance of MMCs in dynamic environments. These strategies allow the converters to handle varying loads more effectively, maintaining stability and efficiency even under rapidly changing conditions.

Finally, the thesis examines the potential of matrix rectifiers as an alternative to conventional rectifiers. Matrix rectifiers provide direct AC-to-DC conversion, offering

higher efficiency than traditional systems. The research explored the theoretical foundations of matrix rectifiers, as well as their practical applications in industrial settings, demonstrating their ability to improve power quality and reliability in high-power environments.

### Chapter 1

### **ENERGY STORAGE FOR MARINE APPLICATIONS**

#### 1.1 Introduction

The maritime industry is the backbone of global trade, responsible for transporting around 90% of the world's goods. However, this sector also contributes significantly to greenhouse gas (GHG) emissions, accounting for nearly 2.5% of global CO<sub>2</sub> emissions [1]. As the urgency to address climate change grows, decarbonizing maritime transport has become a priority for policymakers, industry leaders, and researchers.

#### 1.1.1 Current State of Decarbonization Efforts

CO2 emissions remain significantly high, highlighting the urgent need for effective reduction strategies. Despite fluctuations in recent years due to events like the COVID-19 pandemic and changes in EU regulations. Looking at Figure 1.1 the rebound visible in 2022 shows that emissions are far from being under control. Proactive measures are essential to achieve meaningful and sustained reductions. Efforts to decarbonize maritime transport include exploring alternative fuels, enhancing energy efficiency, integrating renewable energy, and advancing digital technologies to optimize operations.

Figure 1.1 – Reported total EU fleet CO2 emissions; 2018-2022 [2].

A key strategy is the transition from heavy fuel oil to low or zero-carbon fuels. Alternatives like Liquefied Natural Gas (LNG), biofuels, hydrogen, ammonia, and methanol are considered, but each comes with its own challenges, such as availability, energy density, storage needs, and the requirement for new infrastructure. For instance, while LNG reduces some emissions, it is still a fossil fuel and may not meet long-term decarbonization targets [3].

Improving energy efficiency is another important step toward reducing emissions. New ship designs, including advanced hull forms and propulsion systems, help lower fuel consumption. Technologies like air lubrication systems reduce friction between the hull and water, and waste heat recovery systems capture excess energy for additional power [4]. The IMO's Energy Efficiency Design Index (EEDI) sets mandatory standards for new ships, pushing for more sustainable designs.

Renewable energy also plays a role. Wind-assisted propulsion technologies, such as rotor sails and kites, harness wind power to reduce fuel usage, while solar panels provide energy for onboard electrical systems. These technologies, though supplementary, contribute to lowering emissions [5].

Digitalization enhances operational efficiency through data analytics, real-time monitoring, and artificial intelligence. Efficient route planning and speed optimization allow ships to minimize fuel consumption by arriving at ports "just in time", cutting emissions without affecting delivery schedules [6].

Regulatory and market-based measures, like carbon pricing mechanisms and emissions trading systems, are also pushing the industry toward greener technologies. These approaches internalize the environmental costs of emissions, encouraging investment in low-carbon solutions [7].

#### 1.1.2 Challenges Faced

Despite progress, significant challenges remain in decarbonizing the maritime industry. Economic viability is a major concern, as the costs of developing and deploying new technologies and fuels are often high. Without adequate financial incentives or regulations, shipowners may hesitate to invest in unproven or expensive solutions.

Infrastructure limitations also pose a challenge. The global infrastructure for alternative fuels is underdeveloped, requiring significant investments in bunkering facilities and supply chains. Building this infrastructure demands international coordination and cooperation.

Many low or zero-carbon technologies are still in the early stages of development. Scaling these solutions to meet the demands of global shipping presents technical challenges, including ensuring safety, reliability, and compatibility with existing systems.

The regulatory complexity of international shipping makes enforcing uniform standards difficult. Harmonizing policies across nations and ensuring compliance require international collaboration, which is often challenging due to differing national priorities and interests [8]-[9].

#### 1.2 Legislative Framework

Energy storage systems on ferries to reduce GHG emissions are governed by a complex legislative framework that includes international, regional, and national regulations. Central to this framework is the International Maritime Organization (IMO), a United Nations agency responsible for regulating shipping. The IMO has developed several conventions and regulations to minimize the environmental impact of maritime transport.

One key instrument is the International Convention for the Prevention of Pollution from Ships (MARPOL), particularly Annex VI, which addresses air pollution from ships. Annex VI sets limits on nitrogen oxides (NO<sub>x</sub>) and sulfur oxides (SO<sub>x</sub>) emissions and introduces the Energy Efficiency Design Index (EEDI) and the Ship Energy Efficiency Management Plan (SEEMP) [10]. The EEDI sets energy efficiency standards for new ships, and the SEEMP requires all ships to have plans for improving energy efficiency. These regulations encourage the adoption of energy storage systems, as they promote technologies that enhance efficiency and reduce emissions.

The IMO's 2018 Initial Strategy on reducing GHG emissions aims to cut CO<sub>2</sub> emissions per transport work by at least 40% by 2030 and to pursue efforts toward a 70% reduction by 2050, compared to 2008 levels. Additionally, it aims to reduce total annual GHG emissions by at least 50% by 2050, while ultimately phasing them out entirely. This strategy highlights the importance of innovative solutions, such as energy storage systems, to help meet these goals.

At the regional level, the European Union has taken further steps through the EU MRV (Monitoring, Reporting, Verification) Regulation, which requires ships over 5,000 gross tons visiting EU ports to monitor and report CO<sub>2</sub> emissions. The EU is also incorporating maritime shipping into its Emissions Trading System (ETS), incentivizing GHG reductions and promoting clean technologies [11].

National regulations can also impact energy storage systems on ferries. Coastal states can implement stricter environmental regulations within their territorial waters and Exclusive Economic Zones (EEZs). Some nations offer incentives for green technologies, including energy storage, or impose stricter emission limits in designated Emission Control Areas (ECAs).

Safety regulations are another crucial aspect of the legislative framework. The International Convention for the Safety of Life at Sea (SOLAS) sets minimum safety standards for ships, and energy storage systems must comply with SOLAS requirements, as well as guidelines from the International Electrotechnical Commission (IEC) and classification societies, to ensure that they do not compromise vessel safety.

### 1.3 The Role of Energy Storage Systems in Marine Applications

Energy Storage Systems (ESSs) play a crucial role in the marine sector due to the operational demands of modern ships. Vessels often face sudden changes in power needs, especially during activities like dynamic positioning, port entry, and emergency maneuvers. In these situations, a quick response from the ESS is essential to deliver power without waiting for traditional engines to adjust. ESSs are designed to supply high power for short periods with immediate response, making them ideal for maintaining stability and performance in fast-changing scenarios. For instance, in dynamic positioning, ESSs can instantly provide the power needed for thrusters, reducing the strain on diesel engines and cutting fuel consumption. Similarly, during peak loads, ESSs offer supplementary power, preventing engines from operating inefficiently at fluctuating levels.

One of the key benefits of ESSs in marine applications is their ability to improve fuel efficiency. By reducing the reliance on engines during peak loads or transient events, ESSs allow the main engines to function closer to their optimal efficiency, cutting fuel consumption and emissions. This is especially beneficial in hybrid vessels, where ESSs and traditional engines work together to extend operational range while reducing environmental impact.

ESSs also enhance the safety and reliability of marine operations. In emergency situations, such as equipment failure, the ability to instantly provide power can be critical, ensuring that vital systems like navigation and steering controls remain operational.

ESSs bridge the gap between slow-reacting traditional power sources and the fastchanging energy needs of modern marine operations, ensuring both efficiency and reliability.

#### 1.3.1 Types of Energy Storage Technologies

Marine applications require ESSs that are reliable, scalable, durable, and efficient. This section explores four major ESS technologies currently used or under development in the maritime industry: batteries, supercapacitors, flywheels, and superconducting magnets.

Each energy storage technology exhibits different performance characteristics in terms of power density and energy density. The Ragone diagram shown in Figure 1.2 summarizes the main technologies used for energy storing.

Figure 1.2 – Ragone diagram of ESS technologies [12].

#### 1.3.1.1 Batteries

Batteries have been the most common form of energy storage in marine applications due to their reliability [13]-[14]. However, despite their widespread use, batteries like lithiumion, lead-acid, and sodium-sulfur each come with challenges.

**Lithium-ion batteries** are considered the most suitable for marine use because of their high energy density, efficiency, and long-life cycle. They deliver sustained power over long periods, making them ideal for hybrid propulsion and electric ships. Their fast charging times are essential for vessels like ferries that require quick turnarounds. However, they are sensitive to extreme temperatures and can pose safety risks, such as thermal runaway. Advanced thermal management systems are required to mitigate these risks, and their high cost and space requirements remain barriers for some vessels.

**Lead-acid batteries** are still used due to their low cost and availability, often in auxiliary systems for backup power. However, they suffer from low energy density, short life cycles, and slow charging times. Corrosion from saltwater exposure can also degrade performance over time, making them less suitable for demanding applications.

**Sodium-sulfur batteries** offer high energy density and deep discharge capabilities but require high operating temperatures, which adds complexity and takes up valuable space. For smaller vessels, the added cost and operational difficulty outweigh the benefits, making them less practical for widespread use.

Batteries remain the primary energy storage solution for providing stable power over long periods, making them a cornerstone in marine applications like hybrid propulsion and electric ships. Among the various battery technologies, lithium-ion batteries are often favored due to their high energy density, efficiency, and relatively long-life cycle. Other battery types, such as lead-acid and sodium-sulfur, are still in use but come with limitations like lower energy density, slower charging times, or higher operational complexity.

However, while batteries excel at delivering steady power over extended durations, they are not the optimal choice for handling high power peaks over short periods. During transient operations, such as port maneuvers or emergency power demands, the rapid response required can place considerable stress on batteries, leading to faster degradation and reduced lifespan. In these scenarios, fast-response energy storage technologies are better suited to meet the high-power, short-duration demands without compromising the long-term health of the battery system.

#### 1.3.1.2 Supercapacitors

Supercapacitors, also known as ultracapacitors, complement batteries in marine ESSs. Unlike batteries, which store energy chemically, supercapacitors store it electrostatically, allowing for rapid charge and discharge. This makes them ideal for applications requiring short bursts of high power, such as dynamic positioning, load leveling, or emergency power.

Figure 1.3 - Li-ion battery vs Supercap [15].

Their long life cycle, often exceeding a million cycles, makes supercapacitors particularly useful in continuous operations. However, their lower energy density means they are more suitable for high-power, short-duration tasks rather than long-term energy storage.

#### **1.3.1.3** Flywheels

Flywheels store energy in the form of rotational kinetic energy. In marine applications, they are useful for stabilizing power supplies or providing backup power during peak demand. A rotating mass is accelerated using surplus energy, which is then converted back into electricity during high demand periods [16].

Flywheels are valuable in situations requiring quick response and high-power output, such as ship maneuvers. They are also employed in regenerative braking systems to recover and reuse kinetic energy. While they require minimal maintenance, careful integration into the ship's energy management system is needed to ensure efficiency.

#### 1.3.1.4 Superconducting Magnets

Superconducting magnets store energy in a magnetic field generated by a current through a superconducting coil. Their ability to deliver near-instantaneous power makes them highly effective for marine applications that require fast-response energy.

While superconducting magnets systems offer great potential for stabilizing voltage and frequency, they come with challenges, including high costs and the complexity of cryogenic cooling systems. As technology advances, superconducting magnets could become more viable for large-scale marine energy storage.

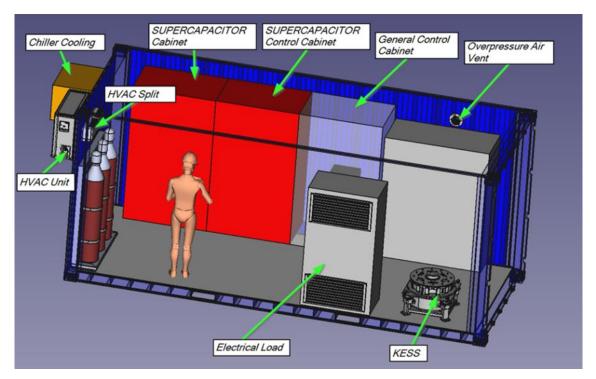

#### 1.4 Poseidon project

The Poseidon Project is an EU-funded initiative aimed at advancing energy storage solutions for marine applications [17]. Launched on January 1st, 2023, and running until December 31st, 2025, the project's primary goal is to demonstrate the feasibility of a Fast-Response Energy Storage System (FRESS) specifically designed for maritime vessels. This system integrates three advanced technologies: Kinetic Energy Storage System (KESS), Superconducting Magnetic Energy Storage (SMES), and Electrostatic Energy Storage System (EESS). These technologies will be tested on marine vessels to enhance operational efficiency and reduce reliance on traditional fossil fuel engines.

The Poseidon Project aims to address key challenges faced by the maritime industry, such as improving fuel efficiency, reducing emissions, and meeting the growing need for operational flexibility. By leveraging cutting-edge energy storage technologies, Poseidon seeks to optimize vessel performance in critical scenarios, such as docking and dynamic positioning, while contributing to international environmental goals.

In addition to technological development, Poseidon will focus on creating assessment tools like the Levelized Cost of Storage (LCOS) to evaluate the cost-effectiveness of these solutions and conduct Life Cycle Assessments (LCA) to quantify their environmental benefits. The project will also work on establishing safety standards and regulatory frameworks to facilitate the adoption of energy storage systems in the maritime sector.

The early findings of this project have been presented at the ELECTRIMACS'24 held in Castellò (Spain) from the 26th to the 30th of May 2024, and will be available in the proceedings of the conference once they will be published.

#### **1.4.1** Context

The maritime industry plays a pivotal role in global trade but also faces increasing pressure to reduce its environmental impact. The International Maritime Organization (IMO) has set ambitious targets to reduce greenhouse gas (GHG) emissions from maritime transport by

50% by 2050 compared to 2008 levels. Achieving these goals requires the adoption of cleaner, more efficient technologies.

While energy storage systems (ESS) have been explored as a means of reducing emissions and improving operational efficiency, the Poseidon Project aims to push this further by integrating FRESS into large vessels. This system will provide stable and reliable energy during high-demand operations, such as port maneuvering and dynamic positioning, reducing reliance on diesel engines and cutting fuel consumption.

Current propulsion systems often struggle with fluctuating power demands, leading to inefficiencies and increased emissions. By incorporating the advanced energy storage systems developed under Poseidon, vessels can operate more efficiently, with lower emissions and better fuel economy, particularly during peak load periods.

#### 1.4.2 Main Goals

The Poseidon Project's main goals are:

- Develop and demonstrate advanced ESS: The project aims to develop and test three

key energy storage technologies: Electrostatic Energy Storage Systems (EESS) based

on supercapacitors, Kinetic Energy Storage Systems (KESS) using flywheels, and

Superconducting Magnetic Energy Storage (SMES). These systems will be integrated

into marine vessels and evaluated for their ability to meet the operational needs of

modern shipping.

- 2. **Assess cost-effectiveness**: Poseidon will develop the Levelized Cost of Storage (LCOS) tool to help maritime operators evaluate the long-term financial benefits of adopting ESS technologies. This tool will provide a comprehensive framework that considers installation, maintenance, operational costs, and fuel savings.

- 3. Lifecycle analysis (LCA): The project will conduct detailed lifecycle assessments to measure the environmental impact of each energy storage system. These LCAs will focus on quantifying emissions reductions, energy savings, and the overall environmental footprint of the ESS technologies developed under Poseidon.

- 4. **Ensure safety and regulatory compliance**: As with any emerging technology, safety and regulatory standards are crucial. Poseidon will work closely with international regulatory bodies to ensure that the ESS technologies comply with safety standards

and maritime regulations. This effort includes identifying potential safety risks and contributing to the creation of guidelines for the safe integration of ESS into marine environments.

#### 1.4.3 Fast-Response Energy Storage System (FRESS)

The FRESS is a hybrid solution designed to manage the fluctuating power demands of marine vessels efficiently.

Figure 1.4 - Balearia's ferry.

Developed under the Poseidon project, FRESS integrates three different energy storage technologies: Kinetic Energy Storage System (KESS), Superconducting Magnetic Energy Storage (SMES), and Electrostatic Energy Storage System (EESS). These systems store energy in different ways, allowing for a flexible and reliable energy management solution that can deliver both immediate and sustained power. A significant component of the FRESS development process involved collaboration with Balearia, a leading ferry operator. Balearia not only provided the vessel (a typical vessel is shown in Figure 1.4) that will be equipped with the FRESS, but also supplied the power profiles required during the ferry's port operations.

These power profiles, which outline the energy demand peaks during docking and departure maneuvers, were critical for designing and sizing the FRESS. The power demand during these phases is typically much higher due to the heavy use of thrusters and other high-

power equipment, and the ability to respond to these spikes is crucial for improving operational efficiency.

Figure 1.5 - Power demand during port approach.

Figure 1.6 - Power demand during port departure.

The FRESS is designed to handle these high-demand periods by using the KESS to absorb and store energy during low-demand phases and release it during peak loads. Meanwhile, SMES provides instantaneous power for stability, and EESS responds to short, sharp power bursts, ensuring that the diesel engines can operate at optimal loads without being overstressed.

This system not only reduces fuel consumption and emissions but also enhances the overall reliability of the ferry's energy management system, making it a crucial step toward more sustainable maritime operations. The ability to combine multiple energy storage technologies in a single integrated system allows FRESS to meet the varying power demands of the vessel while supporting the global push toward cleaner and more efficient marine transport.

#### 1.4.3.1 Kinetic Energy Storage System (KESS)

The KESS relies on the principle of storing energy in a rotating mass, following the equation  $E = \frac{1}{2}J\omega^2$ , where J represents the moment of inertia and  $\omega$  the angular velocity. Energy is stored by accelerating the mass using an electric machine coupled to the flywheel. When energy is needed, the machine decelerates the flywheel to extract power. The decoupling of energy and power allows for flexible operation: energy is related to rotational speed, while the power capability is determined by the electric machine's capacity.

In this case, the design target power for KESS is 20 kW, a value chosen based on CIEMAT's expertise in machine design for high-speed applications. This power level was considered suitable for unitary modules and aligns with the power profiles provided by Balearia, which outlined the vessel's peak power requirements during port maneuvers, specifically docking and departure phases. These are periods of high power demand, and the KESS ensures that the energy demands are met without over-relying on diesel engines, thus improving fuel efficiency and reducing emissions.

Among the electrical machines suitable for this system, the Switched Reluctance Machine (SRM) was selected due to its superior performance characteristics. SRMs have lower losses in no-load conditions, no demagnetization issues at high temperatures (as found in permanent magnet machines), and are more cost-effective, avoiding the use of rare earth materials. A 6/4 configuration of the SRM was chosen, as it minimizes torque ripple and is suitable for high-speed operations, making it an ideal candidate for kinetic energy storage in the KESS.

The SRM requires the use of power electronics to manage the sequential switching of its phases. The machine operates by energizing coils in each phase, generating magnetic forces that rotate the rotor to a position of maximum alignment. Once alignment is achieved, the system de-energizes the current phase and energizes the next, creating continuous rotation

and allowing for efficient energy transfer between the rotating flywheel and the vessel's power grid.

Figure 1.7 - KESS 3D.

The energy stored in the KESS flywheel is based on the inertia of the rotating mass and the square of its rotational speed. For this project, a solid high-strength steel cylinder was selected as the flywheel, capable of operating at speeds ranging from 8000 to 10,400 rpm. This rotational speed range provides a total energy storage capacity of approximately 1.1 kWh, ensuring that the system can meet the vessel's short-term power demands during critical operations.

#### **1.4.3.2** Superconducting Magnetic Energy Storage (SMES)

The SMES system is a critical part of the FRESS, designed to store energy in the magnetic field generated by a direct current (DC) flowing through a superconducting coil according to the expression  $E = \frac{1}{2}LI^2$ , where L is the inductive value of the coil and I is the RMS value of the current flowing through it. The system includes three main components: the superconducting magnet, the cooling system, and the power conditioning system (PCS). The superconducting coil is made of Second Generation High-Temperature Superconductor, better known through its acronym 2G HTS, tape and operates at extremely low temperatures,

facilitated by a cryogenic cooling system, typically between 4.2K and 20K. This enables the coil to achieve zero resistance, allowing it to store energy with minimal losses.

The coil's geometry, particularly the number of turns and the separation between them, significantly affects the SMES's energy storage capability. The solenoidal coil configuration chosen for the Poseidon project consists of 12 double pancakes with a total of 144 turns per coil, yielding an inductance of 1.68 H and a nominal current of 457 A at 4.2K. This design results in an energy storage capacity of 275 kJ. The system optimization involved fine-tuning the separation between coils to maximize energy density while keeping the overall size within the physical constraints of marine applications.

Figure 1.8 - SMES block scheme.

For cooling, a flow refrigeration system using forced helium gas was selected, as it offers cost-effectiveness, compactness, and reliable performance over a broad range of operating temperatures. This cooling system, referred to as the Cryogenic Supply System (CSS), ensures the superconducting coil maintains its critical low temperature, thereby enabling efficient energy storage.

The Power Conditioning System (PCS), which connects the SMES to the vessel's power grid, is based on a Voltage Source Converter (VSC) topology. This allows for the exchange of power between the grid and the SMES in all four quadrants. The PCS features a grid-side inverter and a DC-DC chopper, controlling the voltage across the DC-link capacitor to

regulate energy flow. This configuration helps maintain moderate AC losses and Total Harmonic Distortion (THD), ensuring the system operates efficiently and safely within the vessel's power grid.

#### 1.4.3.3 Electrostatic Energy Storage System (EESS)

The EESS, based on supercapacitors, plays a crucial role in the FRESS by delivering rapid energy bursts for short-duration power demands. The design and manufacturing of this system will be described more in detail in the next chapter since this activity has been my main contribution to the Poseidon project.

#### 1.4.4 EESS Design

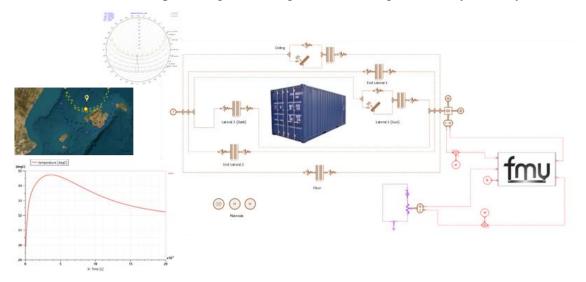

The EESS for the Poseidon project was designed based on a simulation model developed using PLECS software by Plexim. The general schematic of the system, highlighting the main components, is shown in Figure 1.9.

#### 1.4.4.1 Simulation model

Starting from the left of the diagram shown in Figure 1.9, the ferry's common DC bus is represented by an ideal DC voltage source with a resistor in series (depicted in brown). Connected directly to this DC bus is the bidirectional DC/DC converter (in blue). Downstream of the converter is a filtering stage comprising three inductors, one for each leg of the converter (highlighted in red). This is followed by a filter capacitor with a parallel damping branch (in orange) and a second filter inductor (in purple). Finally, downstream of the filtering stage is the supercapacitor (SC) bank (in green).

Figure 1.9 – General scheme of the model.

The initial step in the design was to size the SC bank appropriately. The minimum goal for the EESS was to design an SC bank that, at its End of Life (EOL), is capable of providing 2.5 MJ of energy to the common DC bus, with a maximum peak power of 100 kW.

The fundamental equation relating the energy delivered  $E_{delivered}$  to the capacitance C of the bank is:

$$E_{delivered} = \frac{1}{2} C \left( V_{top}^2 - V_{bottom}^2 \right). \tag{1.1}$$

To determine the total capacitance required, it is necessary first to define the maximum voltage  $V_{top}$  at which the bank is fully charged and the minimum residual voltage  $V_{bottom}$  at the end of the energy transfer.

Considering that the SC bank's voltage can be either the input or output voltage of the bidirectional DC/DC converter, and that the common DC bus voltage is 850 V, it is advantageous to set  $V_{top}$  lower than 850 V. This ensures that the bidirectional converter will always operate as a boost converter during the discharge of the bank towards the DC bus and as a buck converter during the recharge stage. Setting  $V_{top}$  higher than 850 V would necessitate the converter to switch modes during charging or discharging, complicating the control strategy.

Therefore,  $V_{top}$  for the SC bank was set to 750 V.

For  $V_{bottom}$ , it is important to note that supercapacitors release approximately 75% of their total stored energy when discharging from 100% to 50% of their State of Charge (SoC). Discharging the SCs below 40% of their nominal peak voltage is not practical and can be risky, considering that the lower the voltage the higher is the current needed to satisfy the power demand, jeopardizing the life of the semiconductors. Thus,  $V_{bottom}$  should not be lower than 300 V.

With  $V_{top} = 750 \text{ V}$  and  $V_{bottom} = 300 \text{ V}$ , the total capacitance of the SC bank can be calculated by rearranging (1.1):

$$C = \frac{2 \cdot E_{delivered}}{(V_{top}^2 - V_{bottom}^2)} = \frac{2 \cdot 3 \cdot 10^6}{(750^2 - 300^2)} = 12.7 [F].$$

(1.2)

This value represents the minimum EOL capacitance required for the SC bank.

The DC/DC converter features three IGBT legs and is configured as a chopper. All legs are driven synchronously to ensure proper current sharing among them. Since the peak

voltage of the SC bank is always lower than that of the DC bus, the DC/DC converter operates as a buck converter during the charging stage and as a boost converter when transferring energy from the SC bank to the DC bus.

The filtering stage is critical because supercapacitors are sensitive to frequencies above 100 Hz. The three inductors placed at the output of the converter provide initial filtering by smoothing the high-frequency components of the current resulting from the converter's switching actions. Downstream of the common point of these inductors, there are three parallel branches:

- 1. The filter capacitor  $C_{filter}$

- 2. The damping branch

- 3. A series combination of the second filter inductor  $L_{filter}$  and the SC bank

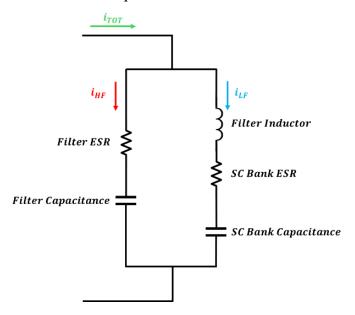

In Figure 1.10, the damping branch is neglected for simplification, as its impedance is typically one or two orders of magnitude higher than the other two branches. The design goal is to size these two branches such that, for frequencies above approximately 100 Hz, the impedance of the filtering branch  $Z_{filterbranch}$  is much lower than that of the SC bank branch  $Z_{SCbranch}$ , while the opposite holds true at low frequencies.

Figure 1.10 - Filter diagram.

The equivalent impedances of the two branches can be computed as:

• Filter branch impedance:

$$Z_{filterbranch} = \frac{1}{j\omega C_{filter}} + R_{ESRfilter}$$

(1.3)

• SC bank branch impedance:

$$Z_{SCbranch} = j\omega L_{filter} + \frac{1}{j\omega C_{SCbank}} + R_{ESRbank}$$

(1.4)

where:

$$\omega = 2\pi f$$

;

f is the frequency;

$R_{ESR}$  is the Equivalent Series Resistance (intrinsic resistance of each component).

Then, the dimensional constraint becomes:

$$Z_{filterbranch} \le Z_{SCbranch}$$

for  $f \ge 100 \, Hz$ . (1.5)

This ensures that high-frequency ripple currents predominantly flow through the filter capacitor rather than the SC bank, thus reducing stress on the supercapacitors.

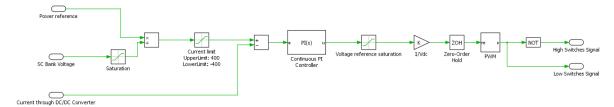

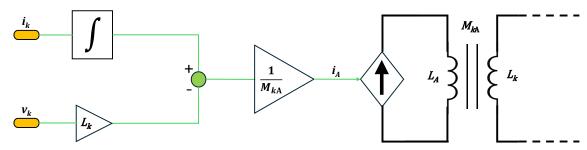

Figure 1.11 illustrates the control logic blocks used in the system. The control implemented takes in input a Power profile reference, the SC voltage measurement and the total current measured on the DC/DC converter.

Figure 1.11 - Control blocks.

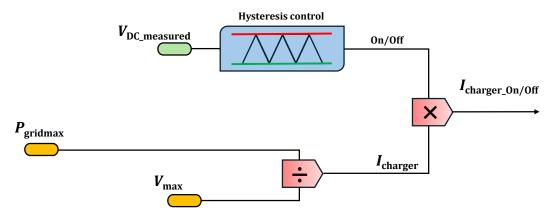

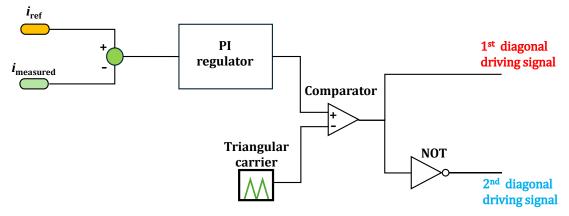

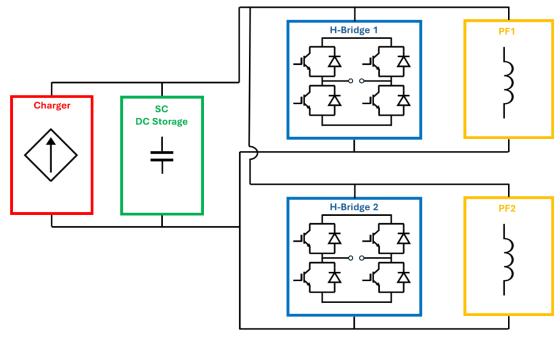

The current converter reference is generated through the power reference and the measured SC voltage, then it is compared to the measured converter current, and the error is regulated through a PI regulator, the output of the regulator, scaled, is used as modulating signal for the PWM block with switching frequency of 5kHz, that will generate the proper driving signals for the converter's IGBTs.

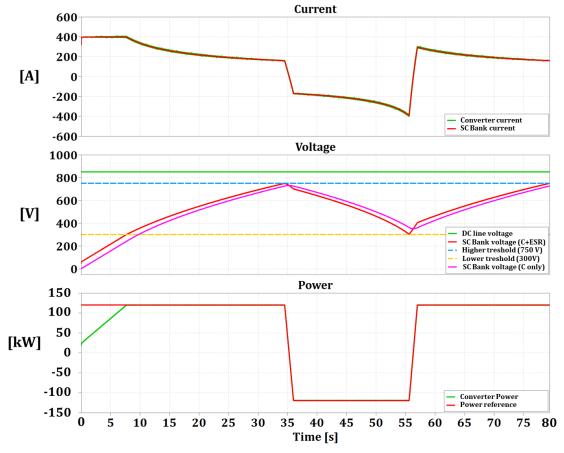

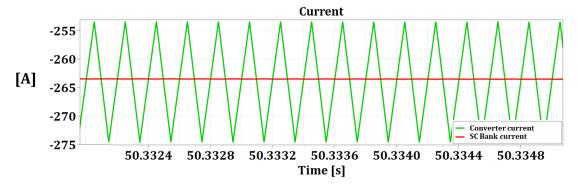

The main outcomes of the simulation are presented in Figure 1.12. The top plot shows the comparison between the converter current and the current flowing in the SC Bank. As

highlighted in Figure 1.13, the current in the SC branch is much smoother, thanks to the action of the filters. The middle plot shows the common DC line voltage (in green), the voltage across the SC bank (in red), the higher voltage threshold (in blue), the lower voltage threshold (in yellow) and the SoC of the SC bank (in purple). The bottom plot displays the power reference (in red) and the actual power delivered (in green).

In the simulated scenario, a conservative approach was taken by assuming that the power demand is always at the peak value. The peak power was set to 120 kW, which is 20% higher than the minimum design goal of 100 kW. During the initial few seconds, the actual power increases linearly due to a current limitation imposed to protect the IGBTs. Once the current stabilizes below the limit of 400 A, the converter accurately tracks the power reference.

Figure 1.12 - Main Outcomes.

Figure 1.13 shows in detail the comparison between the current flowing through the converter and the one through the SC bank. It is evident that a high-frequency ripple current with a peak-to-peak amplitude up to 25 A is present in the converter current (the cumulative current flowing through the three filter inductors at the output of the converter) while it is absent on

the SC bank, this is due to the action of the filters. This effectively reduces the stress on the supercapacitors, enhancing their lifespan.

Figure 1.13 – Comparison between converter current and SC Bank current.

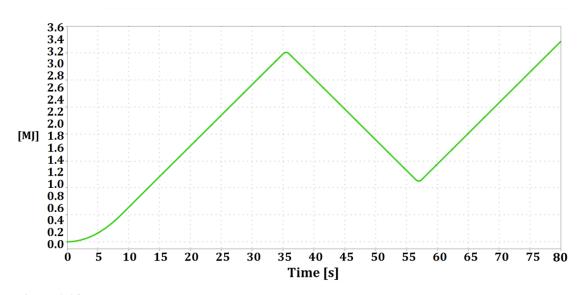

Finally, Figure 1.14 depicts the energy stored in the SC bank. Starting from 0 MJ (fully discharged) it reaches 3.6 MJ once the charge is completed, then, during the discharge, 3 MJ are released from 750 V to 300 V.

**Figure 1.14** – Energy stored in the EESS.

## 1.4.4.2 Selected Components

The component selection started with a proper IGBT model. Considering the voltage level of the common DC line (850 V), the selected IGBT module was the MITSUBISHI CM600DX-34T. This component has a voltage rating of 1700 V that makes it suitable for this application. Furthermore, the current rating (600 A continuous current) ensures a good safety margin since it should carry current not higher than 133 A at 5kHz.

Figure 1.15 – Main data of Mitsubishi CM600DX-34T.

In order to validate this choice, the thermal model of the component has been built on PLECS and has been used to run thermal simulations.

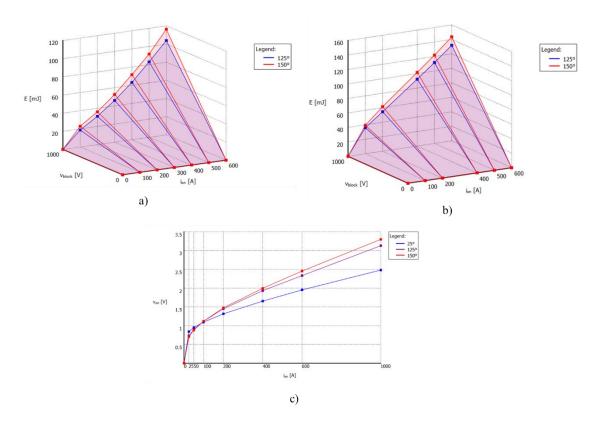

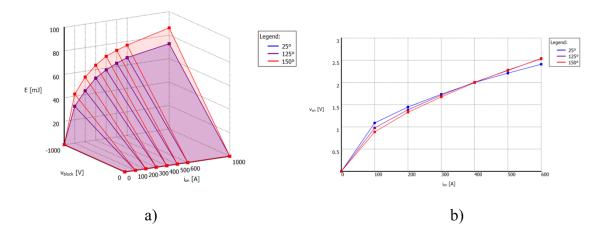

Figure 1.16 and Figure 1.17 show the pictures of the thermal models built for IGBTs and diodes. All curves have been retrieved from the datasheet of the MITSUBISHI CM600DX-34T.

**Figure 1.16** – IGBT thermal model CM600DX-34T: a) Turn on Losses; b) Turn off Losses; c) Conduction Losses.

Figure 1.17 - Diode thermal model CM600DX-34T: a) turn off losses; b) conduction losses.

Figure 1.18 shows the PLECS thermal network for the thermal simulations.

Figure 1.18 – Thermal network built in the simulation model.

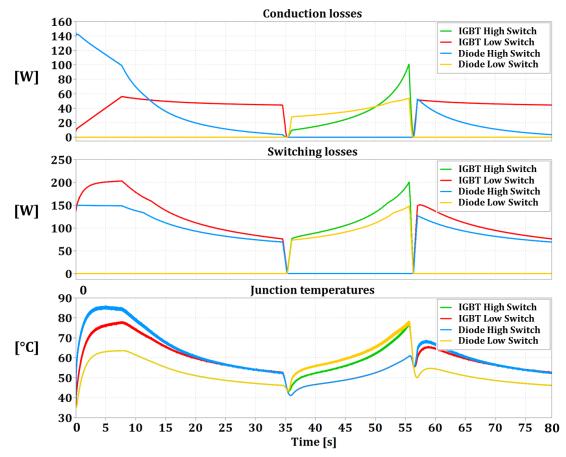

The results of the thermal simulations are summarized in Figure 1.19, which shows that the application is safe from the point of view of the temperatures, considering that the maximum temperature reached is 85 °C and it is reached during the interval in which the converter is operating at the maximum current (400 A).

Figure 1.19 – Main outcomes from thermal simulations.

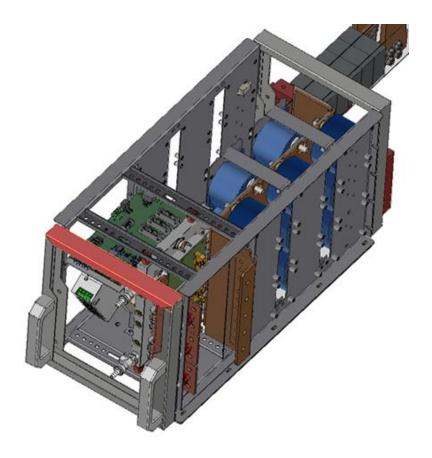

The individual power module (shown in Figure 1.20) is a water-cooled unit provided with IGBTs in the standard 150 x 62 x 17 mm package and completed with IGBT drivers, diagnostic board, bus-bar and local DC-bus film capacitors.

The use of film capacitors also gives a strong contribution to the overall reliability of each module. Moreover, if the module is used as a spare part and is stocked for several years, it does not lose its electrical properties during the stockage period.

The cooling plate of IGBT is realized with copper and stainless steel in contact with water. The capacitors are sized to withstand the ripple current of the IGBT. The power module can be configured to realize different converter topologies and can be equipped with different IGBT and capacitors voltage ratings. For the application presented in this document, the module is configured as half-bridge chopper with three 1700V IGBTs modules in parallel.

The connection between capacitors and semiconductors is made of low inductance laminated busbars.

**Figure 1.20** – Triumf Generation Power Module (TGPS), designed for a power supply at the TRIUMF Canada's Particle Accelerator Centre.

The IGBT drivers used are the Power Integrations 2SP0115T2A0-17, which are directly soldered to the IGBT. The IGBT switching signals and status feedback signals are provided through optic fibre for improved disturbance immunity.

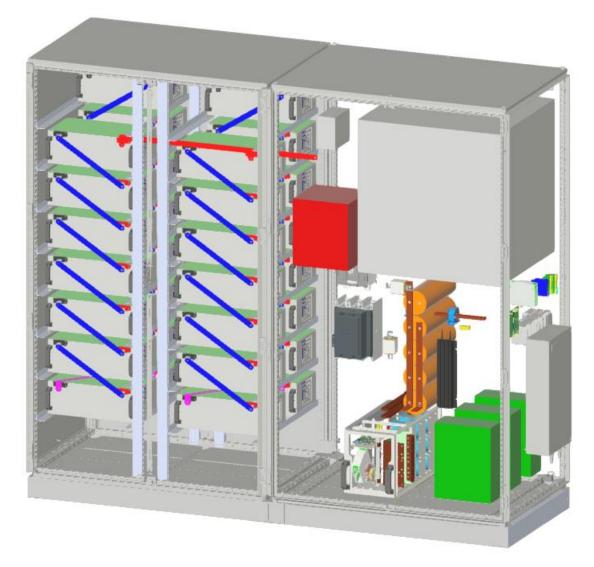

For the SC module, the selected component was the module CapTop CTM 00165C0 0054V0 NN00, depicted in Figure 1.21. This module is rated at 54 V and 165 F, with the capability to handle peak currents of up to 2000 A for short durations. Each module is built through a series connection of 18 SC cells rated 3V 3000F and has its own Dynamic Cells Balancing (DCB) system, reporting to the String Management Unit (SMU) that exposes the ModbusRTU interface for monitoring. Each string will therefore have one or more Modbus addresses.

The suitable voltage and capacitance ratings of the CapTop SC module, along with its high current handling capacity, align well with the requirements of the application.

To arrange the SC Bank, two paralleled stacks of 15 SC modules each will be placed into a cabinet, giving to the SC bank a total capacitance at the Beginning Of Life (BOL) of 22 F

(that at the EOL will be around 17 F). This gives a considerable margin respect to the minimum capacitance needed computed in (2), allowing the system to transfer the required amount of energy with a reduced voltage jump, that implies reduced peak currents and stress on the components.

**Figure 1.21** – CapTop CTM 00165C0 0054V0 NN00 Power Brick.

For what concerns the passive components, the three inductors to be placed one at the output of each converter leg have been sized to have an inductance of 6 mH, a nominal current of 130 A with a ripple superimposed of 13  $A_{pk-pk}$  at 4 kHz. The second filtering inductor has been sized with an inductance of 540  $\mu$ H, a nominal current of 350 A and a superimposed ripple of 35  $A_{pk-pk}$  at 4 kHz. In both cases, the manufacturer is Trasfoproject. Finally, the filter capacitors chosen are the Ducati DCH 85C series, model 416.85.V. 195.x rated 900 V and 4.5 mF. Figure 1.22 shows the picture of the family DCH 85 C. The same component is used for the damping branch, where four capacitors in parallel are in series to a 0.5  $\Omega$  resistor.

Figure 1.22 - Ducati DCH 85C series.

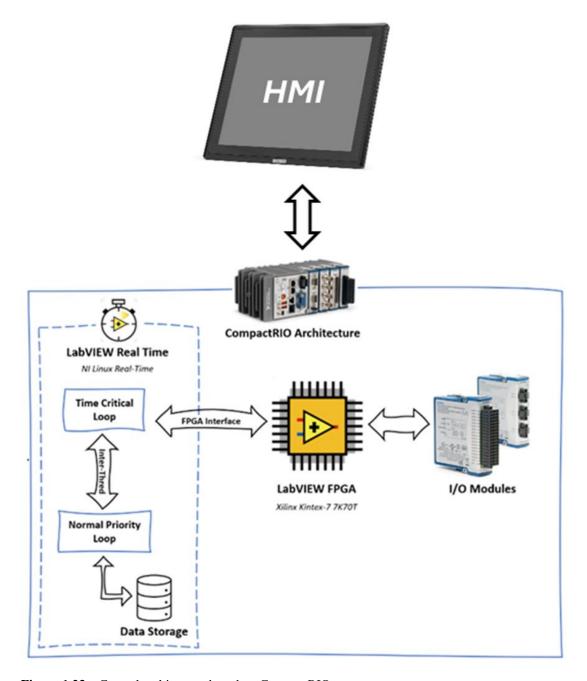

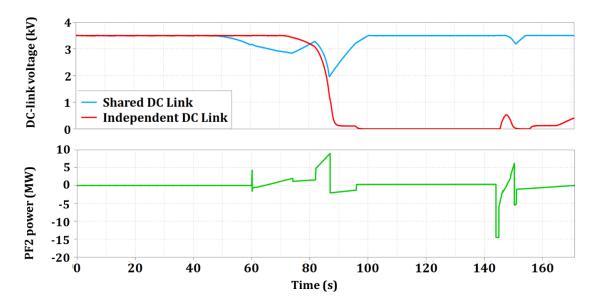

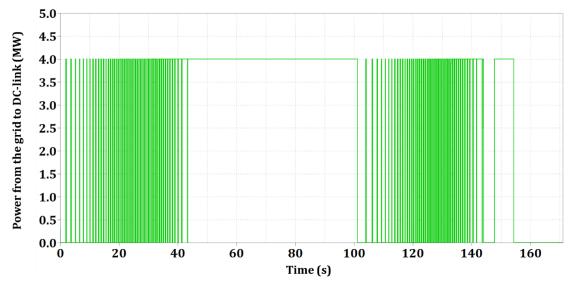

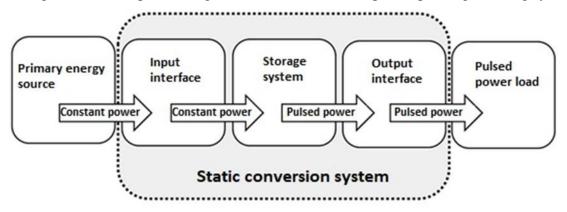

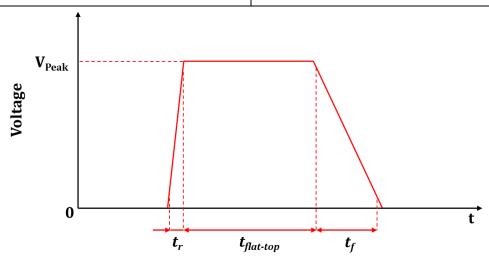

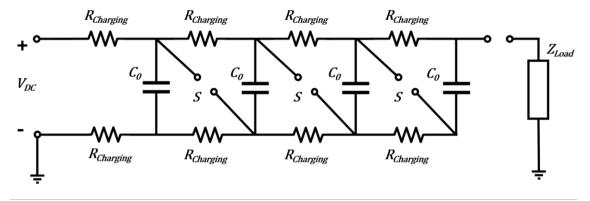

#### 1.4.4.3 Control Architecture