# DOTTORATO DI RICERCA IN DATA SCIENCE AND COMPUTATION

Ciclo 36

Settore Concorsuale: 09/H1 - SISTEMI DI ELABORAZIONE DELLE INFORMAZIONI

Settore Scientifico Disciplinare: ING-INF/05 - SISTEMI DI ELABORAZIONE DELLE

**INFORMAZIONI**

## SCALING PERFORMANCE AT THE END OF MOORE'S LAW: A PROGRAMMER'S PERSPECTIVE

Presentata da: Federico Ficarelli

Coordinatore Dottorato Supervisore

Daniele Bonacorsi Luca Benini

Co-supervisore

Andrea Bartolini

## Contents

| A | bstra  | ct :                                                  | xii       |

|---|--------|-------------------------------------------------------|-----------|

| P | reface | 2                                                     | 1         |

| 1 | The    | Present of Sustainable HPC: GPU-Accelerated Systems   | 8         |

|   | 1.1    | Use Case: Exascale Drug Discovery                     | 11        |

|   | 1.2    | The Virtual Screening Application                     | 12        |

|   | 1.3    | Architecture of GPU Accelerators                      | 14        |

|   | 1.4    | Latency-Optimized Kernels for Task-Based Workloads    | 15        |

|   | 1.5    | Throughput-Optimized Kernels for Task-Based Workloads | 18        |

|   | 1.6    | Experiments                                           | 21        |

|   |        | 1.6.1 Preprocessed Datasets                           | 22        |

|   |        | 1.6.2 Scaling Analysis                                | 23        |

|   |        | 1.6.3 Real World Datasets                             | 24        |

|   |        | 1.6.4 Micro-Architectural Profiling                   | 25        |

|   | 1.7    | Urgent Computing Against COVID-19                     | 40        |

|   |        |                                                       | 40        |

|   |        | 1.7.2 High-throughput Docking Workflow                | 41        |

|   |        | 1.7.3 Urgent Computing Setup                          | 47        |

|   |        | 1.7.4 Evaluating the storage requirements             | 48        |

|   |        | 1.7.5 Intra-node Scaling                              | 49        |

|   |        | 1.7.6 HPC System Scale-out                            | 50        |

|   |        | 1.7.7 Data Pre/Post-processing                        | 51        |

|   | 1.8    | Conclusion                                            | 52        |

| 2 | The    | Future of Sustainable HPC: RISC-V                     | <b>56</b> |

|   | 2.1    | The Monte Cimone Experimental System                  | 58        |

|   | 2.2    | State-of-the-art                                      | 60        |

|   | 2.3    | Hardware Architecture                                 | 61        |

|   | 2.4    | Software Environment                                  | 64        |

|   |        | 2.4.1 HPC Software                                    | 65        |

|   |        | 2.4.2 Power Monitoring Infrastructure                 | 65        |

|   | 2.5    | Assessment Experiments                                | 65        |

|    |                 | 2.5.1    | HPC Applications Performance                       | •   | 66  |

|----|-----------------|----------|----------------------------------------------------|-----|-----|

|    | 2.6             | Heter    | ogeneous HPC on RISC-V: Accelerating Monte Cimone  |     | 69  |

|    | 2.7             | RISC-    | V for HPC: Conclusion and Prospects                |     | 70  |

| 3  | Mu              | lti-leve | el SSA Compilers for RISC-V Accelerators           |     | 72  |

|    | 3.1             | Comp     | iling at the End of Moore's Law: Introduction      |     | 74  |

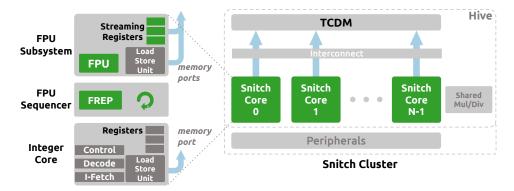

|    | 3.2             | The S    | nitch Architecture                                 |     | 76  |

|    |                 | 3.2.1    | Programming Model                                  |     | 80  |

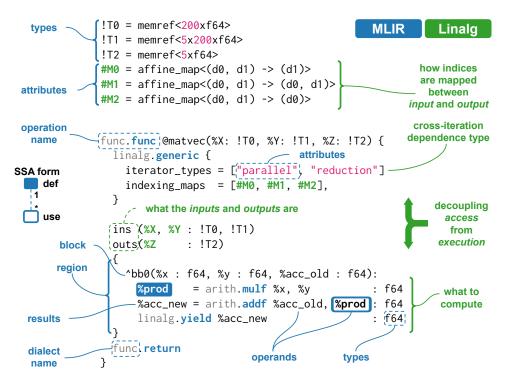

|    | 3.3             | The N    | MLIR Ecosystem                                     |     | 82  |

|    |                 | 3.3.1    | IR Structure                                       |     | 84  |

|    |                 | 3.3.2    | Linear Algebra Programs in MLIR                    |     | 86  |

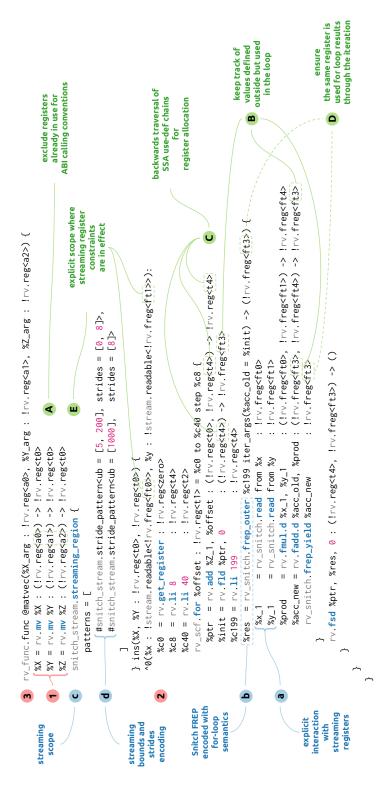

|    | 3.4             | A Mu     | lti-Level Compiler Backend                         |     | 86  |

|    |                 | 3.4.1    | Representing SSRs                                  |     | 91  |

|    |                 | 3.4.2    | Type Legalization                                  |     | 91  |

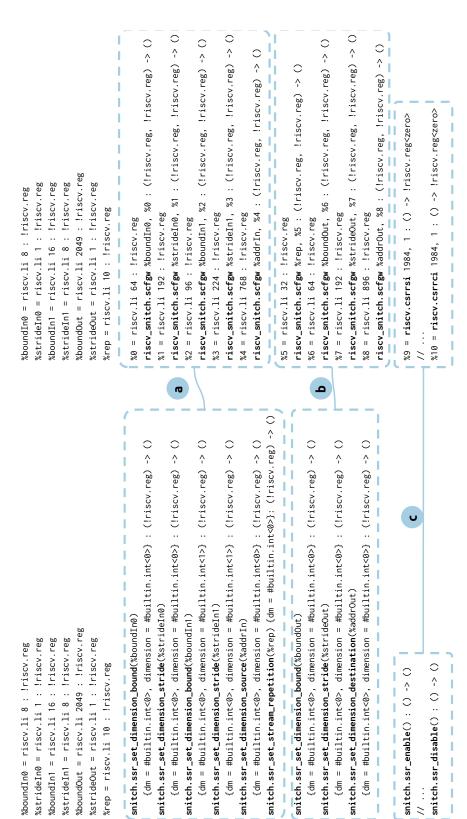

|    |                 | 3.4.3    | Configuring Software-Managed Prefetchers           |     | 95  |

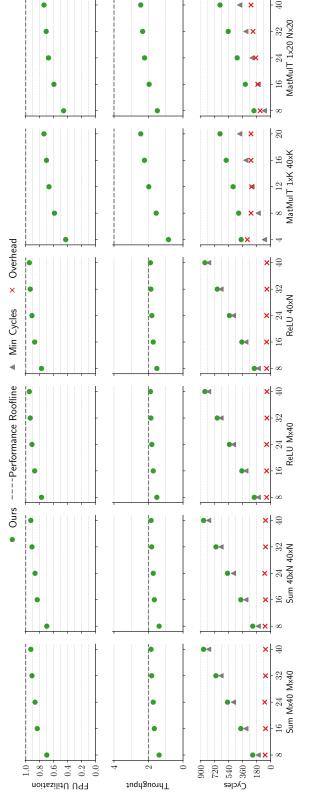

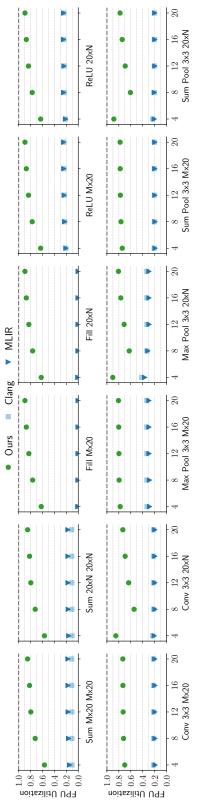

|    | 3.5             | Exper    | imental Evaluation                                 |     | 95  |

|    |                 | 3.5.1    | Performance Model                                  |     | 100 |

|    |                 | 3.5.2    | Performance Metrics                                |     | 101 |

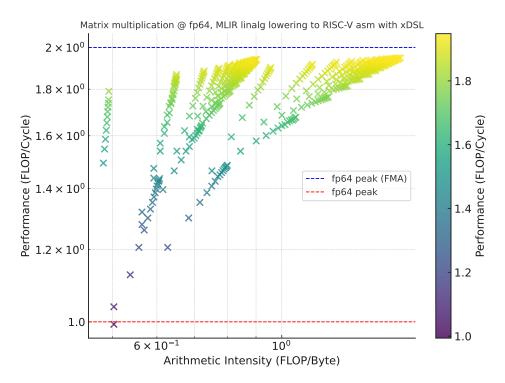

|    |                 | 3.5.3    | Continuous Testing and Benchmarking Infrastructure |     | 102 |

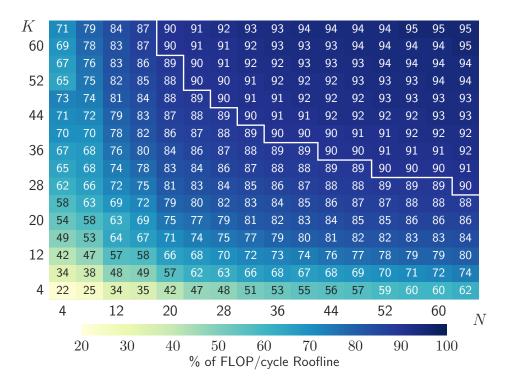

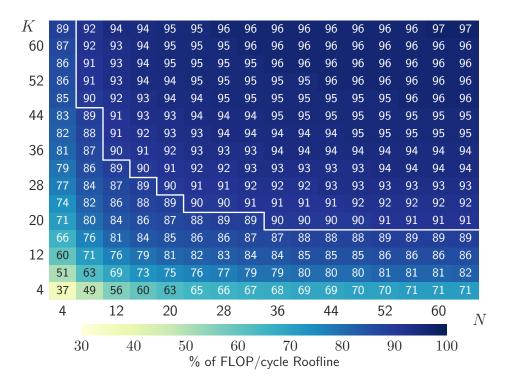

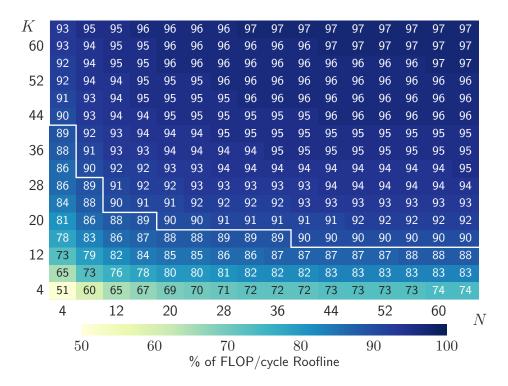

|    |                 | 3.5.4    | Experimental Results                               |     |     |

|    | 3.6             | Relate   | ed Work                                            |     |     |

|    | 3.7             |          | iling at the End of Moore's Law: Conclusion        |     |     |

| Fi | nal (           | Conclu   | sions                                              | ]   | 114 |

| B  | ibliography 117 |          |                                                    | 117 |     |

# List of Figures

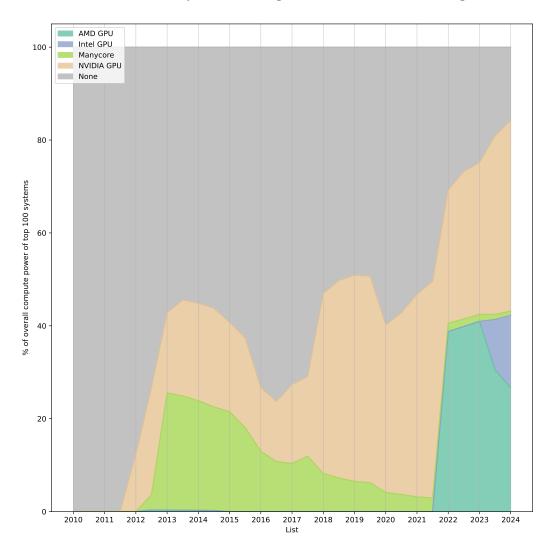

| 1.1 | Evolution of the share of compute power per accelerator across               |     |

|-----|------------------------------------------------------------------------------|-----|

|     | the first 100 positions of TOP500 supercomputer rankings                     |     |

|     | since 2010                                                                   | 9   |

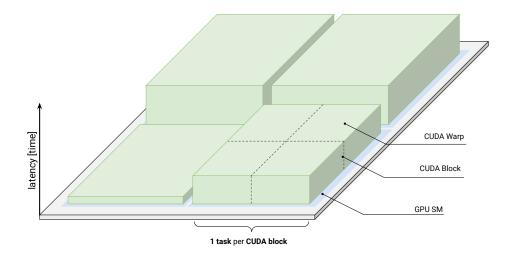

| 1.2 | Task-to-resources mapping for the latency-oriented strategy                  |     |

|     | on the GPU. Execution time $(x \text{ axis})$ is kept optimal by al-         |     |

|     | locating the largest possible resources to each task. Multiple               |     |

|     | warps process a task, and each task consumes all the resources               |     |

|     | available on a GPU streaming multiprocessor (SM)                             | 16  |

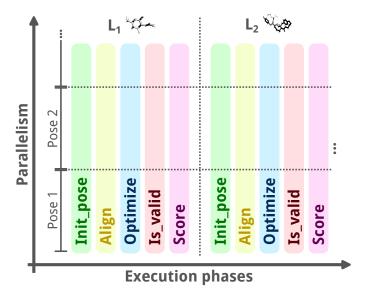

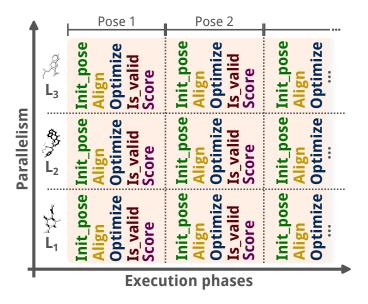

| 1.3 | Logical mapping on how the latency approach hinges on GPU                    |     |

|     | parallelism to accelerate the execution time. Each step is im-               |     |

|     | plemented using at least one dedicated kernel                                | 17  |

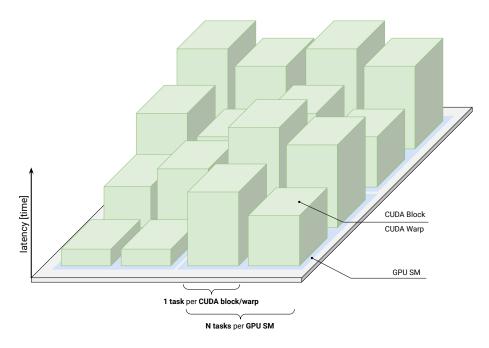

| 1.4 | Task-to-resources mapping for the throughput-oriented strat-                 |     |

|     | egy on the GPU. Execution time $(x \text{ axis})$ is worse than with         |     |

|     | the latency-oriented approach, but each task is granted a                    |     |

|     | fixed, minimum amount of resources. A single warp processes                  |     |

|     | a task, and multiple tasks can be fit into the resource pool of              |     |

|     | a single GPU streaming multiprocessor (SM)                                   | 18  |

| 1.5 | Logical mapping on how the batched approach hinges on GPU                    |     |

|     | parallelism to accelerate the execution time. All the steps are              |     |

|     | implemented in a single kernel                                               | 19  |

| 1.6 | Graphical representation of the batch formation process. In-                 |     |

|     | coming ligands are clustered according to their characteristics:             |     |

|     | first by the number of atoms, then by the number of torsional                |     |

|     | bonds. When a bucket is full, i.e., when the amount of ligands               |     |

|     | is enough to allocate all GPU resources, the batch is executed.              | 21  |

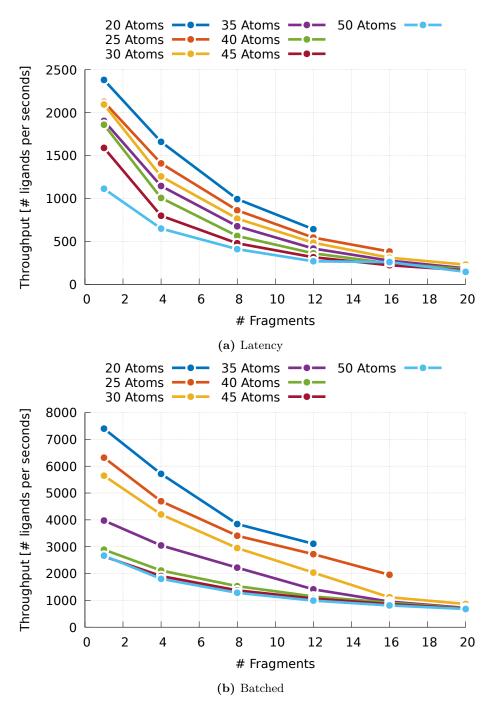

| 1.7 | Throughput of the two implementations with the different                     |     |

|     | datasets, organized by the number of atoms and increasing                    |     |

|     | the number of fragments on the x-axis                                        | 32  |

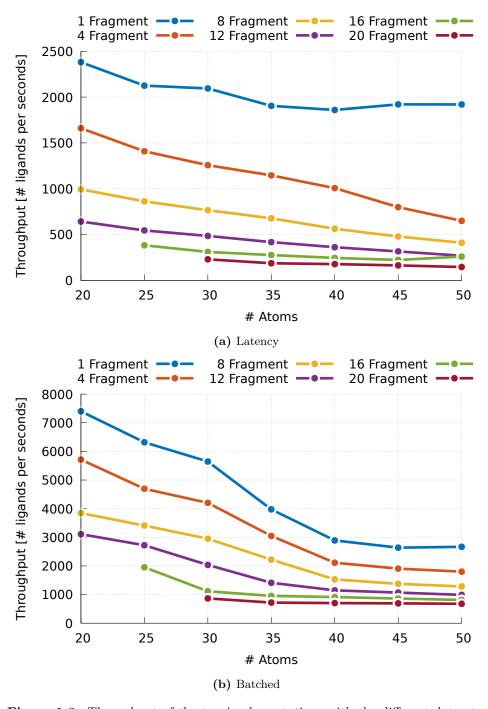

| 1.8 | Throughput of the two implementations with the different                     |     |

|     | datasets, organized by the number of fragments and increasing                |     |

| 1.0 | the number of atoms on the x-axis                                            | 33  |

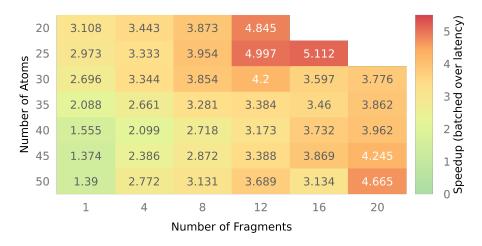

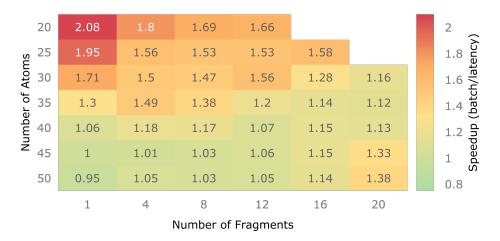

| 1.9 | Speedup heatmap of batched versus latency for different ho-                  | 0.4 |

|     | mogeneous datasets of $50 \mathrm{K}$ ligands with the same characteristics. | 34  |

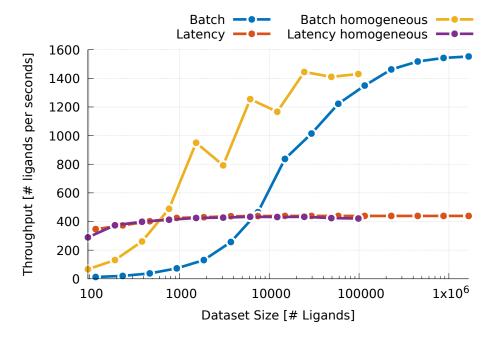

| 1.10 | Single GPU throughput behaviour with varying input dataset size for all the presented approaches. While the latency-op-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | timized kernel dominates the throughput-optimized one on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | small datasets, after the break-even point at around 1000 lig-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | ands the latter scales up to a sustained 1600 ligands per second.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 34 |

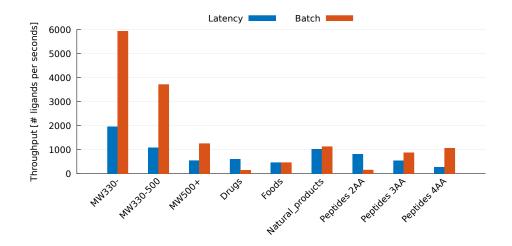

| 1.11 | Throughput comparison on the Mediate dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 35 |

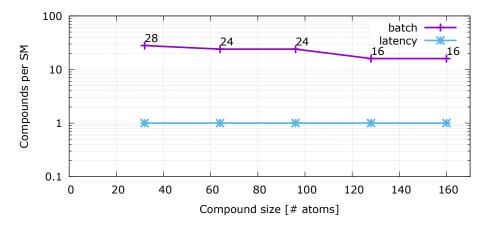

|      | Ligand allocation per GPU streaming multiprocessor (SM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 35 |

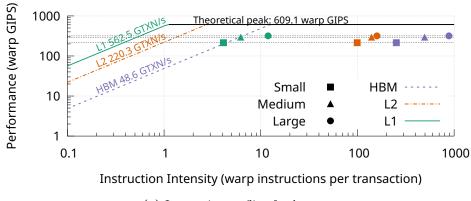

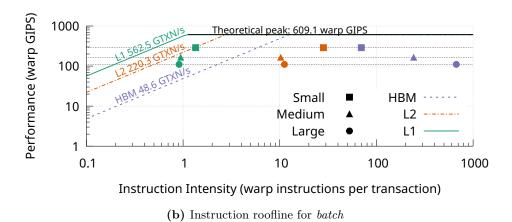

|      | Roofline analysis comparison between <i>latency</i> (top) and <i>batch</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 |

| 1.10 | (bottom) on instruction performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 36 |

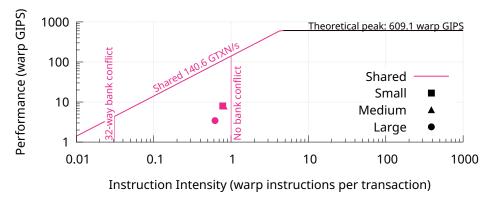

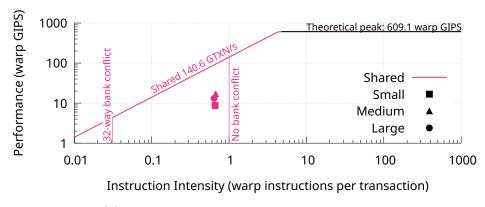

| 1 14 | Roofline analysis comparison between <i>latency</i> (top) and <i>batch</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50 |

| 1.14 | (bottom) on shared memory access pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 37 |

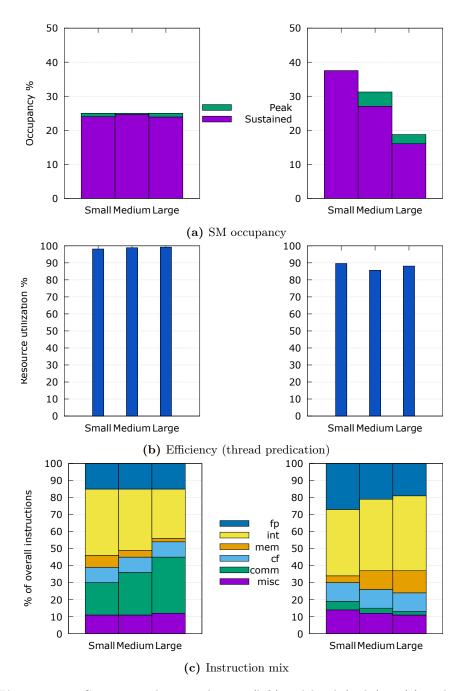

| 1 15 | Comparison between <i>latency</i> (left) and <i>batch</i> (right) on (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 91 |

| 1.10 | peak and sustained active warps, (b) efficiency (or thread                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|      | predication) and (c) instruction mix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38 |

| 1 16 | Speedup heatmap of the batched version against the latency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30 |

| 1.10 | one for the different homogeneous datasets without the early                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |

|      | exit from the <i>check bump</i> function. Both throughputs are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

|      | taken with large enough datasets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 39 |

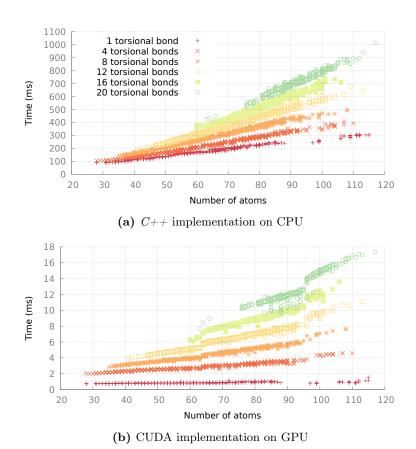

| 1 17 | Time required to dock and score a ligand by varying the num-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00 |

| 1.11 | ber of atoms and torsional bonds. The C++ implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | use a single core IBM 8335-GTG 2.6 GHz. The CUDA imple-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

|      | mentation use a single NVIDIA V100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 42 |

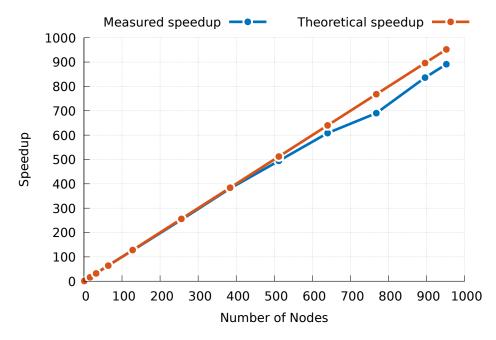

| 1 18 | Strong scaling experiment of the high-throughput molecular                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 42 |

| 1.10 | docking on the whole Marconi100 supercomputer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45 |

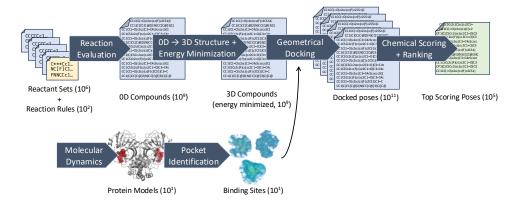

| 1.19 | Exscalate workflow, from the input (ligand's chemical library                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 10 |

| 1.10 | and the protein models) on the left to the outcome (most                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

|      | promising set of molecules) on the right                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 46 |

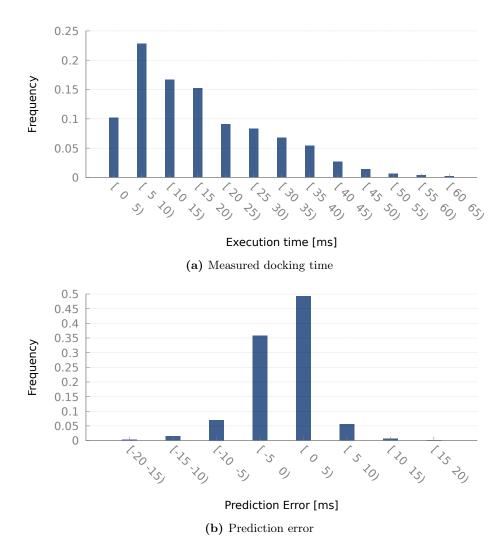

| 1 20 | Frequency distribution of the measured docking time, using                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 10 |

| 1.20 | the CUDA implementation, and its prediction error. Values                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

|      | with a frequency lower than 0.001 are discarded for conciseness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|      | purposes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 54 |

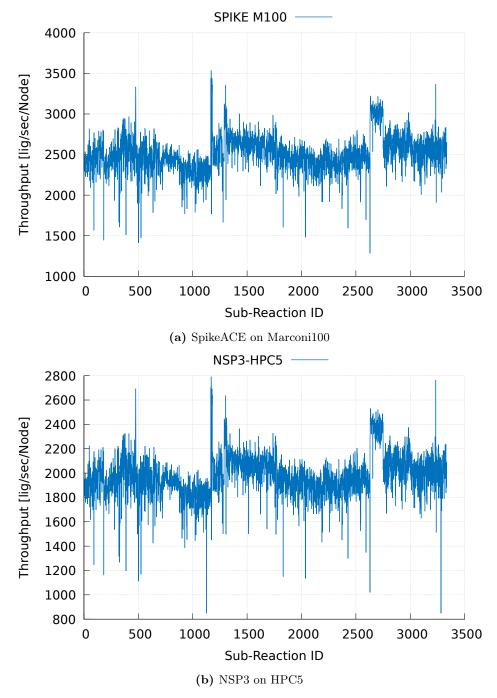

| 1.21 | Execution track of two entire job arrays targeting two different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|      | protein pockets on the two different supercomputers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 55 |

|      | Francisco Control Cont |    |

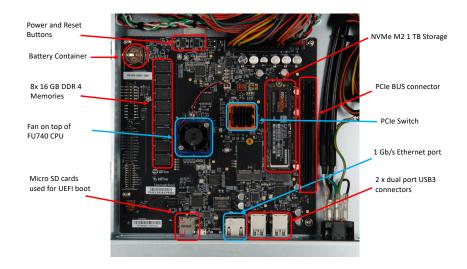

| 2.1  | The custom-built E4 RV007 Server Blade is based on a dual                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |