### Alma Mater Studiorum Università di Bologna

ARCES – Advanced Research Center on Electronic Systems for Information and Communication Technologies E. De Castro

## SPECTRUM SHAPING AND ITS APPLICATION: SPREAD-SPECTRUM CLOCK GENERATOR AND CIRCUITS FOR ULTRA WIDE BAND

Luca Antonio De Michele

TUTORS Professor **Riccardo Rovatti** Professor **Gianluca Setti**  COORDINATOR Professor Riccardo Rovatti

PHD. THESIS January, 2005 – December, 2007

PhD program in Information Technology

${\tt CYCLE} \ XX - ING\text{-}INF/01$

"Killing a fox with a hatchet has been a difficult task at any time, particularly when there was a phase error of as much as 180° between hunter and fox. Apparently both fox and peasant crossed the wall with exactly the same frequency, but the peasant wasn't able to obtain phase tracking."

From Roland E. Best, "Phase-Locked Loops: theory, design and applications", New York, Mc Graw-Hill, 1984. Picture from Wilhelm Busch, Der Fuchs (The Fox), Rascher-Verlag, Zurich, Switzerland, 1881.

## Contents

| Ι  | Sp                                                           | read Spectrum Clock Generator.                      | 3  |  |  |

|----|--------------------------------------------------------------|-----------------------------------------------------|----|--|--|

| 1  | Introduction                                                 |                                                     |    |  |  |

| 2  | Ger                                                          | eration of low-EMI clock signals                    | 13 |  |  |

|    | 2.1                                                          | Random FM Clock Modulation                          | 16 |  |  |

|    | 2.2                                                          | Conclusion                                          | 23 |  |  |

| 3  | Generation of a FM clock through a PLL                       |                                                     |    |  |  |

|    | 3.1                                                          | Phase-Locked Loop                                   | 25 |  |  |

|    | 3.2                                                          | Linear model of the PLL                             | 28 |  |  |

|    | 3.3                                                          | Frequency Modulator based on the PLL                | 31 |  |  |

|    | 3.4                                                          | Conclusion                                          | 35 |  |  |

| 4  | Har                                                          | dware implementation of a SSCG with fast modulation | 37 |  |  |

|    | 4.1                                                          | Description of the 0.35 um SSCG prototype           | 38 |  |  |

|    | 4.2                                                          | Description of the 180 nm SSCG prototype            | 45 |  |  |

|    | 4.3                                                          | Conclusion                                          | 48 |  |  |

| 5  | A SSCG with slow modulation for application to Serial ATA-II |                                                     | 51 |  |  |

|    | 5.1                                                          | Description of the SSCG prototype                   | 54 |  |  |

|    | 5.2                                                          | Conclusion                                          | 62 |  |  |

|    |                                                              |                                                     |    |  |  |

| II | II Circuits for UWB. 65                                      |                                                     |    |  |  |

| 6  | Intr                                                         | oduction                                            | 67 |  |  |

| 7  | A D                                                          | S-UWB modulator for WSN chaos-based spreading       | 77 |  |  |

|    | 7.1                                                          | System model and performance figures                | 80 |  |  |

|    | 7.2                                                          | Chaos-based generation of spreading sequences       | 84 |  |  |

|    | 7.3                                                          | Design of the Modulator                             | 85 |  |  |

### CONTENTS

|   | 7.4                                                       | Numerical Results                         | 87  |

|---|-----------------------------------------------------------|-------------------------------------------|-----|

|   | 7.5                                                       | Conclusion                                | 91  |

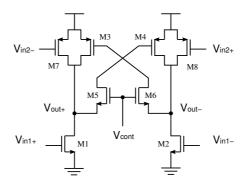

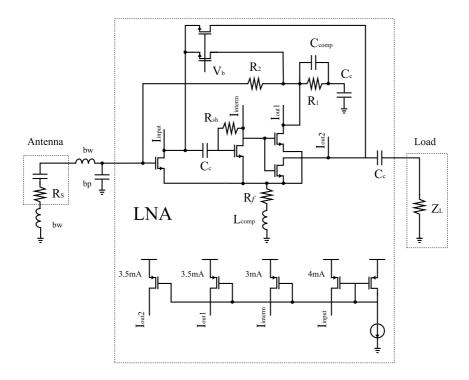

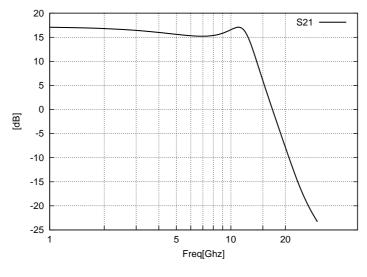

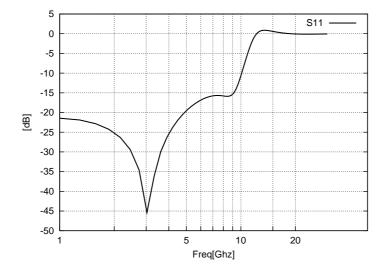

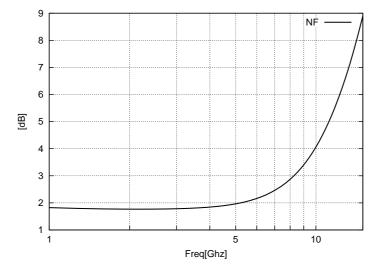

| 8 | WB CMOS 0.13 $\mu$ m LNA with Dual-Loop Negative Feedback | 93                                        |     |

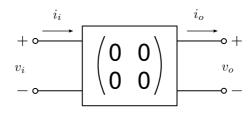

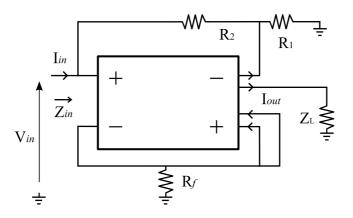

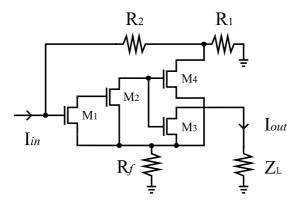

|   | 8.1                                                       | LNA Topology                              | 94  |

|   | 8.2                                                       | Nullor Design                             | 96  |

|   | 8.3                                                       | Simulation Results                        | 98  |

|   | 8.4                                                       | Conclusion                                | 101 |

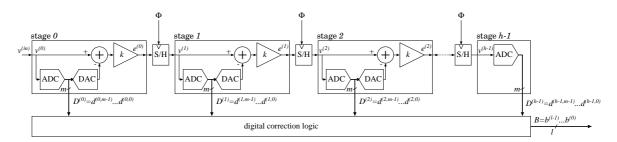

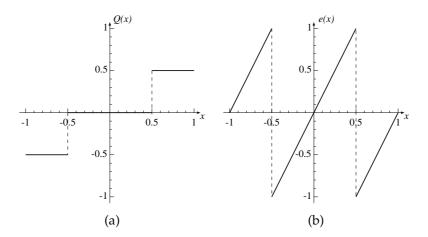

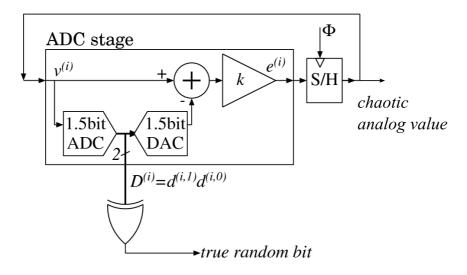

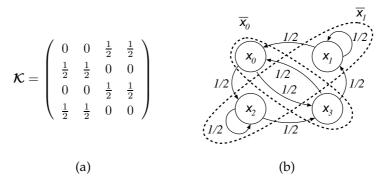

| Α | Har                                                       | dware Implementation of a Chaos-Based RNG | 103 |

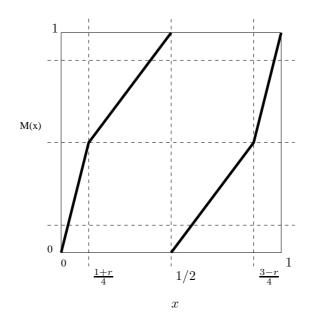

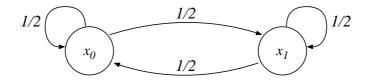

|   | A.1                                                       | Chaotic maps                              | 103 |

|   | A.2                                                       | ADC-based Chaotic Map                     | 108 |

## Preface

A *spectrum*, as spoken of in this thesis, is a frequency domain representation of a signal. Any signal can be described in the time or frequency domain, and transforms (mathematical operators, e.g. the Fourier transform) are available for conversion of descriptive functions from one domain to the other and back again. Even as an oscilloscope window in the time domain for observing signal waveforms, so is a spectrum analyzer a window in the frequency domain. The spectra presented in this work are almost all spectrum analyzer representations, generated by sweeping a filter across the band of interest and detecting the power falling within the filter as it is swept. This power level is then plotted on an oscilloscope. All spectra referred to are power spectra.

The effort in using available spectrum in a way as more productively as possible, by studying new techniques, have started long time ago, since when its importance was recognized. Already in 1959 J. P. Costas [7] concluded that "for congested-band operation, broad-band systems appear to offer a more orderly approach to the problem and a potentially higher average traffic volume than narrow-band systems."

The spectrum can be identified as a *resource* for the designer then, as well as for the manufacturer, from two complementary points of view: first, because it is a good in great demand by many different kind of applications; second, because despite its scarce availability, it may be advantageous to use more spectrum than necessary.

This is the case of Spread-Spectrum Systems, those systems in which the transmitted signal is spread over a wide frequency band, much wider, in fact, than the minimum bandwidth required to transmit the information being sent. Spread spectrum applications started with the first communicator who set up a scheduled time to send and receive messages. This scheduling may have come about through a desire to avoid heavy traffic or a desire to avoid interception by surprising the would-be interceptor. The same technique of time was adapted by radio operators, but they added a new dimension: *frequency*. The

radio operator not only could schedule his transmission for a time unknown to an interceptor but could transmit at one of many frequencies, which forced the interceptor to "find" his transmission in addition to guessing its schedule. Encoding of messages for error correction and improved time and frequency selection naturally followed.

Beside their application to telecommunications, recently spread spectrum systems have received attention by other fields of electronics, in which signal processing such as *spectrum shaping* could signify an additional degree of freedom in the performance of the systems.

This thesis is organized in two parts. In part I, it is shown how it is possible to reduce the electromagnetic interference (EMI) of a clock signal in integrated circuits (ICs) design, through a spread spectrum technique. In part II, two applications of the emerging ultra-wide band (UWB) technology are presented, both dealing with the advantages as well as with the challenges of a wide-band system.

## Part I

# Spread Spectrum Clock Generator.

## Chapter 1

## Introduction

Electromagnetic interference (EMI) is a serious and increasing form of environmental pollution, whose effects range from minor annoyances, like the crackles on broadcast reception, to potentially fatal accidents, like the corruption of safety-critical control systems. Various forms of EMI may cause electrical and electronic malfunctions, can prevent the proper use of the radio frequency spectrum, can ignite flammable or other hazardous atmospheres, and may even have a direct effect on human tissue. As electronic systems penetrate more deeply into all aspects of society, both the potential for interference effects and the potential for serious EMI-induced incidents will increase.

Starting from the first experiments in radiocommunication, it has been observed that spark gaps generate electromagnetic waves which are very rich in spectral components and which are therefore likely to cause interference in electronic systems. Nowadays, several other sources of electromagnetic emission exist, ranging from radio transmitters and radars to relays and dc electric motors, as well as digital electronic devices. As an example, mobile cellular telephones are rapidly establishing themselves, through their sheer proliferation, as a serious EMI threat: passengers boarding civil airliners, for instance, have become familiar with the announcement that the use of such devices is not permitted on board.

The task of designing systems that may be considered *compatible* from the electromagnetic point of view, has so become of great practical concern. Electromagnetic compatibility (EMC) is defined [8] as "the ability of a device, unit of equipment or system to function satisfactorily in its electromagnetic environment without introducing intolerable electromagnetic disturbances to anything in that environment".

A basic situation of interest for electromagnetic interference (EMI) analysis

can be schematically represented as electromagnetic energy emitted by a given *source*, which is transferred though a *coupling path* to an electronic device, or *vic-tim*, where it is processed, potentially giving rise to undesired behaviors. This transfer of energy may be further broken into four subgroups, with regard to the prevention of interference: *radiated* emissions from the source and *radiated* susceptibility of the victim, as well as *conducted* emissions from the source and *conducted* susceptibility of the victim. To summarize, undesired signals may be either radiated or picked up by the power cord, interconnection cables, metallic cabinets or internal circuitry of the subsystems, even though these structures or wires are not intended to carry the signals. From these considerations, three ways to prevent interference follow:

- 1. Suppress the emission at its source;

- 2. Make the coupling path as inefficient as possible;

- 3. Make the receptor less susceptible to the emission.

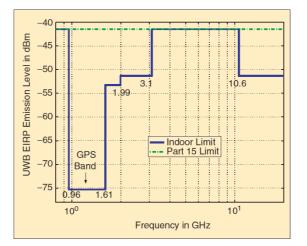

EMI effects were first analyzed with reference to military applications, especially in avionic and aerospace fields, but currently, due to the generalized adoption of electronic equipments, they are experimentally evaluated and carefully studied to find possible prevention methodologies for practically all electronic systems. Additionally, both the USA and the EU have dictated specific rules [9] for the maximum allowed radiation of devices in order to reduce electromagnetic pollution and the possibility of causing faults in nearby apparatuses. Since the regulations affect *any single* civil consumer electronic device and since producers need to be compliant to enter the market, EMI issues are obviously of great practical concern.

An interesting and important type of EMI is due to rapidly switching timing signals. In the following, two significant examples will be analyzed, such as pulse width modulated (PWM) control signals of switched-mode power converters, and synchronization signals in integrated circuits (ICs) design.

Switched-mode power converters are fundamental components in every modern electronic equipment. Being commonly controlled by a fixed frequency timing signal, switching converters result in impulsive, periodic currents and voltages components either in the circuits or in the power lines. Depending on the deployed power, such currents and voltages are typically relatively large so that they can be considered responsible for the largest part of the EMI produced by the system. The emitted and conducted EMI spectra is clearly tightly related to the spectrum of such signals, and, thanks to periodicity is

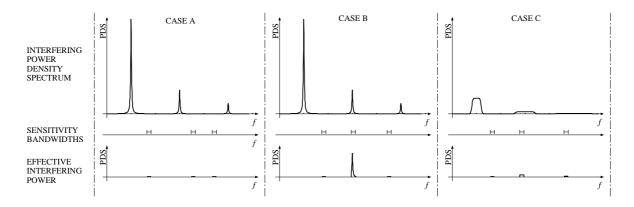

**Figure 1.1:** Relating the EMI which can effectively disturb a victim operation to the EMI PDS and the victim sensitivity bandwidths. Case A - the EMI PDS is concentrated and not overlapped with the victim sensitivity bandwidth: the victim is unaffected; case B - the EMI PDS is concentrated and overlaps the victim sensitivity bandwidth: the victim receives a large portion of the emitted power and fails; case C - the EMI PDS is spread: the victim cannot receive more than a small fraction of the emitted power and survives

composed by clusters of  $\delta$ -like terms concentrated at the master timing signal and its harmonics [10][11][12](fig. 1.1, top plot of cases A and B). On the receiver side, victims are generally sensitive to electromagnetic noise due for instance to internal resonance phenomena and ringing. In other words, most potential victims are actually quite resistant to EMI and risk failure only if the interference falls in some narrow frequency windows where they are particularly good at absorbing electromagnetic energy from the environment. Hence it is common to model potential victims assuming that they have narrow sensitivity bandwidths, as also shown in fig. 1.1 (middle plots). The number and position of such bandwidths cannot generally be known but the information that they must be narrow is already very useful. In fact, the interference that can interact with a victim is approximately the product of the source EMI power density spectrum (PDS) by the characteristic functions of the sensitivity bandwidths. If the emitted spectrum is impulsive, it is quite unlikely that its nonnull regions can intersect with the sensitivity bandwidth of a victim (case A in fig. 1.1), but if they do (case B) the victim receives a significantly large fraction of the emitted power, with a high risk of failure.

Power-supply filters, shielded cables and filtered connectors are common solutions to increase system EMC by *minimizing the coupling* between the source and the victim. The price of these solutions is both direct (packaging, wiring, manufacturability, etc.) and indirect (bulkiness, weight, marketability, product development schedule, etc.). Additionally, since the sensitivity bandwidth of the victim is unknown, there is no a-priori guarantee that their use may effectively increase EMI immunity.

As a consequence, increasing attention has recently been focused on alternative means to improve the EMC of switching power converters mixed signal circuits and boards [13], [14]. A possible alternative way to improve the EMC is the adoption of signal processing methodologies in order to shape the emitted PDS and to make it as spread as possible, thus *tuning* emissions at its source. With this (case C in fig. 1.1), the total emitted power remains unchanged and the probability of an intersection between the emitted PDS and a victim sensitivity bandwidth is actually increased. However, the amount of interference power which, in the worst case, can effectively disturb the victim is sensibly decreased. Note that the approach is coherent with EMC regulations [9][14]. In fact, the latter introduce masks under which the EMI PDS of a source (evaluated at a prescribed resolution and using prescribed methodologies) must fall. Typically masks are frequency-dependent, meaning that all the emitted harmonics are potentially dangerous. Obviously, sources which distribute their EMI power evenly over continuous ranges of frequencies have a much better chance of staying in-mask than sources which distribute their EMI in a localized fashion.

Also in the case of integrated circuits (ICs) design, signal processing based EMC enhancement techniques offer several advantages. To increase reliability and decrease system cost and size, a great effort is nowadays devoted to the implementation of ICs containing both the digital and the analog circuitry. This has a twofold consequence on the EMC design of these circuits. On one hand, the coupling path between digital and analog parts makes the latter more susceptible to interference from the digital clock signal. On the other hand, the typical solutions for increasing EMC by means of filtering and screening cannot be employed, so that the use of alternative method for interference reduction is obviously needed [15],[16],[17].

To achieve the desired result of spectrum spreading, one has to slightly modify the circuit generating the control timing signals by adding an additional modulation layer which operates by slightly anticipating or delaying its rising and falling edges, as in [13], [18] for power conversion, or in [15], [16], [17] for clock signals. Clearly, a trade-off exists in that one might want to perturb the PWM or clock signal, as much as possible to spread its spectrum, and as little as possible not to affect the system operation.

Let us also briefly comment on the characteristics of the external excitation which is needed to drive any possible additional modulation of the timing signal. It is intuitive that to break the periodicity of the timing waveform the excitation should be very irregular or noise-like. Random signals have been proposed for this task [19][20], as well as *chaos-based* signals, i.e. excitations produced by discrete-time dynamical systems showing chaotic behavior. The advantages offered by the latter, for reducing the EMI due to timing signals, over other modulation techniques, have already been discussed [21] and supported by theoretical hints from the statistical approach to dynamical system theory [21][22].

Aim of this contribution is to present a validation of such theoretical results. Part I of this dissertation deals with a signal processing-based technique of EMI reduction for clock signals in IC design, named spread-spectrum clock generation (SSCG). Three different prototypes of chaos-based SSCG are presented in all their aspects: design, simulation, and post-fabrication measurements. For all three prototypes, the author has focused on the design and realization of the *modulator*, whereas the chaos-based modulating signal, still part of the monolithic implementation of the clock generator, has been studied and designed in the context of another PhD work. The interested reader is referred to Appendix A and references therein for an in-depth examination.

Part I of this work is structured as follows:

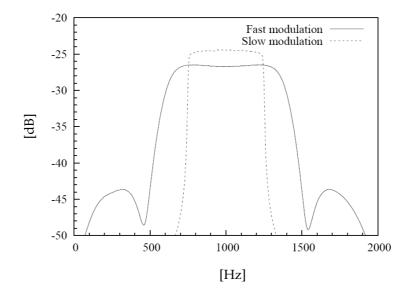

- Generation of low-EMI clock signals for digital circuits and boards is presented in chapter 2. Here the features of frequency-modulated (FM) clock signals are discussed: performance obtained by periodic and random, as well as chaotic, profiles of the modulating signals are compared. Some theorems are reported allowing to compute the PDS of chaos-based random FM clock signal, which link the statistical features of the modulating signal with the final spectrum; some measurement results confirming the superiority of chaotic techniques are also presented. Finally, a distinction between *slow* and *fast* modulation is introduced, and some results are addressed showing the best performance of the latter in terms of EMI.

- The design of a FM clock generator can be conveniently based on a phaselocked loop (PLL). PLLs are feedback systems that, if properly modified, can perform the additional function of frequency modulation, and consequently of SSCG. A brief description of such systems, as well as a mathematical linear model, is discussed in chapter 3. Some guidelines for the design of SSCG implementing either *fast* or *slow* modulation are derived in the conclusion.

- In chapter 4 the design of a PLL-based SSCG prototype aiming at reduc-

ing EMI through chaos-based fast random modulation is presented. The modulating signal is in turn given by the output of an ADC-based random number generator, obtained through a chaotic map. An established technology, such as AMS 0.35  $\mu$ m CMOS, as well as a low frequency,  $f_0 = 100$  MHz have been chosen because considered suitable for proving the theoretical results discussed in chapter 2. Measurements are presented, showing that the expected modulation is performed, and the desired spread of the clock power spectrum is achieved.

- The design of a second SSCG prototype, aiming at reducing EMI through the same chaos-based fast random modulation, is also presented in chapter 4. This SSCG has been obtained through a *scaling* to 180 nm of the first prototype, in order to operate at a higher frequency, namely  $f_0 = 3$  GHz. Adopted values for  $f_0$ , as well as for frequency deviation, are suggested by Serial Advanced Technology Attachment II (SATA-II) protocol, and discussed in chapter 5. Serial ATA specifications [23] do suggest that a spread spectrum technique should conveniently be applied to its synchronization signal, in order to perform an on-chip EMI reduction. Since the modulation requested by the same protocol should be *slow* though, this implementation only aims at proving the benefits of fast modulation is performed, as well as clock power spectrum is shaped as expected. Regrettably, the measured working frequency is lower than expected, probably due to design-time mischaracterization of parasitic effects.

- Finally in chapter 5 a third SSCG prototype is presented, which aims at being possibly applied to standard Serial ATA-II. In the realized prototype, the spreading of the clock spectrum is achieved through a chaosbased random *slow* frequency modulation, as requested by the standard, which also sets the main frequency to  $f_0 = 3$  GHz, along with the value of frequency deviation. The random modulating signal is given by the output of an ADC-based Random Number Generator, based on a chaotic map. Measurements are presented, showing as the expected modulation is performed, and the desired spread of the clock power spectrum is achieved.

The main innovative points developed by the author are here summarized:

- Two prototypes of a spread spectrum clock generator for EMI reduction which use a chaos-based fast random modulation have been implemented. They are described in chapter 4, and use an ADC-based RNG as source of randomness. These prototypes are the first that implements a frequency *binary fast* modulation (see chapter 2), which allows a maximum EMI reduction with respect to all other known modulations. See [3, 4, 5, 6].

- One prototype of a spread spectrum clock generator for EMI reduction which uses a chaos-based slow random modulation has been implemented. It is described in chapter 5, and uses an ADC-based RNG as source of randomness. This prototype is the first implementing a frequency *random* modulation to be proposed as a possible application to standard Serial ATA-II.

CHAPTER 1

12

## Chapter 2

# Generation of low-EMI clock signals

Among the different strategies for generating high-EMC clock signals, increasing attention has recently been paid to simple frequency modulation (FM), rather than on *period modulation* for example used in [18].

This is particularly due to its rather intuitive effect on the shape of the power density spectrum (PDS) of the modulated signal. Roughly speaking, the resulting effect of the FM is to scatter the power of each harmonic over a wider bandwidth, which increases linearly with frequency, so that the spreading provided by the modulation method is also linearly increasing. Obviously, the effect obtained on the spectrum strongly depends on the modulating signal characteristics, ranging from pure sinusoids [14] to optimized frequency deviation profiles based on cubic polynomials [15], and, more recently, to random signals generated by one-dimensional chaotic maps [16][17].

More formally, consider first the simple case of a pure sinusoidal signal with frequency  $f_0$ :

$$s(t) = A\sin(2\pi f_0 t)$$

modulated by one with frequency  $f_m$ , and indicate with  $\Delta f$  the amplitude of the frequency change, or *frequency deviation*. As well known from basic modulation theory [24], the spectrum of the modulated signal

$$s(t) = A\sin(2\pi f_0 t + \Delta f/f_m \sin(2\pi f_m t))$$

presents side-band harmonics at frequency  $f_0 \pm k f_m$ , k = 0, 1, ..., whose amplitudes  $A_k$  satisfy the signal power conservation constraint  $A^2 = A_0^2 + 2(A_1^2 + A_2^2 + ...)$ . Moreover, according to Carson's rule, the total power of a FM signal

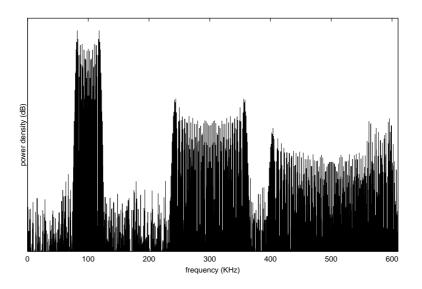

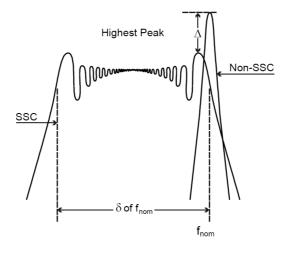

**Figure 2.1:** Power density spectrum of square waveform with  $f_0 = 100$ kHz frequency modulated by a sinusoidal signal with  $f_m = 1$ kHz and modulation index m = 20

is approximately contained inside a bandwidth of amplitude  $B_P = 2(m+1)f_m$ , where  $m = \Delta f/f_m$  is the frequency *modulation index*. Therefore, the effect of the FM is to spread the power associated to the unmodulated signal over (approximatively) the bandwidth  $[f_0 - B_P/2, f_0 + B_P/2]$ , thus reducing the harmonics magnitude at frequency  $f_0$ .

If the unmodulated signal is a square wave, then it contains harmonics itself. Similarly to the previous case, the effect of the frequency modulation is still to scatter each harmonic component into side-band harmonics. However, according to Carson's rule, and since the modulation index of the *n*-th harmonics is *n* times the modulation index of the first harmonic, the amplitude of these band is  $B_P^n = 2(nm+1)f_m \approx nB_P$  for  $m \gg 1$ . In rough terms, the general effect of FM is to spread out the power of each harmonic and the higher the harmonic number, the greater is the spread-out power. This effect is clearly identifiable in fig. 2.1 which represents the power density spectrum of a square wave with  $f_0 = 100$ kHz, frequency modulated by a sinusoidal signal with  $f_m = 1$ kHz and m = 20. Note how the critical contribution to EMI is given by the power in a neighborhood of the first harmonic.

Obviously, the FM carrier frequency  $f_0$  and the frequency deviation  $\Delta f$  must be properly chosen so that  $\phi(t) = \text{sgn}(s(t))$  can be seamlessly used for the timing of a digital apparatus. In other terms, neither  $f_0$  nor  $\Delta f$  can be regarded as tunable parameters for achieving maximal EMC improvement; in fact,  $f_0$  is fixed at the nominal clock rate, and  $\Delta f$  is superiorly bounded at ~ 5–10 % of  $f_0$

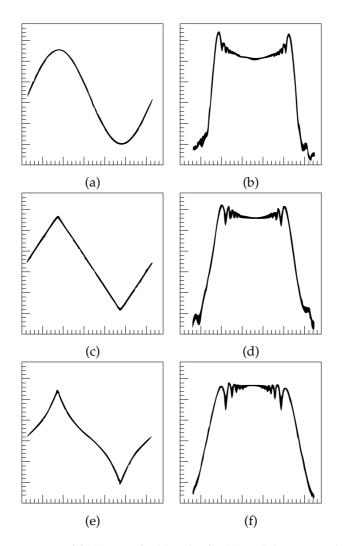

**Figure 2.2:** Comparison between *sinusoidal* (a) *triangular* (c) and *cubic* (e) modulating signals, in terms of resulting spectra, respectively (b), (d) and (f).

not to have a too irregular wave. Therefore only the features of the modulating signals can be exploited to optimize the power spectrum spreading.

A first step along this direction is reported in [15], where it is first noticed that a sinusoidal modulating waveform is not optimal for obtaining maximum attenuation of clock harmonics. This is due to the fact that the power in the spectrum of the modulated signal concentrates at those frequencies corresponding to points in the modulating waveform where the time derivative is small [24]. This effect can be clearly identifiable in fig. 2.1 where peaks are present, corresponding to frequencies where the time derivative of the sine wave is zero. On the contrary, at frequencies corresponding to the zero-

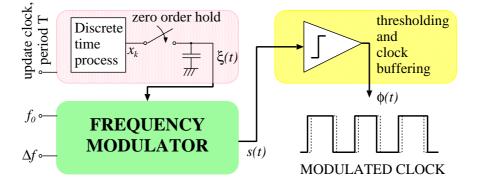

**Figure 2.3:** Architecture of the high-EMC clock synthesizer which needs to be optimized by a proper design of the signal source

crossing of the sinusoid, the amplitude of the harmonics is reduced since the time derivative of the modulating waveform is the largest. These effects can be appreciably reduced by using a properly chosen modulating signal resulting in a instantaneous frequency deviation generated by means of a suitable family of cubic polynomials, which has been optimized in order to increase the time derivative at the peaks of the modulating waveform and to reduce it at the zero crossing. With this, one can obtain a reduction of the PDS peak value of several dB with respect to sinusoidal modulating signal [15]. The comparison between the different profiles, in terms of resulting spectra, taken from [15], is shown in fig.2.2.

### 2.1 Random FM Clock Modulation

As long as the frequency deviation laws are periodic, the power is densely concentrated around specific frequencies (see also fig. 2.1) and thus the peak interference remains quite high. A way to achieve lower power densities relies on the availability of non-periodic modulating signals such as those coming from a random source or a discrete time chaotic system.

More precisely, let us refer to the block diagram of an high-EMC clock generator shown in fig. 2.3, where s(t) is the continuous-valued output of an FM modulator whose driving signal is indicated as  $\xi(t)$ , and where  $\phi(t) = \text{sgn}(s(t))$  is the candidate clock with edges which are slightly delayed or anticipated to avoid perfect periodicity.

To tackle the problem from a general point of view, let us express the mod-

ulating signal as

$$\xi(t) = \sum_{k=0}^{\infty} x_k g_{T_m}(t - kT_m)$$

where  $g_{T_m}(t)$  is the rectangular pulse which is 1 within  $[0, T_m]$  and vanishes elsewhere and  $x_k \in [-1, 1]$  is the sample generated by a suitable source at time step k. In other word, we assume that  $\xi(t)$  is produced by a discretetime process and a zero order hold operation. Let us notice that the degrees of freedom in the modulating signal are limited to the update time  $T_m$  and to the samples  $\{x_k\}$  themselves. In order to take advantage of them for EMI reduction, one needs to know how they relate to the PDS of  $\phi(t)$ .

To obtain such an analytical relationship, it is convenient to derive first the PDS of the baseband equivalent signal  $\tilde{s}(t)$  of s(t) [25]. If we indicate it as  $\Phi_{\tilde{s}\tilde{s}}(\Delta f, T_m, \{x_k\}; f)$ - to show that it is a function of the system parameters, of the statistical features of the source generating the samples  $\{x_k\}$  and of f- then it can be proven that the spectrum  $\Phi_{\phi\phi}$  of  $\phi(t)$  is built of *replicas* of  $\Phi_{\tilde{s}\tilde{s}}$ , namely

$$\Phi_{\phi\phi}(f_0, \Delta f, T_m, \{x_k\}; f) = \sum_{i=0}^{\infty} \frac{8}{(2i+1)\pi} \bigg[ \Phi_{\tilde{s}\tilde{s}}\big((2i+1)\Delta f, T_m, \{x_k\}; f - (2i+1)f_0\big) + \Phi_{\tilde{s}\tilde{s}}\big((2i+1)\Delta f, T_m, \{x_k\}; -f - (2i+1)f_0\big) \bigg]$$

(2.1)

Intuitively, this expression comes from the series expansion of a square wave into sinusoidal terms although the derivation is not completely straightforward [26].

Following consolidated methodologies [27], the computation of  $\Phi_{\tilde{s}\tilde{s}}$  can be practiced by evaluating the Fourier transform of the average autocorrelation of  $\tilde{s}(t)$ . Through a non trivial derivation, for time-shifts  $\tau > 0$  the latter can be cast as

$$\phi_{\tilde{s}\tilde{s}}(\tau) = \frac{1}{2T_m} \left( \mathbf{E} \left[ w^{x_0 \tau/T_m} \right] (T_m - \tau) g(\tau) + \int_0^{T_m} \sum_{n=1}^{\infty} g(t) g(t + \tau - nT_m) E_n(t, \tau) dt \right)$$

(2.2)

where  $w = e^{i2\pi\Delta fT_m}$  and  $E_n(t,\tau)$  is defined as

$$E_n(t,\tau) = \mathbf{E} \Big[ w^{x_0(1-t/T_m) + \sum_{j=1}^{n-1} x_j + x_n(t+\tau/T_m - n)} \Big]$$

(2.3)

from which one gets that PDS calculation passes through the computation of the expected values  $\mathbf{E}[\cdot]$  of a complex observable of the samples  $\{x_k\}$ . Although it is not yet possible to deal with (2.3) in the most general terms, we

report here some analytical results for the case of samples  $\{x_k\}$  generated by an i.i.d. random source (i.e. a source of independent and identically distributed symbols) or by a discrete time chaotic map. We will state the theorems without proof and the interested reader is referred to [28] and reference therein.

Our knowledge about the spectrum of random FM signals can be summarized with the following theorems.

**Theorem 1** (Random-FM spectrum). If s(t) is the output of an FM modulator with frequency deviation  $\Delta f$ , driven by a sequence  $\{x_k\}$  having a pulse period  $T_m$  and made of i.i.d. samples whose probability density function is  $\bar{\rho}(x)$ , then:

$$\Phi_{\tilde{s}\tilde{s}}(f) = \mathbf{E}_{x} \left[ K_{1}(x, f) \right] + Re \left( \frac{\mathbf{E}_{x}^{2} \left[ K_{2}(x, f) \right]}{1 - \mathbf{E}_{x} \left[ K_{3}(x, f) \right]} \right)$$

(2.4)

where

$$K_{1}(x,f) = \frac{1}{2}T_{m}sinc^{2}(\pi T_{m}(f - \Delta f x))$$

$$K_{2}(x,f) = j\frac{e^{-j2\pi T(f - \Delta f x)} - 1}{2\pi\sqrt{T_{m}}(f - \Delta f x)}$$

$$K_{3}(x,f) = e^{-j2\pi T(f - \Delta f x)}$$

(2.5)

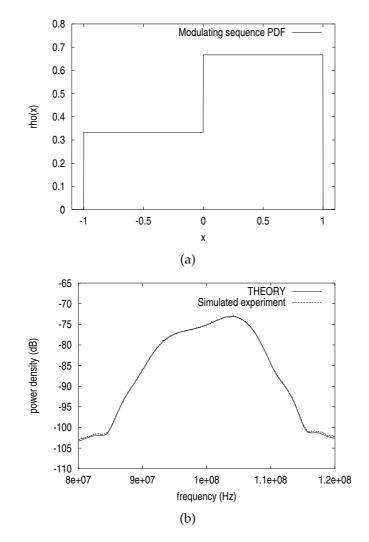

Theorem 1 is a general analysis tool where equation (2.4) can conveniently take an integral form reminding that the statistical independence of  $\{x_k\}$  implies that  $\mathbf{E}_x[f(x)] = \int f(x)\bar{\rho}(x) dx$ . The excellent conformance to numerical results can be remarked by an example. Suppose that a random modulating sequence, whose probability density function is as depicted in fig. 2.4 (a), is fed to an FM modulator with  $f_0 = 100$  MHz and  $\Delta f = 8.5$  MHz at a sample rate of 8.5 Msample/s. Figure 2.4 (b) shows the predicted spectrum and the one obtained by numerical simulations, almost completely superimposed.

As shown in the next subsection, a further analytical result can be obtained under the assumption  $T_m \to \infty$ . Following an established approach [29], one shall refer to the large- $T_m$  case as *slow* modulation, and to the opposite, small- $T_m$ , as *fast* modulation. In the following, the two cases will be studied separately. Notice that in fact it would be more proper to distinguish among large and small modulation index. The confusion arises from the fact already observed that both  $f_0$  and  $\Delta f$  are usually set by applications, thus making the two parameters  $T_m$  and m inter-independent.

#### 2.1.1 Case of *slow* modulation

**Theorem 2** (Slow-modulation Random-FM spectrum). If s(t) is the output of an FM modulator with frequency deviation  $\Delta f$ , driven by a sequence  $\{x_k\}$  having a pulse

**Figure 2.4:** Application example for theorem 1. (a) modulating sequence PDF; (b) correspondent modulated signal spectrum.

period  $T_m$ , made of samples which are now not necessarily i.i.d., with a probability density function  $\bar{\rho}(x)$ , then:

$$\lim_{T_m \to \infty} \Phi_{\tilde{s}\tilde{s}}(f) = \frac{1}{2\Delta f} \bar{\rho}\left(\frac{f}{\Delta f}\right)$$

(2.6)

Theorem 2 is a specialized analysis tool, for the slow modulation case. The advantage of specialization is twofold:

1. The much easier formulation of  $\Phi_{\tilde{s}\tilde{s}}(f)$  as a function of  $\bar{\rho}$ . Note how a slow modulation implies that the modulated signal PDS is *shaped* as  $\bar{\rho}$ . This result can also be intuitively accepted: if  $T_m$  tends to infinity in fact,

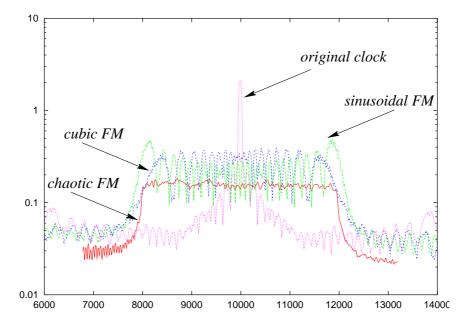

**Figure 2.5:** Experimental comparison between different clock spreading methods.  $f_0 = 10 \text{ kHz}$ ,  $\Delta f = 2 \text{ kHz}$  and  $f_m = 50 \text{ Hz}$ . The resolution bandwidth of the 35670A digital spectrum analyzer has been set to 8 Hz.

each instantaneous frequency of the modulated signal is hold for a time t, which in turn tends to infinity; this in the PDS is represented as a line. The contribution of each line to the whole PDS then, shall be weighted by the *continuous* probability associated to the symbol  $\{x_k\}$  corresponding to the line itself.

It is worth noticing that this formulation is easily reversible, permitting to determine  $\bar{\rho}$  in order to deliver a modulated signal conforming to a given spectrum. In other words, this theorem is also a synthesis tool [28]: if  $\bar{\rho}$  is in fact shaped *uniformly*, then the modulated signal PDS will be *flat*, as can be observed in fig. 2.5.

2. The hypothesis that the source of symbols is "not necessarily" i.i.d. allows to choose as source of randomness a *chaotic* system [28] with proper characteristics, as described in Appendix A.

Figure 2.5 plots the measured PDS of the clock signals (in the neighborhood of the fundamental harmonic) modulated using the chaos-based technique compared with a non-modulated clock, one modulated using a sinusoidal signal, or an optimal periodic profile [15]. In all cases,  $f_0 = 10$  kHz,  $\Delta f = 2$  kHz and  $f_m = 50$  Hz have been assumed and a tent map implemented with off-the-shelf components has been used as simple chaos generator. Mea-

surement have been performed using a digital spectrum analyzer, whose resolution bandwidth was set to 8 Hz. From direct visual inspection one gets that a non-negligible improvement can be obtained with the chaos-based modulation technique. More quantitatively, the achieved attenuation, i.e. the difference between the peak of the unperturbed spectrum and the peak of the spread spectrum, is of  $\approx 5$ dB for a sinusoidal modulating signal,  $\approx 8$ dB for the method considered in [15] and of  $\approx 15$ dB when chaos-based FM is employed.

### 2.1.2 Case of *fast* modulation

There is no theorem specialized for the case of fast modulation. As already observed, though, the modulating signal has got two degrees of freedom, namely the update time  $T_m$  and the samples  $\{x_k\}$  themselves: the case of *slow* random modulation fixes the first one to infinity, and gets a result for the PDS of  $\phi(t)$  depending on the statistic of the samples  $\{x_k\}$ .

A *fast* random modulation has been proposed in [30], wherein the fixed degree of freedom is on the contrary  $\{x_k\}$ , thus expecting the PDS of  $\phi(t)$  to be dependent on  $T_m$ , or equivalently m. In particular, we get:

$$\bar{\rho}(x) = \frac{1}{2}\delta(x+1) + \frac{1}{2}\delta(x-1)$$

(2.7)

that is, the symbols  $\{x_k\}$  can only assume two discrete values (-1 and +1), each one with identical probability p = 1/2. This kind of modulation is called *binary fast* random modulation.

As a consequence, also the instantaneous output frequency can only assume the two values  $f_0 - \Delta f$  and  $f_0 + \Delta f$ . Now, if  $T_m$  was large, one would expect a corresponding PDS of  $\phi(t)$  shaped as two peaks on the edge of the spread spectrum. On the contrary, being  $T_m$  a free degree of freedom, it is possible to obtain, by means of numerical optimization, a value of *m* that optimizes the shape of the PDS [30].

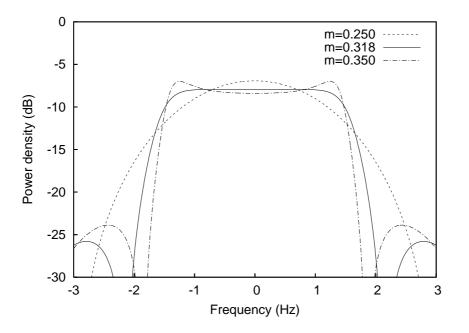

This is obtained, given the exact expression for  $\Phi_{\tilde{s}\tilde{s}}(f)$ , substituting equation 2.7 in 2.4 and looking for a numerical optimum for m: as a result, peaks in the PDS are minimized for the value:

$$m = \Delta f T_m = m_{\text{opt}} \simeq 0.318;$$

whereas lower values of *m* cause the PDS to increase around 0, and higher values increase it around  $f = \pm \Delta f$  (Figure 2.6) (this last result according to slow modulation case).

As already mentioned, each harmonic is described by a different modulation index: as a consequence, this optimization can be achieved *only* on one

**Figure 2.6:** Normalized ( $\Delta f = 1$ ) low-pass equivalent for PDS in the binary frequency modulation for value of the modulation index around  $m_{opt}$

single harmonic; in particular, the optimum modulation index is:

$$\begin{split} m_{1_{

m opt}} &= m_{

m opt} = 0.318, & 1^{st} \mbox{ harmonic} \ m_{3_{

m opt}} &= 3m_{1_{

m opt}} = 0.954, & 3^{rd} \mbox{ harmonic} \ m_{5_{

m opt}} &= 5m_{1_{

m opt}} = 1.59, & 5^{th} \mbox{ harmonic} \ \dots & \dots & \dots \end{split}$$

Since the power content of the fundamental tone is much higher than that of all the other harmonics, and so are the corresponding peaks, the best result in overall peak reduction is achieved when the modulation index is optimized for the fundamental tone, i.e.  $m = m_{opt}$ .

Since *fast* modulation allows to gain 3 further dB on the fundamental tone, with respect to *slow* modulation, it can be considered the best choice for EMI reduction among all known modulation techniques [30].

It is worth noticing that in this case the condition that the source outputs binary symbols are i.i.d. is fundamental, descending from Theorem 1: on the another hand, symbols outputted by chaotic systems are not i.i.d, because *not independent* by definition. It has been proven, though, that by a proper quantization of the output of a chaotic system with certain characteristics, as described in Appendix A, it is still possible to obtain a source of i.i.d random symbols.

**Figure 2.7:** Comparison between fast and slow modulation; center-spread frequency  $f_0 = 1$  kHz,  $\Delta f = 250$  Hz and m = 454 for the slow modulation, m = 0.318 for the fast modulation.

### 2.2 Conclusion

Contrarily to conventional methodologies, signal processing methods are not about reducing the emitter energy of an interferer, but their aim is to affect the *way* in which the energy is emitted, to try to make it less dangerous for potential victims.

Clearly, signal processing has its greatest potential on those systems where the EMI is initially very much localized in frequency, so that the spreading action can make a big difference. On the case of digital clocked devices, where a timing waveform with a periodic structure is the dominant cause of the EMI issues, the signal processing approach is practiced by slightly altering the timing waveforms, through the addition of suitable modulation layers, in particular a frequency modulation.

The choice of modulating waveforms is fundamental; aperiodic waveforms have been proven to be superior to periodic ones. Since aperiodic waveforms are best described through their statistical features, their statistics have been related to the final emission spectrum and viceversa. In all cases there is evidence that the use of chaos-based random-FM modulations can reduce the peak values in the emitted PDS more than other published or patented signal processing methods, with a gain of 3 dB in the case of fast modulation with respect to the case of slow modulation [30] (fig.2.7).

It is worth noticing that when the modulating signal is slowly varying with

respect to the modulated one (slow modulation), a EMC norm compliant signal may still cause victim system to fail. Its output frequency in fact is maintained unaltered for a considerable period of time, thus an amount of energy sufficient to cause victim system failure may be transferred. If this happens, since FM spreads the signal frequency over a wider bandwidth, slow modulation may even cause an *increase* of interference, by enlarging the range of potential victims.

To conclude, fast modulation has to be considered preferable from the EMI point of view; it also provides the best peak reduction for the  $1^{st}$  harmonic with respect to all other known modulations.

## Chapter 3

# Generation of a FM clock through a PLL

The DESIGN of a frequency modulated (FM) clock generator can be conveniently based on a phase-locked loop (PLL). PLLs are feedback systems that were introduced to allow operations such as jitter reduction and frequency multiplication: if they are properly modified, they can perform the additional function of frequency modulation, and consequently its special case, that is spread-spectrum clock generation (SSCG). After a brief description of such systems, a mathematical linear model is discussed in this chapter; for an in-depth analysis of phase-locked systems the reader is referred to [31]. Some guidelines for the design of SSCG implementing either *slow* or *fast* modulation are derived in the conclusion.

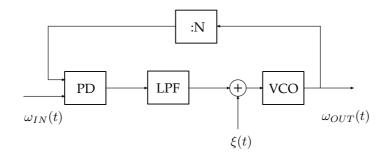

### 3.1 Phase-Locked Loop

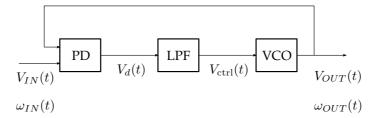

As every feedback system, the phase-locked loop (PLL) is a circuit that causes a particular system to track with another one. More precisely, the PLL is a circuit synchronizing an output signal (generated by an oscillator) with a reference or input signal, in frequency as well as in phase. In the synchronized state the phase error between the oscillator's output signal and the reference signal is zero, or remains constant. If a phase error builds up, a control mechanism acts on the oscillator in such a way that the phase error is again reduced to a minimum. In such a control system the phase of the output signal is actually *locked* to the phase of the reference signal: this is why it is referred to as a *phase-locked loop*. Every PLL consists of three main blocks: a *phase detector (PD), a*

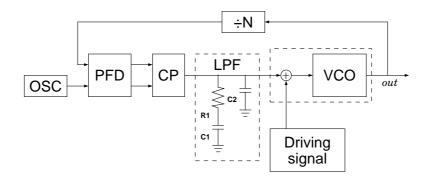

Figure 3.1: Phase-locked Loop.

*low-pass filter (LPF)* and a *voltage controlled oscillator (VCO)*. Referring to fig. 3.1, the operating principle of the PLL is described mathematically in the following.

The VCO oscillates at an angular frequency  $\omega_{OUT}$  which is determined by the output signal  $V_{\text{ctrl}}(t)$  of the low-pass filter, so that:

$$\omega_{OUT}(t) = \omega_0 + K_{VCO} V_{\rm ctrl}(t)$$

where  $\omega_0$  is the center angular frequency of the VCO and  $K_{VCO}$  is the VCO gain in *rad*  $s^{-1}V^{-1}$ . The PD compares the phase of the output signal with the phase of the reference signal and develops an output signal  $V_d(t)$  that is approximately proportional to the phase error  $\Delta \phi$ , at least within a limited range of the latter:

$$V_d(t) = K_d \Delta \phi$$

where  $K_d$  represents the gain of the PD. The output signal  $V_d(t)$  of the PD consists of a dc component and a superimposed ac component: the latter is undesired, hence it is canceled by the low-pass filter.

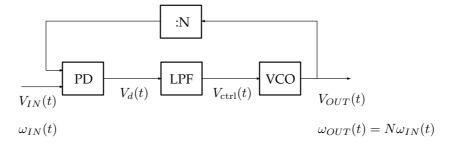

Assume now that the frequency of the input signal is changed by the amount  $\Delta \omega$ . The phase of the input signal then starts leading the phase of the output signal: a phase error is built up and increases with time. The PD develops a signal  $V_d(t)$ , which also increases with time. With a delay given by the loop filter,  $V_{ctrl}(t)$  will also rise. This causes the VCO to increase its frequency. The phase error becomes smaller, and after some settling time the VCO will oscillate at a frequency that is exactly the frequency of the input signal, thus  $\omega_{OUT} = \omega_{IN}$ . Depending on the type of circuits used, the final phase error will have been reduced to zero or to a finite value. In most applications, a *divider* block is added in the feedback loop (fig. 3.2). Assuming that it divides the number of oscillations in a given time interval by a factor N, the frequency of the VCO output signal is forced to be N times the reference frequency, thus  $\omega_{OUT} = N\omega_{IN}$ . It is worth noticing that if the divider ratio N is made programmable, it is possible to synthesize the output frequency of the VCO, given one input frequency.

Figure 3.2: Phase-locked Loop with a divider.

One of the most important characteristics of the PLL is its ability to suppress noise superimposed on its input signal. If the input signal of the PLL is corrupted by noise, in fact, the PD tries to measure the phase error between input and output signals. The noise at the input causes the zero crossings of the input signal to be advanced or delayed in a stochastic manner: this causes the PD output signal to jitter around an average value. If the corner frequency of the loop filter is low enough, almost *no noise* will be noticeable in the signal  $V_{\rm ctrl}$ , and the VCO will operate in such a way that the phase of the output signal is equal to the *average* phase of the input signal. Phase-locked systems have many possible applications, ranging from jitter reduction, skew suppression, clock recovery, etc. to frequency synthesis in wireless and RF applications, high-precision clock generation and the application.

Referring to fig. 3.2, a high precision clock generator can be obtained if the square-wave input signal is given by a low-frequency quartz, with constant frequency  $\omega_{IN}$ . The PLL then multiplies by *N* the frequency of the input signal, and also suppresses the jitter introduced by the high-frequency VCO: thus originates a high-frequency square-wave which carries the same characteristics of accuracy and stability of the quartz.

Moreover, a FM clock generator can be obtained from a standard clock generator by properly adding a modulating signal in the scheme; the PLL will continue to perform its operation as described so far, plus the output frequency will somehow also depend on the modulating signal.

In order to study the possible realization of a SSCG through a PLL, in the following a mathematical model of the PLL will be analyzed.

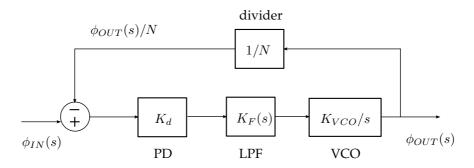

Figure 3.3: Mathematical model for the locked state of the PLL.

### 3.2 Linear model of the PLL

Phase-locked systems exhibit nonlinear behavior at least during part of their operation (e.g. transients), thus requiring time-domain analysis in almost all applications. However, in the steady state and during slow transients, it's extremely helpful to study its response in the frequency domain as well. This is especially true if the application imposes certain constraints on the output spectrum. In this work, frequency analysis has been considered sufficient to provide guidelines for the design of a SSCG.

So, if we assume that the PLL has locked and stays locked for the near future, we can develop a *linear* mathematical model for the system [31] in the Laplace domain, which is used to calculate a frequency-transfer function H(s) that relates the frequency of the input signal to the frequency of the output signal (fig. 3.3).

To get an expression for H(s) we must know the transfer functions of the individual building blocks.

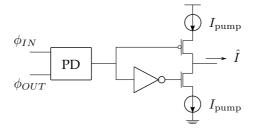

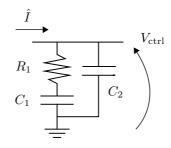

In the following, analysis will limit to the case of interest of a *mixed-signal* PLL, i.e. composed of both analog and digital circuits, which deals with clock signals, thus *square-waves*. The PD, shown in fig. 3.4, is of the type that delivers a current output instead of a voltage output: it is said to have a *charge pump* (*CP*) output. The loop filter considered, shown in fig 3.5, is a passive second-order filter.

Let us proceed then, to derive the transfer function of the system.

From fig. 3.4, PD and CP can be modeled as a single component, which senses the phase difference Δφ between the two inputs of the PD, and outputs a series of high frequency pulses of intensity ±*I*<sub>pump</sub> and duty-cycle proportional to Δφ; a phase difference of Δφ = 2π results in an average output current *Î* = *I*<sub>pump</sub>, while a phase difference of Δφ = −2π

Figure 3.4: Phase detector with charge pump output.

Figure 3.5: Second-order passive low-pass filter.

results in  $\hat{I} = -I_{pump}$ . Analytically:

$$\hat{I} = \frac{I_{\text{pump}}}{2\pi} \Delta \phi = K_d \Delta \phi$$

Obviously, the phase difference is bounded in the interval  $[-2\pi, 2\pi]$ .

• For proper operation, LPF cut-off frequency must be much lower (typically two or more order of magnitude) than the frequency of the pulses coming from the CP (i.e. the input frequency); as a consequence, one can consider that at the input of the filter only the average value of  $\hat{I}$  is present, that is:

$$\hat{I}(s) = K_d \Delta \phi(s)$$

Referring to Figure 3.5, the filter output voltage is:

$$V_{\text{ctrl}}(s) = \frac{1 + sT_2}{sT_1(1 + sT_3)}\hat{I}(s) = K_F(s)\hat{I}(s)$$

where

$$T_1 = C1 + C2$$

$$T_2 = R1 C1$$

$$T_3 = R1 \frac{C1 C2}{C1 + C2}$$

• The VCO in turn converts this voltage into an output angular frequency:

$$\omega_{\rm OUT}\left(s\right) = K_{\rm VCO}V_{\rm ctrl}\left(s\right)$$

Observing that the phase  $\phi(t)$  of a signal is just the integral of the instantaneous frequency  $\omega(t)$  in time domain, it holds:

$$\phi_{\text{OUT}}(s) = \frac{\omega_{\text{OUT}}(s)}{s} = \frac{K_{\text{VCO}}}{s} V_{\text{ctrl}}(s)$$

If we now consider the *open-loop transfer function* H<sub>0</sub> (s), from Δφ to φ<sub>OUT</sub>, we get:

$$H_{0}(s) = \frac{\phi_{OUT}(s)}{\Delta\phi(s)} = K_{d}K_{F}(s)\frac{K_{VCO}}{s} = \frac{I_{\text{pump}}}{2\pi}\frac{1+sT_{2}}{sT_{1}(1+sT_{3})}\frac{K_{\text{VCO}}}{s}$$

Observing that  $\Delta \phi = \phi_{IN} - \phi_{OUT}/N$ , *N* being the divider ratio, the correspondent *closed-loop transfer function* from  $\omega_{IN}$  to  $\omega_{OUT}$  is:

$$H_{1}(s) = \frac{\omega_{\text{OUT}}(s)}{\omega_{\text{IN}}(s)} = \frac{\phi_{\text{OUT}}(s)}{\phi_{\text{IN}}(s)} = \frac{H_{0}(s)}{1 + \frac{H_{0}(s)}{N}}$$

(3.1)

• It is very common to consider  $C2 \ll C1$ , thus  $T_3 \simeq 0$  and

$$K_F(s) \approx \frac{1 + sT_2}{sT_1}$$

Under this assumption, equation (3.1) can be recast as

$$H_1(s) = N \frac{\omega_n^2 (1 + sT_2)}{s^2 + 2\omega_n \zeta s + \omega_n^2}$$

(3.2)

with

$$\omega_n = \sqrt{\frac{I_{\text{pump}} K_{VCO}}{2\pi N T_1}}$$

$$\zeta = \frac{\omega_n T_2}{2}$$

which is the standard form used in control theory [32] for a two poles transfer function, where  $\omega_n$  is the natural frequency and  $\zeta$  the dumping factor.

$H_1(s)$  presents a double pole in  $\omega_n$  and a zero in  $1/T_2$ . For proper values of its parameters, the system is designed to be *stable* [31] and exhibits a low-pass behavior, with cut-off frequency  $\omega_n$  and base-band gain N, as expected. This means that the second-order PLL is able to track for phase and frequency variations of the reference signal, as long as this variations remain within an angular frequency band roughly between zero and  $\omega_n$ . Equivalently, it is able to track for variations of the output signal, in case the reference signal is kept constant.

The time the PLL takes to track for a slow variation is defined as *lock-in* time, and can be in general calculated as:  $T_L \simeq 2\pi/\omega_n$ .

#### 3.3 Frequency Modulator based on the PLL

The PLL-based SSCGs that appear in Literature can be roughly divided into three categories: those which directly add a signal at the input of the VCO [33][34], those which varies the divider ratio N [35][36][37][38], and those which combine the multi-phase outputs of the clock source and the special digital processing circuits to achieve the spread spectrum function [39][40][41]. Among these different techniques, in the following we will focus on the first two cases:

- 1. modulation obtained by adding a signal to the input of the VCO;

- 2. modulation obtained by varying the divider ratio *N*.

#### 3.3.1 Modulated signal added at the input of the VCO

Let us indicate with  $\xi(t)$  a driving signal added at the input of the VCO, and with  $\xi(s)$  its Laplace transform. The VCO converts the sum of this driving signal and  $V_{\text{ctrl}}(s)$  into an output angular frequency:

$$\omega_{\text{OUT}}\left(s\right) = K_{\text{VCO}}\left(V_{\text{ctrl}}\left(s\right) + \xi\left(s\right)\right)$$

and it follows:

$$\phi_{\text{OUT}}\left(s\right) = \frac{\omega_{\text{OUT}}\left(s\right)}{s} = \frac{K_{\text{VCO}}}{s}\left(V_{\text{ctrl}}\left(s\right) + \xi\left(s\right)\right)$$

For the *closed-loop transfer function* between  $\omega_{OUT}(s)$  and  $\xi(s)$ , one gets:

$$H_{2}(s) = \frac{\omega_{\text{OUT}}(s)}{\xi(s)} = \frac{1}{s} \frac{\phi_{\text{OUT}}(s)}{\xi(s)} = s \frac{1}{1 + \frac{H_{0}(s)}{N}} \frac{K_{\text{VCO}}}{s}$$

thus, similarly to what observed for equation 3.1:

$$H_2(s) = \frac{s^2/\omega_n^2}{s^2 + 2\omega_n \zeta s + \omega_n^2}$$

This transfer function presents a double zero in the origin, and a double pole at  $\omega_n$ ; this is a high-pass transfer function, with cut-off frequency equal to  $\omega_n$ : it is indeed the transfer function "seen" from the driving signal at the input of the VCO.

Let us consider two significant cases.

1. If the (angular) frequency of the driving signal  $\xi(t)$  is much lower than the cut-off frequency of the PLL, that is:

$$2\pi f_m \ll \omega_n$$

Figure 3.6: PLL-based SSCG with fast modulation.

then the PLL loop is able to *track* this  $\xi(t)$ , thus minimizing phase and frequency errors between this signal and the reference clock. This case is very similar to the one of clock generator without any modulation, wherein some low-frequency jitter is introduced by the VCO and the PLL loop takes charge of reducing it to a minimum. To conclude, under this condition, no modulation is performed.

2. On the contrary, if the (angular) frequency of the driving signal  $\xi(t)$  is much higher than the cut-off frequency of the PLL, that is:

$$2\pi f_m \gg \omega_n$$

then  $\xi(t)$  cannot be *tracked* by the PLL loop, due to the low-pass nature of the loop. The high-frequency "perturbation"  $\xi(t)$ , in fact, enters the PD, where it is compared with the low-frequency reference, thus originating a high-frequency error, which does not pass through the filter. As a consequence, as in an open-loop system, the modulating signal ends up driving the VCO *directly*, leaving to the feedback loop the mere function of tracking the *average* output frequency, thus setting the center-spread frequency equal to *N* times the input reference clock.

In time-domain, it means that the PLL lock-in time  $T_L$  is much longer than the period  $T_m$  of  $\xi(t)$ : then, every time  $\xi(t)$  varies, the PLL starts the process of tracking, but it is not able to finish it before a new variation occurs. To conclude, under this condition, a *fast* modulation is performed, as defined in chapter 2.

From both these considerations, a SSCG with fast modulation, using the scheme shown in fig.3.6, has been implemented; its output frequency can be expressed as  $\omega_{OUT}(t) = N\omega_{IN}(t) + K_{VCO}\xi(s)$ . Circuital description, along with simulations and post-fabrication measurements of the SSCG can be found in chapter 4.

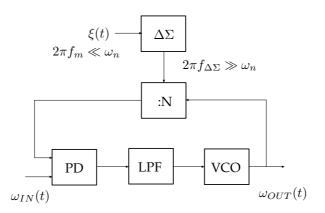

## 3.3.2 Modulated signal driving the input of the programmable divider

Consider now the case of a driving signal which acts on the value of the divider ratio N, at a rate  $f_m$ . Let us indicate with N(t) the varying divider ratio and with N(s) its Laplace transform. The *closed-loop transfer function* between  $\omega_{\text{OUT}}(s)$  and N(s) can be calculated from equation 3.2 as:

$$H_3(s) = \frac{\omega_{\text{OUT}}(s)}{N(s)} = \omega_{\text{IN}}(s) \frac{\omega_n^2 (1 + sT_2)}{s^2 + 2\omega_n \zeta s + \omega_n^2}$$

$H_3(s)$  is the product of two terms of which:

- the first one can be simply considered as the Laplace transform of the frequency of a constant frequency square-wave, (the one given by the reference clock), that is equal to a constant value.

- the second one is the same as in H<sub>1</sub>(s), thus mainly characterized by a low-pass nature with a double pole in ω<sub>n</sub>.

It follows that  $H_3(s)$ , similarly to  $H_1(s)$ , is a transfer function with a low-pass nature, with a cut-off frequency equal to  $\omega_n$ . Again, two significant cases will be considered.

1. If the (angular) frequency of the driving signal  $\xi(t)$  is much lower than the cut-off frequency of the PLL, that is:

$$2\pi f_m \ll \omega_n$$

then the PLL loop can *track* the varying value of the divider ratio. Then, since the period of change  $T_m$  of N results much longer than the lock-in time, every time the value of N is changed, the output frequency in turn switches to a different value in a negligible time. To conclude, under this condition, a *slow* modulation is performed, as defined in chapter 2.

2. On the contrary, if the (angular) frequency of the driving signal  $\xi(t)$  is much higher than the cut-off frequency of the PLL, that is:

$$2\pi f_m \gg \omega_n$$

then  $\xi(t)$  cannot be *tracked* by the PLL loop, due to the low-pass nature of the loop. As a consequence, the feedback loop can only track the *average* division ratio.

Figure 3.7: PLL-based SSCG with slow modulation.

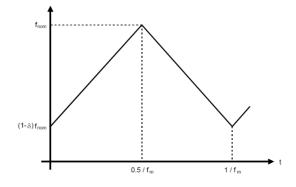

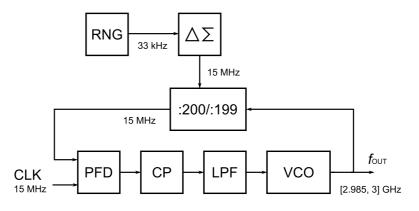

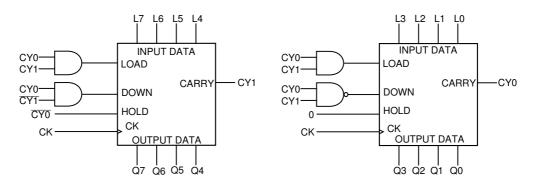

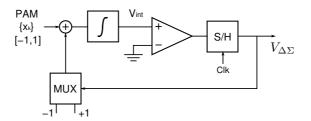

From both these considerations, a SSCG with slow modulation, using the scheme shown in fig. 3.7, has been implemented. Its circuital description, along with simulations and post-fabrication measurements can be found in chapter 5; in the following the principles of its operation will be discussed. As indicated in fig. 3.7, the frequency  $f_m$  of the modulating signal  $\xi(t)$  is such that  $2\pi f_m \ll \omega_n$ : consequently, the performed modulation is *slow*. One can notice, though, that  $\xi(t)$  does not drive directly the divider ratio N: it drives instead the input of a  $\Delta\Sigma$  converter. The  $\Delta\Sigma$  circuit is an over-sampling A/D converter that transforms each analog value at its input in a sequence of "1s" and "0s"; the length of such a sequence depends on the  $\Delta\Sigma$  Over-Sampling Ratio (OSR), that is:

$$OSR = \frac{f_{\Delta\Sigma}}{f_m}$$

If this OSR is sufficiently high, i.e. if the sequence of "1s" and "0s" in turn drives the division ratio N with a frequency  $f_{\Delta\Sigma}$  such that  $2\pi f_{\Delta\Sigma} \gg \omega_n$ , then the feedback loop can only track the *average* division ratio.

The SSCG shown in fig. 3.7 is said to implement a (slow) modulation that is based on "fractional synthesis" [31]: the divider can provide only two possible ratios,  $N_{min}$  and  $N_{max}$ , but the whole range of frequency within  $\omega_{OUT} = N_{min}\omega_{IN}$  and  $\omega_{OUT} = N_{max}\omega_{IN}$  can be generated by inputting into the divider a sequence which originates a proper *average* value for N. Let us explain this mechanism through some examples; the values for  $N_{min}$  and  $N_{max}$  will be set to 199 and 200, respectively.

Imagine to input the periodic sequence of bits "10101010..." to the programming input of the divider, and say input "1" corresponds to N = 200, and input "0" corresponds to N = 199. Let us assume as well that the initial value for the output frequency is  $\omega_{OUT} = 199\omega_{IN}$ . Then, at the occurrence of the first "'1", the feedback loop starts the process of tracking, trying to adapt the output frequency to the value  $\omega_{OUT} = 200\omega_{IN}$ ; before it is able to finish it, though, a "0" occurs, thus setting *N* back to 199. Again the feedback loop tries to adapt the output frequency to  $\omega_{OUT} = 199\omega_{IN}$ , but it cannot get to this value because interrupted by a further variation. It is easy to conclude that the mentioned sequence of bits at the input of the divider will originate an actual output frequency of

$$\omega_{\rm OUT} = \frac{N_{min} + N_{max}}{2} \omega_{\rm IN} = \frac{200 + 199}{2} \omega_{\rm IN} = 199.5 \omega_{\rm IN}$$

This concept can be extended to get any other value of N within the interval  $[N_{min}, N_{max}]$ , by simply inputting a different sequence of bits into the divider, which corresponds to a sequence of division ratios whose average value is the one desired. For instance, the periodic sequence "100100100..." will result in a division ratio of

$$N = \frac{200 + 199 + 199}{3} = 199.333$$

More in general, for *any* sequence, even *non-periodic*, the actual value of *N* depends:

- in first approximation, on the ratio between occurrences of "1s" and occurrences of "0s", i.e. the value of N is the weighted sum of "1s" and "0s" occurring in the sequence. For instance, the sequence with period "11000" and the one with period "01010" give rise to the same average value of N;

- due to the low-pass nature of the system, though, also on the *position* of the bits in the sequence: the higher the rate of switch from a value to a different one, the best the value of *N* is *averaged* by the loop; thus, the example sequence with period "01010" gives better results than the one with period "11000".

#### 3.4 Conclusion

PLLs-based frequency modulation have been analyzed, and significant guidelines have been derived and used to implement two different types of SSCGs. In chapter 4, two prototypes of SSCG with *fast* modulation, whereas in chapter 5 one prototype of SSCG with *slow* modulation, will be presented.

CHAPTER 3

36

## Chapter 4

# Hardware implementation of a SSCG with fast modulation

**T**<sup>N</sup> THIS CHAPTER two prototypes of Spread-Spectrum Clock Generators (SS-CGs), designed to implement a *fast* binary modulation are described. For both prototypes:

- the modulation parameters have been chosen so that the modulation index m is equal to its optimum value m = 0.318: this means that a *flat* shape for the first harmonic of the clock is expected (see chapter 2);

- the modulating signal is a PAM random signal, as expected by random modulation (see chapter 2), whose time-symbol is *T<sub>m</sub>*.

- the modulator is based on a standard Phase-Locked Loop (PLL), wherein the modulation is obtained by adding a signal to the input of the VCO; (see chapter 3);

In both implementations, the symbols of the modulating signal comes from the output of an embedded ADC-based Random Number Generator. This circuit is based on a *chaotic map*, whose implementation has been part of another PhD work; a brief description of its working principles and hardware realization can be found in Appendix A. Remember that fast modulation requires a PAM driving signal with i.i.d. binary values, which can be obtained by the quantization of the output of a chaotic map (chapter 2).

Furthermore, since the power density spectrum of a PAM signal is composed of adjacent lobes, the first of which ranging from 0 to  $f_m$ , it can be intuitively accepted that the consideration derived in chapter 3 about the conditions to obtain a fast or a slow modulation can be extended to this case. For this

| Center-Spread Frequency, $f_0$                    | 100 MHz   |

|---------------------------------------------------|-----------|

| Spread-Spectrum Modulation frequency, $f_m$       | 10 Mbit/s |

| Spread-Spectrum Modulation Deviation , $\Delta f$ | 3.18 MHz  |

Table 4.1: Specifications of 0.35  $\mu$ m SSCG.

reason, in the following we will continue to refer to  $f_m = 1/T_m$  as the *frequency* of the modulating signal.

#### 4.1 Description of the 0.35 $\mu$ m SSCG prototype

The first SSCG prototype here described has been designed in an established technology, to perform at low frequency: these characteristics have been considered suitable for getting a first practical proof of the theoretical results discussed in chapter 2.

- The technology is 0.35 μm C35B3C1. Provided by Austria Micro System (AMS) AG, it is a n-well CMOS technology with a minimum MOS width of 0.35 μm and a minimum resolution of 0.05 μm. Also a double polysilicon layer is provided (with a poly-poly capacitor module and a high resistive poly-silicon module) as well as three levels of metallization. A power supply voltage of 3.3 V is required.

- The mean working frequency is  $f_0 = 100$  MHz.

The modulation parameters are summarized in table 4.1. It is worth noticing that the value of frequency deviation  $\Delta f$  in table 4.1 corresponds to about 3%  $f_0$ , which is a standard value for frequency deviation of a clock.

From table 4.1 one gets for the modulation index:

$$m = \frac{\Delta f}{f_m} = 0.318$$

that is exactly the optimum value derived in chapter 2.

#### 4.1.1 Implementation of the PLL

The block diagram of the PLL-based modulator is shown in fig. 4.1. It is composed of a phase-frequency detector (PFD) with a charge pump (CP), a secondorder passive low-pass filter (LPF), a voltage-controlled oscillator (VCO) and a divider by N on the feedback path.

Figure 4.1: Block diagram of the PLL modified to achieve a frequency modulator.

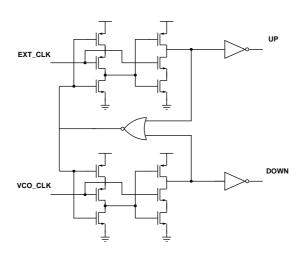

In this scheme, a *phase-frequency* detector (PFD) has been used in place of a simple *phase* detector (PD) as in chapter 3. The PFD is a circuit whose output depends on phase error in the locked state of the PLL, and also on frequency error in the unlocked state [31], which guarantees that a PLL using a PFD will lock under any condition. Its schematic, taken from [42], is shown in fig. 4.2. Dynamic logic gates are used instead of conventional static logic circuitry: as a result, the number of transistors is reduced, which reflects in a shortened feedback path delay, thus increasing circuit precision. The PFD asserts two outputs, here named UP and DOWN: if there is a phase difference between EXT\_CLK and VCO\_CLK, the width of UP and DOWN pulse will be proportional to the phase difference of the inputs.

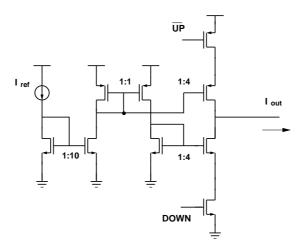

The aim of the CP, whose schematic is shown in fig. 4.3, is to convert the UP and DOWN signals into one current signal:

$$I_{\rm out} = \begin{cases} I_{\rm pump} & {\rm UP} = 1 \\ 0 & {\rm UP} = 0, {\rm DOWN} = 0 \\ -I_{\rm pump} & {\rm DOWN} = 1 \end{cases}$$

Although the value of  $I_{pump}$  is not explicitly indicated in fig. 4.3, it is set through  $I_{ref}$  and the ratio between the form factors of the current mirror branches.  $I_{out}$  is then filtered by the second-order LPF, which re-converts it into a voltage signal and generates the control voltage  $V_{ctrl}$  needed by the VCO.

In the project design, it has been set  $I_{pump} = 400 \mu A$  and N = 64. To ensure stability, the (external) filter has been designed with:

$$C_1 = 58 \text{ nF}$$

$$C_2 = 5.8 \text{ nF}$$

$$R_1 = 370 \Omega$$

Figure 4.2: Phase Frequency Detector.

The resulting closed-loop PLL bandwidth and dumping factor are equal to:

$$\omega_n = \sqrt{\frac{I_{\text{pump}} K_{\text{VCO}}}{2\pi N C_1}} = 94.25 \text{krad/s}$$

$$\zeta \simeq 1$$

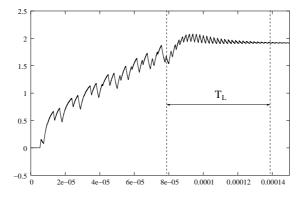

thus meaning a cut-off frequency of about 15 KHz, while the zero of  $H_1(s)$  is at  $1/T_2 = 46.6$  krad/s, i.e. 7.4 KHz. Also, the PLL lock-in time can be estimated as  $T_L = 2\pi/\omega_n \simeq 66 \ \mu s$ .

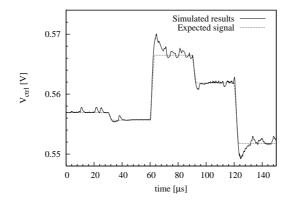

Figure 4.4 shows a simulation of the VCO control voltage during the pull-in process (that is the process to enter the *locked* state, [31]) for the PLL without any driving signal. It is possible to notice that the PLL eventually reaches stability; also the time between entering the locked state (i.e. when major oscillations end) and reaching a complete settlement, is almost equal to the estimated lock-in time  $T_L$ .

#### 4.1.2 Implementation of the modulation

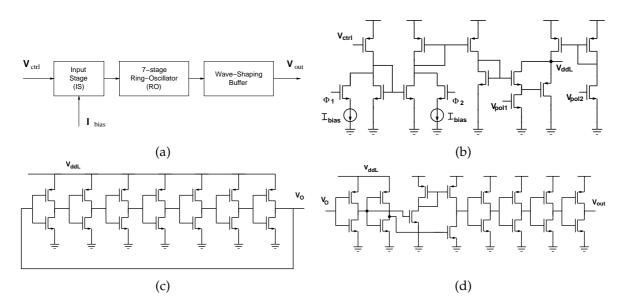

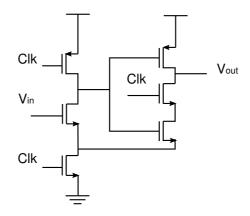

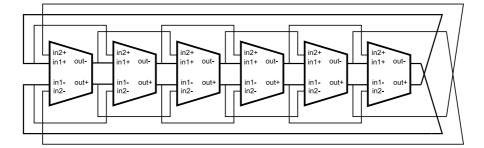

The core block of the PLL is the VCO, whose base-design shown in fig. 4.5 (a) is taken from [33]. It is essentially composed of a seven-stage ring oscillator (c), which is followed by a wave-shaping buffer (d), in order to obtain proper values of logic levels and slew-rate for the output, and is controlled by an input stage (b), whose purpose is mainly to supply the correct operating current to the ring oscillator, and to decouple it from the other parts of the circuit.

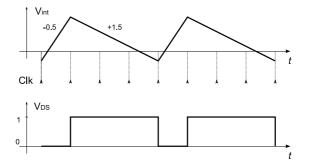

As already mentioned, the modulation is obtained by adding a signal to the input of the VCO. Due to the discrete (i.e. binary, then digital) nature of

Figure 4.3: Charge Pump.

Figure 4.4: Simulation of the *pull-in* and *lock-in* process of the PLL.

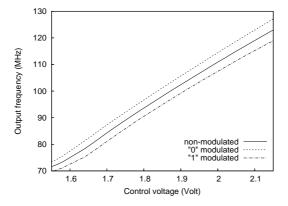

the modulating signal, no full analog adders have been realized: the additive function is instead performed by the input stage of the VCO. Figure 4.5 (b) shows how this is obtained through the two pass-transistors driven by  $\Phi_1$  and  $\Phi_2$ , along with the two current sources  $I_{\text{bias}}$ . This circuit is designed to work with  $\Phi_1 = \overline{\Phi_2} = \Phi$ , where  $\Phi$  is the digital representation of the modulating signal  $\xi(t)$ , which comes from the random number generator. However its behavior is more evident considering  $\Phi_1$  and  $\Phi_2$  separately. Supposing  $\Phi_1 = \Phi_2 = 0$ , the circuit acts as a linear voltage amplifier, where  $V_{\text{ddL}}$  is proportional to  $V_{\text{ctrl}}$ ; the obtained VCO  $f_{\text{OUT}}/V_{\text{ctrl}}$  characteristic is represented by the solid line in fig 4.6; the voltage/frequency ratio is set to:

$$K_{\rm VCO} = 518 {\rm Mrad/s/V}$$

corresponding to  $K_{\rm VCO} = 82.5 {\rm MHz/V}$ . When  $\Phi_1 = 1$ , the current  $I_{\rm bias}$  is sub-tracted from the current mirror, thus shifting up the  $f_{\rm OUT}/V_{\rm ctrl}$  characteristic.

Figure 4.5: (a) Block diagram of the VCO. (b) Modified Input Stage. (c) Ring-Oscillator. (d) Wave-shaping Buffer.

Figure 4.6: Voltage/Frequency characteristic of the VCO in non spread spectrum mode (solid line) and spread spectrum mode (dashed lines).

On the contrary,  $\Phi_2 = 1$  adds  $I_{\text{bias}}$  to the current mirror and shifts down the characteristic. The two shifted characteristics are represented by dashed lines in fig. 4.6. The distance between the curves is approximately constant in the range of interest and represents the PLL  $\Delta f$ . Its value depends on  $I_{\text{bias}}$ ; furthermore there is an almost linear relationship between  $\Delta f$  and  $I_{\text{bias}}$ , that is:

$$K_{\Delta f} = 1.106 \,\mathrm{Mrad/s/\mu A}$$

corresponding to  $K_{\Delta f} = 0.176 \text{ MHz}/\mu\text{A}$ .

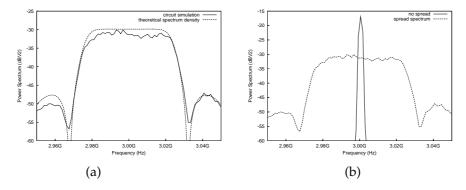

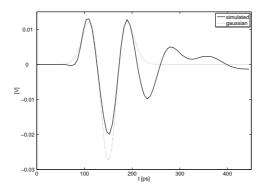

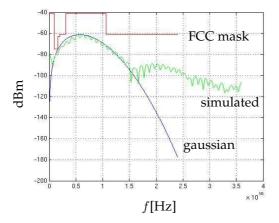

**Figure 4.7:** Comparison between power spectrum density of the output clock obtained from the simulated circuit and the theoretical power spectrum density of the binary modulation, for (a) a wide set of harmonics; and (b) only for the fundamental tone.

**Figure 4.8:** Comparison between power spectra density of the modulated and non modulated output clock for (a) a wide set of harmonics; and (b) only for the fundamental tone.

#### 4.1.3 Simulation results and post-fabrication measurements

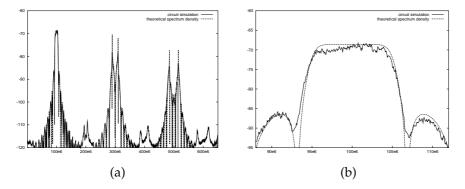

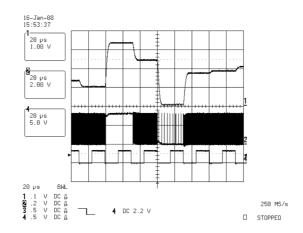

The simulated power spectrum density of the output clock signal can be seen in fig. 4.7 (a) and (b). The figures have been obtained from a 1.2 ms simulations and discarding the first 200  $\mu$ s data, which is a sufficient time, according to PLL bandwidth, to consider extinguished all circuit transients . The simulated spectrum is also compared with the theoretical one from chapter 2. As can be seen, the simulated spectrum is very close to the theoretical one.

Figures 4.8 (a) and (b) show a comparison between the simulated power spectrum density of the output clock signal and the same spectrum obtained from the circuit without any driving signal, i.e. working as a standard PLL-based clock generator. The resolution bandwidth is set to 120 kHz, as indicated by CISPR regulations [43] [44]. The comparison shows a peak reduction on the fundamental tone of about 13 dB.

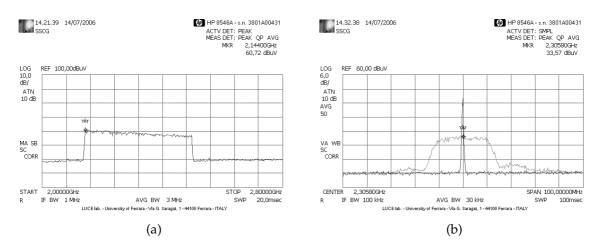

All the simulation results are confirmed by measurements on the proto-

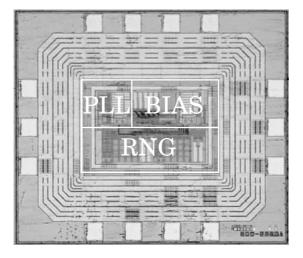

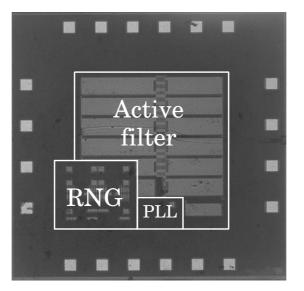

**Figure 4.9:** Microphotograph of the 0.35  $\mu$ m SSCG prototype.

| Output frequency      | 100 MHz                         |

|-----------------------|---------------------------------|

| Modulation type       | Binary Random                   |

| Modulation frequency  | 10 MHz                          |

| Frequency Deviation   | 3.18 MHz                        |

| Lock-range            | 63–108 MHz                      |

| Chip area             | $1.38\times 1.20 \mathrm{mm^2}$ |

| Power consumption     | 20.5mW                          |

| Closed loop Bandwidth | 15 KHz                          |

|                       | $C_1 = 58$ nF, $C_2 = 5.8$ nF   |

|                       | $R_1 = 370\Omega$               |

**Table 4.2:** Performance summary of the 0.35  $\mu$ m SSCG prototype

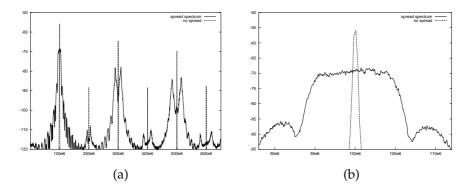

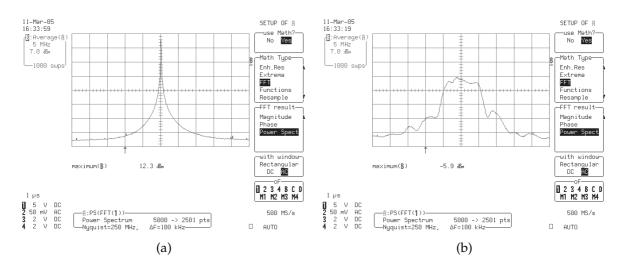

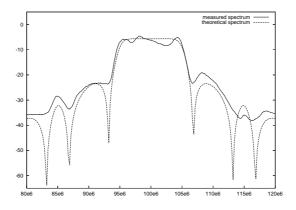

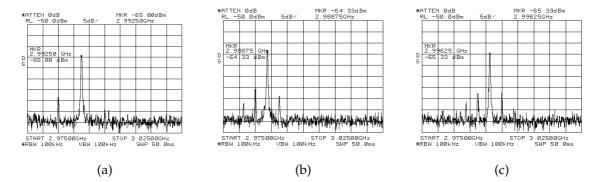

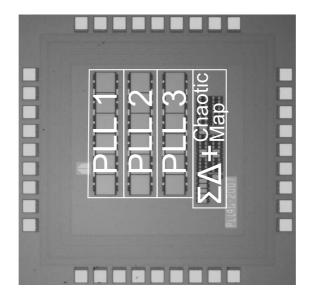

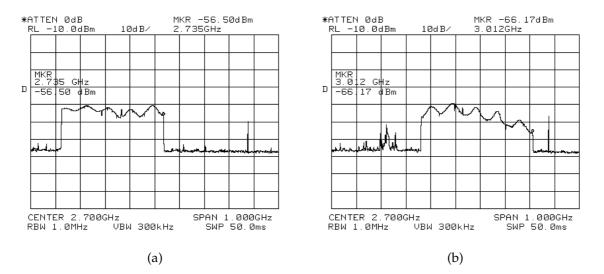

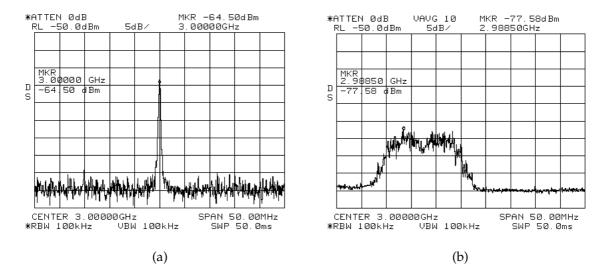

type. The chip microphotograph is shown in fig. 4.9, while table 4.2 gives a performance summary of the integrated SSCG. The active area occupies  $0.38 \times 0.65 \text{ mm}^2$  and the total area including pads is  $1.38 \times 1.20 \text{ mm}^2$ . The low-pass filter is off-chip. Figure 4.10 shows the measured spectrum of the 100 MHz output signal without any modulation (a) and modulated with the optimum index value m = 0.318 (b). The measured peak reduction is about 18 dB. Figure 4.11 shows the comparison between the spectrum from fig. 4.10 (a) and the theoretical one; the matching is very good, confirming the effectiveness of the proposed circuital approach.

Figure 4.10: (a) Measurements from the prototype in non spread spectrum mode; and (b) in spread spectrum mode.

Figure 4.11: Comparison between the measured spectrum of Figure 5.17(b) and the theoretical one.

#### 4.2 Description of the 180 nm SSCG prototype

The second SSCG prototype here described has been scaled in technology, to perform at high frequency: the parameters of the modulation, such as center frequency and frequency deviation, have been suggested by Serial Advanced Technology Attachment (SATA) protocol [23]. This standard, though, requires that the performed modulation applied to its synchronization signal is of *slow* type. For this reason, this implementation does not aim at being suitable for the standard, but only at proving the benefits of fast modulation at high frequency.

The technology used is UMC 180 nm: a standard n-well CMOS technology, optimized for digital applications. It has a single poly-silicon layer, up to six metal layers, and a metal/metal capacitor options between the two top metal layers. The core power supply voltage is reduced to 1.8 volts, but 3.3 volts

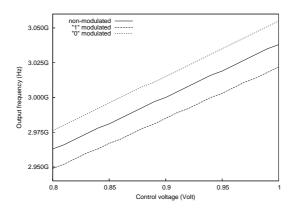

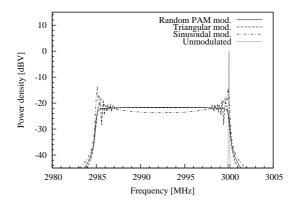

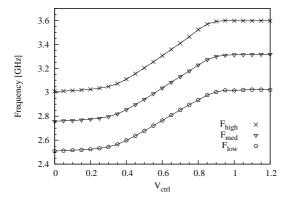

| Center-Spread Frequency, $f_0$                   | 3 GHz        |

|--------------------------------------------------|--------------|

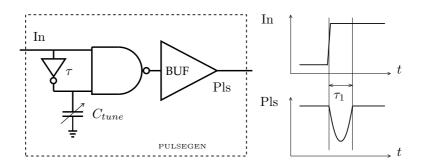

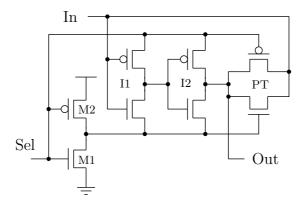

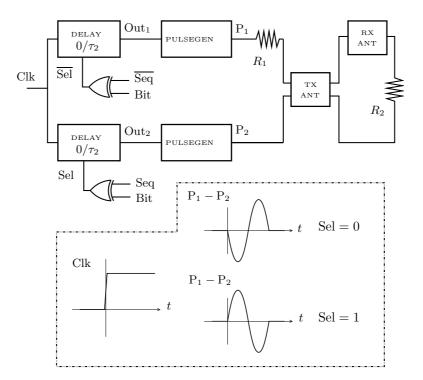

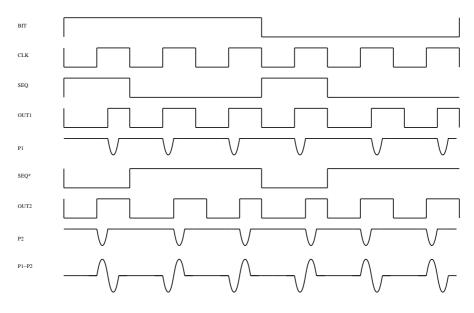

| Spread-Spectrum Modulation frequency, $f_m$      | 47.17 Mbit/s |