#### Alma Mater Studiorum - Università di Bologna

#### DOTTORATO DI RICERCA IN

### INGEGNERIA ELETTRONICA, TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE

Ciclo 35

## Settore Concorsuale: 09/E3 - ELETTRONICA Settore Scientifico Disciplinare: ING-INF/01 - ELETTRONICA

## DESIGN AND CHARACTERIZATION OF WIDEBAND HALL CURRENT SENSORS IN BCD TECHNOLOGY FOR SMART POWER AND METERING APPLICATIONS

Presentata da: Sana Fatima Syeda

**Coordinatore Dottorato** Prof. Aldo Romani

Supervisore Prof. Marco Crescentini

> **Co-Supervisore** Prof. Aldo Romani

Esame finale anno 2023

"The most beautiful experience we can have is the mysterious. It is the fundamental emotion that stands at the cradle of true art and true science" — Albert Einstein

# Contents

| A        | cknov | wledgements                                  | ix |

|----------|-------|----------------------------------------------|----|

| A        | bstra | let                                          | xi |

| 1        | Intr  | oduction                                     | 1  |

|          | 1.1   | Motivation and objectives                    | 1  |

|          | 1.2   | Thesis structure                             | 14 |

| <b>2</b> | Bac   | kground on Hall Sensors                      | 15 |

|          | 2.1   | Galvanomagnetic effects                      | 15 |

|          | 2.2   | Materials                                    | 23 |

|          | 2.3   | Hall plate technology                        | 25 |

|          | 2.4   | Operating modes                              | 28 |

|          | 2.5   | Horizontal versus Vertical Hall sensors      | 30 |

|          | 2.6   | Hall - Effect Current Sensor                 | 31 |

|          |       | 2.6.1 Current-to-Magnetic Field Transduction | 32 |

|          |       | 2.6.2 Offset cancellation                    | 39 |

|          |       | 2.6.3 Analog Front-End                       | 42 |

|          | 2.7   | Non-idealities                               | 45 |

| 3        | Ban   | dwidth enhancement in Hall sensors           | 49 |

|          | 3.1   | Bandwidth limits                             | 49 |

|          | 3.2   | The X-Hall probe                             | 50 |

|          |       | 3.2.1 Device model                           | 50 |

|          | 3.3   | KF94: X-Hall implementation in voltage mode  | 56 |

|               |               | 3.3.1         | KF94 prototype issues                                                         | 61  |

|---------------|---------------|---------------|-------------------------------------------------------------------------------|-----|

| 4             | CH            | 09: Pr        | oposed X-Hall sensor in current mode                                          | 65  |

|               | 4.1           | Theore        | etical validation                                                             | 67  |

|               | 4.2           | CH09:         | Proposed architecture                                                         | 71  |

|               |               | 4.2.1         | I-B Transducer                                                                | 72  |

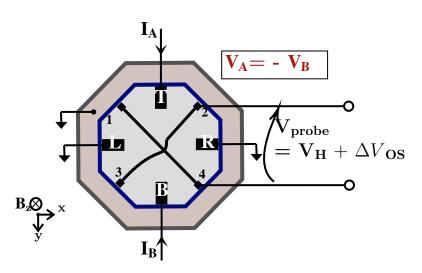

|               |               | 4.2.2         | X-Hall probe                                                                  | 73  |

|               |               | 4.2.3         | Common mode control $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 73  |

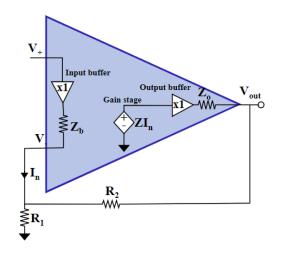

|               |               | 4.2.4         | Analog Front End                                                              | 75  |

|               | 4.3           | Prelim        | inary results                                                                 | 78  |

|               | 4.4           | Experi        | imental characterization                                                      | 81  |

|               |               | 4.4.1         | Static characterization                                                       | 82  |

|               |               | 4.4.2         | Offset                                                                        | 83  |

|               |               | 4.4.3         | Dynamic characterization                                                      | 86  |

|               |               | 4.4.4         | Validation                                                                    | 88  |

|               |               | 4.4.5         | Magnetic sensitivity                                                          | 90  |

| <b>5</b>      | $\mathbf{CH}$ | 100: E        | nhancements to CH09                                                           | 93  |

|               | 5.1           | Propos        | sed architecture                                                              | 94  |

|               | 5.2           | Gain o        | lrift                                                                         | 95  |

|               |               | 5.2.1         | Temperature sensor                                                            | 97  |

|               | 5.3           | Dynan         | nic range                                                                     | 103 |

|               | 5.4           | Offset        | reduction                                                                     | 103 |

|               |               | 5.4.1         | Novel offset cancellation                                                     | 105 |

|               |               | 5.4.2         | Switched Hall bias circuit                                                    | 109 |

|               | 5.5           | Comm          | non mode control amplifier                                                    | 111 |

|               | 5.6           | Impler        | mentation                                                                     | 112 |

| 6             | Cor           | nclusio       | ns                                                                            | 115 |

|               | 6.1           | CH09:         | X-Hall sensor in current mode                                                 | 115 |

|               | 6.2           | CH100         | ): X-Hall sensor for accuracy                                                 | 118 |

| $\mathbf{Li}$ | st of         | <b>Tables</b> | S                                                                             | 121 |

| List of Figures | 123 |

|-----------------|-----|

| Bibliography    | 131 |

## Acknowledgments

First and foremost, I owe my sincere and humble gratitude to my outstanding mentors and supervisors Prof. Marco Crescentini and Prof. Aldo Romani for their invaluable guidance and expertise throughout the program. Their adept knowledge, insightful remarks and constructive criticism enabled me to optimize solutions from diverse perspectives to obtain results. I also owe a heartfelt thanks to Prof. Marco Tartagni, for always instigating our weekly group meetings with much zeal, inviting fruitful discussions of curiosities, problems and solutions on a broader research horizon.

I would like to acknowledge STMicroelectronics for providing us the platform and access for the advanced silicon process technologies to carry out our research activities and design of the silicon chips. A special thanks to Giulio Ricotti for being a great inspiration on design discussion, Marco Marchesi for his extensive support for Hall device physics modelling and our Unibo - STMicroelectronics coordinator, Roberto Canegallo for his invaluable support during the fabrication and development phases of the silicon chips.

My gracious thanks to members of the sensor group for their valuable contributions, and all my dearest colleagues and friends for their unending support and encouragement during the research activity.

I would also like to acknowledge the joint support by the European Union's Horizon 2020 research and innovation program, under the Electronic Components and Systems for European Leadership (ECSEL) Joint Undertaking, and from Germany, Slovakia, Netherlands, Spain, and Italy under grant agreement No. 876868 (PROGRESSUS).

My reflection is incomplete without the indebted gratitude to my beloved family, from whom I receive unconditional love and support. <u>x</u>\_\_\_\_\_

## Abstract

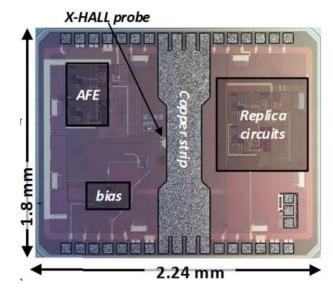

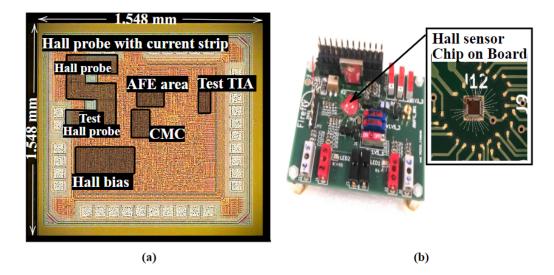

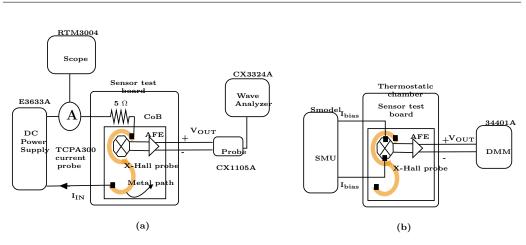

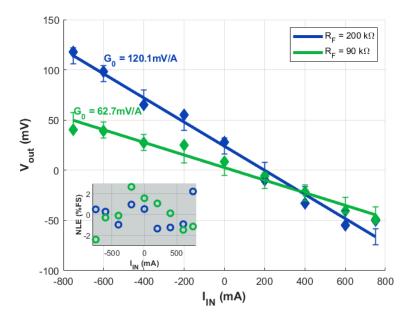

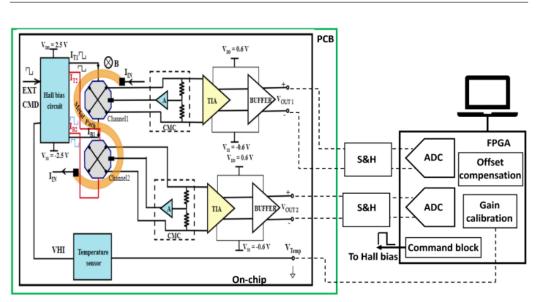

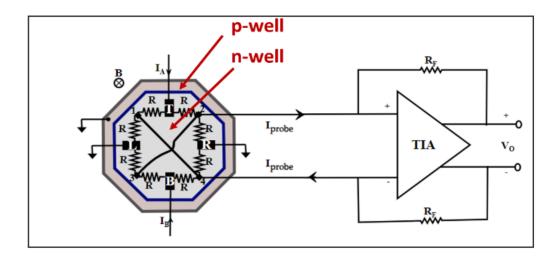

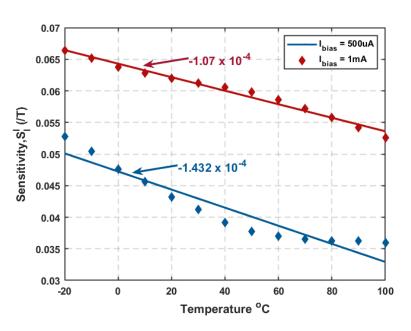

Power electronic circuits are moving towards higher switching frequencies, exploiting the capabilities of novel devices, so as to shrink the dimension of the passive components. This trend demands sensors capable enough to operate at such high frequencies. This thesis aims to demonstrate through experimental characterization, the broadband capability of a fully integrated CMOS X-Hall current sensor in current mode, chip CH09, realized in CMOS technology for power electronics applications such as power converters. Current-mode operation alleviates the impact of stray capacitive loading at the probe-readout interface and enables the usage of a transimpedance amplifier (TIA) as readout circuit, offering better bandwidth, noise and power performance than conventional instrumentation amplifiers. The system exploits a common-mode control system to operate the sub-modules at dual supply voltages, respectively 5-V for the X-Hall probe to achieve high sensitivity, and 1.2-V for the readout to exploit the high transition frequency of transistors with reduced oxide thickness. A chip-on-board mounting limits the parasitic inductive effects on the host PCB. The developed prototype achieves a maximum acquisition bandwidth of 12 MHz. With a power consumption of 11.46 mW and a resolution of 39 m $A_{rms}$ , it presents a sensitivity of 8  $\%T^{-1}$  and achieves a FoM of 569-MHz/ $A^2$ mW, which is significantly higher than current state-of-the-art hybrid Hall/coil solutions.

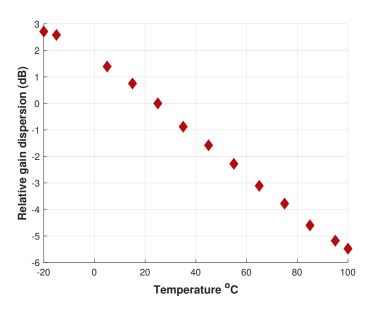

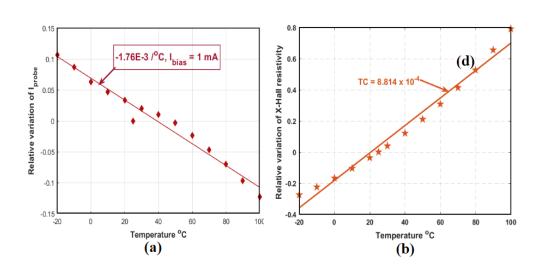

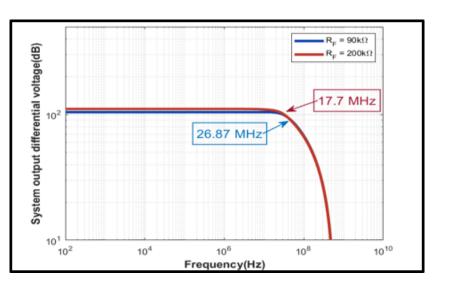

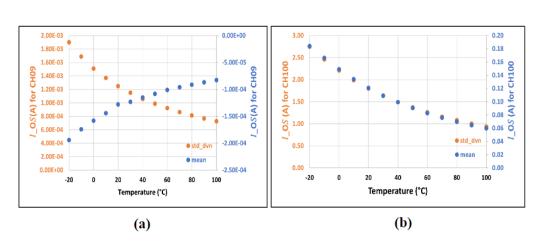

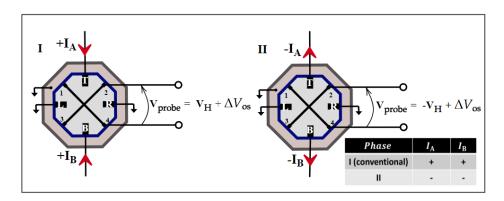

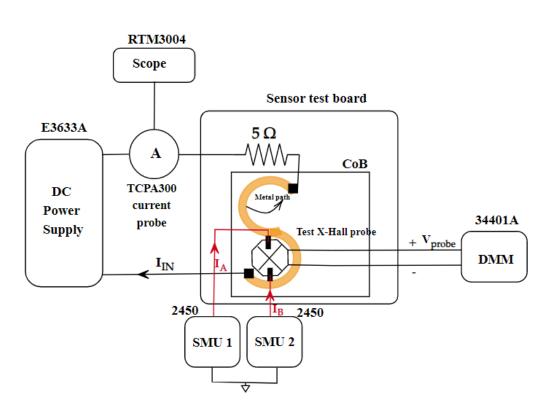

Further, enhancements were proposed to CH09 as a new chip CH100, aiming for accuracy levels that are a prerequisite for a real-time power electronic application. The internal analog read-out circuits were optimized for a wider bandwidth of 26.7 MHz with nearly 30% reduction of the integrated input referred noise of 26.69  $nA_{rms}$  at the probe-Analog Front End (AFE) interface in the frequency band of DC-30 MHz, and a 10% improvement in the dynamic range. Preliminary results show an upper bandwidth limit of the system as 26.87 MHz. The input range of the expected prototype is 5-A as it will be realized using a stud-bump instead of the chip on board. The chip incorporates a dual sensing chain for differential sensing as an option to overcome common mode interferences. A novel offset cancellation technique is proposed that would require switching of polarity of bias currents using a switched Hall bias circuitry. In contrast to the spun Hall sensors, it does not involve switching between the Hall probe contacts, hence the methodological limit is not imposed due to the switch parasitics, rather, the realized bandwidth would be a function of the frequency of switching the bias currents. Thermal gain drift was improved by a factor of 8 and will be calibrated digitally off the chip utilizing a new built-in temperature sensor module that can provide a post-calibration measurement accuracy greater than 1%. The estimated power consumption of the entire differential sensing system is 55.6 mW. Both prototypes have been implemented through a 90-nm microelectronic process from STMicroelectronics and occupy a silicon area of 2.4  $mm^2$ .

Keywords: Current sensing, Magnetic sensors, Hall sensors, broadband sensing, X-Hall, current mode, residual-offset cancellation, Integrated sensors, Microelectronic circuits, BCD technology, Precise current sensors, Power electronic applications

## Chapter 1

## Introduction

### **1.1** Motivation and objectives

Power electronics is a challenging and exciting interdisciplinary domain that applies the knowledge of analog/digital electronics, control systems, electromagnetism, sensors, signal processing, etc, and deals with solid-state devices designed for various applications, for the control and conversion of electrical power. In other words, power electronic circuits form a power converter that can transduce energy from a supply to a load or an energy storage device in any of the combinations: AC-AC, AC-DC, DC-AC and DC-DC, with a possibility of systems combining the converters. Control electronics would be the heart of such an interconnected system and their algorithms could involve the sensing and measurement of voltages and currents that could act as input to trigger a specific control cycle to attain a stable operation, depending on the application. Moreover, they are usually based on high-frequency switching semiconductors that enable high-speed signal processing [1,2]. When we focus on power electronics and their applications, and aim to address their requirements, we must understand that power electronic systems are usually modeled in two classes based on the objective of study: (i) evaluation of responses to the harmonics introduced by a power electronics sub-system, (ii) evaluation of a complex range of practical issues that arise due to the interdependence of two connected systems or subsystems. The latter is a crucial evaluation as it involves control loops and

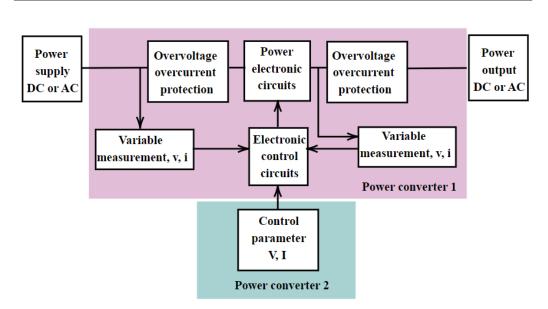

Figure 1.1: Block diagram of a power converter in an autonomous power electronic application

their accurate monitoring of dynamic variation of parameters such as voltage or current which can directly or indirectly affect the performance of the entire system [3]. A typical block scheme of an autonomous power converter is as shown in Fig.1.1. Detection of sharp transients or fluctuations of voltage/current or magnetic perturbations beyond the accepted threshold, due to the high-speed switch semiconductors can prevent damage to the converters and protect the power switches. This is where high-performance broadband current sensors come into play and their requirement is highlighted with utmost importance by a broad range of power electronic applications, from small scale systems used in electrical appliances to macro systems of energy supply and distribution. Some examples of such applications [4], include electric vehicles, DC-DC converters, photovoltaics, magnetometers, motor drives, and smart grids.

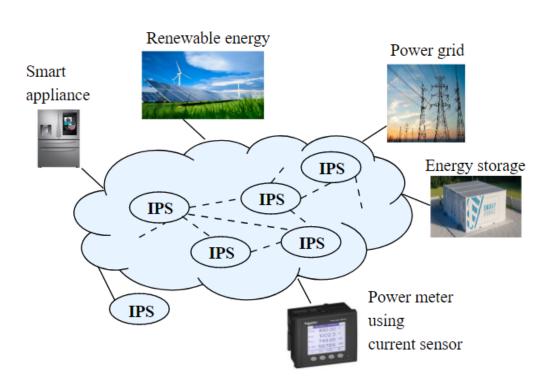

Fig.1.2 illustrates a wireless architecture for a smart grid lab [5] which is connects to various energy sources through Intelligent Power Switches (IPS) that can route power from one point to another. The power meter is an important device that is used to measure the current in the test line using a current sensor and in this case for experimental purpose, a Hall sensor by Al-

Figure 1.2: Architecture of a general wireless power network in a smart grid illustrating the use of current sensor for the computation of power

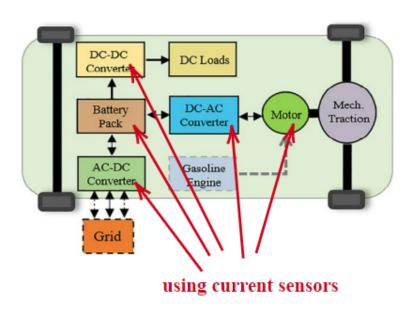

legro Microsystems, ACS714 was used. Modern hybrid/ electric vehicles use several integrated power electronic modules for compactness, reduced costs and reduced interconnects but this also causes the accessibility to internal information signals to become more difficult. To measure the current circulated between the motor and the motor-drive subsections, on-site current measurements within the power modules using highly sensitive Giant Magnetoresistance (GMR) current sensors were demonstrated in [6] while Fig.1.3 illustrates a general block diagram of an Electric Vehicle [7]. The sensors were also used for temperature sensing and thus, proved to be highly useful in protecting the functionalities of the semiconductor electronics within the power modules. A current sensor was also used for fault diagnosis algorithm proposed by [8]for brushless dc motors that find use in highly reliable electromobility systems. DC-DC converters especially high voltage converters, have an incessant need for load or inductor current monitoring in order to

Figure 1.3: Block diagram of a generic Electric Vehicle

implement the in-built control loop compensation. Current sensing becomes a challenge due to the wide input common mode voltage range of the converter and stringent time specifications. There is a gaining interest to exploit fully integrated and low cost broadband sensing to achieve good regulation losses. High power shunts using sense resistors with low tolerance for current sensing are hard to integrate due to their size and additional components, and so a compact and economical sense-FET with a high immunity to board level parasitics that could degrade the system efficiency was implemented for a 40-V buck converter [9]. It achieved a gain bandwidth, GBW of 20.3 MHz but could only sense the current for a half cycle while the other half could only be partially sensed.

As the applications of power electronics call for an increased necessity of critical and accurate monitoring and control of their modules and interdependent submodules, there has been progress in research towards high-frequency and efficient contactless current sensing techniques to compensate the efficiency degradation and improve the switching frequency of converters [11]. Current being an indispensable parameter for their real-time control, traditional current sensing techniques can no longer serve the requirements of

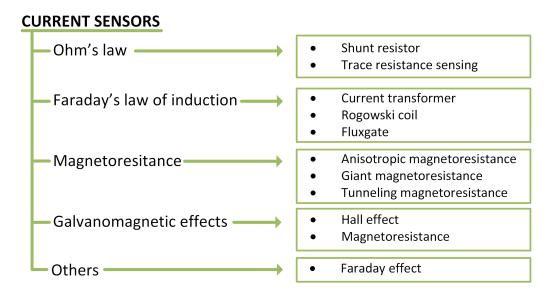

**Figure 1.4:** Figure from source [10]. Overview of current sensing techniques ordered by their operating principle.

modern power converters. Smart and unattended current and energy metering are basic to such applications as they enable the detection of failures, analysis of power consumption and reduction of energy losses. Broadband current acquisition is also integral to non-invasive load monitoring applications in which the appliances are recognized based on the actual consumed current waveform. Miniature and low-power sensors highly affect the development of smart grids in this aspect and must be characterized in themselves to perform power management and sustainable operation [12]. There are several applied techniques for current sensing, but to respond to the demand for fast switching power electronics, the challenge lies in seeking innovative current-sensing solutions that facilitate high signal bandwidths. So, an ideal approach would be the deployment of a non-invasive current sensor, compact in size, fully integrable, which fulfills the criteria of the broadband operation of power electronics, supports AC and DC sensing with perfect galvanic isolation, and low power consumption. Fig.1.4 illustrates one of the possible classifications for the various sensing techniques found in literature, based on the sensing principle [13].

In contrast to other sensing techniques, sensors based on Ohm's law are

usually invasive. They lack galvanic isolation but can accurately measure both AC and DC currents with limitations for the input range at the expense of the power dissipation. They are conventionally bulky and adding galvanic isolation using additional expensive electrical isolation amplifier limits its broadband capability [14,15]. Recent advances in research achieve a galvanic isolation by implementing a fully integrated semiconductor shunt sensor with an input range of  $\pm 1.25$  A and 12.5 MHz bandwidth [16]. Zhong Tang et al., [17] demonstrated a shunt resistor implemented both as a PCB trace and a metal alloy with a microelectronic readout circuitry for battery management applications, but with a bandwidth limited to a few kHz. Galvanic isolation was achieved by bonding the die to the shunt trace with an insulative glue.

The Rogowski coil (RC) [18] and the Current Transformers (CT) [14, 19] are competent in terms of realizable bandwidth (up to GHz) [20], galvanic isolation, but the resulting sensor is bulky due to the coil wounded core, difficult to integrate, and loses the DC signal component. RCs can be realized using Printed circuit board (PCB) technology [21] with a precise geometry and improved thermal drift and although difficult, was fully integrated into a chip [22]. Fluxgate sensors exploit the magnetic hysteresis of ferromagnetic materials in order to sense very small magnetic fields. They can be used to realize highly accurate current sensors, yet they have limited Dynamic Range (DR) and bandwidth.

Magnetoresistive (MR) sensors or XMRs are based on the variation of resistivity due to the presence of an external magnetic field. They can be grouped by the underlying magnetoresistance effect: anistropic magnetoresitance (AMR), giant magnetoresistance (GMR), and tunneling magnetoresistance (TMR) [23]. AMR sensors exploit the magnetic anisotropic scattering of conduction electrons in ferromagnetic materials [24], while GMR and TMR are based on physical effects arising in multilayer devices with magnetic materials [13, 25]. MR sensors are very good candidates for modern power applications in the aspect of size, reliability and low power but they all require specific back-end processes in the semiconductor technology, leading to relatively high costs. some commercial sensors such as the TLE5501 and the TMR2301 could reach a few hundreds of kHz [26] [27] and the literature state-of-the art demonstrates a bandwidth of 5 MHz [28].

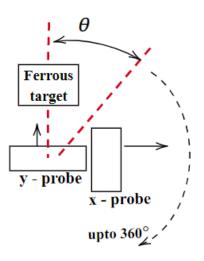

Galvanomagnetic sensors rely on the Lorentz force acting on moving electrons to sense the magnetic field [29]. They can be grouped depending on the dominant galvanomagnetic effect: the geometrical magnetoresistive effect causes a change in the resistivity of the material along the main path of moving electrons, whereas the Hall effect generates a voltage drop orthogonal to the path of moving electrons. Compared to most sensors, Hall - Effect Current Sensors (HECS)s, which are the argument of this thesis, are highly compatible with standard silicon technology and can be either integrated with CMOS circuits or might leverage on alternative compounds to achieve better performance hence, allowing for a very compact solution for any application. Their conventional usage is found in a wide range of contactless industrial applications for proximity, magnetic field, speed and current sensing in the fields of automotives, electric motors, photovoltaics, smart grids, etc. To get an idea, angular position of a magnetic target can be determined using Hall-effect sensor to sense the magnetic field if it is placed at the centre of rotation of a magnetic field generated by a magnetic target. As the target rotates, it will be exposed to the field from different directions and responds monotonically to the components in a single axis over a range of  $\pm 90^{\circ}$  of rotation. For full range measurement of 360°, two Hall probes are placed at  $90^{\circ}$  orientation with respect to each other as illustrated in Fig.1.5, for example, one for the x-axis and one for the y-axis followed by mathematical operation to determine the output. Exclusive mechanical systems risk wear and tear that limit their speed and performance and in some applications, it would be tedious to install ferrous targets or gears [30] to sense their speed or position, however the requirement is still called for, in numerous industries. Extraction of an electrical signal from the passing features of the gear teeth is a sought after challenge. A Hall-effect sensor can be utilized to detect the variation of magnetic flux between the airgap of a permanent magnet and the ferrous gearteeth and yield a usable electric signal. The magnet is used to magnetize the gearteeth, so as the teeth move across the surface of the magnet, the flux changes. MLX90217 geartooth sensor from Melexis [31] realized digitized output with a reset which is activated when the signal changes po-

Figure 1.5: Angular sensing for full range of  $360^{\circ}$  using two Hall-effect probes positioned at  $90^{\circ}$  with respect to each other.

larity and changes the output level based on signal threshold, thus creating a zero speed peak detection speed sensor. The sensor bandwidth is 15 kHz and challenging time requirements such as for crank position sensing suffer accuracy issues at high speeds. The constraint for high-speed operation is even higher for Power electronic applications that require current sensing in a minimal time frame for peak and over-current detection of fast switching currents. Let us now overview the state of the art for Hall sensors and the challenges to overcome.

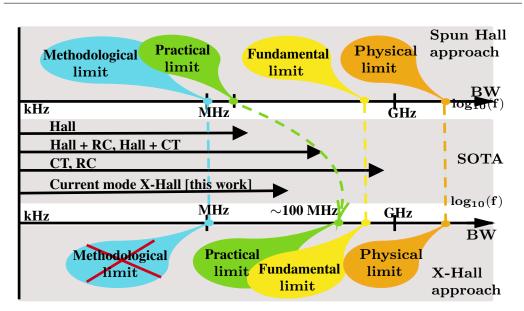

#### State of the art for Hall sensors

The HECS finds much of its appeal in the applications and market owing to its low cost, low heat dissipation, galvanic isolation, large DR, good linearity, and the ability to measure DC currents, make HECS well suited for modern power applications [15,32]. Practically, the device also comes with its own set of imperfections in terms of device geometry, doping concentration, and other fabrication issues, resulting in an undesirably high intrinsic offset of tens of mV that completely dominates the detected signal, which usually is in the order of a few  $\mu V$ . Additionally, low sensitivity, limited bandwidth which barely reaches the MHz range [33–35], sensitivity to external electric fields, and temperature dispersion of the parameters also limit its performance. Nevertheless, all these limitations can be mitigated by exploiting exotic materials for devices, additional back-end processes, and smart circuit configurations and design [36–38]. To overcome these limitations, state-ofthe-art broadband current sensing techniques have adopted hybrid solutions by combining RC or CT with compact Hall-effect current sensors [39, 40] for high speed switching and fully galvanically isolated current sensing. The input measurand current range is also wide without risking the coil saturation. This approach is however challenged by non-linearity issues mainly arising from the matching of different frequency responses. When following a hybrid approach, reduction of the non-linear deviation is of primary concern [41], while the bandwidth requirements are usually assured by the CT or RC. Multiple solutions were proposed to overcome the limitation of the offset which highly affects the accuracy of the sensor [10, 42]. The most used offset-reduction method is the Spinning Current Technique, (SCT) [43], which uses a single Hall plate but spins the bias current around it using all the contact pairs sequentially while sensing the Hall voltage at contacts perpendicular to the respective bias direction. The measurement is made at every  $T_{spin} = 1/f_{spin}$  implying a rotation time of n- $T_{spin}$  for an n-phase SCT. Summing all the measurements over a complete rotation leads to a reduction of the offset by almost a factor of 100 [10, 44]. A detailed discussion can be found in section 2.6.2 and the illustration in Fig.2.12(c). The downside of this, is that at higher spin frequencies, there is also a degradation of the offset. Besides this, the practical implementation of this technique increases the capacitive load seen by the Hall plate, which sets a significant limit to the bandwidth. This methodological bandwidth limit was overcome by the design of the X-Hall probe [45] by providing intrinsic static offset cancellation, hence eliminating the need for the SCT and speculating an improved practical limit of 200 MHz bandwidth achievable by the X-Hall probe itself, subject to the AFE's design. This would place the X-Hall sensor ahead of the state-of-the-art hybrid solutions. Practically, the X-Hall sensing system operated in voltage mode [46] achieved a 4-MHz bandwidth when implemented in 0.16  $\mu$ m technology with a Differential-Difference Current Feedback Amplifier (DDCFA) as AFE. The limitations in bandwidth were mainly due to the amplifier itself and the parasitic inductive effects at package level. From a technological perspective, purely silicon-based HECSs also have lower sensitivity with respect to GMR and TMR sensors, with resolutions that are usually limited to a few hundreds  $\mu T$  [47, 48] in standard implementations, or a few  $\mu T$  when using magnetic concentrators [49, 50]. Based on a fresh study of 2022 by Allegro Microsystems, most industrial and automotive application requirements overlap and comparing the Hall sensors with the XMRs, the Hall sensors will continue to be the best solution for such applications unless the XMRs would find a balance between performance and costs [51]. A further improvement in sensitivity, offset (down to a few hundred nT) and a resolution of about 30 nT in the sub-Hz range in heterostructure-based Hall plates can be obtained by exploiting the 2D electron gas (2DEG) layer of quantum-well Hall sensors (QWHS) [52] that exhibit a high electron mobility and a very stable density. Higher bandgap GaN-based Hall-effect devices have also caught up on the trend in research due to their high resilience in extreme environments of up to 600  $^{\circ}C$  with a guaranteed sensitivity recovery, unlike silicon-based devices [38, 53, 54].

Well, moving apart from the hybrid solutions and other technological alternatives for Hall devices and focusing on just the purely semiconductor based Hall-effect sensor, it was mainly considered for low frequency applications, however, it has immense potential to become a valuable solution in broadband applications, by boosting its bandwidth limit in the MHz range [10, 55] and beyond [56]. Table 1.1 summarizes the features of the different state of the art current sensors and highlights the problem area and direction for necessary research in the field of Hall sensors. My PhD activity was primarily focussed on overcoming the challenges of the bandwidth limitation of the HECS and to push the performance metrics such as the noise, resolution and further working on the limitations of accuracy that relate to the offset and drift with respect to time and temperature beyond the state of the art, with the ultimate future goal of integrating the sensor with a real power electronic application such as the DC-DC converter to monitor LDMOS degradation [57]. A HECS can be generally treated as a three-stage

| Sensor<br>type | Bandwidth | Accuracy | DC<br>measure | CMOS<br>integration | Galvanic<br>isolation | Heat<br>dissipation | Compact | Cost |

|----------------|-----------|----------|---------------|---------------------|-----------------------|---------------------|---------|------|

| Shunt          | High      | Yes      | Yes           | Possible            | Difficult             | Yes                 | No      | Low  |

| CT             | Very high | Yes      | No            | Difficult           | Yes                   | No                  | No      | low  |

| Coil           | Very high | Yes      | No            | Difficult           | Yes                   | No                  | No      | High |

| Fluxgate       | Limited   | Yes      | Yes           | Easy                | Yes                   | No                  | No      | High |

| XMR            | Limited   | Yes      | Yes           | Easy                | Yes                   | No                  | Yes     | High |

| Hall           | limited   | moderate | Yes           | Easy                | Yes                   | no                  | yes     | Low  |

Table 1.1: Overview of features of State-of-the-art current sensors

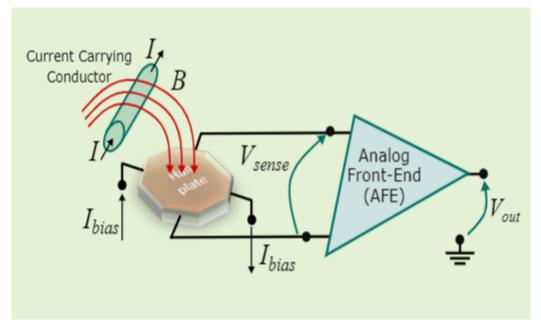

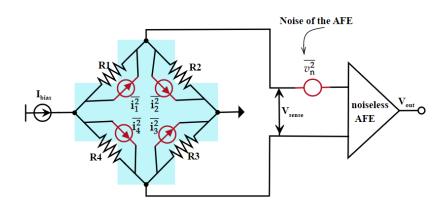

**Figure 1.6:** Hall - Effect Current Sensor system with (i Current to magnetic field transducer, (ii) Hall plate, and (iii) the Analog Front End

sensing chain as illustrated in Fig.1.1 consisting of: i) a current-to-magnetic field transducer; ii) the Hall probe itself (i.e., the magnetic sensitive device), and iii) the analog front-end (AFE). The analysis of each of these stages is critical for a proper design of the current sensor <sup>1</sup>. The design considerations

<sup>&</sup>lt;sup>1</sup>Note: The reader must not confuse with 'sensor' as just the Hall plate. Throughout the thesis, when referring to a 'sensor', a 'Hall-sensor' or 'HECS' or 'sensor system' it is inclusive of the entire sensing chain, while when referring to a Hall element, the terms

took into account were minimum power consumption, system acquisition bandwidth, BW to be achieved beyond the state of the art as greater than 10 MHz. In an on-chip power system, the measurand current is usually in the mA to A range, so a soft input current limit for the Minimum Detectable Signal, (MDS) of 5 mA and a maximum of 5 A was aimed for. The sensor should also be insensitive to the magnetic field generated by other sections of the application circuit. This aspect however, is for future investigation.

#### Sensor Metrics

Before proceeding further, we must understand that when analyzing any sensor, it is important to define the main Figure of Merits, (FoM)s to be considered for performance evaluation [23,30], the knowledge of which is essential to characterize and compare it with the other sensors in the state of the art. From a functional perspective, current sensors can be generally described by expressing the output voltage  $V_{out}$  as a function of the measurand current I [58] and the relation is formulated as:

$$V_{out} = SI + V_{os} + f_{nl}(I) + v_n; (1.1)$$

where the following definitions are introduced:

• Sensitivity, indicated by S, is defined as the ratio between the increment in the output voltage over the increment in the measurand current. Sensitivity is a fundamental performance metric that expresses the ability of the device in sensing small variations of the measurand current and translate them into a large and robust voltage signal at the output. So, from a designer's perspective, high sensitivity is a bonus point as it would reduces the complexity and cost of electronics required to process the large output signal. In conjunction, the thermal drift of sensitivity, or let us say, the stability of sensitivity in extreme conditions is also a parameter that adds merit to the characterization of the sensor. It is much desirable for a sensor to have as low temperature

<sup>&#</sup>x27;Hall plate' or 'Hall probe' are used.

coefficient (TC) as possible.

- Additive DC Offset, indicated by  $V_{os}$ , is defined as the non-zero output voltage value at DC in the presence of a null measurand current. This quantity is intended as the result of different effects, including the electrical offset introduced by the electronic front-end, as well as the effect of the earth magnetic field. Similar to the case of sensitivity, the stability of the offset with thermal variations is important with a low TC. It is necessary to validate that the offset returns to the same value at nominal temperature after being subjected to extreme hot and cold temperatures. This allows one point compensation of the offset.

- Non-Linearity, indicated by  $f_{nl}(I)$ , is defined as the deviation from linearity for the relationship between the output voltage and the measurand current.

- Noise, indicated by  $v_n$ , is the output-referred noise density integrated over the acquisition bandwidth (in V). Alternatively, it can be expressed as an input-referred noise (in A) by  $v_n/S$ . The noise property is a random variation of the sensor output when the measurand quantity is zero. It is characterized by its Power Spectrum Density at a given frequency, PSD(f), and by integrating over a frequency range  $f_l$ ,  $f_h$ , noise is expressed as a root mean square (rms) value. In this case, the frequency band for which it holds true must be specified.

- *Bandwidth*, defined as the frequency interval from DC to the 3-dB attenuation point of the transfer function of the sensor. Usually, increasing the bandwidth also means increased noise levels within the frequency range of interest.

- *Dynamic range*, defined as the ratio between the maximum measurable current and the minimum detectable signal (MDS). The MDS of course is determined by the output referred noise of the sensor itself.

#### **1.2** Thesis structure

The thesis is organized as follows:

Chapter 2 aims to provide an exhaustive review on the necessary background on the Hall-effect sensors, study on the associated physical effects, their realization, functioning modes and the technicalities for integrating a Hall probe into a system. Further, a discussion is made on its evolution to the present state of the art, the limitations it has to overcome and a mention of modern day applications.

Chapter 3 initiates with the discussion of the base of the research target and the benchmark for the project, semiconductor chip KF94, with its achievements and limitations.

Chapter 4 proposes the current mode solution, chip CH09 for bandwidth enhancement, with a section explaining and validating the theory, a description of its architecture. This is followed by a discussion on the preliminary simulated results and the experimental characterization results carried out for the chip CH09 in our lab.

Chapter 5 proposes a new chip CH100 with its architecture and preliminary results with fine refinements and improvements for chip CH09 to cope with thermal gain drift. It further proposes a novel off-chip offset cancellation technique.

Chapter 6 covers general conclusions for this thesis and state of the art comparison.

## Chapter 2

## **Background on Hall Sensors**

### 2.1 Galvanomagnetic effects

The physics is always amazing and to brace ourself with the fundamental knowledge and understanding of the various effects that take place at the sub-atomic level, makes their exploitation to meet our purpose even more interesting. This section aims to summarize and provide the necessary analytical background of physical effects in a Hall-effect device. The galvanomagnetic effects refer to the charge mobilization that manifests in condensed matter carrying electrical current in the presence of magnetic field and is an integration of three different effects: the Hall-effect, magnetoresistance effect and the galvanothermomagnetic effects. The first two effects are characterized under isothermal conditions while the latter is a non-isothermal galvanomagnetic effect. Although, the Hall-effect device could be composed of any conductive material such as metal or semiconductor, for the sake of staying inclined to the scope of this project which is based on semiconductor based microelectronic technology, we would always consider a semiconductive material. The forthcoming analysis, will consider practical and ideal geometry of the semiconductor material, thereafter referred to as the Hall plate. The plate dimensions could either be long, with the plate length greater than the width, or on the contrary, it could be short. Such an analysis will give us clarity on the variation of the physical effects in the device.

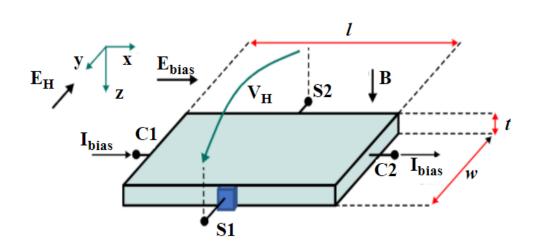

Figure 2.1: Rectangular semiconductor plate highlighting the generation of a transverse electric field when an out-of-plane magnetic field is applied.

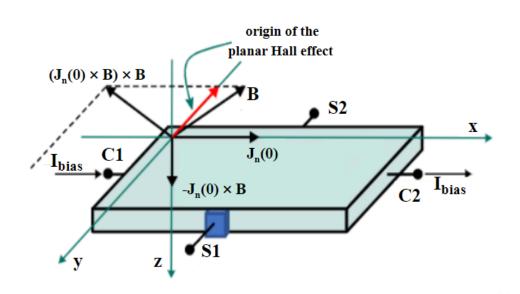

Let us consider a strong extrinsic n-type rectangular semiconductor (refer Fig.2.1) with electron concentration n, thickness t, width w, and length l, in which a current  $I_{bias}$  is forced to flow through the contacts C1 and C2 due to an external electric field  $\mathbf{E}_{bias}$ . When an orthogonal magnetic field  $\mathbf{B}$  is applied to the device, the Lorentz force acting on electrons is composed of the electrostatic and the magnetic components [10, 59, 60] respectively and can be described as:

$$\mathbf{F} = \mathbf{F}_{\mathbf{bias}} + \mathbf{F}_{\mathbf{mag}} \tag{2.1}$$

$$\mathbf{F} = -q\mathbf{E}_{\mathbf{bias}} - q(\mathbf{v} \times \mathbf{B}); \qquad (2.2)$$

Let us begin our analysis with a short device. From Fig.2.1, we get an idea that the device is compressed laterally between two bias current contacts.

Case I: Short Hall device  $(l \ll w)$  and an initial condition  $\mathbf{B} \approx 0$ , hence  $\mathbf{F}_{\mathbf{bias}} \gg \mathbf{F}_{\mathbf{mag}}$

To obtain the equivalent current densities in a short device  $(l \ll w)$ , the total equivalent Lorentz electrical force in eq.(2.2) is given by  $-q\mathbf{E}$  with  $\mathbf{E}$  being the total equivalent electric field component and so eq.(2.2) can be re-written as:

$$-q\mathbf{E} = -q\mathbf{E}_{\mathbf{bias}} - q(\mathbf{v} \times \mathbf{B}); \qquad (2.3)$$

where  $q = 1.6 \times 10^{-19}$  C is the electron charge and **v** the local velocity of the carriers due to the thermal agitation which is influenced by the drift velocity,  $\mathbf{v_{dn}} = \mu_n \cdot \mathbf{E_{bias}}, \mu_n$  being the drift mobility of the electrons. Since we follow the condition,  $\mathbf{F_{bias}} \gg \mathbf{F_{mag}}$ , most of the electric field is contributed to  $\mathbf{E_{bias}}$ . Multiplying the eq.(2.3) with  $-\mu_n \mathbf{n}$  we can arrive to the corresponding current density equation as a function of applied magnetic field:

$$-\mu_n nq \mathbf{E} = -\mu_n nq \mathbf{E}_{\mathbf{bias}} - \mu_n^2 nq (\mathbf{E}_{\mathbf{bias}} \times \mathbf{B})$$

(2.4)

From equation 2.4, we arrive at the definition of the corresponding total equivalent current density:

$$\mathbf{J}_{\mathbf{n}}(\mathbf{B}) = \mu_n n q \mathbf{E},\tag{2.5}$$

where the current density in the absence of magnetic field

$$\mathbf{J_n}(\mathbf{0}) = \mu_n n q \mathbf{E_{bias}} \tag{2.6}$$

and the contribution to overall current density due to the magnetic field is perpendicular to the current density component at  $\mathbf{B} = 0$

$$\mathbf{J}_{\mathbf{mag}} = \mu_n(\mathbf{J}_n(\mathbf{0}) \times \mathbf{B}) \tag{2.7}$$

Hence, the equivalent current density in the device from Eq.2.4,

$$\mathbf{J}_{\mathbf{n}}(\mathbf{B}) = \mathbf{J}_{\mathbf{n}}(\mathbf{0}) - \mu_n(\mathbf{J}_{\mathbf{n}}(\mathbf{0}) \times \mathbf{B})$$

(2.8)

**Case II:** Short Hall device  $(l \ll w)$  and  $\mathbf{B} \not\approx 0$ , hence  $\mathbf{F}_{mag} \gg \mathbf{F}_{bias}$

In this case, most of the bias electric field is masked by the magnetic field and so Eq2.4 is transformed accordingly as:

$$-\mu_n nq\mathbf{E} = -\mu_n nq\mathbf{E}_{\mathbf{bias}} - \mu_n \mu_n nq(\mathbf{E} \times \mathbf{B}); \qquad (2.9)$$

This implies an equivalent current density

$$\mathbf{J}_{\mathbf{n}}(\mathbf{B}) = \mathbf{J}_{\mathbf{n}}(\mathbf{0}) - \mu_n(\mathbf{J}_{\mathbf{n}}(\mathbf{B}) \times \mathbf{B})$$

(2.10)

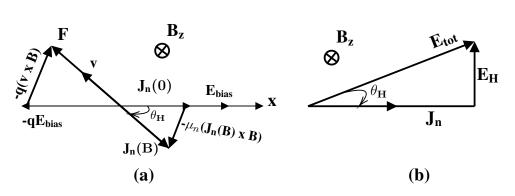

The current density when applied magnetic field,  $\mathbf{B} = \mathbf{0}$  is aligned to  $\mathbf{E}_{\mathbf{bias}}$ but the equivalent current density,  $\mathbf{J}_{\mathbf{n}}(\mathbf{B})$  is not collinear with  $\mathbf{E}_{\mathbf{bias}}$  and deflects at an angle, also referred to as the Hall angle,  $\theta_H$  [59] as can be observed in Fig.2.2(a). This is true for equations 2.8 and 2.10

$$\tan \theta_H = \mu_n \mathbf{B}_{\mathbf{z}}.\tag{2.11}$$

This results in a transversal current in the device with the magnetic electromotive force being shorted, thus nulling the Hall voltage. This is also known as the current deflection effect.

**Case III:** Long Hall device  $(l \gg w)$  such that  $t \sim 0$  and  $\mathbf{B} \not\approx 0$

Then most of the electric field in Eq. 2.3 along the longitudinal axis of the device is primarily due to the external bias  $\mathbf{E}_{\mathbf{bias}}$ . So, the associated current density

$$\mathbf{J_n} = q.\mu_n \mathbf{E_{bias}} \tag{2.12}$$

Writing the magnetic part of the Lorentz force without considering the thermal agitation, from eq(2.3) we obtain:

$$\mathbf{F}_{\mathbf{mag}} = -q.\mu_n [\mathbf{E}_{\mathbf{bias}} \times \mathbf{B}] \tag{2.13}$$

This magnetic part pushes the electrons toward one edge of the device along the y-direction, creating a space charge density gap across the edges in the device which creates an electric field  $\mathbf{E}_{\mathbf{H}}$  along y as shown in Fig.2.1. This electric field acts on the charges with a force

$$\mathbf{F}_{\mathbf{H}} = -q.\mathbf{E}_{\mathbf{H}} \tag{2.14}$$

that, at a steady state, counterbalances the magnetic action of the Lorentz

force. Hence, equating the equations 2.13 and 2.14,  $\mathbf{E}_{\mathbf{H}}$  can be expressed as

$$\mathbf{E}_{\mathbf{H}} \approx \mu_n(\mathbf{E}_{\mathbf{bias}} \times \mathbf{B}) \tag{2.15}$$

This generation of a transverse electric field under the influence of Lorentz force across a current carrying conductor due to an applied magnetic field normal to the conductor's surface is called the Hall-electric field. The total electric field in the device is given by

$$\mathbf{E_{tot}} = \mathbf{E_{bias}} + \mathbf{E_H} \tag{2.16}$$

which is not aligned with the applied  $\mathbf{E}_{\mathbf{bias}}$  and therefore is not aligned to the current density along the device from equation2.12 and this results in a deflection between  $\mathbf{E}_{\mathbf{tot}}$  and  $\mathbf{J}_{\mathbf{n}}$  as illustrated in Fig.2.2(b) referred to as the Hall angle,

$$\tan \theta_H = \frac{|\mathbf{E}_{\mathbf{H}}|}{|\mathbf{E}_{\mathbf{bias}}|} = \mu_n \mathbf{B}_{\mathbf{z}}$$

(2.17)

The Hall angle is a fundamental metric for the Hall effect devices, as it clearly expresses the perceptibility of the Hall effect with respect to the electrostatic bias. It is also identical for long and short Hall devices as derived from Eq.(2.11) and (2.17). It also clarifies that the mobility of the charge carriers, $\mu_n$  is a key parameter in the selection of a Hall device as it takes into care thermal agitation, scattering effects due to thermal agitation, and velocity distribution as will also be explained shortly. Now, if we include the contribution of the effect of thermal agitation of the carriers,

$$\mathbf{E}_{\mathbf{H}} \approx \mu_{H_n} (\mathbf{E}_{\mathbf{bias}} \times \mathbf{B}) \tag{2.18}$$

In this equation,  $\mu_{H_n}$  represents the Hall mobility of the carriers, which is a product of the drift mobility and the Hall scattering factor,  $r_H$  that differs by less than 20% from unity and considers the influence of the thermal motion

Figure 2.2: Vector diagram illustrating the Hall angle,  $\theta_H$  for an n-type semiconductor device (a) a short device: The Hall effect shows up through the tilting of the current density  $\mathbf{J_n}(\mathbf{B})$  with respect to  $\mathbf{E_{bias}}$ , (b) long device: the Hall effect develops through the tilting of the total electric field,  $\mathbf{E_{tot}}$  relative to  $\mathbf{E_{bias}}$  and the current density,  $\mathbf{J_n}$ , which in this case, are collinear in the sample.

of carriers and their scattering on the Hall-effect,

$$\mu_H = \mu_n r_H \tag{2.19}$$

Thus, from equations 2.15 and 2.18, the Hall electric field is proportional to the external electric and magnetic fields with a proportionality constant of carrier mobility. So, in order to have a high mobility characteristic for a Hall device, we would usually prefer n-type semiconductor than a p-type.

Further, by accounting for (2.15), the Hall effect in a device ultimately results in a transverse Hall voltage between contacts S1 and S2:

$$V_H = \int_{S_1}^{S_2} \mathbf{E}_{\mathbf{H}} \, dy = \frac{\mu_n}{\sigma t} I_{bias} B_z = \frac{1}{nqt} I_{bias} B_z. \tag{2.20}$$

with  $\sigma = nq\mu_n$  being the electrical conductivity which also contains information on the geometrical magnetoresistance effect, as will be discussed shortly. From equation 2.20, we can clearly understand that  $V_H$  is directly proportional to the vertical magnetic field and the applied bias, and inversely proportional to the geometrical/physical parameters of the device. So, in order to increase the output Hall voltage, the device must feature low carrier concentration and be as thin as possible. This is the reason, Hall-effect devices are usually referred to as Hall plates. Including the thermal agitation of the carriers and include Hall mobility as in equation 2.19 in Equation 2.20, we obtain another expression for  $V_H$  introducing the Hall coefficient,  $R_H = r_H/nq$  as:

$$V_H = \frac{r_H}{nqt} I_{bias} B_z = R_H \frac{I_{bias}}{t} B_z, \qquad (2.21)$$

With the definition of the transversal Hall voltage, we conclude with the primary contributor of the galvanomagnetic effects.

Let us now forego our earlier assumptions of orientations of an applied orthogonal magnetic field, **B** and the external field, **E**<sub>bais</sub> and try to interpret the current density components. If we observe in Fig.2.2(a), for short Hall plates, the current deflection due to the magnetic field, causes an attenuation of the current density such that  $J_n(0) > J_n(B)$ . Similarly, for a long device, the current deflection effect creates a longer path for the current density lines and adds a greater effective longitudinal resistance and therefore attenuates them in the presence of magnetic field. This is known as the magnetoresistance effect. It can be shown that,  $J_n(B)$  is a function of the effective conductivity of the semiconductor,  $\sigma_B$  and to determine the factor by it is attenuated, we solve the eq.2.10 with respect to  $J_n(B)$ :

$$J_n(B) = \frac{J_n(0) - [J_n(0) \times B] - B[J_n(0) \cdot B]}{1 + (\mu_n B)^2}$$

(2.22)

For a perpendicular magnetic field,  $[J_n(0).B] = 0$ , hence

$$J_n(B) = \frac{J_n(0) - [J_n(0) \times B]}{1 + (\mu_n B)^2}$$

(2.23)

$$J_n(B) = \frac{n\mu_n q E_{bias} - n\mu_n^2 q [E_{bias} \times B]}{1 + (\mu_n B)^2}$$

(2.24)

The conductivity of the n-type semiconductor is given by

$$\sigma = n\mu_n q \tag{2.25}$$

Figure 2.3: Graphical representation of the planar Hall effect

and effective conductivity,  $\sigma_B$

$$\sigma_B = \frac{\sigma}{1 + (\mu_n B)^2} \tag{2.26}$$

Hence, eq2.24 can be expressed to define the magnetoresistance effect:

$$J_n(B) = \sigma_B E_{bias} - \sigma_B \mu_n [E_{bias} \times B]$$

(2.27)

Another effect characteristic of Hall devices is that they are sensitive to not only the magnetic field incident perpendicular to their surface, but also to a field aligned to the plane of the Hall plate. This is referred to as the Planar effect [61] and corresponds to a deflection of current (and related generation of induced electric field) collinear with the magnetic field **B**. This effect can be easily observed in Fig. 2.3 by assuming that the magnetic field is in-plane with the bias current (i.e., on the x-y plane). In this case, due to the Lorentz force, the bias current generates a component of  $\mathbf{J}_n$  in the z-direction that, in turn, causes the generation of another deflection current by magnetic action in the x-y plane, decomposed into  $J_x$  and  $J_y$ . This last term will produce a Hall voltage that is transverse to the bias current, but in-plane with the magnetic field contributing an error in the sensed voltage. If we invalidate the hypothesis of negligible device thickness, all the threedimensional components of the magnetic field **B** should be taken into account in the solution of Eq.(2.4). In this case, it can be demonstrated that the current density in the device can be written as [59]:

$$\mathbf{J}_{\mathbf{n}}(\mathbf{B}) = \sigma_B \mathbf{E}_{\mathbf{bias}} - \mu_H \sigma_B (\mathbf{E}_{\mathbf{bias}} \times \mathbf{B}) + Q_H (\mathbf{E} \cdot \mathbf{B}) \mathbf{B}$$

(2.28)

where the third term is referred to as the planar Hall effect, and  $Q_H$  is the planar Hall-current coefficient.

This effect is usually negligible in Hall plates, which are the devices exploiting the Hall effect to realize a magnetic sensor and it has been shown that specific crystal orientations and the geometry of vertical Hall devices would counteract to an extent of an order of magnitude, the influence of such planar Hall voltage compared to the plate-shaped devices.

Finally, galvanothermomagnetic effects are characterized non-isothermally and include the Ettingshausen effect, which is the appearance of a transverse temperature gradient in a sample as a consequence of a Hall effect taking place in the sample; the Nernst effect, which is the generation of a voltage in a Hall device with the heat flow replacing the current; and the Righi–Leduc effect, which is a thermal analogue of the Hall effect. An in-depth analysis of these effects is not within the scope of this thesis, nevertheless, a rigorous and detailed description can be found in [59]. Now that we have an understanding of the physical effects that take place within the device, let us enquire into the composition of the device, the possible materials for construction and their role in device performance. The following sections will furnish the reader with information regarding the conventional technologies used to realize Hall devices with considerations to their possible geometries.

#### 2.2 Materials

The choice of device material plays a significant role in originating the Hall effect [10, 59, 60, 62, 63]. As also pointed out earlier, the equation (2.20)

| Material | $\mu (\rm cm^{-2} V^{-1} s^{-1})$ | $n (\mathrm{cm}^{-3})$ | $R_H \ (\mathrm{cm}^{-3}\mathrm{C}^{-1})$ |

|----------|-----------------------------------|------------------------|-------------------------------------------|

| doped Si | 1500                              | $2.5 \times 10^{15}$   | $2.5 \times 10^3$                         |

| InSb     | 80000                             | $9 \times 10^{16}$     | 70                                        |

| InAs     | 33000                             | $5 \times 10^{16}$     | 125                                       |

| GaAs     | 8500                              | $1.45 \times 10^{15}$  | $2.1 \times 10^3$                         |

Table 2.1: Characteristics (at 300 K) of semiconductors used for Hall-effect sensors.

clearly shows that the Hall voltage is directly proportional to the carrier mobility, and that it is inversely proportional to conductivity and carrier concentration.

Metals are characterized by carrier concentrations (e.g.,  $n = 8.4 \times 10^{22} \text{cm}^{-3}$  for copper), which are orders of magnitude higher than those present in intrinsic semiconductor materials (e.g.,  $n \approx 1 \times 10^{10} \text{cm}^{-3}$  for intrinsic silicon), thus resulting in a very low Hall voltage.

Suitable candidates for HECS devices are, instead, semiconductor materials like silicon (preferebly the n-type) and III-V compounds (e.g., InSb, GaAs, InAs) with high mobility and relatively low conductivity. Apart from having a choice of the dominant charge carriers, using doped semiconductor materials is beneficial primarily because in pure semiconductors, the carrier concentration is highly influenced by temperature, while doping changes this property and instead makes it a function of dopant concentration which is fixed and usually constant over temperature. Table 2.1 reports the mobility, the average carrier concentration, and the Hall coefficient of semiconductors typically used for HECS devices. Nevertheless, it should be noted that low energy bandgap materials usually show high mobility but also high carrier concentration, leading to a trade-off. Moreover, when choosing the device material, the designer must consider compatibility with the available semiconductor technologies in terms of integrability, economic feasibility, and reliability.

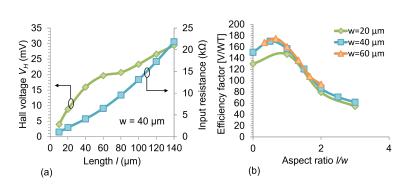

**Figure 2.4:** (a) Variation of Hall voltage and input resistance with device length for a 40  $\mu$ m wide Hall plate biased at 500  $\mu$ A under 50 mT of out-of-plane field (b) Device efficiency as a function of its aspect ratio.

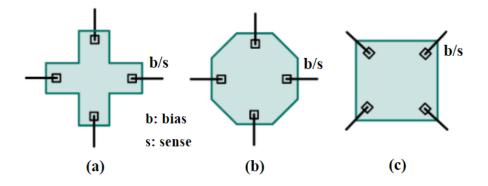

Figure 2.5: Different geometries of the active area (i.e., n-type well) for Hall plates: a) cross b) octagonal c) square with contacts on the angles

## 2.3 Hall plate technology

The Hall probe is a four-terminal solid-state device that relies on the Hall effect discussed in Sec. 2.1. Equation (2.21) was obtained for an ideal device characterized by  $l \gg w$ , negligible contacts, and unconstrained by any specific technology process. However, the technological aspects are important when dealing with the implementation of the sensing device [64]. In this Section, the analysis will focus on CMOS technology, but similar considerations can be applied to other semiconductors.

A real Hall-effect device cannot be assumed infinitely long, and at least four contacts are needed to realize a Hall plate. Two contacts are necessary for the flow of electrical energy, also called bias contacts, and two sense contacts positioned orthogonally and at equipotential points at the plate boundary. Their sizing is crucial for the Hall plate and affects the basic plate structure, for if they are too large, the sense contacts may create local short circuits with the bias current, thus reducing the Hall voltage, and on the contrary if they are too small, then the material resistance surrounding the contact contributes a high resistance relative to the device as a whole [23]. Their doping concentrations also play a role, as highly doped sense contacts create space charge regions that lower the measurable Hall voltage [65]. The effects of the implemented shape are taken into account by defining the Hall geometrical factor [59],

$$G_H = \frac{V_H}{V_H^{\infty}} \tag{2.29}$$

as the ratio between the actual Hall voltage  $(V_H)$  and that generated by an infinitely long Hall device  $(V_H^{\infty})$ . Therefore, the Hall voltage of a generic Hall plate can be expressed as

$$V_H = \frac{G_H R_H}{t} I_{bias} B_z. \tag{2.30}$$

The exact value of  $G_H$  depends on the shape of the device, on the sizing and position of the contacts, and also on the Hall angle,  $\theta_H$  as also discussed in [59]. The  $G_H$  factor of a specific device shape can be analyzed by using different techniques, e.g., conformal mapping [59], boundary element methods, or finite element methods (FEMs) [64,66]. Some general design rules are summarized in [64]. Following the definition of  $G_H$ , the longer the device, the higher the Hall voltage, up to the theoretical limit (see Fig. 2.4a). However, increasing the length of the device also increases the input resistance (also observed in Fig. 2.4a). In this case, a higher bias voltage is required to force the same  $I_{bias}$ , causing an overall raise in power consumption. This trade-off is well represented by the efficiency factor  $\eta$  (also known as power-related sensitivity):

$$\eta = \frac{V_H}{V_{bias}I_{bias}B},\tag{2.31}$$

which shows a local maximum for an aspect ratio  $l/w \simeq 1$  (see Fig. 2.4b). Therefore, highly symmetrical shapes are preferred from an energy perspective. Moreover, symmetric devices are easier to fabricate, and symmetry can be also exploited to improve the final performance of the sensor.

In this context, FEM analyses revealed that, for a generic square shape, the  $G_H$  factor can be maximized by using large bias contacts (as large as half the width of the device) and small sense contacts placed at half the length of the device [58]. However, this compromises the perfect symmetry of the plate, and small sense contacts are more susceptible to misalignment errors, giving rise to an additive offset voltage. Figure 2.5 reports on the Hall plate geometrical aspects and their optimization, while an in-depth analysis can be found in [67–72]. The cross shape was demonstrated to achieve high values of  $G_H$  even employing large sense contacts, while the square shape displayed higher sensitivity values.

Regardless of the chosen shape, the Hall plate is meant to be a bidimensional device with negligible thickness. In standard CMOS implementations, the Hall probe is usually realized by a low-doped n-type well because of the higher mobility with respect to p-type wells. The thickness is defined by the diffusion depth set by the CMOS process, and cannot be changed by the designer [37]. The n-type active well is encapsulated in a p-type layer, which could be the epitaxial substrate or an isolation layer. In any case, the encapsulation in the p-type well originates a pn junction with its corresponding depletion layer, which lowers the effective thickness of the Hall probe and makes it non-constant along the Hall plate [58, 72, 73]. Moreover, it causes spurious dependencies on the bias and the magnetic field by means of the magnetoresistive effect and the junction field effect, leading to nonlinearity [74,75]. The p-type layer can be reverse-biased to enlarge the depletion layer, reduce the effective thickness, and increase the sensitivity. However, the achievable improvement is negligible with respect to the increased complexity of the electronics. Alternatively, the effective thickness can be reduced by placing a shallow trench isolation on top of the active layer, or can be modulated by covering the n-well with a thin p-type implantation layer (which creates another depletion region) or a poly gate inducing

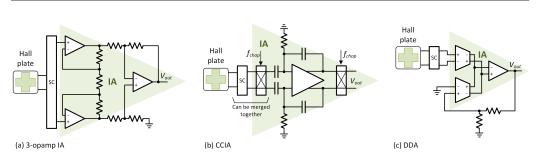

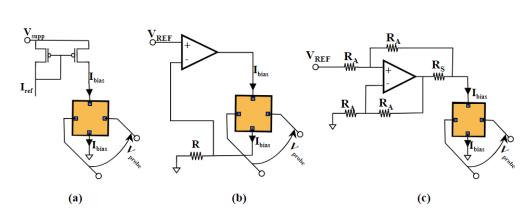

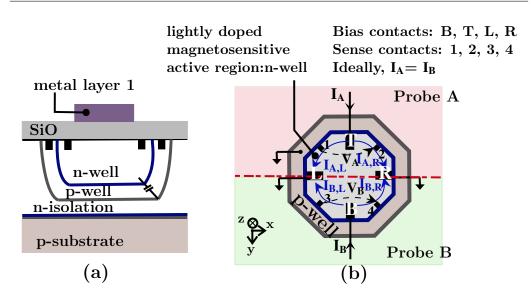

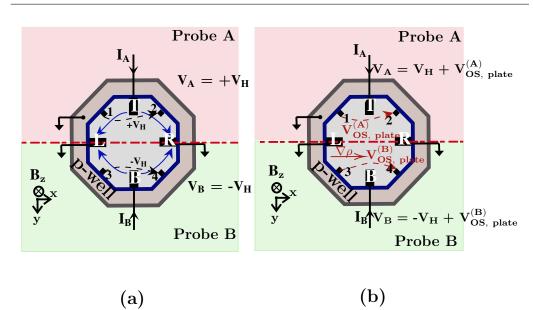

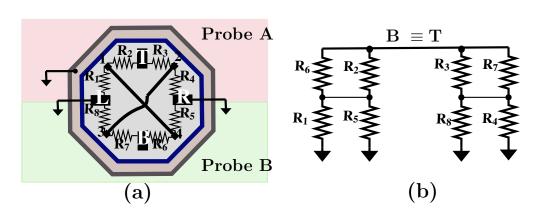

a field effect [72,73]. In all the cases, an equivalent capacitance can be associated to the depletion region, setting a fundamental bandwidth limit for the HECS [36,76,77]. Taking our attention to interfacing a Hall device, the bias contacts must be connected to a current source with high output impedance and the sense contacts connected to a high input impedance AFE for sensing the Hall voltage without sinking current, although alternative configurations can be developed [78–80]. This constraint is applicable when the Hall plate is configured in voltage mode, however, when its dual is implemented as current mode, the criteria of the impedance of the AFE changes to low impedance as will be discussed in the next sections and also is the subject of this project.

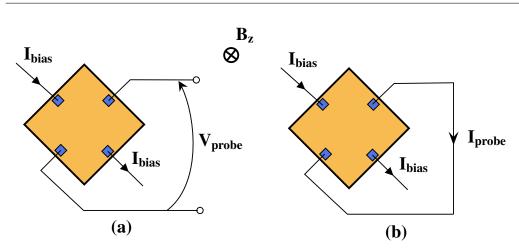

## 2.4 Operating modes

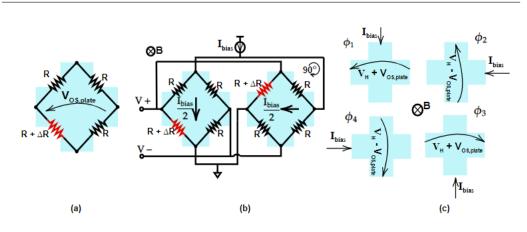

The output signal of a Hall-effect device can be generated in one of the two complementary configurations: The voltage mode or the current mode. The earlier discussions related to the general concepts of the Hall effect where in the output signal was a Hall voltage is the most conventional configuration of the Hall sensor. When the output signal is its dual, i.e, a Hall current obtained by shorting of the sense contacts such that the Hall voltage is forced to be zero, the Hall sensor is said to be configured in the current mode. The two configurations are illustrated for a square shaped Hall plate biased with a current,  $I_{bias}$  in the presence of a magnetic field,  $B_z$  in Fig.2.6. Their respective output signals are a sum of the Hall signal: Hall voltage,  $V_H$  or a Hall current,  $I_H$  and the plate offset,  $V_{OS,plate}$  and are given as follows <sup>1</sup>:

$$V_{probe} = V_H + V_{os,plate} \tag{2.32}$$

$$I_{probe} = I_H + I_{os,plate} \tag{2.33}$$

It is to be noted that the current related sensitivities of the two configurations are different and incomparable. The sensitivity of a sensor biased with voltage in voltage mode and a sensor biased with current in current mode

<sup>&</sup>lt;sup>1</sup>Note:  $V_{probe}$  and  $I_{probe}$  are interchangeably used with  $V_{sense}$  and  $I_{sense}$  respectively

Figure 2.6: Square shaped Hall-effect device configured in (a) Voltage mode, (b) Current mode

has been compared as it has been found in literature based on equating the units of the derived results [81], but this is not a fair comparison because the biasing conditions affects the temperature-magnetic cross sensitivity and linearity of the device. Usually, high-mobility, thin-film semiconductor materials with a small band-gap are intrinsic at room temperature and usually biased by a voltage source that results in a low temperature-magnetic crosssensitivity. But their device current has a very high temperature coefficient, and therefore is susceptible to thermal breakdown. Other semiconductor materials such as silicon and GaAs, on the contrary, are strongly extrinsic at nominal temperature and the temperature-magnetic cross-sensitivity of a current biased Hall device is much smaller than that of a voltage-biased device [59]. This is also a primary reason for our choice of current biasing in this project as will be discussed in the next chapters.

The following mathematical formulations hold true for the sensitivity of the Hall device:

Voltage-related sensitivity, when biased by voltage,  $V_{bias}$  in voltage mode

$$S_V^V = |\frac{V_{probe}}{V_{bias} \times B_z}| \quad [V/VT] = [T^{-1}]$$

(2.34)

Voltage-related sensitivity, when biased by voltage in current mode

$$S_V^I = \left| \frac{I_{probe}}{V_{bias} \times B_z} \right| \quad [A/VT] \tag{2.35}$$

Current-related sensitivity, when biased by  $I_{bias}$  in voltage mode

$$S_I^V = \left| \frac{V_{probe}}{I_{bias} \times B_z} \right| \quad [V/AT] \tag{2.36}$$

Current-related sensitivity, in current mode

$$S_I^I = \left| \frac{I_{probe}}{I_{bias} \times B_z} \right| \quad [A/AT] = [T^{-1}] \tag{2.37}$$

More elaborate discussion on the operating modes can be referred in sections 3.3 and 4.

## 2.5 Horizontal versus Vertical Hall sensors

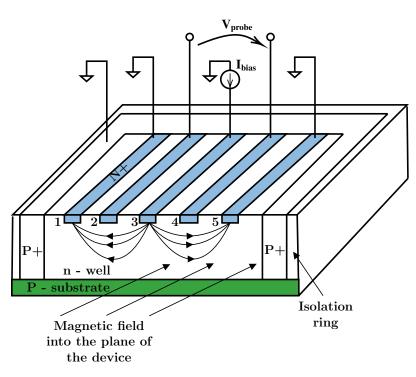

In contrast to the conventional structuring and usage where the magnetic field to be measured is perpendicular to the plate surface, specific applications would require measuring the magnetic field which could be parallel to the plate surface or is non-homogenous over the volume of Hall device. In other words, a multi-axis sensor on a single semiconductor wafer may be required. Non-plate-like or vertical or in other terms 3-D Hall devices fulfill this sensing requirement by adapting to conform to the shape of the magnetic field. Fig. 2.7 illustrates a vertical Hall device with five contacts. In the presence of magnetic induction, now planar to the device surface, and normal to the applied bias current, which arches across the device and sinks into the ground through contacts 1 and 5 resulting in the Hall signal between the sense contacts 3 and 4. To create a three axis sensitivity, a pair of these devices aligned to each other by  $90^{\circ}$  can be used with the horizontal Halleffect device [30]. However, it is worth highlighting that the vertical Hall devices lack the general four-way symmetry that is present in the horizontal devices and the sensitivity when configured in voltage mode is usually lower

Figure 2.7: Vertical Hall-effect transducer with five contacts

in contrast to the configuration in current mode [81].

## 2.6 Hall - Effect Current Sensor

Having gained an understanding of the composition of a Hall device, the various factors that contribute to the sensed Hall voltage and the possible technologies for realizing it and the various modes it can be configured with their corresponding sensitivities, we must also realize that the Hall plate cannot be used for current or magnetic field sensing as a standalone for a practical application. This is because the sensed signal is a small quantity that must be amplified with an appropriate microelectronic readout circuitry for usability. Moreover, the sensed voltage or current is a sum of the actual Hall electric output with an offset (refer Eq.2.32 and 2.33), which is usually orders of magnitude higher than the usable Hall signal itself. With these technicalities, one must not be disinclined, because unlike most sensing techniques the realization of the Hall sensor is quite easy to implement and integrate

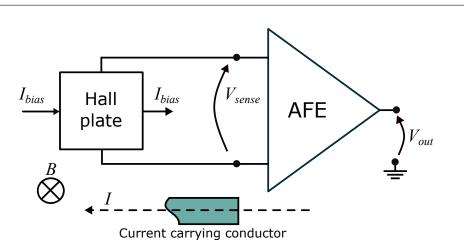

Figure 2.8: Typical sensing chain of the HECS, consisting of the current-to-magnetic field transduction, the Hall plate, and the AFE.

with standard CMOS or BCD processes which gives a strong motivation for the design of the supporting circuits for amplification and trimming of the offset. Before gaining an insight into the realization of the HECS, Fig.2.8 recalls the overall HECS system block diagram. For an overview, the chain includes the magnetic field induction on the Hall plate for the generation of the Hall electric output. The offset within the output must be trimmed and the useful signal read and amplified. A detailed description follows:

## 2.6.1 Current-to-Magnetic Field Transduction

The transduction from current to magnetic field is based on the Ampere's circuital law. In the magnetostatic case, and considering the simple example of a conductor of infinite length and negligible cross area traversed by a constant current I, the Ampere's law can be simplified by using the Biot-Savart formula:

$$|\mathbf{B}(r)| = \frac{\mu_0 \mu_r I}{2\pi r}; \tag{2.38}$$

where  $\mu_0$  is the magnetic permeability of the vacuum,  $\mu_r$  is the relative permeability of the media surrounding the current conductor, and r is the distance between the conductor and the point in space at which the magnetic field is sensed/evaluated. The Ampere's law and its derivations state that it is always possible to indirectly estimate a current by sensing the associated magnetic field at a known distance r. However, magnetic interferences may corrupt (2.38) with an additive term, affecting the selectivity of the HECS.

The current-to-magnetic field transduction factor,  $G_{ib}$  is of paramount importance in HECSs, as it can affect many sensor metrics, e.g., sensitivity, input full-scale range, and MDS. For the example above, it can be defined from (2.38) as

$$G_{ib} = \frac{|\Delta \mathbf{B}(r)|}{\Delta I} = \frac{\mu_0 \mu_r}{2\pi r},$$

(2.39)

highlighting a direct dependence of  $G_{ib}$  to the exact distance of the sensor from the conductor by means of the parameter r. This dependence may cause many issues like increased sensitivity to mechanical noise and nonlinear effects. While (2.39) reports the transduction factor for a simple academic case, an accurate analysis of the magnetic circuit and geometries are required for getting the exact formulation of  $G_{ib}$  in practical cases. Usually, the  $G_{ib}$ factor should be maximized to improve the MDS and sensitivity, and should be made insensitive to thermo-mechanical effects.

Moreover, the magnetic environment should be designed to reduce the sensitivity to external EMI. In general, the use of a core allows to shunt stray magnetic fields around the sensor. Conversely, coreless architectures are susceptible to stray fields from high-current carrying traces, which may be captured by the Hall plate and eventually cause inaccurate current measurements. In this case, a differential Hall plate configuration can be employed, although any mismatch between the Hall plates, or any field disuniformity, will result in a deviation in the output signal. In the following, the most used and important arrangements employed in HECSs are briefly summarized.

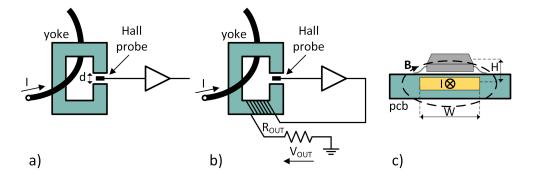

#### Yoke-Hall

An arrangement combining a Hall plate with a gapped magnetic yoke is shown in Fig. 2.9a [29, 82–84]. Specifically, the magnetic core is clamped around the current-carrying conductor (i.e., a wire or a busbar), and all the magnetic flux generated by the current I is concentrated on the core itself and focused on the Hall plate, which is placed in the air gap of the magnetic core. This arrangement is named open-loop configuration and changes the equation of the magnetic field on the Hall plate as follows:

$$|\mathbf{B}| = \frac{\mu_0 \mu_r I}{2\pi (r-d) + d\mu_r},$$

(2.40)

where d is the thickness of the air gap, while the distance r can be usually approximated with the yoke diameter. A good design satisfies the inequality  $d\mu_r \gg 2\pi r$ , allowing to simplify (2.40) in

$$|\mathbf{B}(r)| = \frac{\mu_0 I}{d},\tag{2.41}$$

which is independent of the relative position of the wire. By comparing (2.41) and (2.38) in free space, it is possible to notice that  $G_{ib}$  in the yoke-Hall open-loop configuration has been increased by a factor  $2\pi r/d$ , and that it can be increased even further by wounding the wire around the yoke. This arrangement offers  $G_{ib}$  factor as high as 1 mT/A and it is robust against EMI, but the bandwidth, weight, and space are affected by the presence of the yoke, which also suffers from magnetization in case of large over-current events.

The closed-loop configuration, also known as zero-flux sensor, copes with this last issue [13, 29, 82–84]. In this case, the output of the Hall probe drives a secondary coil wound around the magnetic core, in order to null the magnetic flux density inside the core (Fig. 2.9b). This arrangement still exploits the advantages given by the core to improve the sensitivity and to reduce the dependency on the geometry, as well as the sensitivity to EMI. It should be noted that the Hall plate is placed in the feedback loop, so that the output of the HECS is the voltage potential on the output resistor. Moreover, this arrangement resembles a CT at high frequencies [84, 85], improving the bandwidth. Nevertheless, its usage is not straightforward in modern applications given the weight and space occupation.

#### Yoke-less open-loop sensor

A more compact arrangement can be obtained by realizing a yoke-less open-loop configuration at PCB level, as shown in Fig. 2.9c. [29, 48, 86–91]. In this case, the current-carrying conductor is realized as a trace on the top conductive layer of the PCB (or on a separated bus bar) and the Hall probe is implemented as an integrated circuit (IC) placed vertically on top of the trace in order to maximize the  $G_{ib}$  factor. Thus, the  $G_{ib}$  factor for this configuration can be approximated as [87]:

$$G_{ib} = \frac{\mu_0}{2(W+2H)};$$

(2.42)

where W is the trace width and H is the trace-to-sensor distance. Yet, package-to-PCB clearance as well as package and die thicknesses usually imply H > 0.3 mm [91]. Typical values of  $G_{ib}$  factor are in the order of 100  $\mu$ T/A. However, multi-layer/multi-turn techniques, as well as ferromagnetic shields [87] can be used to further increase the  $G_{ib}$  factor by concentrating the magnetic field on the Hall probe.

An important implication of the PCB approach is that the magnetic field lines on the Hall probe lie on the x-y plane, while the Hall plate is sensitive to the out-of-plane field. Thus, it is required to either rotate the Hall IC or bend the field lines. The usage of a through-hole package for the sensor allows to rotate the Hall IC and place it vertically with respect to the board

**Figure 2.9:** a) Open-loop HECS with magnetic yoke. b) Closed-loop HECS with magnetic yoke. c) Open-loop yoke-less HECS with current-carrying trace realized at PCB level.

plane. However, this technique increases the trace-to-probe distance above 1 mm.

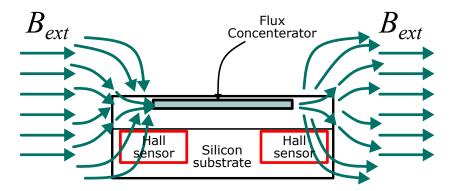

Alternatively, it is possible to integrate magnetic flux concentrators (IMCs) in the same IC used for the Hall probe [49, 50, 92–94]. IMCs are thin layers  $(10 - 100 \ \mu\text{m})$  of high-permeability ferromagnetic material spattered over the silicon die. The magnetic field lines converge on one edge of the magnetic material and diverge on the opposite one. Hence, the field lines bend in the proximity of the flux concentrator edge, creating a convenient positioning for the Hall plate (Fig. 2.10). Moreover, the concentration of the field lines lead to an amplification of the magnitude of the magnetic field, with an amplification factor depending on the shape and thickness of the concentrator, on the relative position of the Hall device, and on other geometical factors. Magnetic gain values from 5 to 10 are reported in the literature [49, 92]. It should be noted that IMC can suffer from the saturation of the ferromagnetic material, making the  $G_{ib}$  factor nonlinear at high-field, hence limiting the full-scale range.

#### Open-loop sensor with on-chip trace

To reduce the trace-to-probe distance down to a few  $\mu$ m, it is possible to integrate the current-carrying trace and the Hall probe within the same IC [32, 77, 95, 96] by exploiting thick copper layers [97], redistribution layers

Figure 2.10: 2D representation of the magnetic effects of IMCs. The flux lines due to the external magnetic field are bended and concentrated into the IMC, where the flux density is higher.

in wafer-level packaging, or copper frames. However, when placing the Hall plate at the minimum allowed distance, i.e., vertically beneath the trace, the out-of-plane field acting on the probe is zero. As IMCs and other magnetic techniques cannot be exploited at such a small scale, the only possible solution is moving the probe laterally away. This will increase the trace-to-probe distance and lower the magnitude of  $\mathbf{B}$ , but the component of the field on the z-axis will increase, leading to a design trade-off.

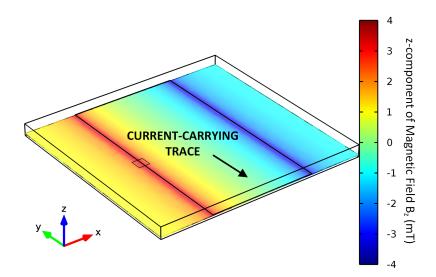

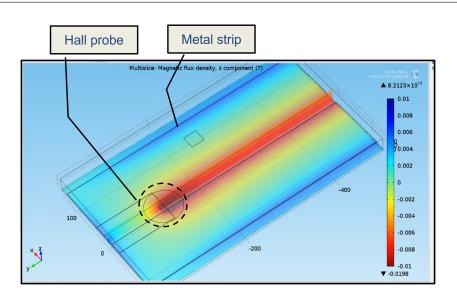

Figure 2.11 reports the z-component of the field at the silicon-oxide interface beneath the trace, showing that the optimum position for the Hall probe is exactly below the edge of the current-carrying trace. This geometrical arrangement also implies that the magnetic field on the Hall probe is not confined to the z-direction, and a non-negligible in-plane field will arise. This could trigger spurious behaviour at the probe level, like planar Hall effects (see Sec. 2.1).

The integration of the trace and probe on the same IC provides a good rejection of mechanical noise, allowing to assume a noiseless I - B transduction, given the precise and stable definition of the relative distance. On the other hand, the lack of magnetic circuits makes the HECS sensitive to exter-

**Figure 2.11:** Bidimensional map of the  $B_z$  field computed at the silicon-oxyde interface 10  $\mu$ m beneath the copper current-carrying trace. The map shows a maximum of the  $B_z$  field at the vertical projections of the edge of the trace.

| Table 2.2:         Full | -scale ranges for | r open-loop | current sensors. |

|-------------------------|-------------------|-------------|------------------|

|-------------------------|-------------------|-------------|------------------|

| Technical Solution                   | Typical Input Full-scale Range        |  |

|--------------------------------------|---------------------------------------|--|

| Open-loop HECS with yoke             | up to 700 A                           |  |

| Bus bar with magnetic shield         | From 50 A to 700 A $$                 |  |

| On-board PCB trace                   | From $10 \text{ A}$ to $50 \text{ A}$ |  |

| On-board PCB trace with multi-turn   | From $2 \text{ A}$ to $10 \text{ A}$  |  |

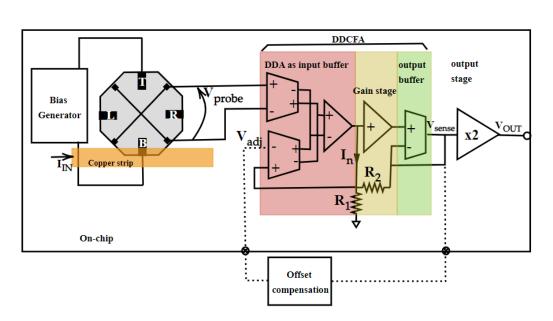

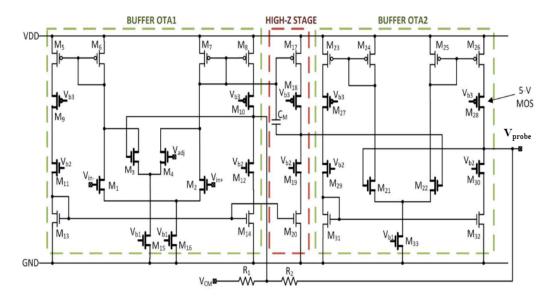

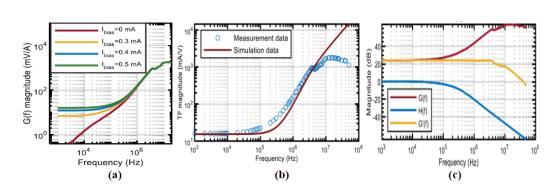

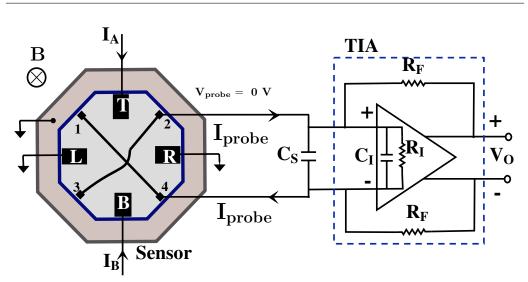

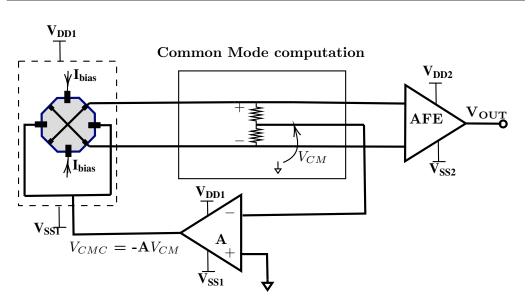

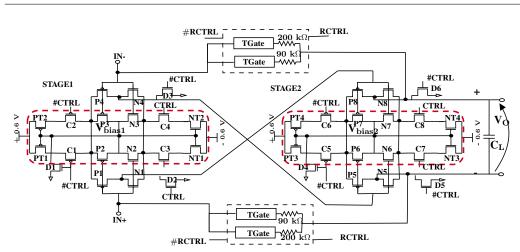

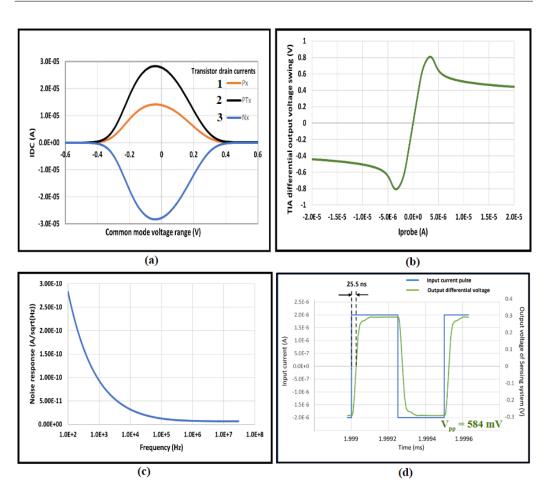

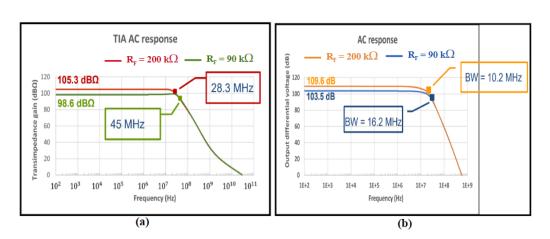

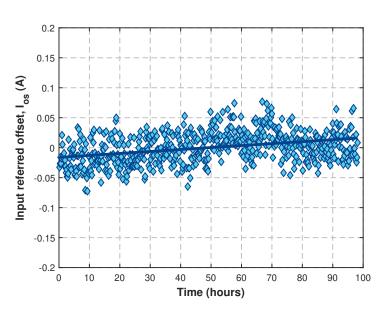

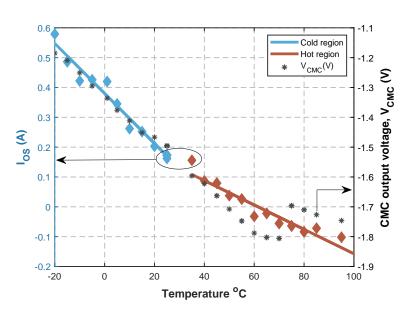

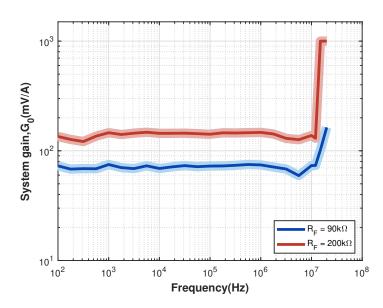

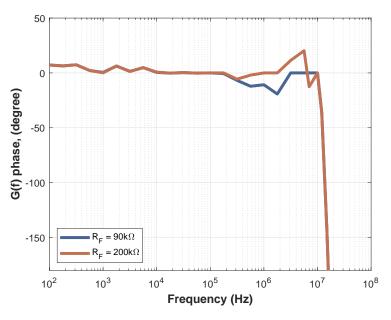

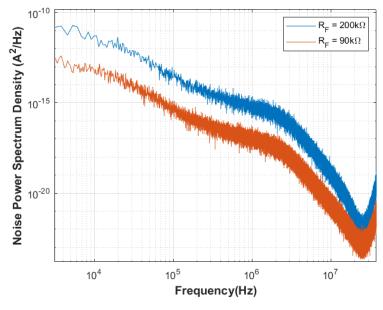

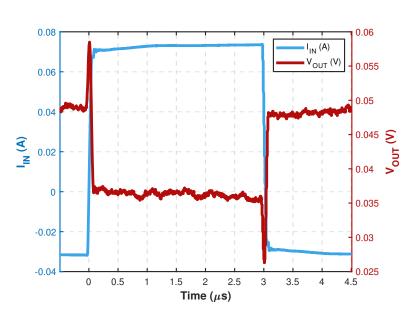

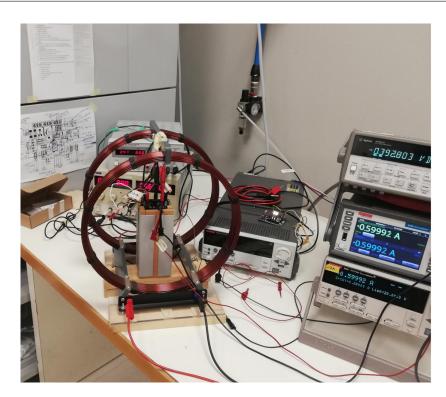

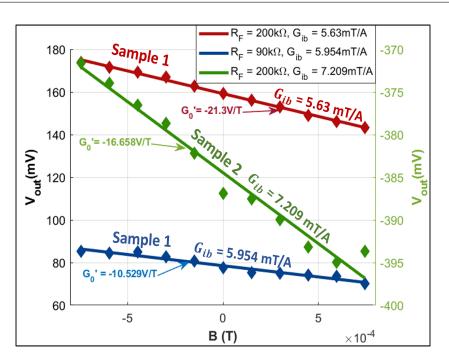

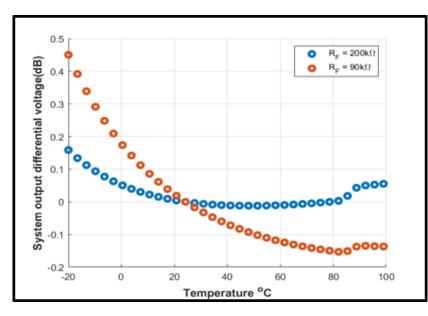

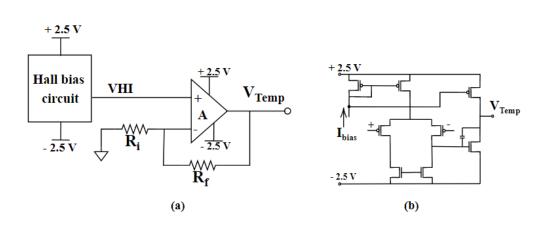

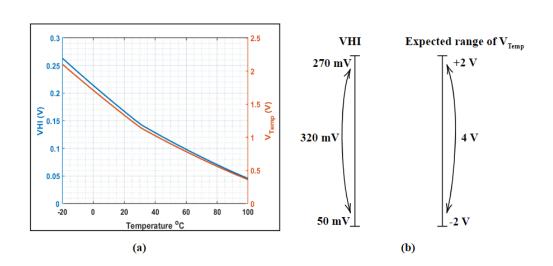

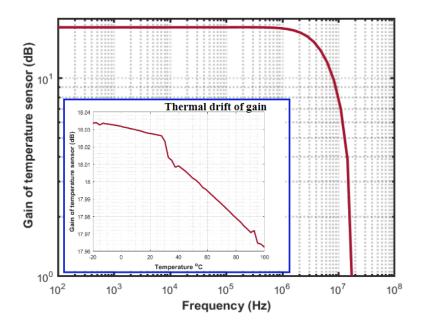

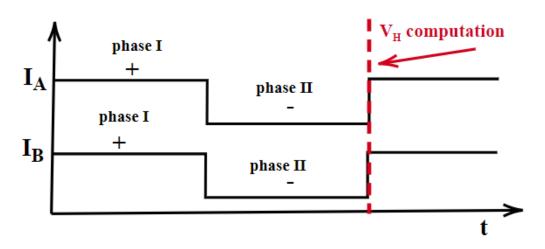

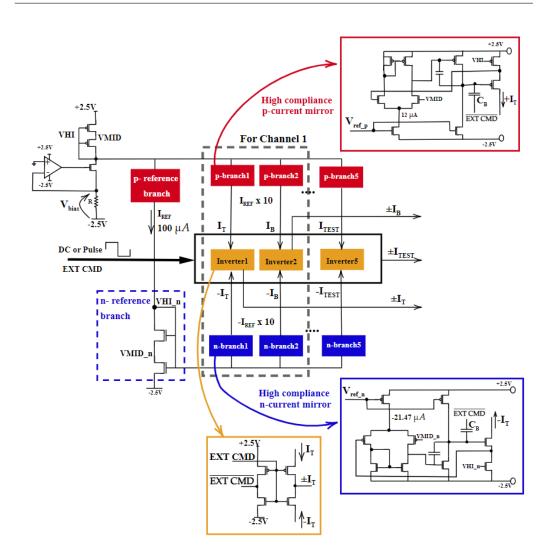

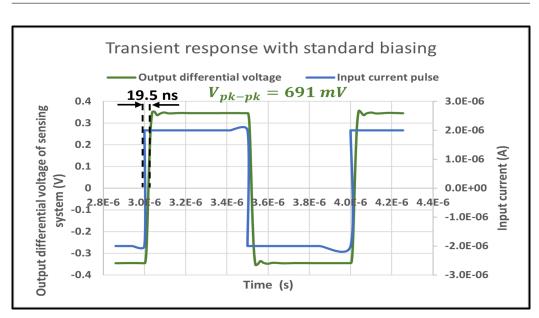

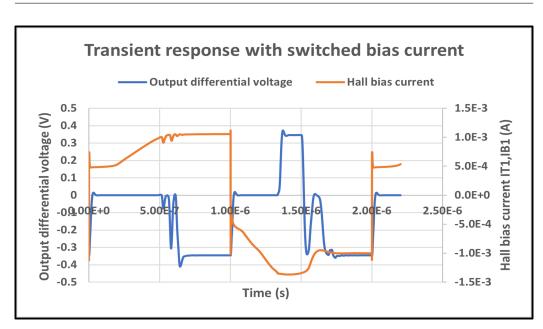

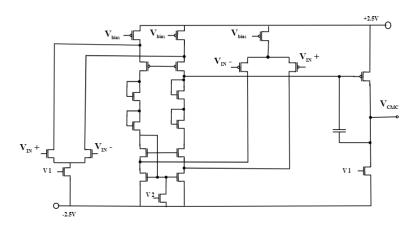

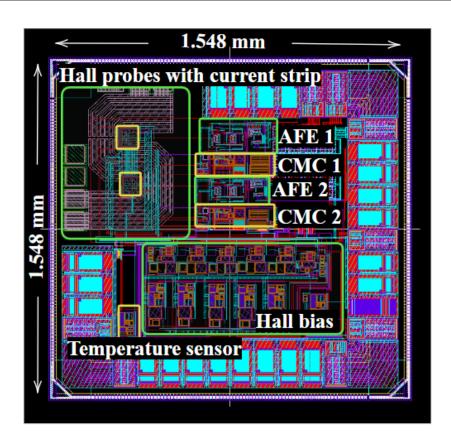

| open-loop sensor with trace on WLCSP | < 20 A                                |  |