#### ALMA MATER STUDIORUM - UNIVERSITÀ DI BOLOGNA

#### Dottorato di Ricerca in

#### MONITORAGGIO E GESTIONE DELLE STRUTTURE E DELL'AMBIENTE - SEHM2

#### XXXIII Ciclo

Settore Concorsuale: 08/B1 - Geotecnica

Settore Scientifico Disciplinare: ICAR/07 - Geotecnica

# A GENERAL FRAMEWORK FOR IOT-READY GEOTECHNICAL OBJECTS

Presentata da: Giacomo Mazzoni

**Coordinatore di Dottorato**

Prof. Ing. Alessandro Marzani

Supervisore

Prof. Ing. Laura Tonni

Co-supervisore

Dott. Giulio Dal Forno

Esame finale anno 2021

#### **Foreword**

In this thesis the outcomes of a 3-year research and development project hosted at ENVIA in collaboration with SEHM2 (Structural and Environmental Health Monitoring & Management) PhD program at Alma Mater Studiorum - University of Bologna are presented.

The project focuses on the relationship between current IoT trends and geotechnics within the civil engineering context. A simple framework for geotechnical data exchange tailored to IoT applications, potentially suitable for both small to large scale structural and infrastructural scenarios, has been prototyped. Within such scenarios further a special case of data generation from sensor-enabled geosynthetics has been explored.

The framework is primarily based on the data exchange open standards of Geographical Information Systems (GIS) and Building Information Modeling (BIM). In particular, it entails an extension of the current AGS4 data exchange format through a novel AGS-JSON schema that is specifically tailored to store and manage data streams from sensors.

Additionally, different modelling and analytics strategies, based both on FEA procedures and Machine Learning algorithms, have been developed to provide the necessary data-to-knowledge tools to complement the framework. In one specific case (the smart foundation prototype) a contribution to the development of a SaaS, which is currently in its beta-testing phase and available to a selected number of engineers in the Australasian region, has been provided.

Finally, the most prominent "environmental" factors that may challenge the opportunity of ubiquitous and heterogeneous geotechnical data sources, including sensor-enabled geotechnical objects, have been investigated. In particular, the use of blockchain technology to provide an additional security layer based on the "data transactions" logic has been investigated. Furthermore, general economical considerations based on the outcomes of this research have been reported, emphasizing the potential benefits of sensor-enabled geotechnical objects within the fast-growing IoT panorama.

# **Table of contents**

| F | orewo   | rd                                                                 | 1    |

|---|---------|--------------------------------------------------------------------|------|

| Т | able o  | f contents                                                         | 3    |

|   | List of | acronyms                                                           | 5    |

|   | List of | symbols                                                            | 6    |

| 1 | . Inte  | ernet of things and geotechnics                                    | 7    |

|   | 1.1     | General trends of the construction industry in a data-driven econo | omy8 |

|   | 1.2     | Data mining in the AEC industry                                    | 11   |

|   | 1.3     | The idle capacity of geological and geotechnical data              | 12   |

|   | 1.4     | Geotechnics and the Geographical Information Systems               | 15   |

|   | 1.5     | Geotechnics and the Building Information Modelling                 | 16   |

|   | 1.6     | The potential role of sensor-enabled geotechnical objects          | 17   |

| 2 | . Dat   | a sources                                                          | 19   |

|   | 2.1     | Typical geotechnical data sources                                  | 19   |

|   | 2.2     | "Smart" objects vs. regular geotechnical monitoring                | 22   |

|   | 2.3     | Sensor-enabled geosynthetics                                       | 23   |

|   | 2.4     | Smart geocell prototype: physical components                       | 26   |

|   | 2.4.    | 1 Sensors                                                          | 26   |

|   | 2.4.    | Wiring, enclosure and installation                                 | 28   |

|   | 2.4.    | Powering and networking                                            | 28   |

| 3 | . Dat   | a management                                                       | 30   |

|   | 3.1     | The pitfall of dispersive data                                     | 30   |

|   | 3.2     | The GIS approach                                                   | 31   |

|   | 3.3     | The BIM approach                                                   | 34   |

|   | 3.4     | Smart geocell prototype: edge computing                            | 35   |

|   | 3.4.    | Data normalization and standardization                             | 35   |

|   | 3.4.    | 2 Low-level thresholds handling                                    | 40   |

| 4 | . Mo    | delling and analytics                                              | 42   |

|   | 4.1     | Model-based vs. Data-driven approach                               | 42   |

|   | 4.2     | Distributed numerical modelling: the smart foundation              | 43   |

| 4.3    | Distributed Machine Learning              | 49 |

|--------|-------------------------------------------|----|

| 4.4    | Smart geocell prototype: machine learning | 50 |

| 4.4    | .1 Status classifier                      | 50 |

| 4.4    | .2 Predictive maintenance regressor       | 52 |

| 5. Da  | ta security                               | 54 |

| 5.1    | Centralized vs. Decentralized data        | 54 |

| 5.2    | Cryptography and Blockchains              | 55 |

| 5.3    | Policies and regulations                  | 57 |

| 5.4    | Data ethics                               | 60 |

| 6. Ec  | onomical considerations                   | 61 |

| 6.1    | The general paradigm of data value        | 61 |

| 6.2    | The costs of geotechnical data mining     | 62 |

| 6.3    | The benefits of geotechnical data mining  | 65 |

| 7. Co  | ncluding remarks                          | 68 |

| 7.1    | Review of the research                    | 68 |

| 7.2    | Discussion                                | 70 |

| 7.3    | Future research and developments          | 72 |

| Acknow | wledgements                               | 74 |

| Refere | nces                                      | 75 |

#### LIST OF ANNEXES

Annex 1 - Hardware description

Annex 2 - Software design principles and strategies

# List of acronyms

AEC Architecture Engineering Construction

AGS Association of Geotechnical and Geoenvironmental Specialists

API Application Programming Interface

BIM Building Information Modelling

CPU Central Processing Unit

DIGGS Data Interchange for Geotechnical and Geoenvironmental Specialists

DT Digital Twin, Decision Tree

EDF Élecricité de France

EU European Union

FEA Finite Element Analysis

GIS Geographical Information System

GPS Global Positioning System

HM High Modulus

IFC Industry Foundation Classes

IoT Internet of Things

IT Information Technology

JSON Javascript Object Notation

MEMS Micro Electromechanical System

ML Machine Learning

OT Operation Technology

PCA Principal Component Analysis

PSD Power Spectral Density

RMS Root Mean Square

RF Random Forest

SaaS Software as a Service

SHM Structural Health Monitoring

Note: Acronyms are presented in alphabetical order

# List of symbols

| а | Linear acceleration                                      |

|---|----------------------------------------------------------|

| 3 | Correction (small) factor                                |

| Р | Modified periodogram from discrete Fourier transform     |

| K | Number of batches                                        |

| Α | Target matrix (for PCA)                                  |

| U | Matrix with orthonormal columns of dimension $m \ x \ k$ |

| V | Matrix with orthonormal columns of dimensions n x k      |

| Σ | Diagonal matrix                                          |

| n | Number of samples                                        |

| k | Number of features                                       |

| Х | Sample feature value, Predictor value, Generic variable  |

| μ | Cluster centroid feature value                           |

| С | Cluster                                                  |

| Q | Data subset (batch)                                      |

| G | Impurity                                                 |

| Н | Impurity base function                                   |

| R | Observation region                                       |

| N | Observation number                                       |

| p | Probability                                              |

| Χ | Training data                                            |

| L | Loss function (linear regressor)                         |

| у | Response variable                                        |

| α | Calibration parameter                                    |

| β | Calibration parameter                                    |

|   |                                                          |

Note: Symbols are presented in order of appearance

# 1. Internet of things and geotechnics

The Internet of Things (IoT) is a broad and sometimes controversial technological trend, which is becoming transversal to numerous aspects of the modern global economy. Such trend is necessarily galloping at global scale as IoT is intrinsically related to the current level of interconnection, which is the highest humanity has ever experienced.

Pushed by the ubiquity of IoT, many industries, including low-tech ones, are experiencing a surge in technical and regulatory instruments aiming to its adoption. However, while there is consensus among a variety of stakeholders that IoT would bring outstanding social and economical results, there is still uncertainty in the very definition of the term as well as in the definition of the underlying philosophy.

Some authors suggest a general and positive definition for IoT based on the desirable convergence between *people*, *things*, *processes* and *data* towards a data-driven economy (Rayes, 2019). Others outline the duality between network-enabled capabilities and network-induced constrains in a super connected physical world (Brous, 2020; Zuboff, 2018).

With this second, even-tempered definition in mind, one might argue that a specific industry would endorse the IoT logic and instruments due to their expected end-state benefits, while underestimating the structural changes and the impacts this adoption is going to produce.

The adoption course in the case of the AEC industry is following the rise of Building Information Modeling (BIM) and its progressive merging with Geographical Information Systems (GIS). BIM first adoption efforts at scale were promoted in the UK in the early 2000s with an initial focus on architectural and structural design. It soon became clear that BIM could have represented a leap forward for the whole

industrial process, as AEC suffered from chronical inefficiencies due to a lack of proper communication when compared to other, more *integrated* industries.

This introductory chapter outlines some general features and trends of the IoT in the data-driven economy. It focuses briefly on the AEC industry's most notable data management systems (BIM and GIS as anticipated) and, finally, it presents some broad reasoning about the current and potential role of data, especially geotechnical data, in the construction sector information value chain.

# 1.1 General trends of the construction industry in a data-driven economy

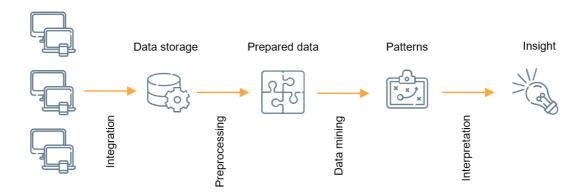

As many authors point out (Rayes, 2019), the general trend of the *Fourth Industrial Revolution*, which is dominated by the IoT paradigm, is propelled by the convergence of Operation Technology (OT) and Information Technology (IT). This convergence brings real-time data from operations closer to the expertise and technologies capable of using such data to make decisions and automate feedback instructions. Thanks to a dramatic increase in data quantity and granularity (Bramer, 2016), information itself has become a raw material for production in many industrial sectors. A schema for the general process of data-to-knowledge exploiting data as row material is shown in Figure 1.

#### Data sources

Figure 1 - General schema for the data-to-knowledge process

As anticipated, the process applies to a wide range of industries with some notable examples of disruptive achievements. In the AEC industry this logic is most prominent in the *smart building* philosophy, in which sensor-enabled built items are deemed to optimize a plethora of routine and maintenance operations throughout the life of a structure or an infrastructure. For both buildings and infrastructures this might includes, for instance:

- Safety monitoring and alerting (e.g. fire, noise, vibration, flooding, air pollution, earthquake early warning, etc.)

- Smart energy management (incl. lighting, natural gas, renewable energy production, etc.)

- Predictive maintenance

As for data integration (see Fig. 1), the AEC industry relies on two major means of data standardization:

- The Geographical Information System standards (GIS)

- The Building Information Modeling standards (BIM)

The latter being the youngest and more complex database format built around the Industry Foundation Class format (ISO 16739, acronym IFC) and currently in the way of converging with GIS.

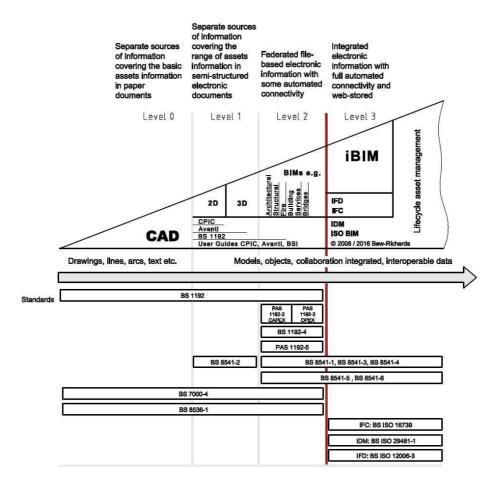

Nowadays BIM is undergoing a rapid evolution that is shifting the underlying logic from project-based collaboration to data integration (Ademci, 2018). This is usually identified as a shift from BIM to integrated BIM or iBIM (see Fig. 2).

Figure 2 - BIM evolution chart

As broadly stated in the recently delivered EN ISO 19650:2019, BIM is about getting benefit through better specification and delivery of just the right amount of information concerning the design, construction and management of buildings and infrastructure, using appropriate technology tools. Hence it is quite clear that BIM's prime purpose is to make clarity in the increasing data complexity of the AEC industry and promote value extraction from it.

IoT lives in the realm of Level 3 BIM (iBIM), where a fully functional and widely adopted database standard is capable of handling a considerable amount of diverse data sources to convey any sort of valuable information concerning a building or an infrastructural asset.

#### 1.2 Data mining in the AEC industry

As anticipated in section 1.1, data are important raw materials in the Fourth Industrial Revolution paradigm. The term *data mining* is then an appropriate way to describe such attitude towards maximizing data collection and data quality to extract the highest value from this resource.

Unlike the most prominent sectors in this latest industrial revolution, the AEC industry does not rely massively on *big data* to enhance business performances yet (Ahmed, 2018). This might be due to several hindering factors, including:

- Low adoption rates for BIM, GIS and data standardization protocols in general

- Low level of global construction standard harmonization

- Overall low technological level of the industry

Although no clear path for data mining in the AEC sector has been set so far, it is understood that the industry is now sufficiently mature to benefit from an increasing attention to information quality and management (EU BIM Taskgroup, 2017). It is the writer own opinion that this includes his specific fields of interest, namely applied geology and geotechnical engineering.

#### 1.3 The idle capacity of geological and geotechnical data

Geological and geotechnical data are usually collected at the beginning of every civil engineering project. Those data are of the utmost importance in the early phases of a project to allow for strategic decision regarding e.g. foundations and ground improvement activities. They are also important to evaluate and mitigate serious risks related to geo-hazards (earthquakes, landslides, expansive soils, etc.). The lack of sound geological and geotechnical data is often regarded as a major cause of unexpected costs, damages and fatalities; plus it prevents professionals from adopting risk mitigation strategies based on robust statistics (Christian, 2011).

The most interesting aspect of this chronical lack of *usable* data about the underground is that, at least in most cases, the information (including direct sounding, laboratory testing, geophysical testing, etc.) is present but totally *unusable* or only *partially usable* by the engineers. This is especially the case for historical data.

Moreover, in a number of different scenarios including high-risk contexts, geological and geotechnical monitoring is simply neglected, and permanent sensor-enabled geotechnical elements (e.g. sensor-enabled piles) are seldomly part of routine monitoring protocols.

If tunneling works are not accounted for, in the writer's professional experience geological and geotechnical monitoring is more often set up *a posteriori* when some

sort of damage has already occurred both during construction or after construction completion. And even when monitoring takes place, this is usually relegated to a *data niche* that lacks in standardization protocols and ultimately provides very little value for the investors as well as for the contractors.

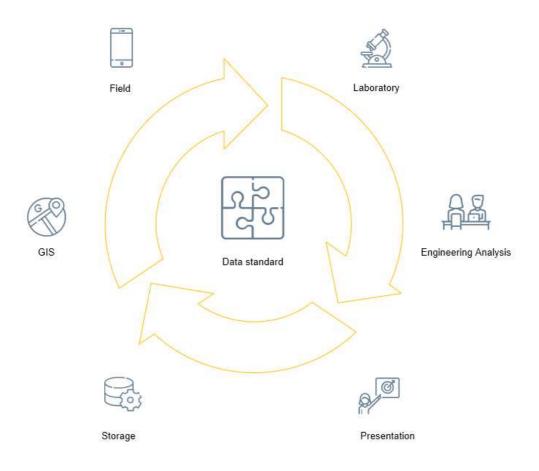

Standardization is surely one relevant issue, even though some interesting standards for geological and geotechnical data have reached maturity and others are gaining momentum at present (see Fig. 3). To cite a few of the most relevant data exchange formats:

- GeoSciML from the Open Geospatial Consortium (OGC)

- AGS data format from the (UK) Association of Geotechnical & Geoenvironmental Specialists

- DIGGS data format from ASCE Geo Institute (USA)

Figure 3 - Benefits of standardization in geotechnical data management

The idle capacity of geological and geotechnical data is then somehow universally recognized, even though is still gets little attention from the industry and its processes.

Geographical Information Systems (GIS) are frequently and commercially used to manage geological and geotechnical factual and interpreted data, even though, at least in most cases, open standards are omitted in favor of proprietary management data formats.

An important paradigm change in terms of interoperability could be represented by the current attempts within Building Smart International to introduce strong subsurface data standardization within the Building Information Modeling developing framework.

#### 1.4 Geotechnics and the Geographical Information Systems

As far as the relationship between geotechnics and GIS is concerned, the market offers a relatively wide variety of software capable of handling geological and geotechnical information in a geospatial fashion. Usually two main categories of management procedures are found:

- GIS for structural geology

- GIS for geotechnical in situ and laboratory testing and geotechnical monitoring management

The first procedure is most tailored to producing visualization aids based on direct sounding and geophysical testing and focuses mainly on structural geology. This includes mapping, 3D spatial interpolation and uncertainty management. This kind of software is usually very well suited for large scale project such as tunnels, offshore installations, etc.

On the other hand, another class of well-established software is conceived to geotechnical *in situ* and laboratory testing management, resulting in wider use cases, ranging from small to large scale civil engineering projects. This second data management schema is becoming more and more integrated into complex automated or semi-supervised workflows, starting from field data acquisition to geotechnical model generation to geotechnical numerical simulations.

In both of the aforementioned logics, the underlying feature of GIS that is so well suited for managing information about the underground, is the ability to offer spatial correlation tools that enormously facilitate data manipulation and allow valuable information extraction from bulky datasets (potentially including historical data).

#### 1.5 Geotechnics and the Building Information Modelling

As anticipated in section 1.1 and as shown in some recent pioneering research (Fabozzi S., 2020; Huang M. Q., 2020), the Building Information Modeling (BIM) is an extremely attractive opportunity to centralize and extract value from data produced at the project scale. As far as geotechnics is concerned, this means establishing some adequately broad and complete criteria to store and share information about soils/rocks, underground fluids and, especially, underground structures and infrastructures.

According to a recent survey (Tawelian, 2016), it appears that the current status of *geotechnical BIM* is still quite immature, however, most of the interviewees at that time agreed that, as applied geology and geotechnical professionals, they would benefit from the adoption of the communication standards of BIM.

|                            | Helpful                                                                                                                                                                               | Harmful                                                                                                                                                                                                                                                            |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal<br>(organization) | Strengths: BIM process familiar to most of engineers Familiarity with the current geotechnical data standards Potential for decrease in time and costs for projects                   | Weaknesses:  Current BIM does not include a strong geotechnical data exchange protocol (yet)  Current applications do not incorporate most of geotechnical design elements  Small companies may struggle with initial investment in training and software/hardware |

| External<br>(environment)  | Opportunities:         Training based on successful application of the process to relevant projects         Relatively small number of geotechnical data types         Reducing risks | Threats:      Segmentation of geotechnical BIM protocols     Collaborative working may be slowed down     Increase in project costs                                                                                                                                |

Table 1 - SWOT analysis for BIM applied to geotechnics

Although none of the aforementioned BIM-compliant storage and sharing criteria are present in the previous and current versions of the IFC standard (current version IFC4.1), attempts are being made to include some new geological and geotechnical distinctive features in the IFC5 development standard. Those attempts are aiming to integrate some existing and industry-wide data exchange formats (see section 1.3) within the BIM framework as well as to define new standards for e.g. interpreted data (including risk assessment) and monitoring. This work, carried out mainly within the Infrastructure Room in the Building Smart International panel, is also expected to deliver standards and tools for BIM and GIS integration.

One apparently minor and yet lingering desirable aspect of the developing geotechnical BIM emerges in the same survey, especially when the authors summarize their findings in a SWOT chart (see Table 1). This aspect regards what the authors (Tawelian, 2016) address to as *buried services and underground structures*, i.e. elements relevant to the project that lay underground and interact/interfere with geotechnical works.

The idea of extracting valuable information from components laying underground stands at the basis of this work. The goal, as engineering services providers, would be to manage and manipulate data from sensor-enabled *geotechnical objects*, to take advantage of the normalization ensured by the BIM framework and, ultimately, draw value from otherwise idle information sources.

#### 1.6 The potential role of sensor-enabled geotechnical objects

Although Health Monitoring is not a new topic for some distinctive, geotechnicalintensive civil engineering activities (incl. deep excavations, roadways and airfields), the vast majority of all geotechnical remote sensing installation focuses on project variable and constrains rather than pure data extraction. It is quite common to have optical displacement monitoring during deep excavation works, but it is not so common to have inertial monitoring systems systematically embedded in D-wall reinforcements. It is even less common to have integrated monitoring systems that can produce valuable information for all the involved stakeholders (designers, contractors, HS, developers, etc.).

It is the writer's opinion that the potential role of sensors enabled geotechnical objects, such as precast and cast-in-place deep foundations, ground anchors, geosynthetics, tunnel liners, etc. is currently underestimated and relatively simple to achieve, at least in medium-to-large structural and infrastructural scenarios.

Especially geosynthetics, which are a product of a relatively highly specialized and precision industry, seem the most suitable first candidate for a transition towards natively smart geotechnical objects. This research has explored the potential of one class of geosynthetics, namely geocells, to be equipped with low-cost, consumer grade MEMS sensors and to be able to *talk* to a networked system using GIS and BIM-compliant protocols. This choice is quite arbitrary, as ideally any other geosynthetic can be turn into a smart geotechnical object. In fact, examples of such attempts involving sensor-enable geosynthetics are already well underway in the technical community (Cui, 2018) (Yazdani & Hatami, 2016). One distinctive aspect of this research is represented by the development of a novel data management framework, exemplified on a simple real-case scenario, in which data standardization (GIS/BIM compliance) and data value extraction (via daisy-chained edge and cloud computing) play a central role.

#### 2. Data sources

In the AEC industry data sources are usually related to the so-called "Smart" devices. Data can be gathered by all sort of stand-alone or embedded sensors and most of such sensors convey data that is useful for the property/asset management throughout the life of a building or an infrastructure.

In the geotechnical engineering practice data are usually acquired before or during construction activities and, as opposite to other disciplines of the industry, little to no further monitoring is used to provide geotechnical information throughout the life of the building/infrastructure.

This chapter focuses on the general aspects of geotechnical information management and on the possibilities offered by the *smart device logic*. It starts from the standard engineering practice, that entails well-established in situ and laboratory testing procedures as well as purpose-specific monitoring (e.g. inclinometers, piezometers, etc.). Then it explores the possibility of more long-lasting data sources that mimic the anticipated smart device logic. Finally, it introduces the concept of sensor-enabled geosynthetics as one promising way to fulfill a permanent geotechnical monitoring framework, suitable for both buildings and infrastructure management.

### 2.1 Typical geotechnical data sources

In common geotechnical engineering practice, data are usually acquired via essentially three classes of methods:

Direct testing and monitoring: this include drilling and continuous coring, CPT soundings (Figure 4), in-hole installations such as inclinometers and piezometers, direct compaction testing, etc.

- Indirect testing: this includes a wide range of geophysical methods such as GPR (Figure 5), active and passive seismic methods, ERT, non-invasive compaction testing, etc.

- Laboratory testing: i.e. all standardized testing carried out in the geotechnical laboratory to complement the two previous categories.

The majority of such information are, in most cases, gathered at the beginning of the construction project and are at the basis of standard geotechnical reports. Investigation and preliminary monitoring results are then made available to the geotechnical engineers for the further design phases.

Figure 4 - Typical CPT probing equipment

Figure 5 - Typical GPR equipment

In some scenarios monitoring during construction plays a particularly important role. This is the case of most deep excavation and tunneling works, where systematic monitoring during construction is performed to mitigate the most prominent risks related to ground settlement, collapsing of excavation supports, etc.

Geotechnical information from site investigations, as anticipated, are usually incapsulated in static reports, while monitoring data are usually managed in proprietary servers (typically supplied by the monitoring system manufacturers) and made available to the engineers via dedicated (proprietary) software or web platforms.

Some advanced software systems (an example in Figure 6) allow for an integral visualization of ground investigation and monitoring, most of them leveraging the GIS capabilities to correlate data in a geospatial fashion.

Figure 6 - Commercial software for geotechnical data management through a GIS-like approach

This software, as a necessity, relies on some sort of data standardization to manipulate and exchange information from different data sources. All the commercial packages currently available on the market and capable of this sort of integration rely on the AGS data format to provide a robust data exchange framework (see section 3.4 for further details about geotechnical and geo-environmental data exchange formats).

## 2.2 "Smart" objects vs. regular geotechnical monitoring

By looking at some developing practices in the field of data integration at the building/infrastructure level, i.e. energy management (Wang, 2013) or OHS (Riaz, 2017) as well as some remarkable research and development works in the geotechnical field (Xue W., 2015), one may become aware of the potential of "smart objects" (i.e. sensor-enabled) when compared with state-of-the-art geotechnical monitoring.

While regular monitoring is usually stand-alone and installed *a posteriori* and might generate "unwanted" costs and interferences on site, sensor-enabled geotechnical objects would be ideally much more site-tolerant and cost-effective. By embedding sensors in e.g. piles, Diaphragm walls, geosynthetic layers/objects, etc. one may be able to collect virtually any kind on valuable information depending on the specific site context without the costs associated to post installation.

The downside of embedding sensors *a priori* is that some high-precision measures would be precluded due to the less accurate installation procedures as well as the potential damages during construction.

Definitely, one may think of smart geotechnical objects as valuable sources of information in situations where monitoring granularity, persistence and repeatability is deemed interesting for asset management purposes and as a valid complement to standard, well-established monitoring techniques.

In light of the considerations above, a choice has been made to explore the opportunity of sensor-enabled geosynthetics to develop the IoT framework based on a plausible use-case scenario.

# 2.3 Sensor-enabled geosynthetics

Finding a suitable way for extracting information from sensor-enabled geosynthetics is not a novel idea (Yazdani & Hatami, 2016; Cui, 2018),. Most of the researchers in this niche focus on strain monitoring of the geosynthetic layer itself for specific SHM, while, at present, apparently no effort is dedicated to the opportunity of embedding general-purpose sensors with data granularity in mind.

Geosynthetics are a special class of geotechnical objects that are industrially manufactured and, consequently, utterly standardized. Elements such as geogrids (Figure 7), geocells (Figure 8), geo-membranes, geo-composites, geofoam, etc. are used in many different circumstances to build an equally large number of different items. Such items include:

- Road and railway embankments

- Dikes and earth dams

- Stiffened rafts (e.g. for structures laying on ground improved with stone columns, etc.)

- Earth walls

- Landfill capping

- Channel protection surfaces

- Stabilization of erodible slopes

Figure 7 - Geogrids used for soil improvement

Figure 8 - Geocells used for fast access road building

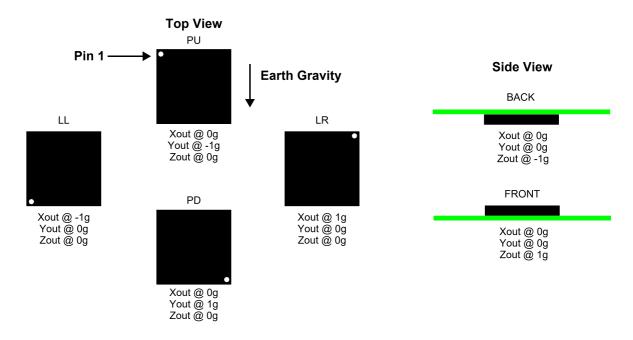

The scope of this work, while keeping the centrality of the IoT logic, is to explore the possibility of natively sensor-enabled geosynthetics that could convey general-purpose information according to the specific use case and site conditions. The prototype presented in this work, that will be described the following sections, includes inertial (acceleration) measurement from sensor-enabled geocells, managed through an IoT framework based on protocols that are, by design and to an adequate extent, compatible with GIS and BIM.

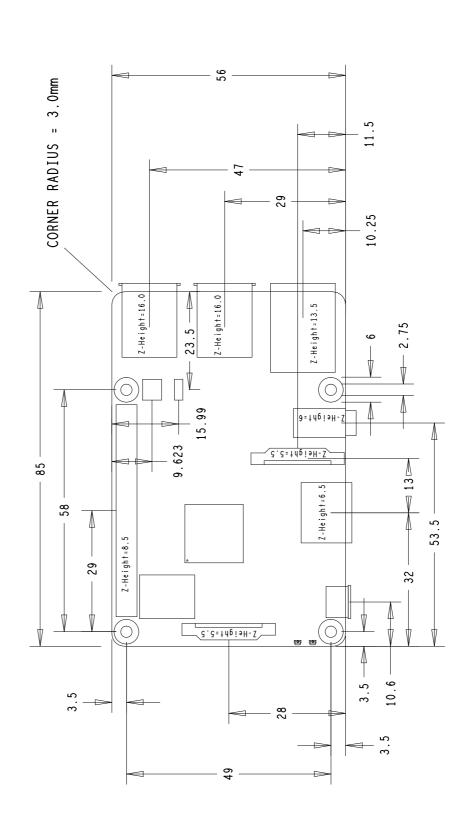

#### 2.4 Smart geocell prototype: physical components

The smart geocell prototype is built on top of a standard, commercially available polyethylene geocell and via consumer-grade electronics. Although perfectible, the setup can clarify the most distinctive features and capabilities of a sensor-enabled geosynthetic layer to be potentially embedded in regular civil engineering applications. The following sections illustrate the main physical components of the system together with some practical considerations based solely on lab-scale applications and testing.

#### 2.4.1 Sensors

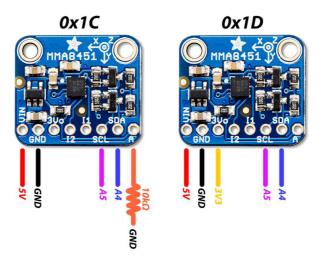

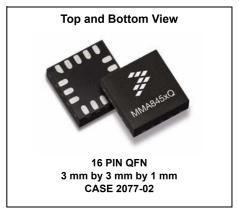

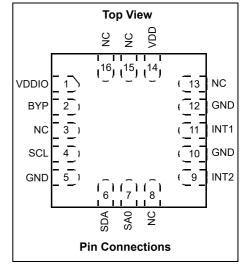

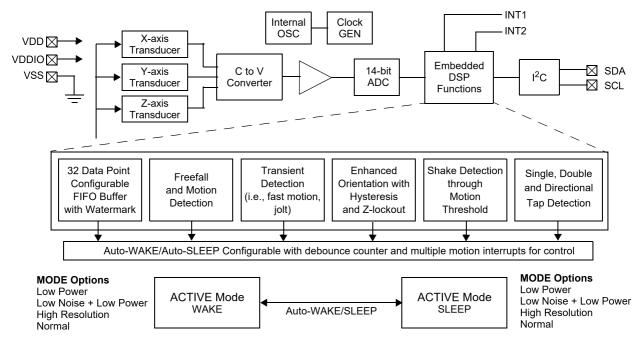

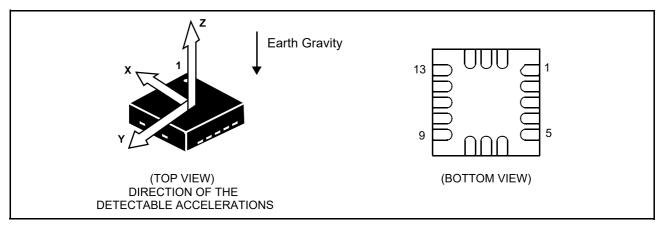

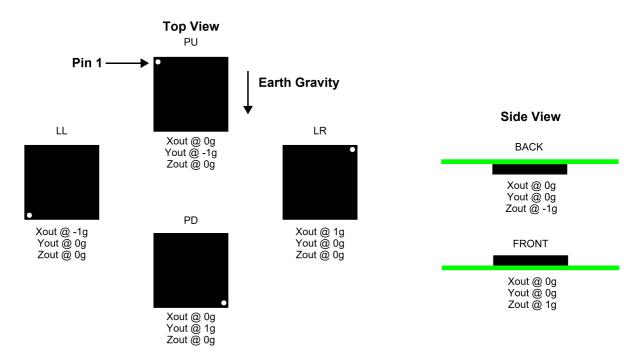

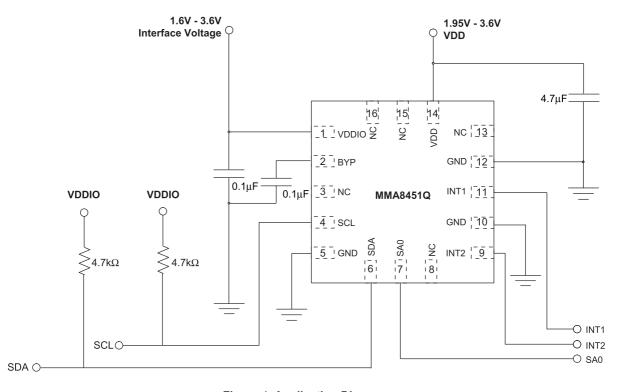

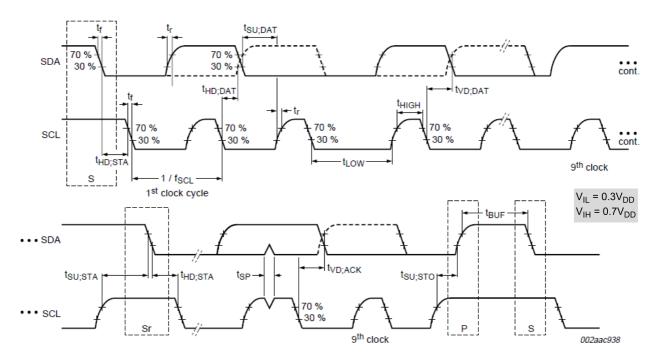

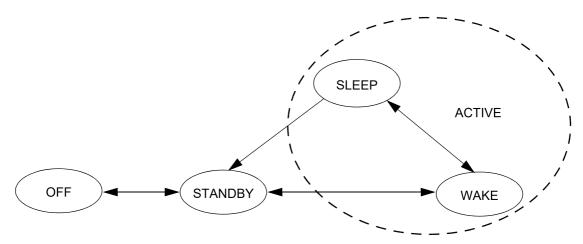

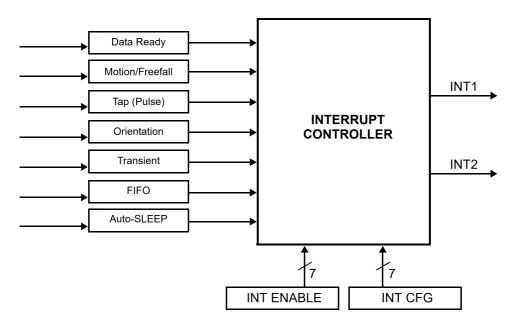

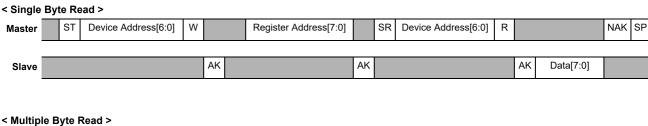

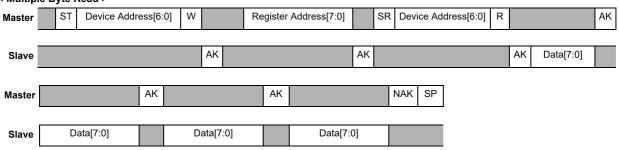

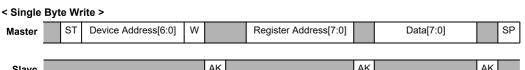

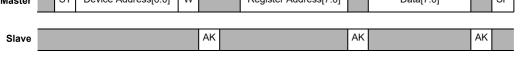

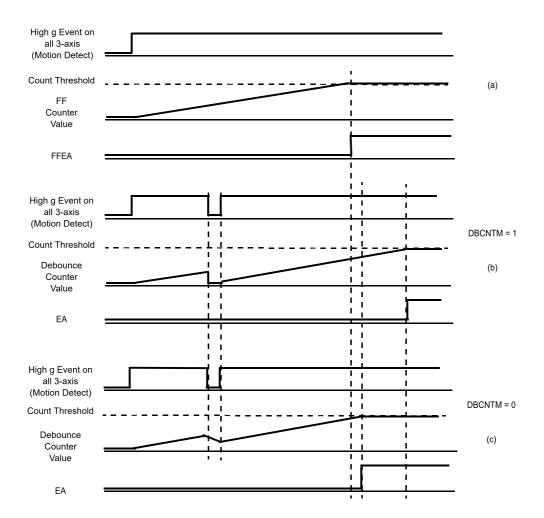

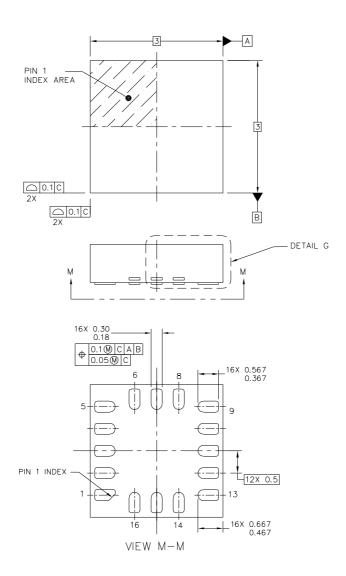

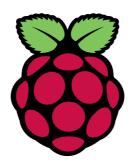

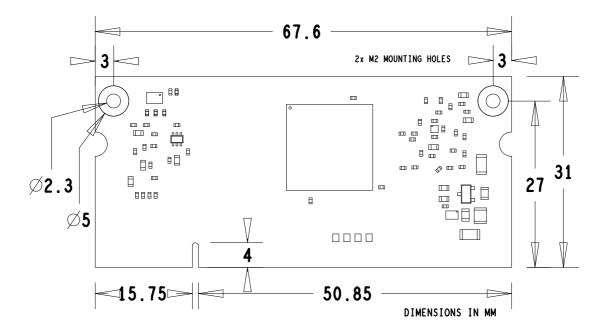

The sensors used in the prototype setup are consumer-grade triaxial accelerometers. It is a 3V, 14-bit ADC accelerometer capable of handling maximum accelerations in the ranges ±2g - ±8g. In the standard setup (with the measuring range set to ±2g) the sensor's sensitivity is declared as high as 4096 counts/g. It communicates via the standard I2C port with a Raspberry Pi 3 single-board computer (see fig. 10). In the lab-scale prototype either a single sensor and a dual sensor sensors setup over the same board (see fig. 9) has been used. The full datasheets of the sensor a the controller are provided in Annex 1.

Figure 9 - MMA8451Q 3-Axis 14-bit/8-bit Digital Accelerometer (with I2C wiring schema)

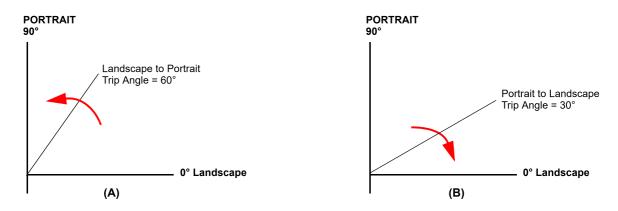

The sensors are used to infer both the variation in tilt and, more generally, to extract information from vibrations induced by external sources. For more details about the basic edge-computing strategies associated with this simple setup, refer to section 3.4.

The sensing system can be further complemented with useful side hardware, such as temperature sensors, an on-board GPS module and RFIDs.

Figure 10 - Raspberry Pi 3 B+ single-board computer

#### 2.4.2 Wiring, enclosure and installation

In order to ensure a decent protection for both sensor and connectors, a simple and effective wiring and enclosure has been developed. A small IP65 split-type enclosure has been adapted to host a single accelerometer, in order to prevent dust and moisture form the fill aggregate particles to get in contact with the electronic component. The enclosure has been solidarized with the geocell sidewall and the outgoing wiring has been performed with an adequately strong ensemble cable.

Ideally, an industrially manufactured smart geocell would include "sensors cells" with built-in wiring to minimize or exclude *a posteriori* installation of the sensing devices. This would undoubtedly ensure faster and more controlled installation procedures and an overall better quality of the enclosure and wiring apparatus.

Finally, considering that especially the sensor orientation might be affected by the geocell installation process, the edge-computing interpretation procedures are tailored to handle this uncertainty by different normalization strategies (see par. 3.4.1). More generally, one should always consider that sensors installed *a priori* on construction materials and elements may suffer from displacement during transportation and installation and the reliance upon precise positioning and orientation, at least outside reasonable limits, should be avoided by design.

#### 2.4.3 Powering and networking

In the lab setup both power and networking are provided through landlines.

Nonetheless the very same system could manage more field-tailored power sources

(e.g. solar + battery) and can communicate wirelessly via Bluetooth and/or WLAN.

The I2C bus is easily set up through a few lines of (Python) code. The code snippets relevant to the hardware connection and initialization via I2C are reported and commented in Annex 2.

No further study nor prototyping has been dedicated to data transmission technologies specifically tailored to IoT (e.g. LoRa or LPN).

# 3. Data management

Data management is critical for distributed sensors and IoT applications. This chapter outlines the most promising approaches tailored to geotechnical-related data sources based on GIS and BIM ecosystems and centered onto robust standardization protocols.

### 3.1 The pitfall of dispersive data

Having the ability to gather and draw to the network large amount of data does not necessarily means extracting most of their intrinsic value from them. Dispersive data is one major pitfall of geotechnical engineering practice, at least in the writer's experience.

In the future perspective of ever increasing data sources, hopefully including sensorenabled geosynthetics, a dispersive handling is not an option, as it would deprive the IoT item from its additional value and would simply push it out from the large-scale markets of e.g. smart cities and smart infrastructures.

As part of the R&D, two main strategies have been developed to try and mitigate this tendency by incapsulating data from geotechnical investigation and geotechnical monitoring into two complementary ecosystems, GIS and BIM, as already anticipated in section 1.4 and 1.5.

Both strategies aim to centralize data management and visualization while keeping adequate de-centralization for data processing and data transaction (see Chapter 5).

The "GIS approach" that has been developed is quite general and strictly dataoriented and can be applied successfully to structural and infrastructural projects of all sizes (see. section 3.2). On the other hand, the proposed "BIM approach" is more specific and modeling-oriented and it is more suitable for small projects or subsets of large projects (at least at the present development level of commercial BIM authoring tools), especially where geotechnical issues represent important driving factors (see section 3.3).

Both approaches have been voluntary developed on top of open standards and platforms, in order to ensure the widest possible interoperability.

#### 3.2 The GIS approach

GIS is naturally a large-scale tool. Its DB structure is capable of handling large amounts of geographical data with a low level of 2D geometrical detail (namely points, lines and/or polygons). This feature, when looking at IoT applications, is useful in infrastructural projects, together with the ability to manage a wide variety of data sources and formats (Li W., 2020).

During the prototyping phases, a standardized data exchange format based on the JSON format and built according to the hierarchical logic of AGS format has been developed. This simple format can transport basic geo-localization information together with a number of custom fields for status, tags, alerts, time series related/derived parameters, etc.

The JSON standard was chosen simply because it is easier to handle within the current GIS software framework, using Python as main programming language and PostgreSQL as DBMS. The custom JSON format is built on top of the AGS4 NZ v1.0.1 standard, that includes appropriate tags for general-purpose monitoring devices ("MONG" and "MOND" headings). Such schema should be fully compatible with the new version of AGS (4.1), released in December 2020, as well as with the new AGSi format (interpreted data AGS counterpart, released in November 2020 in beta

version), which is natively JSON-formatted. The general JSON schema for a single triaxial accelerometer is reported in Annex 2 and it is briefly outlined in Table 2 and Table 3. A vis-à-vis conversion to IFC4 standard has been attempted even though, at least at present stage, AGS format appears superior in terms of standardization capabilities of geotechnically-oriented sensors.

| Monitoring Installations and Instruments |                                         |        |                                  |  |

|------------------------------------------|-----------------------------------------|--------|----------------------------------|--|

| AGS heading                              | IFC rel. entity                         | Туре   | Description                      |  |

| LOCA_ID                                  | A_ID IFCSite string Location identifier |        | Location identifier              |  |

| MONG_ID                                  | IFCSensor                               | string | Monitoring point reference       |  |

| MONG_DATE                                | IFCPropertySet                          | date   | Installation date                |  |

|                                          |                                         | string |                                  |  |

| MONG_TYPE                                | IFCSensorType                           | string | Instrument type (according to    |  |

|                                          |                                         |        | standard abbreviations list)     |  |

| MONG_DETL                                | IFCPropertySet                          | string | Details of instrument            |  |

| MONG_BRGA                                | IfcTimeSeries/                          | number | Bearing of monitoring axis A     |  |

|                                          | IfcPlaneAngleMeasure                    |        |                                  |  |

| MONG_BRGB                                | IfcTimeSeries/                          | number | Bearing of monitoring axis B     |  |

|                                          | IfcPlaneAngleMeasure                    |        |                                  |  |

| MONG_BRGC                                | IfcTimeSeries/                          | number | Bearing of monitoring axis C     |  |

|                                          | IfcPlaneAngleMeasure                    |        |                                  |  |

| MONG_INCA                                | IFCTimeSeries/                          | number | Inclination of instrument axis A |  |

|                                          | IFCReal                                 |        |                                  |  |

| MONG_INCB                                | IFCTimeSeries/                          | number | Inclination of instrument axis B |  |

|                                          | IFCReal                                 |        |                                  |  |

| MONG_INCC                                | IFCTimeSeries/                          | number | Inclination of instrument axis C |  |

|                                          | IFCReal                                 |        |                                  |  |

| MONG_REM                                 | IFCPropertySet                          | string | Remarks                          |  |

| MONG_CONT                                | IFCPropertySet                          | string | Contractor who installed the     |  |

|                                          |                                         |        | instrument                       |  |

| MOND [] See Table 3                      |                                         |        |                                  |  |

Table 2 - AGS-compatible headers and IFC4 compatibility schema for the AGS-JSON format. MONG group headers

| Monitoring Readings     |                |          |                                       |

|-------------------------|----------------|----------|---------------------------------------|

| Heading IFC rel. entity |                | Туре     | Description                           |

| MOND_DTIM               | IFCTimeSeries/ | datetime | Date and time of reading              |

|                         | IFCReal        |          |                                       |

| MOND_TYPE               | IFCPropertySet | string   | Instrument type (according to         |

|                         |                |          | standard abbreviations list)          |

| MOND_INST               | IFCPropertySet | string   | Instrument reference / Serial No.     |

| MOND_RDNG               | IFCTimeSeries/ | -        | Readings                              |

|                         | IFCReal        |          | (IFC has different entries for actual |

|                         | and/or         |          | readings and status)                  |

|                         | IFCTimeSeries/ |          |                                       |

|                         | IFCLabel       |          |                                       |

| MOND_UNIT               | IFCPropertySet | string   | Units of reading                      |

| MOND_METH               | IFCPropertySet | string   | Measurement method                    |

| MOND_LIM                | IFCPropertySet | -        | Detection limit                       |

| MOND_ULIM               | IFCPropertySet | -        | Upper detection limit                 |

| MOND_CONT               | IFCPropertySet | string   | Contractor who takes readings         |

| MOND_REM                | IFCPropertySet | string   | Remarks                               |

Table 3 - AGS-compatible headers and IFC4 compatibility schema for the AGS-JSON format. MOND group headers

By using a specific version of AGS as counterpart, it is possible to define a format that is readily translatable into a broadly recognized standard and, meanwhile, is easily manageable within standard GIS platforms, 60% lighter on average (when compared to the CSV standard AGS format) and still human-readable. It is worth noticing that IFC format is more flexible than AGS (see, for instance, the ubiquity of the container class IFCPropertySet, which is conceived to hold properties within a dynamically extensible property tree), while the latter is surely more detailed and less prone to ambiguity in terms of field-specific dictionaries/definitions.

#### 3.3 The BIM approach

Intuitively, BIM is far more detailed than GIS as for geometrical description of physical entities, hence it is more suitable for smaller, circumscribed projects. When looking at IoT, this means BIM would be the ideal interface for sensor-enabled objects at the scale of buildings or small infrastructural elements/networks.

By keeping the basic JSON structure described in section 3.2 and reported in Annex 2, one can perform a translation from such format to the IFCJSON-4 development format, namely to the IFCSensor class (J. Rio, 2013; Smarsly K., 2016), by means of the JSON schema provided by BuildingSmart. Thanks to this logic a straightforward link between the GIS and BIM models including sensor-enabled geosynthetics has been developed.

One major pitfall about this approach is represented by georeferencing. While in GIS georeferencing is native, in BIM the majority of users tend to omit global CSs references. While custom CSs may be beneficial for a number of practical reasons, still not having an indication about global positioning (e.g. through the provided fields in the IFCSite class) is detrimental to a proper integration of data from geographical-sensitive ecosystems (such as GIS).

This research did not aim to produce a solution to this particular problem because it has been assumed that the state-of-the-art would naturally evolve towards a proper management of geographical positioning for BIM models, hence resolving the issue at a more general level before approaching the market with the framework.

## 3.4 Smart geocell prototype: edge computing

The raw data acquired from the accelerometers is processed on the edge thanks to the capabilities of the single-board computer within the sensing bundle. Edge processing has solved some relevant issues in terms of data transmission, noise reduction and power consumption and has allowed us to promote a de-centralized logic that has proved to be intriguing, especially when looking at the general problem of IoT data security (see Chapter 5).

The following sections present two of the main edge-computing procedures that has been developed for the smart geocell prototype.

#### 3.4.1 Data normalization and standardization

As anticipated in section 3.2 and 3.3, a protocol to translate the accelerometer timeseries into synthetic data to be transported via a compact format, which would be readily translatable into AGS and IFC, is designed. To perform such translation the data must first undergo a normalization process. Several approaches were tested during prototyping and the most promising are listed below:

| Approach       | Distinctive features             | Python library |

|----------------|----------------------------------|----------------|

| Tilt analysis  | Intuitive feature                | Scipy 1.5+     |

|                | Fast evaluation over subsets     |                |

|                | Useful to trigger alarms         |                |

| Power spectral | Robust feature                   | Scipy 1.5+     |

| density (PSD)  | Can be used as a noise estimator |                |

|                | Can be used to estimate RMS      |                |

| Principal          | • | Can be used in a pipeline with                                     | Scikit-learn 0.23+ |

|--------------------|---|--------------------------------------------------------------------|--------------------|

| component analysis |   | power spectra                                                      |                    |

| (PCA)              | • | Reduces dimensionality while                                       |                    |

|                    |   | retaining most of the variance                                     |                    |

|                    | • | Facilitates further processing (see                                |                    |

|                    |   | section 4.3)                                                       |                    |

| (PCA)              | • | retaining most of the variance Facilitates further processing (see |                    |

Table 4 - Libraries used for data normalization and standardization

For tilt angles estimation from acceleration time-series the following formulations are used:

$$\tan \varphi_{yxz} = \frac{a_y}{\sqrt{a_x^2 + a_z^2}}$$

$$\tan\theta_{yxz} = -\frac{a_x}{a_z}$$

where:

a<sub>x</sub>, a<sub>y</sub>, a<sub>z</sub> measured linear accelerations in the x, y and z directions

φ<sub>yxz</sub> roll angle

$\theta_{yxz}$  pitch angle

The angles are calculated in accordance with the  $R_{\text{yxz}}$  rotation sequence.

The following formulations can be adopted, as an alternative to the previous ones, to reduce the numerical effects of the instability regions (where  $a_z$  approaches zero):

$$\tan \varphi_{yxz} = \frac{a_y}{\sqrt{a_x^2 + a_z^2}}$$

$$\tan \theta_{yxz} = -\frac{a_x}{\text{sign}(a_z)\sqrt{a_z^2 + \varepsilon a_y^2}}$$

As for power spectral density calculation, the classical Welch's approach is preferred, as it natively reduces the noise impact:

$$S_{x}(f) = \frac{1}{K} \sum_{k=1}^{K} P_{k}(f)$$

where:

P<sub>k</sub> is the modified periodogram obtained from the discrete Fourier transform

K is the number of batches

As for PCA, randomized SVD is chosen primarily for its computational efficiency (Halko, Martinsson, & Tropp, 2011). The PCA procedure is classically formulated as follows:

$\boldsymbol{A} \simeq \boldsymbol{U}\boldsymbol{\Sigma}\boldsymbol{V}^T$

where:

A target matrix of dimension m x n

U matrix with orthonormal columns of dimension m x k

V matrix with orthonormal columns of dimension n x k

Σ diagonal (singular values) matrix of dimension k x k

The relevant code snippets are reported in full in Annex 2.

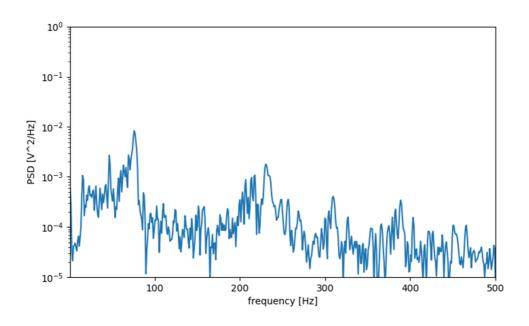

Figure 11 reports an example of PSD for a single acceleration component up to the frequency of 512 Hz evaluated during one of the smart geocell lab trials. The PSD is a simple and yet very powerful tool to evaluate both the noise impacts and the signal

RMS amplitude. It is also a convenient way to compare multiple time-series through e.g. Coherence.

Figure 11 - Example of PSD from the smart geocell single-sensor prototype

Either single time-series noise estimation (average PSD excluding peaks) and RMS (absolute peak of PDS) or multi-series coherence can be used to compress/feature the minimal inertial monitoring information and transport them via the proposed AGS-JSON format. Another type of compression/featuring can be achieved by the proposed PCA algorithm applied to the PSD in a pipeline. Table 5 reports an example of PCA applied to another experimental set, where the PSD variance ratio for the three principal directions was targeted.

| Component | Variance Ratio |  |

|-----------|----------------|--|

| Х         | 81.0%          |  |

| Y         | 14.8%          |  |

| Z         | 4.2%           |  |

Table 5 - Example of PCA applied to the principal directions of the smart-geocell sinle-sensor prototype

This form of compression/featuring (together with some other opportunities of the pipeline PSD+PCA, e.g. PCA noise covariance) can be used to prepare the data for further edge and cloud computing. In the proposed example, the X-component carries most of the variance, hence it might be used alone to perform further machine learning while retaining most of the information and, therefore, optimizing the chained procedures.

As anticipated, after the normalization process described above, one can try and translate the compact output in terms of peaks, PSD and/or PCA+PSD in a format compatible with AGS and, potentially, IFC exchange formats (namely IFCJSON formats).

To do so one may take advantage of e.g. MONG/MOND classes of AGS4 format (see Tables 2 and 3), as described in Aguilar (2017). Those classes are, in fact, sufficiently general to be able to host any sort of monitoring data, including the verbose description of data sources and data processing. The same is true for the IFC4 format that includes the IFCSensor object type (Wang, 2013), though such format is still not as mature as AGS for this particular task.

Once the data has been translated into one or both the interoperable formats cited above, the information can be exchanged through any compatible commercial and open source GIS/BIM platforms, both via desktop software and PaaS/SaaS products.

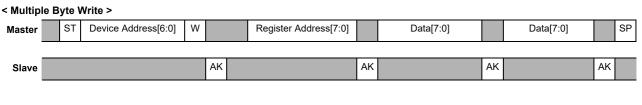

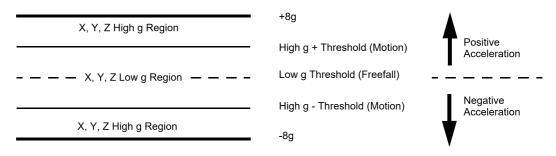

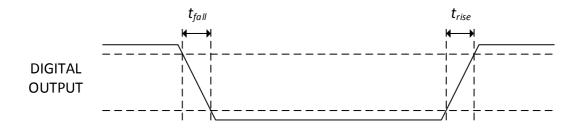

#### 3.4.2 Low-level thresholds handling

Edge-computing can also be used to trigger alarms based on low-complexity procedures. The first and simpler attempt was to set up an alarm triggering criterion based on fixed thresholds and windowed signals. Alarms have been set both on acceleration and tilt, the latter being the most significant for identifying slow and progressive stability/distortion problems. Another proposed, slightly more complex strategy entails an adaptive threshold logic based on a simple unsupervised learning algorithm, i.e. K-Means:

$$\sum_{i=0}^{n} \min(\|x_i - \mu_j\|^2) \qquad \mu_j \in C$$

where:

- n is the number of samples

- x are the sample feature values (e.g. RMS amplitude, roll, pitch, PCA variance ratio, ecc...)

- μ are the cluster centroid feature values

- C are the disjoint clusters

The relevant code snippets for low-level threshold handling are reported in full in Annex 2.

Even in this case one may take advantage of the AGS and/or IFC standards to convey the status information from the edge to a GIS/BIM server directly, without the need of full timeseries transfer (see Figure 12 for an example of such logic).

In fact, this could represent the most compact data exchange modality, even more compact than that described in section 3.4.1. As the benefits of data compactness in

a potentially overcrowded IoT environment are evident, one may think of the statusonly mode as a normal operation protocol, while retaining the possibility of acquiring the descriptive parameters (or even streaming live data) under certain non-standard circumstances.

```

"PROJ": {

"PROJ_ID": "4-00495",

"PROJ_NAME": "Smart_Foundation",

"PROJ_CLNT": "Biax",

"PROJ_CONT": "Cresco Group",

"PROJ_ENG": "ENVIA"

"LOCA": {

"LOCA_ID": "ACC1",

"LOCA_TYPE": "Instrument",

"LOCA_STAT": "Monitoring",

"LOCA_LAT": 4929412,

"LOCA_LON": 686687,

"LOCA_GL": 0.000,

"LOCA_LLZ": "EPSG:32632",

"LOCA_REM": "Smart_Foundation_Location"

"MONG": {

"MONG_ID" : "ACC1",

"MONG_DIS" : 0,

"MONG_DATE" : 01/01/2020,

"MONG_TYPE" : "ACM",

"MONG_CONT" : "ENVIA",

"MOND" : {

"MOND_DTIM" : ["04/01/2021 11:45:00", "04/01/2021

12:00:00",

"05/01/2021

11:45:00",

"06/01/2021

11:45:00",

"07/01/2021

11:45:00",

"08/01/2021

11:45:00",

"09/01/2021

11:45:00",

"10/01/2021

11:45:00",

"11/01/2021

11:45:00",

"12/01/2021 11:45:00"],

"MOND_RDNG" : ["OK", "OK", "OK", "OK", "OK", "OK",

"Tilt Alarm", "Tilt Alarm", "Tilt Alarm"],

"MOND TYPE" : "STA"

}

}

}

}

```

Figure 12 - AGS-JSON for a simple, single-sensor configuration. Status indicator (based on tilt) is stored and exchanged

# 4. Modelling and analytics

The procedures presented in Ch. 3 and carried out *on the edge*, are meant to provide fast feedback and data wrapping and are not sufficient to extract the most of value from the smart geocell (and from sensors enable geotechnical objects in general).

The following sections present some of the attempts aiming to extend the smart geocell capabilities by further cloud computing. Two main strategies are presented: and they are both discussed in terms of capabilities and implementation on remote computing services.

### 4.1 Model-based vs. Data-driven approach

As anticipated, several cloud computing procedures that fall into two different strategical categories have been tested. The first strategy, and the most intuitive from an engineering point of view, is founded on the definition of a physically based prediction model that is subsequently fed with data from sensors to trace and even trigger events. On the other hand, the second strategy is based on general-purpose classification/regression models (supervised machine learning models) that are not bound to a specific physical representation and that need to be *trained* before they can be put at use. Both strategies have prediction capabilities over the physical phenomenon of interest, and both have, in the writer's opinion, preferential fields of usage.

The model-based strategy has been deployed in a rather *easy-to-model* scenario involving a raft foundation subject to differential settlements and the data-driven approach (machine learning) in a *hard-to-model* scenario, where smart geocells are allegedly used to detect road/airfield pavement or rail superstructure wearing.

Both approaches proved feasible and showed good adaptivity to the potential and limitation of the simple sensing system. The first approach has been fully developed and it is under testing within a broader commercial initiative. The second is still in its conceptual phase and it has not been fully developed at present.

# 4.2 Distributed numerical modelling: the smart foundation

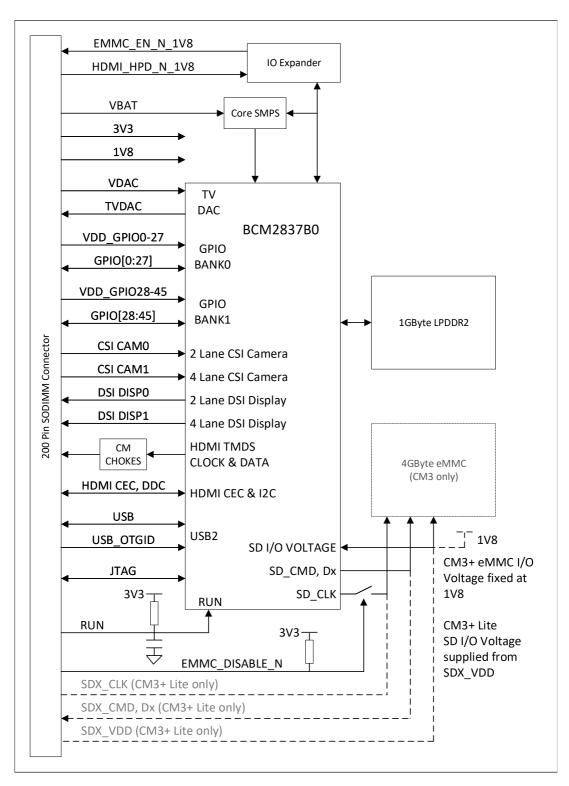

The distributed numerical modeling strategy is based on the joint use of a general purpose, open source FEA ecosystem (EDF, 1989-2020) and the cloud computing tools that combine the capabilities of two well known frameworks, namely Docker for containerization/distribution and Kubernetes for instances orchestration.

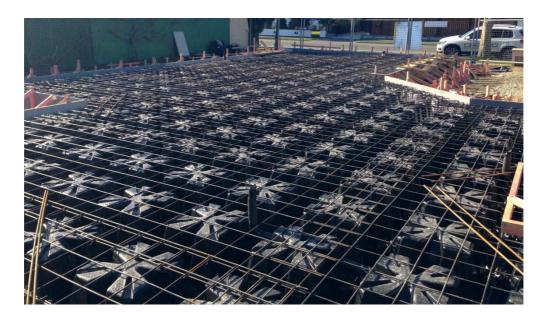

The first and simplest attempt was part of a broader commercial initiative involving a recently patented ribbed raft foundation system from Cresco Engineers New Zealand (see Figure 13). This system is specifically tailored to withstand the significant distortions caused by expansive or severely liquefiable soils thanks to a peculiar design of the void (plastic) pods.

Figure 13 - Building phase of the voided raft system (courtesy of Cresco Engineering NZ)

In case of large distortions, the same system can be equipped with innovatively designed perimetral jacking pads that can be used to re-level the superstructure by means of hydraulic jacks (see Figure 14).

Figure 14 - Preparatory phase of the voided raft system: engineered base mat and jacking pads (courtesy of Cresco Engineering NZ)

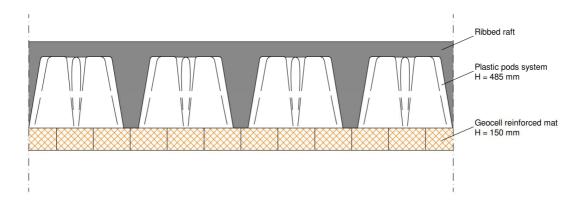

Thanks to the collaboration with the ribbed raft patent holders and distributors for Australasia, a SaaS platform dynamically linked to Code Aster libraries (EDF, 1989-2020) that is currently used by designers to evaluate the performances and the safety requirements of the novel foundation system subject to different distortion profiles (as anticipated, due to liquefaction and to swelling/shrinkage cycles) has been developed. Provided that geocells have being investigated as a complementary means of differential settlement mitigation to be placed below the said ribbed rafts (see Figure 15), the very same software is being developed further to model the foundation behavior under measured distortions aside from theoretical ones (AS, 2011).

For this particular application, acceleration + tilt for liquefaction and tilt only for swelling/shrinkage are the designated target quantities. In both cases the simple, commercial-grade sensors chosen in the first place for the laboratory setup are potentially capable of handling the target acceleration and tilt ranges (accelerations in the range of 0.1 - 1.0 g and planar rotations in the order of 0.1° or greater).

Figure 15 - Typical cross-section: engineered base mat (w. geocells) and ribbed raft

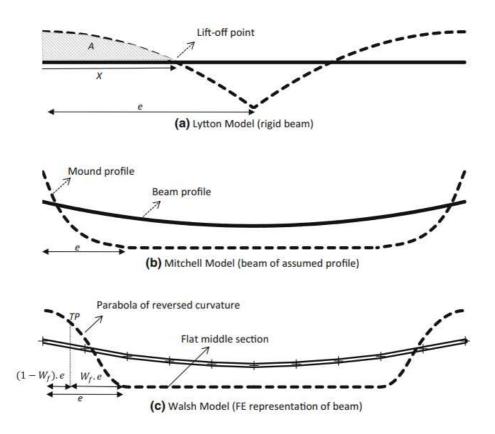

Sensors location for the model-based approach is quite important, at least in this particular scenario. For the swelling-shrinkage setup, for example, one way to choose the best sensors location under the foundation area would be to use theoretical deformation profiles, like those included in relevant design codes (AS, 2011) and derived from e.g. Mitchell's and Walsh works (Fardipour, 2016; Karunarathne, 2012).

Figure 16 - Typical edge-heave swelling profiles from various authors

Both Mitchell and Walsh models (figures 16.b and 16.c), which are generally more suitable to perform the design of deformable rafts subject to swelling height profiles in the range of 20-100 mm, identify regions of maximum mound curvatures in proximity of the slab edges. This is generally confirmed by field experience. Hence the optimal location of inclination sensors for the swelling-shrinkage setup should be in the within the "active" zone *e*, close to the edges and possibly in proximity of the occasional critical spots (such as large trees that might influence the suction profiles). Some additional modeling testing will be needed to validate this assumption, as some boundary effects are not considered in the simplified mound-shape methods. Such effects include:

- The stiffening effect of the geocell-reinforced mat

- The effect of the damp-proof membrane

- The effect of the system's voids in terms of pressure localization and swelling relief under the ribbed raft

The first full-scale prototype should then serve as a reference to fine tune the integrated monitoring as well as to calibrate the provisional numerical modeling and geocell-reinforced mat design accordingly.

In this scenario, the distributed numerical modeling based on measure points could be beneficial for progressive product optimization, also taking advantage of spatial analysis of monitoring data based on the GIS logic.

This is especially true for expansive soils. This is, in fact, a largely diffused and frequent phenomenon (much more frequent than severe liquefaction, being related to perpetual seasonal water content variations) which underlying physics is quite complicated and extremely site dependent. By accumulating the right amount of geospatial data, the developers and designers of the system would benefit from e.g. "performance maps" as well as additional design and optimization criteria.

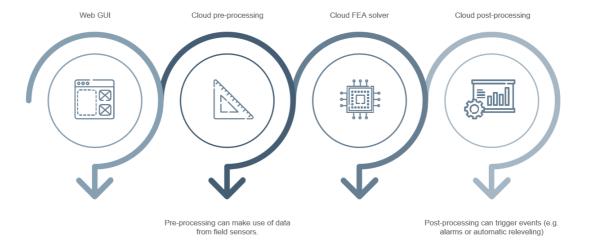

As anticipated, the software (which cannot be reproduced in full in Annex 2 due industrial and commercial secrecy arrangements) runs in the form of a REST API containerized in a Linux-based Docker and orchestrated by Kubernetes. The software logic, involving the anticipated prototype health monitoring strategy, is outlined in Figure 17.

Figure 17 - Basic architecture of the SaaS

The SHM coupling strategy includes, in brief:

- The possibility to use both theoretical and measured distortion profiles as inputs for the modeling

- The possibility to trigger events in real-time based on the modeling outputs.

This may include simple alarms and push notifications as well as more complex actions (i.e., hydraulic jacks control and actuation for releveling)

In the case of automatic releveling, the potential benefits of equipping the plastic pods with sensors as well are sought. For this purpose, as the expected strains/rotation of the structural elements would allegedly be smaller than those of the geocell-reinforced mat, one shall explore other sensing options that may prove more suitable than the first prototype setup.

### 4.3 Distributed Machine Learning

The distributed machine learning approach can be very useful to extend the capability of the collected dataset for both classification and regression (prediction) purposes. This approach, when compared to the model-based approach outlined in the previous section, is not constrained to a pre-determined physical representation of a specific phenomenon. Hence its applicability is virtually far more general and multi-tasking by nature.

The most interesting distributed machine learning procedure for smart geocells, as well as smart geotechnical objects in general, targets the predictive maintenance problem. In fact, this is a very tough problem to be addressed with the model-based approach described in section 4.2, while, with a sufficiently large dataset available, might become easier to solve using supervised learning strategies. This is due mainly to the ability of machine learning procedures to cluster and classify datapoints based on any feature set and even to emphasize relationships that might be invisible or counter-intuitive for a human model builder.

Since the full development of such procedure depends on the availability of large sets of data, it was not possible to test the prototype at scale. Nonetheless, in section 4.4 a brief description of the proposed approach is presented. Such approach is based on state-of-the-art classification/regression supervised learning algorithms including:

- Random Forest (RF)

- Elastic Net

Especially RF has been already experimented for classification in other fields of geotechnics with positive outcomes (Liu, et al., 2020).

# 4.4 Smart geocell prototype: machine learning

Machine learning, like remote modeling, takes place on cloud servers specifically designed to handle this sort of algorithms. While the most demanding machine learning procedures (e.g., Deep Neural Networks) might require different architectures than those built for the prototype SaaS and outlined in section 4.2, the procedures anticipated in section 4.3 are simple and lightweight enough to run onto the same, low memory single CPU, Docker + Kubernetes architecture. The following sections describe two of the tentative procedures, based on the smart geocell setup, that has been developed for predictive maintenance purposes.

#### 4.4.1 Status classifier

For the generic task of defining a "status" of the sensor-enabled geotechnical object,

Randomized Decision Trees (supervised) classification algorithm has been tested.

The simplest status classes can be set to identify:

- an OK status (no action needed)

- an off-line or no data status

- a pre-alarm status (might be used to trigger continuous data stream to inspect the data in deeper details)

- an alarm status (might be used to trigger some mitigation measures)

Being a general purpose, supervised classification algorithm, Randomized Decision Trees (aka Random Forests, RF in short) can be used virtually in any application context, provided that the collected dataset is sufficiently good to properly train-test it.

By definition, Decision Trees (DTs) are a non-parametric supervised learning method used for classification and regression. The goal of DTs is to create a model that predicts the value of a target variable by learning simple decision rules inferred from the data features.

Given training vectors  $x_i$  and a label vector y, a decision tree recursively partitions the space such that the samples with the same labels are grouped together.

Let the data at node m be represented by Q. For each candidate split  $\theta(j,t_m)$  consisting of a feature j and a threshold tm, partition the data into  $Q_{left}(\theta)$  and  $Q_{right}(\theta)$  subsets:

$$Q_{left}(\theta) = (x, y) | x_j \le t_m$$

$$Q_{right}(\theta) = (x, y) | x_j > t_m$$

The impurity at m is computed using an impurity function H, the choice of which depends on the task being solved (classification or regression):

$$G(Q, \theta) = \frac{n_{left}}{N_m} H(Q_{left}(\theta)) + \frac{n_{right}}{N_m} H(Q_{right}(\theta))$$

If a target is a classification outcome (like in this case), taking on values 0,1,...,k-1, for node m representing a region  $R_m$  with  $N_m$  observations, let

$$p_{mk} = \frac{1}{N_m} \sum_{x_i \in R_m} I(y_i = k)$$

be the proportion of class k observations in node m.

One of the most versatile impurity function in this context is Gini:

$$H(X_m) = \sum_{k} \rho_{mk} (1 - \rho_{mk})$$

where  $X_m$  is the training data in node m.

The purpose of assembling multiple DTs (i.e. implementing the Randomized Decision Trees logic) by inserting some randomness sources (e.g. bootstrapping both samples

and predictions) is to decrease the variance of the estimator. Indeed, individual decision trees typically exhibit high variance and tend to overfit. The injected randomness in forests yield decision trees with a certain level of decoupling of prediction errors. By taking an average of those predictions, some errors can cancel out. Random forests achieve a reduced variance by combining diverse trees, sometimes at the cost of a slight increase in bias. In practice the variance reduction is often significant, hence yielding an overall better model.

An implementation attempt for RF Status classifier for this framework is reported in Annex 2. This attempt considers a very general purpose for this classifier, making it potentially suitable for the smart foundation prototype, as well as for other, unexplored applications of smart geocells.

#### 4.4.2 Predictive maintenance regressor

Predictive maintenance is a very interesting topic for sensor-enabled geotechnical objects. Especially in infrastructural IoT, a predictive maintenance regressor can prove extremely useful in anticipating damaging and wearing patterns and, ultimately, in optimizing the most delicate maintenance activities.

By implementing the very same logic of predictive maintenance used e.g., in the Oil & Gas industry (Rayes, 2019), one can define a set of (supervised) ML algorithms that can be used as regressors or part of regressors based on time-series.

Furthermore, the potential of the Elastic Net (supervised) regression/regularization algorithm has been tested as well. One of the main advantages of such algorithm is

that it is particularly suitable for sparse datasets, which can be very useful if one needs to keep the data stream as small as possible and still be able to perform a robust enough prediction.

Elastic Net is a linear regression and regularization model that aims to minimize the following loss function:

$$L(\hat{\beta}) = \frac{\sum_{i=1}^{n} (y_{i} - x_{i}^{'} \hat{\beta})^{2}}{2n} + \lambda \left( \frac{1 - \alpha}{2} \sum_{j=1}^{m} \hat{\beta}_{j}^{2} + \alpha \sum_{j=1}^{m} |\hat{\beta}_{j}| \right)$$

where the regularization parameters  $\alpha$  and  $\lambda$  are set through cross-validation. An implementation attempt for Elastic Net regressor for this framework is reported in Annex 2

When comparing the status classifier based on RF (section 4.4.1) with the Elastic Net regressor implementation, one shall consider that the latter is conceived to be interoperable inside a broader and multi-purpose infrastructural IoT environment (as a basis for higher-order ML/DL procedures), rather than a stand-alone estimator. One of the main reasons for that choice is that, especially for infrastructures, interoperability of different data sources is deemed crucial to establish data-driven predictive maintenance protocols. As for roads, for example, one could consider the integration of the following data sources:

- fixed sensors (incl. smart geocells)

- mobile (vehicle-mounted) sensors

- atmospheric monitoring data

- InSAR and other satellite imaging

# 5. Data security

When considering potentially large networks of sensors, data security is one aspect to be studied in depth before getting to production. This is especially true if one considers the intrinsic value of data extracted from widespread monitoring in terms of industrial advantage (Zuboff, 2018).

This chapter analyzes the data security aspects of sensors enabled geosynthetics in view of the latest research about substantial risks of IoT systems (Brous, 2020). Firstly, the potential drawbacks of data centralization and, on the other hand, the benefits of a decentralized, smart geosynthetics network are explored. Secondly, the potential role of cryptography and blockchains to ensure security and trust in a decentralized network is analyzed. Finally, the role of current policies and regulations applicable to IoT as well as data ethics issues are discussed.

#### 5.1 Centralized vs. Decentralized data

According to (Rayes, 2019) a regular IoT architecture is made up of three distinct domains:

- Sensing domain: the domain made up of all smart objects that can collect data from the environment.

- Fog domain: the domain of fog devices (i.e., gateways) that aggregate sensors

data, stores them and perform preliminary operations onto them.

- Cloud domain: the domain composed of cloud devices/services (i.e., servers)

that orchestrate all fog devices and perform the heavy-computational processes to extract the most of data value.

This hierarchy is fully centralized, being the cloud servers the entities that retain and manage most of the system capabilities and value. This means a full IoT sensors network (e.g., a full stack of smart geocell data points along a railway segment) is potentially vulnerable to a single malfunctioning or security breach on the managing server side.

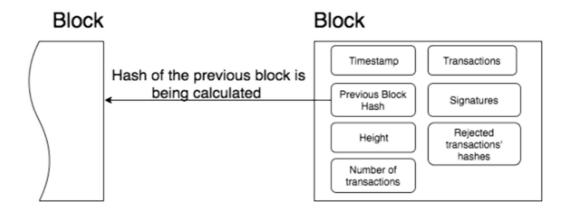

As clarified in Chapters 3 and 4, a tentative has been done to overcome this security issue by delegating some actions to the sensing domain (through the well-known logic of edge computing). Moreover, an alternative high-level orchestration method, based on distributed ledgers rather than centralized servers has been explored. This particular aspect, which will be described in further details in section 5.2, involves the use of cryptography and blockchains that would provide an immutable ledger for data-driven events (transactions), rendering the IoT process much harder to manipulate and disrupt and, on the other hand, way easier to control and inspect.

# 5.2 Cryptography and Blockchains

This section introduces a conceptual design for a simple private blockchain implementation tailored to the prototype sensor-enabled geotechnical objects, based on the (open source) Hyperledger Iroha project and the YAC consensus algorithm (Muratov F., 2018).