## Alma Mater Studiorum – Università di Bologna

## DOTTORATO DI RICERCA IN

# INGENGERIA ELETTRONICA, INFORMATICA E DELLE TELECOMUNICAZIONI

Ciclo XXVII

Settore Concorsuale di afferenza: 09/E3

Settore Scientifico disciplinare: ING-INF/01

MANY-CORE ARCHITECTURES: HARDWARE-SOFTWARE OPTIMIZATION AND MODELING TECHNIQUES

Presentata da: Christian Pinto

Coordinatore Dottorato Relatore

Prof. Alessandro Vanelli Coralli Prof. Luca Benini

Esame finale anno 2015

# Many-Core Architectures: Hardware-Software Optimization and Modeling Techniques

## Christian Pinto

Dept. of Electrical, Electronic and Information Engineering (DEI)

University of Bologna

A thesis submitted for the degree of

Doctor of Philosophy

2015

## Abstract

During the last few decades an unprecedented technological growth has been at the center of the embedded systems design paramount, with Moore's Law being the leading factor of this trend. Today in fact an ever increasing number of cores can be integrated on the same die, marking the transition from state-of-the-art multi-core chips to the new many-core design paradigm. Such many-core chips aim is twofold: provide high computing performance, and increase the energy efficiency of the hardware in terms of OPS/Watt. Despite the extraordinarily high computing power, the complexity of many-core chips opens the door to several challenges. First of all, as a result of the increased silicon density of modern Systems-on-a-Chip (SoC), the design space exploration needed to find the best design has exploded. Hardware designers are in fact facing the problem of a huge design space, with an extremely high number of possibilities to be explored to make a comprehensive evaluation of each of their architectural choices. This is also exacerbated by the extremely competitive silicon market, forcing each actor to always shrink the time-to-market of products to be ahead of the competitors. Virtual Platforms have always been used to enable hardware-software co-design, but today they are facing with the huge complexity of both hardware and software systems. In this thesis two different research works on Virtual Platforms are presented: the first one is intended for the hardware developer, to easily allow complex cycle accurate simulations of many-core SoCs. The second work exploits the parallel computing power of off-the-shelf General Purpose Graphics Processing Units (GPGPUs), with the goal of an increased simulation speed.

The term *Virtualization* can be used in the context of many-core systems not only to refer to the aforementioned hardware emulation tools (*Virtual Plat-forms*), but also to identify parallel programming aid tools and the higher level virtualization techniques used today to create software instances of computing

systems [21]. Virtualization can be used in fact for two other main purposes: 1) to help the programmer to achieve the maximum possible performance of an application, by hiding the complexity of the underlying hardware. 2) to efficiently exploit the high parallel hardware of many-core chips in environments with multiple active Virtual Machines, in which the accelerator might be able to sustain multiple execution requests from different virtual machines. In this last context beside the sharing of the accelerator, isolation between different virtual machines is required. This thesis is focused on virtualization techniques with the goal to mitigate, and overtake when possible, some of the challenges introduced by the many-core design paradigm.

Beside the design challenge, many-core chips themselves pose some challenges to programmers in order to effectively exploit their theoretical computing power. The most important and performance affecting is the Memory-Bandwidth Bottleneck: as a result of several design choices most many-core chips are composed by multi-core computing clusters, which are replicated over the design. Such design pattern is aimed at reducing the design effort, by just defining the architecture of a single cluster and then deploying several clusters on the same chip. For the sake of area/power efficiency, processing elements in a cluster are often not equipped with data cache memories, but rather they share an on-chip data scratch-pad memory. On-chip memories are usually fast but available in limited amount, and the data-set of an application can not always fit into. For this reason data are usually allocated in the much ample, but way slower, external memory. To mitigate the external-memory access latency, and due to the lack of a data cache, programmers are forced to apply copy-in/copy-out schemes to move chunks of data from the external memory to the on-chip memory (and vice versa). Such programming patterns usually exploit a Direct Memory Access Engine (DMA engine) to overlap the computation of a chunk of data with the copy of the next. In this thesis a memory virtualization infrastructure is presented, aimed at automatically dealing with external-memory-to-scratch-pad transfers. The virtualization framework treats the on-chip scratch-pad of a computing cluster as if it was a cache (Software Cache), and data is moved back and forth from external memory without the intervention of the programmer. The software cache is also able to deal with multiple concurrent accesses from the processing element of each cluster.

The last aspect investigated is virtualization at its higher level of abstraction, used in the domain of servers/cloud computing to create sand-boxed instances of operating systems (Virtual Machines) physically sharing the same hardware (hardware consolidation). Such type of virtualization has recently been made available also in the embedded systems domain, thanks to the advent of hardware assisted virtualization in ARM based processors [15]. In a virtualized system each hardware peripheral needs to have its virtual counterpart, to give each virtual machine the idea of a dedicated computing device. Since many-core chips are used as a co-processor (Accelerators) to general purpose multi-core processors (Host), they also need to be virtualized and made available to all the virtual machines running on the system. However modern many-core based systems are still under constant refinement, and current virtualization techniques are not able to overcome some of the architectural limitations. One of these limitations is memory sharing between host and accelerator. General purpose processors usually handle any memory region under virtual memory, giving a flexible and contiguous view of the physical memory even if data is not contiguously allocated. This goal is achieved by using a Memory Management Unit (MMU). On the other hand many-core chips are only able to access contiguously physical memory, being them not equipped with an MMU. This makes impossible for the co-processor to directly access any data buffer created from the host system. The problem of memory sharing is much more effective in a virtualized environment, where the accelerator could be sharing data with different virtual machines. This challenge is addressed in this thesis with the definition of a virtualization transparently enabling host-accelerator memory sharing, and implementing a resources sharing mechanism enabling the many-core accelerator to be used concurrently by several virtual machines.

| To my Family and Vanessa<br>and love de | for their unconditional su<br>uring these years. | $upport,\ trust$ |

|-----------------------------------------|--------------------------------------------------|------------------|

|                                         |                                                  |                  |

|                                         |                                                  |                  |

|                                         |                                                  |                  |

|                                         |                                                  |                  |

|                                         |                                                  |                  |

## Contents

| $\mathbf{C}$ | onter | nts                                                      | İ  |

|--------------|-------|----------------------------------------------------------|----|

| Li           | st of | Figures                                                  | v  |

| Li           | st of | Tables                                                   | ix |

| 1            | Intr  | roduction                                                | 1  |

|              | 1.1   | Thesis Contribution and Organization                     | F  |

|              | 1.2   | Many-core architectures                                  | 7  |

|              |       | 1.2.1 Cluster Architecture: Relevant Examples            | S  |

|              |       | 1.2.1.1 ST Microelectronics $P2012/STHORM$               | S  |

|              |       | 1.2.1.2 Plurality HAL - Hypercore Architecture Line      | 11 |

|              |       | 1.2.1.3 Kalray MPPA MANYCORE                             | 12 |

| <b>2</b>     | Vir   | tualSoC: a Virtual Platform for Design Space Exploration | 15 |

|              | 2.1   | Overview                                                 | 15 |

|              | 2.2   | Related work                                             | 18 |

|              | 2.3   | Target Architecture                                      | 20 |

|              | 2.4   | Many-core Accelerator                                    | 21 |

|              | 2.5   | Host-Accelerator Interface                               | 25 |

|              | 2.6   | Simulation Software Support                              | 27 |

|              | 2.7   | Evaluation                                               | 28 |

|              |       | 2.7.1 Experimental Setup                                 | 28 |

|              |       | 2.7.2 VirtualSoC Use Cases                               | 28 |

## CONTENTS

|   | 2.8           | Concl  | usions                                          | 31         |

|---|---------------|--------|-------------------------------------------------|------------|

| 3 | $\mathbf{GP}$ | -GPU   | based Acceleration of Virtual Platforms         | 33         |

|   | 3.1           | Overv  | riew                                            | 33         |

|   | 3.2           | Relate | ed Work                                         | 35         |

|   | 3.3           | Targe  | t architecture                                  | 38         |

|   | 3.4           | The F  | Germi GPU Architecture and CUDA                 | 39         |

|   |               | 3.4.1  | Key Implementative Issues for Performance       | 40         |

|   | 3.5           | Full S | imulation Flow                                  | 41         |

|   |               | 3.5.1  | Instruction Set Simulator                       | 42         |

|   |               | 3.5.2  | Cache Simulator                                 | 44         |

|   |               |        | 3.5.2.1 Communication buffers                   | 46         |

|   |               | 3.5.3  | Network-on-Chip Simulator                       | 47         |

|   | 3.6           | Exper  | rimental Results                                | 50         |

|   |               | 3.6.1  | Simulation time breakdown                       | 50         |

|   |               | 3.6.2  | Simulator Performance Evaluation                | 52         |

|   |               | 3.6.3  | Comparison with OVPSim                          | 55         |

|   | 3.7           | Concl  | usions                                          | 58         |

| 4 | Me            | mory ' | Virtualization: Software Caches                 | 61         |

|   | 4.1           | Overv  | riew                                            | 61         |

|   | 4.2           | Relate | ed work                                         | 65         |

|   | 4.3           | Imple  | mentation                                       | 68         |

|   |               | 4.3.1  | Software cache data structures                  | 68         |

|   |               | 4.3.2  | Logic implementation                            | 69         |

|   |               |        | 4.3.2.1 Lookup function                         | 69         |

|   |               |        | 4.3.2.2 Miss Handling routine                   | <b>7</b> 0 |

|   |               | 4.3.3  | Concurrency management                          | 71         |

|   |               | 4.3.4  | Direct-mapped vs set-associative software cache | 73         |

|   | 4.4           | Objec  | et Oriented caching extensions                  | 74         |

|   |               | 4.4.1  | Objects of arbitrary size                       | 77         |

|   |               | 4 4 2  | Programmer Interface                            | 78         |

## CONTENTS

|   | 4.5 | Evalua | ation                                                           |

|---|-----|--------|-----------------------------------------------------------------|

|   |     | 4.5.1  | Simulation infrastructure and experimental setup 80             |

|   |     | 4.5.2  | STHORM evaluation board 80                                      |

|   |     | 4.5.3  | Comparison between HWS and T&S locks 81                         |

|   |     | 4.5.4  | Micro-benchmark                                                 |

|   |     |        | $4.5.4.1$ Comparison between $cache\ lock\ and\ line\ lock\ 82$ |

|   |     |        | 4.5.4.2 Software cache implementation validation 83             |

|   |     | 4.5.5  | Object-Oriented extensions                                      |

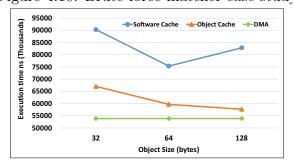

|   |     |        | 4.5.5.1 Line caching vs Object caching 87                       |

|   |     |        | 4.5.5.2 Use case 1: Bruteforce Matcher 89                       |

|   |     |        | 4.5.5.3 Use Case 2: Normalized Cross Correlation 90             |

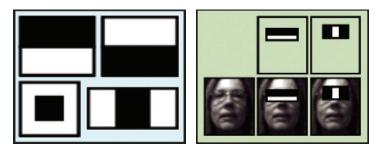

|   |     |        | 4.5.5.4 Use case 3: Face Detection                              |

|   | 4.6 | Concl  | usions                                                          |

| 5 | Mei | mory \ | Virtualization: DMA assisted prefetching 97                     |

|   | 5.1 | ·      | iew                                                             |

|   | 5.2 |        | ed work                                                         |

|   | 5.3 |        | ch techniques                                                   |

|   |     | 5.3.1  | Automatic prefetch schemes                                      |

|   |     | 5.3.2  | Programmer assisted prefetch                                    |

|   | 5.4 | Prefet | ch infrastructure                                               |

|   |     | 5.4.1  | Additional data structures                                      |

|   |     | 5.4.2  | Lookup routine extension                                        |

|   |     | 5.4.3  | Line prefetch subroutine                                        |

|   | 5.5 | Exper  | imental Results                                                 |

|   |     | 5.5.1  | Experimental Setup                                              |

|   |     | 5.5.2  | Prefetching Overhead Characterization                           |

|   |     | 5.5.3  | Case study 1: Normalized Cross Correlation 109                  |

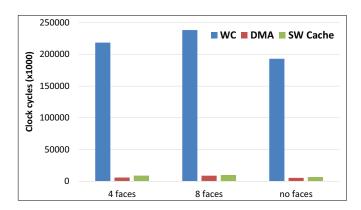

|   |     | 5.5.4  | Case study 2: Face Detection                                    |

|   |     | 5.5.5  | Case Study 3: Color Conversion                                  |

|   | 5.6 | Concl  | usions                                                          |

## CONTENTS

| 6                         | Mai    | y-Core accelerators virtualization in Linux/KVM environ- |    |

|---------------------------|--------|----------------------------------------------------------|----|

|                           | mer    | ts 11                                                    | 7  |

|                           | 6.1    | Overview                                                 | 7  |

|                           | 6.2    | Related work                                             | 0  |

|                           | 6.3    | Target platform                                          | 2  |

|                           | 6.4    | Virtualization of many-core accelerators                 | 3  |

|                           | 6.5    | Implementation                                           | 27 |

|                           |        | 6.5.1 PMCA virtual driver                                | 0  |

|                           |        | 6.5.2 PMCA virtual device                                | 0  |

|                           |        | 6.5.3 VM bridge                                          | 1  |

|                           |        | 6.5.4 PMCA host driver                                   | 2  |

|                           | 6.6    | Experimental Results                                     | 3  |

|                           |        | 6.6.1 Offload cost                                       | 3  |

|                           |        | 6.6.2 Memory copies breakdown                            | 5  |

|                           |        | 6.6.3 Real benchmarks                                    | 6  |

|                           | 6.7    | Conclusions                                              | 8  |

| 7                         | Cor    | clusions 14                                              | 1  |

|                           | 7.1    | Future research directions                               | :3 |

| Pι                        | ublic  | tions 14                                                 | 5  |

| $\mathbf{B}^{\mathbf{i}}$ | ibliog | raphy 14                                                 | 9  |

# List of Figures

| 1.1 | NVidia Tegra K1 floorplan                                              | 2  |

|-----|------------------------------------------------------------------------|----|

| 1.2 | Thesis logical organization                                            | 5  |

| 1.3 | Clustered many-core architecture organized in a 4x4 mesh and off-      |    |

|     | chip main-memory                                                       | 9  |

| 1.4 | Overview (simplified) of P2012/STHORM cluster architecture $$          | 10 |

| 1.5 | Plurality HAL architecture overview                                    | 12 |

| 1.6 | Overview (simplified) of Kalray MPPA architecture                      | 13 |

| 2.1 | Target simulated architecture                                          | 21 |

| 2.2 | Many-core accelerator                                                  | 22 |

| 2.3 | Mesh of trees 4x8 (banking factor of 2)                                | 23 |

| 2.4 | Execution model                                                        | 26 |

| 2.5 | Speedup due to accelerator exploitation                                | 30 |

| 2.6 | Benchmarks execution for varying L3 access latency (shared I-          |    |

|     | cache architecture)                                                    | 30 |

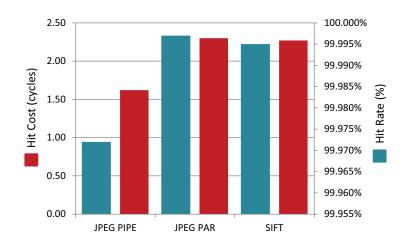

| 2.7 | Benchmarks hit rate and average hit cost                               | 31 |

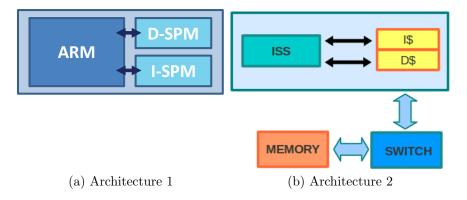

| 3.1 | Target simulated architecture                                          | 38 |

| 3.2 | Main simulation loop                                                   | 41 |

| 3.3 | Instruction decoding                                                   | 43 |

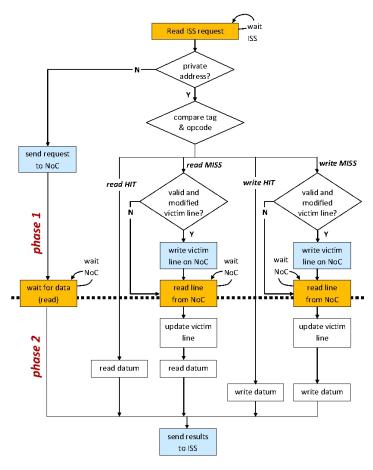

| 3.4 | Functional block diagram of a simulated cache (write-allocate) $\ .$ . | 45 |

| 3.5 | Functional block diagram of the operations executed for every          |    |

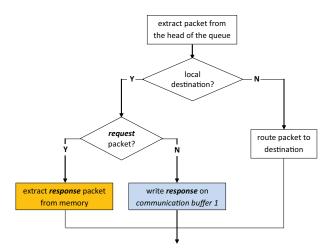

|     | queue in a simulated NoC switch                                        | 48 |

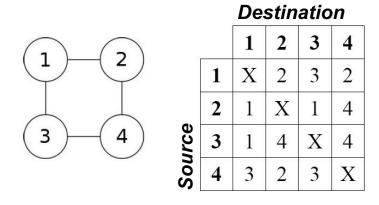

| 3.6 | $2\times2$ mesh and routing table (dimension-order)                    | 49 |

## LIST OF FIGURES

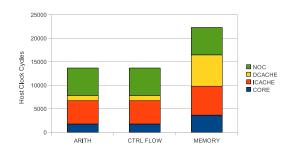

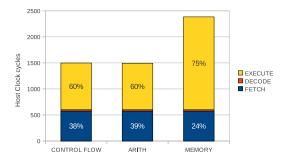

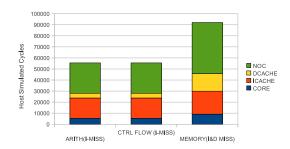

| 3.7  | Components Breakdown                                              | 51  |

|------|-------------------------------------------------------------------|-----|

| 3.8  | Pipeline Breakdown                                                | 51  |

| 3.9  | Cache Miss Breakdown                                              | 52  |

| 3.10 | Two different instances of a simulation node representing as many |     |

|      | architectural templates                                           | 53  |

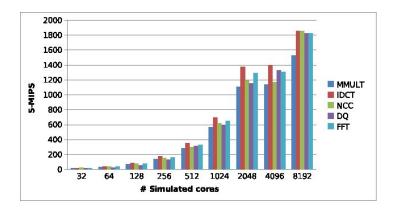

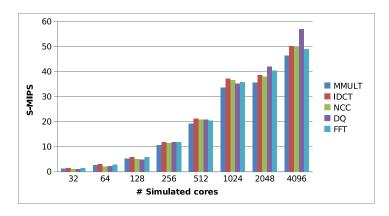

| 3.11 | Benchmarks performance - Architecture 1                           | 54  |

| 3.12 | Benchmarks performance - Architecture 2                           | 55  |

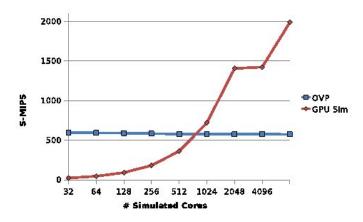

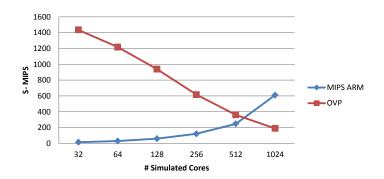

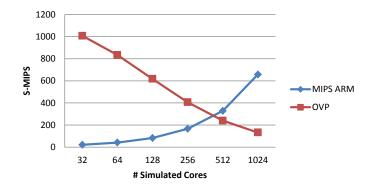

| 3.13 | OVP vs our simulation approach - Dhrystone                        | 56  |

| 3.14 | OVP vs our simulation approach - Fibonacci                        | 56  |

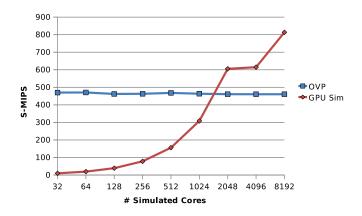

| 3.15 | OVP vs our simulation approach - MMULT                            | 57  |

| 3.16 | OVP vs our simulation approach - NCC                              | 58  |

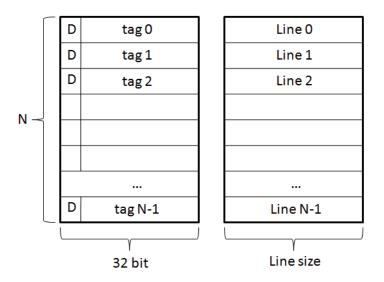

| 11   | Coftenant and a late atmentions                                   | eo. |

| 4.1  | Software cache data structures                                    | 68  |

| 4.2  | C implementation of the lookup phase, and STxP70 translation      | 70  |

| 4.0  | with jump in case of hit                                          | 70  |

| 4.3  | Parallel access to the Tags table                                 | 72  |

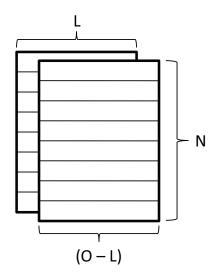

| 4.4  | Multi-dimensional lines organization                              | 78  |

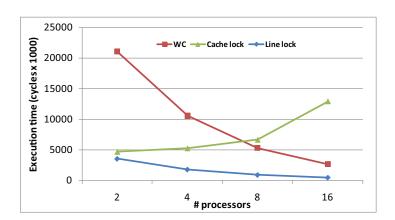

| 4.5  | Comparison between the cache lock and line lock implementation    | 82  |

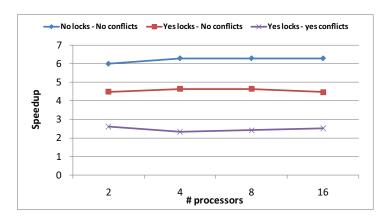

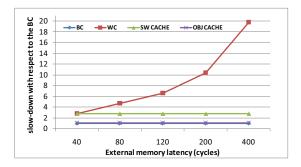

| 4.6  | Cache speedup with respect to the WC                              | 85  |

| 4.7  | STxP70 assembly code snippets                                     | 85  |

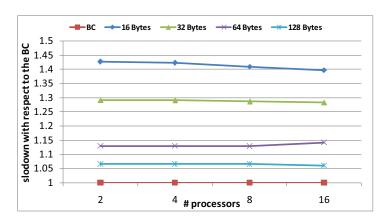

| 4.8  | Slowdown with respect to the BC when the software cache is used   |     |

|      | as an object cache                                                | 86  |

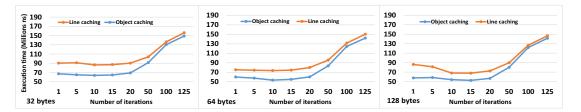

| 4.9  | Comparison between Line caching and Object caching,               | 87  |

| 4.10 | Brute force matcher case study                                    | 90  |

| 4.11 | NCC case study                                                    | 90  |

| 4.12 | Haar features used for Viola-Jones Face Detection                 | 92  |

| 4.13 | Face Detection case study                                         | 93  |

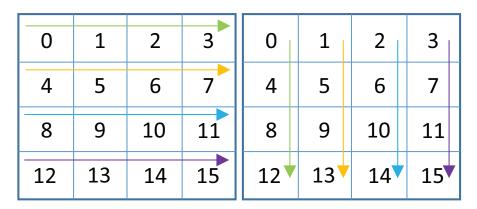

| 5.1  | Images access pattern                                             | 102 |

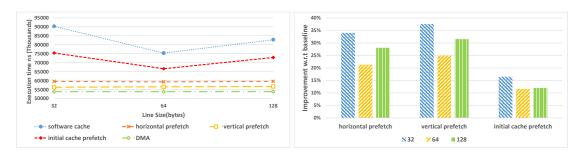

| 5.2  | NCC Benchmark execution time                                      | 110 |

| 5.3  | NCC Improvement due to prefetching with respect to the software   |     |

|      | cache without prefetching                                         | 110 |

## LIST OF FIGURES

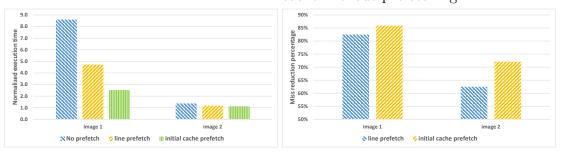

| 5.4  | Face Detection execution time normalized to a DMA hand-tuned                                                                       |     |

|------|------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | $implementation \dots  | 110 |

| 5.5  | Face Detection miss reduction percentage                                                                                           | 110 |

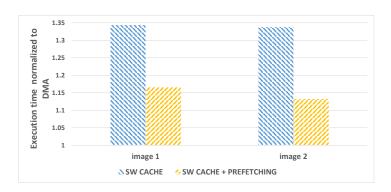

| 5.6  | Color conversion execution time normalized to DMA hand-tuned                                                                       |     |

|      | implementation                                                                                                                     | 112 |

| 6.1  | Target platform high level view                                                                                                    | 122 |

| 6.2  | Accelerator's partitions assigned to different applications $\ \ldots \ \ldots$                                                    | 124 |

| 6.3  | Example of application of<br>floading a kernel to the accelerator $\ . \ . \ .$                                                    | 125 |

| 6.4  | Memory handling in presence of an IOMMU (left side), and in                                                                        |     |

|      | absence of IOMMU (right side) $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$                                                       | 125 |

| 6.5  | Virtualization infrastructure overview                                                                                             | 126 |

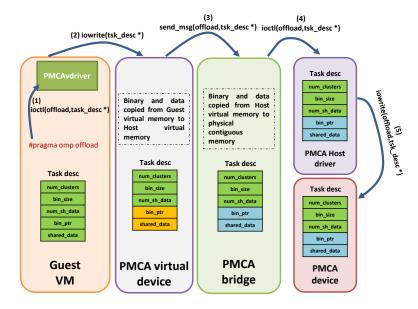

| 6.6  | Task offload descriptor                                                                                                            | 128 |

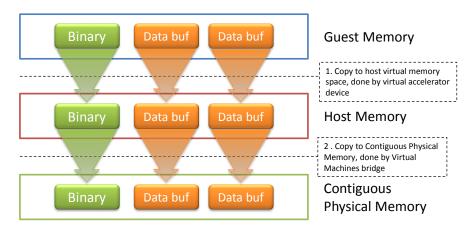

| 6.7  | Data copies performed                                                                                                              | 129 |

| 6.8  | Flow of the offload descriptor through the virtualization infrastruc-                                                              |     |

|      | $ \text{ture}  \dots $       | 129 |

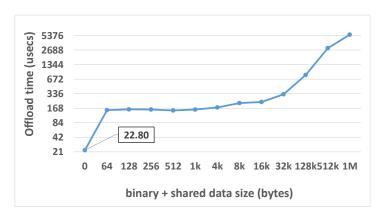

| 6.9  | Offload cost                                                                                                                       | 133 |

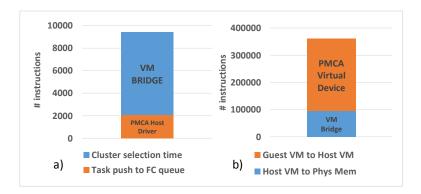

| 6.10 | a) Breakdown of the constant component of the offload time. b)                                                                     |     |

|      | Breakdown of the copy time when 128 KB of data are copied                                                                          | 134 |

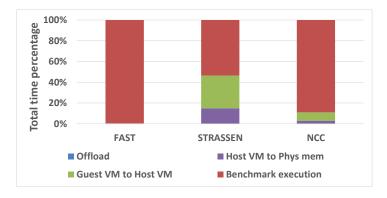

| 6.11 | Distribution of memory copies over the total execution time of                                                                     |     |

|      | benchmarks                                                                                                                         | 136 |

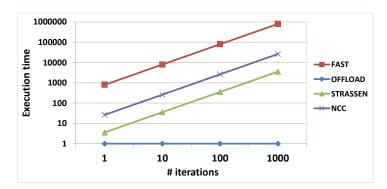

| 6.12 | Execution time over multiple iterations, normalized to (offload                                                                    |     |

|      | time + memory copies)                                                                                                              | 137 |

## LIST OF FIGURES

## List of Tables

| 2.1 | Experimental Setup                                                  | 29  |

|-----|---------------------------------------------------------------------|-----|

| 3.1 | Cache design parameters                                             | 44  |

| 3.2 | Benchmarks scaled-up datasets                                       | 54  |

| 4.1 | Comparison between T&S and HWS locks                                | 81  |

| 5.1 | Prefetch overhead added to the lookup function, each cell contains: |     |

|     | #instructions / #clock cycles (line size 32 bytes)                  | 107 |

| 6.1 | Benchmarks details                                                  | 136 |

## Chapter 1

## Introduction

The advent of many-core architectures has profoundly changed the panorama of both hardware and software design. Embedded systems today are rapidly moving from small homogeneous systems with few powerful computing units, towards the much complex heterogeneous *Multi-Processor Systems on Chip* (MPSoC) embedding on the same die several small computing units. The increasing number of computing units allows embedded systems to be exploited for workloads usually tailored for workstation or high performance computing, representative examples are *Machine Vision* and *Scientific Computation* [3].

Energy efficiency in terms of OPS/Watt is the most influencing factor for an embedded system design, with the future target to provide 100 GOPS within the power envelope of 1W [129]. Heterogeneity is used as a key tool to increase the energy efficiency of a MPSoC and sustain the disruptive computing power delivered by such systems, by staying within an always shrinking market-driven power budget. Various design schemes are available today: systems composed by a combination of powerful and energy efficient cores [81], and also designs exploiting various types of specialized or general purpose parallel accelerators [96, 134]. The combination of different types of computing units allows the system to adapt to different workloads, providing computing power when running complex tasks or running on the more energy efficient cores when the performance is not required. And finally offloading computation to an accelerator, when high parallel

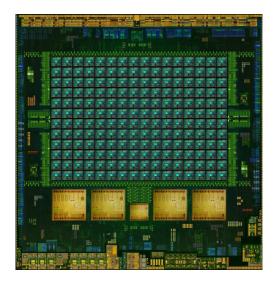

Figure 1.1: NVidia Tegra K1 floorplan

computing capabilities are required. A state-of-the-art heterogeneous MPSoC is shown in Figure 1.1, which is the NVidia Tegra-K1. It is immediately visible in the bottom of the image that a multi-core processor (*Host processor*), composed by four powerful cores and one smaller and more energy efficient, is flanked by a many-core embedded GPU acting as a parallel co-processor (*Accelerator*). The GPU is placed exactly above the host processor.

However, even if MPSoCs are designed to deliver high computing performance with a low power consumption, achieving this goals is not a trivial task. Such new design paradigm opens the door to several challenges. In this thesis two of the many possible are addressed: *Hardware design space exploration complexity* and *Performance scalability*.

#### Hardware design space exploration complexity

Hardware designers have been relying for years on virtual platforms as a tool to reduce the time to market of a chip design, forecast performance and power consumption and also to enable early software development before the actual hardware is available. However, the complexity of modern systems forces hardware designers to cope with a huge design space to be explored to find the best trade-off among energy consumption, area and performance delivered. Several simulation

frameworks are available today off-the-shelf [24, 29, 75, 77, 84, 87, 126, 136], but almost all of them suffer of three main problems, which make them not suitable to model a complex MPSoC:

- 1. Lack of models for deep micro-architectural components: hardware designs with more than hundreds of computing units use various architectural components, to allow efficient and scalable communication between cores (e.g. Networks-On-Chip) and complex memory hierarchies. Such components have to be modeled at the micro-architectural level to enable accurate power estimations and performance measurements.

- 2. Lack of support for *Full System* simulation: modern MPSoCs are composed by a Host processor and one or more accelerators. The host processor is usually in charge of executing an operating system (e.g. Linux), while the accelerators are used as a co-processors to speedup the execution of computationally heavy tasks. In this scenario the interaction between host processor and accelerators, being it a memory transfer or a synchronization, may have a significant effect on applications performance. Virtual platforms have to accurately model such interactions to enable precise application profiling.

- 3. Sequential simulation: most of the available modeling tools are relying on a sequential execution model, in which all components of the design are simulated in sequence by a single application thread. In the near future MPSoCs will feature thousand of computing units, and such a modeling technique will make the simulation time of a reasonable application to be to slow for practical use.

#### Performance scalability

Even if Pollack's rule sates that the increase of performance is proportional to the square root of the increase in complexity of a system, achieving such performance is not a trivial task. Programmers seeking for applications performance are thus obliged to know architectural specific details, and apply complex programming patterns to adapt their applications to the specific target hardware.

One of the most performance affective problems is the memory wall [133], which is due to a huge gap in the technological advance between CPU and memory speed. An efficient utilization of the memory hierarchy is thus critical for performance, especially in a system with thousand of cores where the required memory bandwidth can be extremely high. However due to some design choices taken for the sake of area and power consumption reduction, the hardware is not always able to automatically fill the gap of memory latency. One example is the choice to substitute data caches with scratchpad memories, because the latter with the same size in bytes occupies 30% less area than a cache [20]. Programmers can not rely anymore on data caches to hide the external memory access latency, and try to overlap as much as possible computation with communication. One common programming pattern is DMA double buffering, in which computation is divided in chunks and while the actual is computed the next one is read from external memory. Such type of design choice forces application programmers to know deep hardware related features to boost the performance of their code, leading often to complex and error-prone programming. A software runtime is presented in this thesis which automatically handles external-memory-to-scratchpad memory transfers, without any intervention of the programmer.

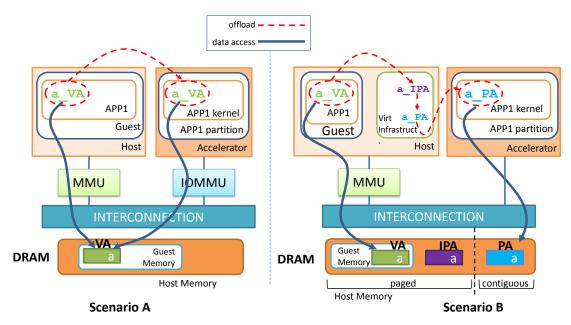

Another design related challenge is memory sharing between host processor and many-core accelerator. A general purpose processor, when running an operating system, uses a virtual memory abstraction to handle the whole physical memory available on a platform. This is possible thanks to a Memory Management Unit (MMU), which is in charge to translate any virtual address to its equivalent in physical memory. State-of-the-art many-core accelerators are often not equipped with an MMU [101, 104], meaning that only physical memory addresses can be used from within the accelerator. In a typical application the Host processor acting as a master is in charge of handling the main application flow, and input/output data buffers shared with the accelerator are created under the virtual memory abstraction. Since most many-core accelerators are only able to

Figure 1.2: Thesis logical organization

directly access physical memory, input/output buffers have to be copied into a memory region which is not handled under virtual memory, before being accessible from the accelerator. Those memory copies affect the overall performance of an application, limitating also the usability of the accelerator itself for real applications. An example is system virtualization, which has recently been enabled on embedded systems thanks to the advent of hardware support for virtualization in ARM cores [15]. In a virtualized system several instances of an operating system (Guest) run at the same time on the same hardware, and all peripherals need to have a virtual counterpart to be visible by all guests. In this context several memory virtualization layers are involved, and a many-core accelerator without an MMU can not be easily virtualized and used by all the guests running on a system. In this dissertation, as last contribution, a virtualization framework for many-core accelerators is presented which overcomes the lack of an MMU.

## 1.1 Thesis Contribution and Organization

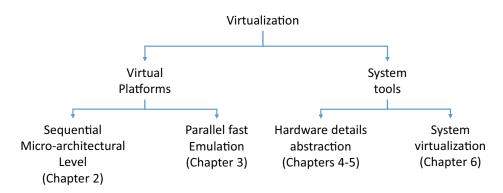

The contribution of this dissertation can be organized under the broader topic of *Virtualization*. The work presented in this thesis can be divided in two main fields (Figure 1.2) for which Virtualization can be exploited: *Virtual Platforms* and *System Tools*.

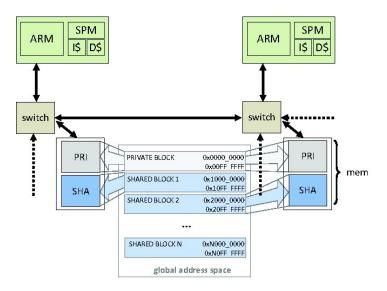

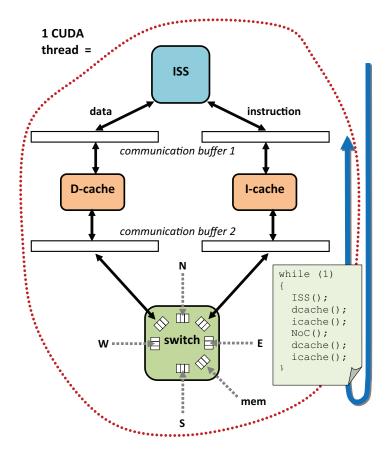

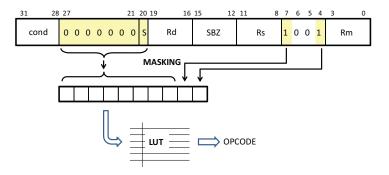

Virtual Platforms: used for design space exploration and early software development, are a virtual representation of an hardware system which can be modeled at different levels of abstraction. In particular in this thesis in **Chapter** 2 is presented VirtualSoC, a SystemC [7] based virtual platform. VirtualSoC can perform the full system simulation of MPSoCs, where the host processor is modeled by QEMU [25] and a many-core accelerator is completely written in SystemC. The focus of this virtual platform is on the many-core accelerator and its interaction with the host processor. In particular it is possible to model at the micro-architectural level various on-chip interconnection mediums, memories, instruction and data caches and computing units. The models used are heavily configurable to perform an exhaustive design space exploration, and allow also to perform performance and power analyses based on user provided models. In Chapter 3 the simulation of large systems is addressed, presenting the internals of a tool for parallel simulation (SIMinG-1k) exploiting commodity hardware like GP-GPUs. SIMinG-1k is able to model a many-core system with up to 4096 computing units (ARM and X86 ISA) connected using an On Chip Network(NoC), and sharing a common memory hierarchy organized under the PGAS <sup>1</sup> scheme. SIMinG-1k can be used for the design of parallel programming models and high level design space exploration.

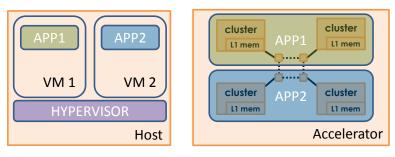

System tools: Virtualization can be considered a system tool when used to ease the work of programmers, by abstracting hardware details of the platform, enclosing them in a higher level (virtual) representation. It can also be considered a system tool when talking of system virtualization, where several instances of an operating system run indistinctly on the same hardware and all have the view of dedicated (virtual) hardware system. In this dissertation in Chapter 4 and Chapter 5 is presented a memory virtualization framework targeting STHORM [88], a cluster based many-core accelerators with on chip scratchpad data memories. The framework is able to automatically handle the on-chip scratchpad memory in each cluster as a data cache (Software Cache), relieving the program-

<sup>&</sup>lt;sup>1</sup>PGAS: Partitioned Global Address Space, which assumes a global memory address space that is logically partitioned among all the computing nodes in the system

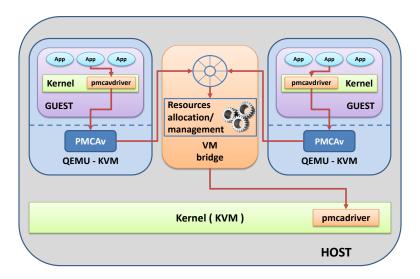

mer from the task of hiding the external memory access latency. Since each computing cluster is composed by 16 processors, the software cache runtime is able to orchestrate parallel accesses to a shared cache structure exploiting the hardware synchronization facilities provided by the STHORM chip. Moreover a DMA-based prefetching extension is presented with the aim of further mitigating the external memory access latency. **Chapter 6** is focused on system virtualization. We present a framework for the virtualization of IOMMU-less many-core accelerator, which enables the virtualization of many-core chips in Linux/KVM environments. Beside the actual sharing of the many-core accelerator among different virtual machines, the framework presented is also able to overcome the problem of memory sharing with the Host processor, thanks to a fully-software memory sharing subsystem. It is demonstrated in the chapter that even in absence of an MMU, a many-core accelerator can be still utilized to obtain concrete benefits in terms of application speedup.

Finally, in **Chapter 7** the dissertation is concluded summarizing the main results obtained by this research work.

## 1.2 Many-core architectures

Several variants of many-core architectures have been designed and are in use for years now. As a matter of fact, since the mid 2000s we observed the integration of an increasing number of cores onto a single integrated circuit die, known as a Chip Multi-Processor (CMP) or Multi-Processor System-on-Chip (MPSoC), or onto multiple dies in a single chip package. Manufacturers still leverage Moore's Law [92] (doubling of the number of transistors on chip every 18 months), but business as usual is not an option anymore: scaling performance by increasing clock frequency and instruction throughput of single cores, the trend for electronic systems in the last 30 years, has proved to be not viable anymore [11, 31, 52]. As a consequence, computing systems moved to multi-core<sup>1</sup> designs and subsequently,

<sup>&</sup>lt;sup>1</sup>For clarity, the *multi-core* term is intended for platforms with 2 to few tens cores, while with *many-core* we refer to systems with tens to hundreds of cores. The distinction is not rigid

thanks to the integration density, to the many-core era where energy-efficient performance scaling is achieved by exploiting large-scale parallelism, rather than speeding up the single processing units [11, 31, 52, 76].

Such trend can be found in a wide spectrum of platforms, ranging from general purpose computing, high-performance to the embedded world.

In the general purpose domain we observed the first multi-core processors almost a decade ago. Intel core duo [55] and Sony-Toshiba-IBM (STI) Cell Broadband Engine [71] are notable examples of this paradigm shift. The trend did not stop and nowadays we have in this segment many-core examples such as the TILE-Gx8072 processor, comprising seventy-two cores operating at frequencies up to 1.2 GHz [40]. Instead, when performance is the primary requisite of the application domain, we can cite several notable architectures such as Larrabee [115] for visual computing, the research microprocessors Intel's SCC [68] and Terascale project [130] and, more recently, Intel's Xeon Phi [63]. In the embedded world, we are observing today a proliferation of many-core heterogeneous platforms. The so-called asymmetric of heterogeneous design features many small, energy-efficient cores integrated with a full-blown processor. Its is emerging as the main trend in the embedded domain, since it represents the most flexible and efficient design paradigm. Notable examples of such architectures are the AMD Accelerated Processing Units [33], Nvidia TEGRA family [96], STMicroelectronics P2012/STHORM [27] or Kalray's many-core processors [72].

The work presented in this thesis is focused on the embedded domain where, more than in other areas, modern high-end applications are asking for increasingly stringent and irreconcilable requirements. An outstanding example consist of the mobile market. As highlighted in [129], the digital workload of a smartphone (all control, data and signal processing) amounts to nearly 100 Giga Operations Per Second (GOPS) with a power-budget of 1 Watt. Moreover, workload requirements increase at a steady rate, roughly by an order of magnitude every 5 years.

From the architectural point of view, with the evolution from tens of cores to and throughout the dissertation, the terms multi-core and many-core may be used indistinctly.

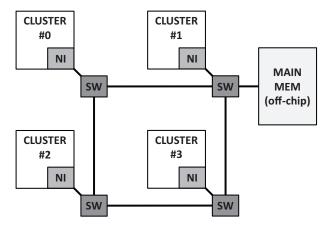

the current integration capabilities in the order of hundreds, the most promising architectural choice for many-core embedded systems is *clustering*. In a clustered platform, processing cores are grouped into small- medium-sized clusters (i.e. few tens), which are highly optimized for performance and throughput. Clusters are the basic "building blocks" of the architecture, and scaling to many-core is obtained by the replication and global interconnection through a scalable medium such as a Network-on-Chip (NoC) [26, 45]. Figure 1.3 shows a reference clustered

Figure 1.3: Clustered many-core architecture organized in a 4x4 mesh and off-chip main-memory

many-core architecture, organized in 4 clusters with a 4x4 mesh-like NoC for global interconnection. Next section reports some representative examples of recent architectures with a focus at the cluster level.

### 1.2.1 Cluster Architecture: Relevant Examples

The cluster architecture considered in this work is representative of a consolidated trend of embedded many-core design. Few notable examples are described, highlighting the most relevant characteristics of such architectures.

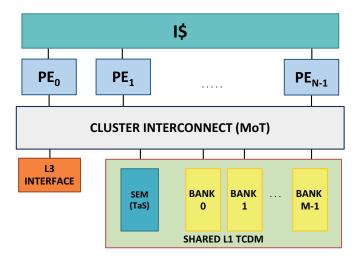

#### 1.2.1.1 ST Microelectronics P2012/STHORM

Platform 2012 (P2012), also known as STHORM [27], is a low-power programmable many-core accelerator for the embedded domain designed by ST Microelec-

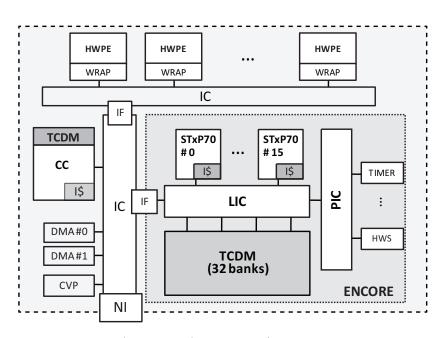

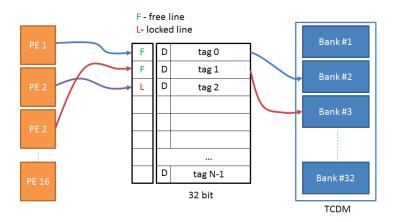

tronics [120]. The P2012 project targets next-generation data-intensive embedded applications such as multi-modal sensor fusion, image understanding, mobile augmented reality [27]. The computing fabric is highly modular being structured in clusters of cores, connected through a Globally Asynchronous Network-on-Chip (GANoC) and featuring a shared memory space among all the cores. Each cluster is internally synchronous (one frequency domain) while at the global level the system follows the GALS (Globally Asynchronous Locally Synchronous) paradigm. In Figure 1.4 is shown a simplified block scheme of the internal structure of a single cluster. Each cluster is composed of a Cluster Controller (CC) and a multi-core computing engine, named ENCore, made of 16 processing elements. Each core is a proprietary 32-bit RISC core (STxP70-V4) featuring a floating point unit, a private instruction cache and no data cache.

Processors are interconnected through a low-latency high-bandwidth logarithmic interconnect and communicate through a fast multi-banked, multi-ported tightly-coupled data memory (TCDM). The number of memory ports in the TCDM is equal to the number of banks to allow concurrent accesses to different banks. Conflict-free TCDM accesses are performed with a two-cycles latency.

Figure 1.4: Overview (simplified) of P2012/STHORM cluster architecture

The logarithmic interconnect consists of fully combinatorial Mesh-of-Trees (MoT) interconnection network. Data routing is based on address decoding: a first-stage checks if the requested address falls within the TCDM address range or has to be directed off-cluster. The interconnect provides fine-grained address interleaving on the memory banks to reduce banking conflicts in case of multiple accesses to logically contiguous data structures. If no bank conflicts arise, data routing is done in parallel for each core. In case of conflicting requests, a round-robin based scheduler coordinates accesses to memory banks in a fair manner. Banking conflicts result in higher latency, depending on the number of concurrent conflicting accesses. Each cluster is equipped with a Hardware Synchronizer (HWS) which provides low-level services such as semaphores, barriers, and event propagation support, two DMA engines, and a Clock Variability and Power (CVP) module. The cluster template can be enhanced with application specific hardware processing elements (HWPEs), to accelerate key functionalities in hardware. They are interconnected to the ENCore with an asynchronous local interconnect (LIC). The first release of P2012 (STHORM) features 4 homogeneous clusters for a total of 69 cores and a software stack based on two programming models, namely a component-based Native Programming Model (NPM) and OpenCL-based [121] (named CLAM - CL Above Many-Cores) while OpenMP [42] support is under development.

#### 1.2.1.2 Plurality HAL - Hypercore Architecture Line

Plurality Hypercore [6] is an energy efficient general-purpose machine made of several RISC processors. The number of processors can range from 16 up to 256 according to the processor model.

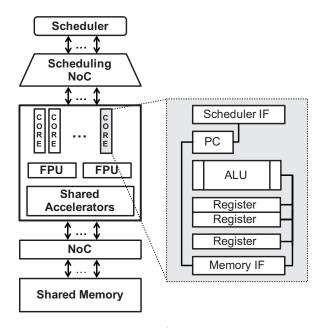

Figure 1.5 shows the overall architecture and the single processor structure, which is designed with the goal of simplicity and efficiency in mind (no I/D caches nor private memory, no branch speculation) to save power and area. The memory system (i.e., I/D caches, off-chip main memory) is shared and processors access it through a high-performance logarithmic interconnect, equivalent to the interconnection described in Section 1.2.1.1. Processors share one or more Floating

Figure 1.5: Plurality HAL architecture overview

Point Units, and one or more shared hardware accelerators can be embedded in the design. This platform can be programmed with a task-oriented programming model, where the so-called "agents" are specified with a proprietary language. Tasks are efficiently dispatched by a scheduler/synchronizer called Central Synchronizer Unit (CSU), which also ensures workload balancing.

#### 1.2.1.3 Kalray MPPA MANYCORE

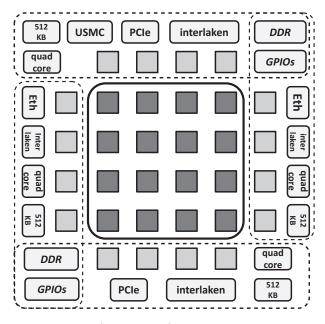

Kalray Multi Purpose Processor Array (MPPA) [72] is a family of low-power many-core programmable processors for high-performance embedded systems. The first product of the family, MPPA-256, deploys 256 general-purpose cores grouped into 16 tightly-coupled clusters using a 28nm manufacturing process technology.

The MPPA MANYCORE chip family scales from 256 to 1024 cores with a performance of 500 Giga operations per second to more than 2 Tera operations per second with typical 5W power consumption. Global communication among the clusters is based on a Network-on-Chip. A simplified version of the architecture is shown in Figure 1.6.

Figure 1.6: Overview (simplified) of Kalray MPPA architecture

Each core is a proprietary 32-bit ISA processor with private instruction and data caches. Each cluster has a 2MB shared data memory for local processors communication and a full-crossbar. Clusters are arranged in a 4x4 mesh and four I/O clusters provide off-chip connectivity through PCI (North and South) or Ethernet (West and East). Every I/O cluster has a four-cores processing unit, and N/S clusters deploy each a DDR controller to a 4GB external memory. The platform acts as an accelerator for an x86-based host, connected via PCI to the North I/O cluster. Accelerator clusters run a lightweight operative system named NodeOS [95], while I/O clusters run an instance of RTEMS [97].

## Chapter 2

# VirtualSoC: a Virtual Platform for Design Space Exploration

## 2.1 Overview

Performance modeling plays a critical role in the design, evaluation, and development of computing architecture of any segment, ranging from embedded to high performance processors. Simulation has historically been the primary vehicle to carry out performance modeling, since it allows for easily creating and testing new designs several months before a physical prototype exists. Performance modeling and analysis are now integral to the design flow of modern computing systems, as it provides many significant advantages: i) accelerates time-to-market, by allowing the development of software before the actual hardware exists; ii) reduces development costs and risks, by allowing for testing new technology earlier in the design process; iii) allows for exhaustive design space exploration, by evaluating hundreds of simultaneous simulations in parallel.

High-end embedded processor vendors have definitely embraced the heterogeneous architecture template for their designs as it represents the most flexible and efficient design paradigm in the embedded computing domain. Parallel architecture and heterogeneity clearly provide a wider power/performance scaling, combining high performance and power efficient general-purpose cores along with massively parallel many-core-based accelerators. Examples and results of this evolution are AMD Fusion [33], NVidia Tegra [96] and Qualcomm Snapdragon [107]. Besides the complex hardware, generally these kinds of platforms host also an advanced software eco-system, composed by an operating system, several communication protocol stacks, and various computational demanding user applications.

Unfortunately, as processor architectures get more heterogeneous and complex, it becomes more and more difficult to develop simulators that are both fast and accurate. Cycle-accurate simulation tools can reach an accuracy error below 1-2%, but they typically run at a few millions of instructions per hour. The necessity to efficiently cope with the huge HW/SW design space provided by this target architecture makes clearly full-system simulator one of the most important design tools. Clearly, the use of slow simulation techniques is challenging especially in the context of full-system simulation. In order to perform an affordable processor design space exploration or software development for the target platform, trade-off accuracy for speed is thus necessary by implementing new virtual platforms that allow for faster simulation speed at the expense of modeling fewer micro-architecture details of not-critical hardware components (like the host processor domain), while keeping high-level of accuracy for the most critical hardware components (like the manycore accelerator domain).

We present in this chapter VirtualSoC, a new virtual platform prototyping framework targeting the full-system simulation of massively parallel heterogeneous system-on-chip composed by a general purpose processor (i.e. intended as platform coordinator and in charge of running an operating system) and a many-core hardware accelerator (i.e. used to speed-up the execution of computing intensive applications or parts of them). VirtualSoC exploits the speed and flexibility of QEMU, allowing the execution of a full-fledged Linux operating system, and the accuracy of a SystemC model for many-core-based accelerators.

The specific features of VirtualSoC are:

• Since it exploits QEMU for the host processor emulation, unmodified operating systems can be booted on VirtualSoC and the execution of unmod-

ified ARM binaries of applications and existing libraries can be simulated on VirtualSoC.

- VirtualSoC enables accurate manycore-based accelerator simulation. We

designed a full software stack allowing the programmer to exploit the hardware accelerator model implemented in SystemC, from within a user-space

application running on top of QEMU. This software stack comprise a Linux

device driver and a user-level programming API.

- The host processor (emulated by QEMU) and the SystemC accelerator model can run in an asynchronous way, where a non-blocking communication interface has been implemented enabling parallel execution between QEMU and SystemC environments.

- Beside the interface between QEMU and the SystemC model, we also implemented a synchronization protocol able to provide a good approximation of the global system time.

- VirtualSoC can be also used in stand-alone mode, where only the hardware accelerator is simulated, thus enabling accurate design space explorations.

To the best of our knowledge, we are not aware of any existing public domain, open source simulator that rivals the characteristics of VirtualSoC. This chapter focuses on the implementation details of VirtualSoC and evaluates the performance of various benchmarks and presents some example case studies using VirtualSoC.

The rest of the chapter is structured as follows: in Section 2.2 we provide an overview of related work, in Section 2.3 we present the target architecture, focusing on the many-core accelerator in Section 2.4. The implementation of the proposed platform is discussed in Section 2.5. Software simulation support is described in Section 2.6, finally experimental results and conclusions are presented in Sections 2.7 and 2.8.

## 2.2 Related work

The importance of full-system emulation is confirmed by the considerable amount of effort committed by both industry and research communities in developing such designing tools as more efficient as possible. We can cite several examples, like Bochs [77], Simics [84], Mambo [29], Parallel Embra [75], PTLsim [136], AMD SimNow [24], OVPSim [126] and SocLib [87].

QEMU [25] is one of the most widely used open-source emulation platform. QEMU supports cross-platform emulation and exploits binary translation for emulating the target system. Taking advantage of the benefits of binary translation, QEMU is very efficient and functionally correct, however it does not to provide any accurate information about hardware execution time. In [59] authors have implemented program instrumentation capabilities to QEMU for user application program analysis. This work has only been done for the user mode of QEMU and it cannot be exploited for system performance measurements (e.g. device driver). Moreover, profiling based on program instrumentation can heavily change the execution flow of the program itself, leading to behaviors which will never happen when executing the program in the native fashion. Authors in [89] have instead presented pQEMU, which simulates the timing of instruction executions and memory latencies. Instruction execution timings are simulated using instruction classification and weight coefficients, while memory latency is simulated using a set-associative cache and TLB simulator. This kind of approach can lead to a significant overhead due to the different simulation stages (i.e. cache simulation, TLB simulation), and even in this case the proposed framework can only run user-level applications without the support of an operating system.

QEMU lacks also of any accurate co-processors simulation capabilities. Authors in [109] interfaced QEMU with a many-core co-processor simulator running on an nVidia GPGPU [103]. Despite the co-processor simulator described in [103] is able to simulate thousands of computing units connected through a NoC, it runs at a high level of abstraction and does not provide precise measurements from the simulated architecture. Moreover authors do not address the problem of timing synchronization between QEMU and the co-processor simulation.

Other works have been mainly concentrated on enabling either cycle accurate instruction set simulators for the general purpose processor part or SystemC-based simple peripherals, without considering complex many-core-based accelerators [54].

When interfacing QEMU with the SystemC framework, several implementation aspects and decisions need to be accurately taken into account, since development choices can limit and constraint the performance of the overall emulation environment. The optimal implementation should not possibly affect efficiency, flexibility and scalability.

Establishing the communication between QEMU and SystemC simulator through inter-process communication socket is another approach. Authors in [106] use such facility between a new component of QEMU, named QEMU-SystemC Wrapper, and a modified version of the SystemC simulation kernel. The exchanged messages have the purpose not only to transmit data and interrupt signals but also to keep the simulation time synchronized between the simulation kernels. However using heavy processes does not allow fast and efficient memory sharing, which in this case can be achieved only using shared memory segments. Moreover, Unix Domain Sockets are less efficient, in terms of performance and flexibility, than direct communication between threads.

QEMU-SystemC [91] allows devices to be inserted into specific addresses of QEMU and communicates by means of the PCI/AMBA bus interface. However, QEMU-SystemC does not provide the accurate synchronization information that can be valuable to the hardware designers. [80] integrates QEMU with a SystemC-based simulation development environment, to provide a system-level development framework for high performance system accelerators. However, this approach is based on socket communication, which strongly limits its performance and flexibility. Authors in [135] suggested an approach based on threads since context switches between threads are generally much faster than between processes. However, communication among QEMU and SystemC uses a unidirectional FIFO, limiting the interaction between QEMU and the SystemC model.

We present in this chapter a new emulation framework based on QEMU and

SystemC which overcomes these issues. We chose QEMU amongst all simulators cited (e.g. OVPSim [126], Soclib [126]) because it is fast, open-source and also very flexible enabling its extension with a moderate effort. Our approach is based on thread parallelization and memory sharing to obtain a complete heterogeneous SoC emulation platform. In our implementation the target processor and the SystemC model can run in an asynchronous way, where non-blocking communication is implemented through the use of shared memory between threads. Beside the interface between QEMU and a SystemC model, we also present a lightweight implementation of a synchronization protocol able to provide a good approximation of a global system time. Moreover, we designed a full SW stack allowing the programmer to exploit the HW model implemented in SystemC, from within a user-space application running on top of QEMU. This software stack comprise a Linux device driver and a user-level programming API.

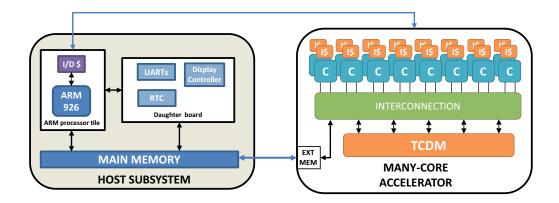

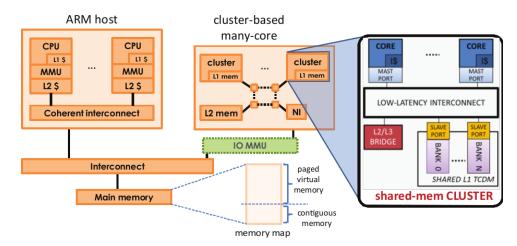

# 2.3 Target Architecture

Modern embedded SoCs are moving toward systems composed by a general purpose multi-core processor accompanied by a more energy efficient and powerful many-core accelerator (e.g. GPU). In these kinds of systems the general purpose processor is intended as a coordinator and is in charge of running an operating system, while the many-core accelerator is used to speed up the execution of computing intensive applications or parts of them. Despite their great computing power, accelerators are not able to run an operating system due to the lack of all needed surrounding devices and to the simplicity of their micro-architectural design. The architecture targeted by this work (shown in Figure 6.1) is representative of the above mentioned platforms and composed by a many-core accelerator and an ARM-based processor.

The ARM processor is emulated by QEMU which models an ARM926 processor, featuring an ARMv5 ISA, and interfaced with a group of peripherals needed to run a full-fledged operating system (ARM Versatile Express baseboard). The many-core accelerator is a SystemC cycle-accurate MPSoC simulator. The ARM

Figure 2.1: Target simulated architecture

processor and the accelerator share the main memory, used as communication medium between the two. The accelerator target architecture features a configurable number of simple RISC cores, with private or shared I-cache architecture, all sharing a Tightly Coupled Data Memory (TCDM) accessible via a local interconnection. The state-of-the-art programming model for this kind of systems is very similar to the one proposed by OpenCL [73]: a master application is running on the host processor which, when encounters a data or task parallel section, of-floads the computation to the accelerator. The master processor is in charge also of transferring input and output data.

# 2.4 Many-core Accelerator

The proposed target many-core accelerator template can be seen as a cluster of cores connected via a local and fast interconnect to the memory subsystem. The following sub-sections describe the building blocks of such cluster, shown in Figure 2.2.

### **Processing Elements**

the accelerator consists of a configurable number of 32-bit RISC processor. In the specific platform instance that we consider in this chapter we use ARMv6 processor models, specifically the ISS in [65]. To obtain timing accuracy we

Figure 2.2: Many-core accelerator

modified its internal behavior to model a Harvard architecture and we wrapped the ISS in a SystemC [7] module.

### Local interconnect

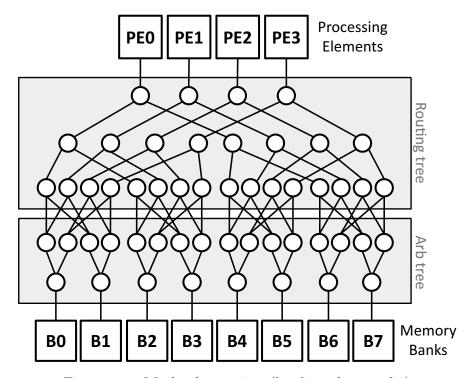

the local interconnection has been modeled, from a behavioral point of view, as a parametric Mesh-of-Trees (MoT) interconnection network (logarithmic interconnect) to support high-performance communication between processors and memories resembling the hardware module described in [110], shown in Figure 2.3. The module is intended to connect processing elements to a multi-banked memory on both data and instruction side. Data routing is based on address decoding: a first-stage checks if the requested address falls within the local memory address range or has to be directed to the main memory. To increase module flexibility this stage is optional, enabling explicit L3 data access on the data side while, on the instruction side, can be bypassed letting the cache controller take care of L3 memory accesses for lines refill. The interconnect provides fine-grained address interleaving on the memory banks to reduce banking conflicts in case of multiple accesses to logically contiguous data structures. The crossing latency consists of one clock cycle. In case of multiple conflicting requests, for fair access to memory banks, a round-robin scheduler arbitrates access and a higher

number of cycles is needed depending on the number of conflicting requests, with no latency in between. In case of no banking conflicts data routing is done in parallel for each core, thus enabling a sustainable full bandwidth for processors-memories communication. To reduce memory access time and increase shared memory throughput, read broadcast has been implemented and no extra cycles are needed when broadcast occurs.

Figure 2.3: Mesh of trees 4x8 (banking factor of 2)

### **TCDM**

On the data side, a L1 multi-ported, multi-banked, Tightly Coupled Data Memory (TCDM) is directly connected to the logarithmic interconnect. The number of memory ports is equal to the number of banks to have concurrent access to different memory locations. Once a read or write request is brought to the memory interface, the data is available on the negative edge of the same clock cycle, leading to two clock cycles latency for conflict-free TCDM access. As already

mentioned above, if conflicts occur there is no extra latency between pending requests, once a given bank is active, it responds with no wait cycles.

# Synchronization

To coordinate and synchronize cores execution the architecture exploits HW semaphores mapped in a small subset of the TCDM address range. They consist of a series of registers, accessible through the data logarithmic interconnect as a generic slave, associating a single register to a shared data structure in TCDM. By using a mechanism such as a hardware test & set, we are able to coordinate access: if reading returns '0', the resource is free and the semaphore automatically locks it, if it returns a different value, typically '1', access is not granted. This module enables both single and two-phases synchronization barriers, easily written at the software level.

### Instruction Cache Architecture

the L1 Instruction Cache basic block has a core-side interface for instruction fetches and an external memory interface for refill. The inner structure consists of the actual memory and the cache controller logic managing the requests. The module is configurable in its total size, associativity, line size and replacement policy (FIFO, LRU, random). The basic block can be used to build different Instruction Cache architectures:

- Private Instruction Cache: every processing element has its private I-cache, each one with a separate cache line refill path to main memory leading to high contention on external L3 memory.

- Shared Instruction Cache: there is no difference between the private architecture in the data side except for the reduced contention L3 memory (line refill path is unique in this architecture). Shared cache inner structure is made of a configurable number of banks, a centralized logic to manage requests and a slightly modified version of the logarithmic interconnect described above: it connects processors to the shared memory banks operating

line interleaving (1 line consists of 4 words). A round robin scheduling guarantees fair access to the banks. In case of two or more processors requesting the same instruction, they are served in broadcast not affecting hit latency. In case of concurrent instruction miss from two or more banks, a simple bus handles line refills in round robin towards the L3 bus.

# 2.5 Host-Accelerator Interface

In this section we describe the QEMU-based host side of VirtualSoC (VSoC-Host), as well as the many-core accelerator side (VSoC-Acc).

### Parallel Execution

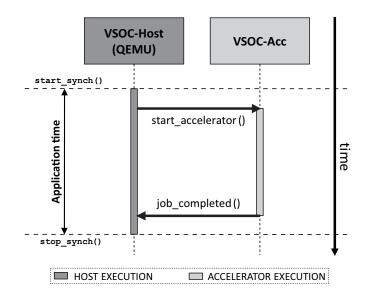

In a real heterogeneous SoC host processor and accelerator can execute in an asynchronous parallel fashion, and exchange data using non-blocking communication primitives. Usually the host processor, while running an application, offloads asynchronously a parallel job to the accelerator and goes ahead with its execution (Figure 2.4). Only when needed the host processor synchronizes with the execution of the accelerator, to check the results of the computation.

In our virtual platform the host processor system and the accelerator can run in parallel, with VSoC-Host and VSoC-Acc running on different threads: when the thread of VSoC-Acc starts its execution triggers the SystemC simulation. It is important to highlight that the VSoC-Acc SystemC simulation starts immediately during VSoC-Host startup, and the accelerator starts executing the binary of a firmware (until the shutdown) in which all cores are waiting for a job to execute.

### Time Synchronization Mechanism

VSoC-Host and VSoC-Acc run independently in parallel with a different notion of time. The lack of a common time measure leads to only functional simulation, without the possibility of profiling applications performance even in a qualitative way. Application developers often need to understand how much time, over

Figure 2.4: Execution model

the total application time, is spent on the host processor or on the accelerator. Also, without a global simulation time it is not possible to appreciate execution time speedups due to the exploitation of the many-core accelerator. To manage the time synchronization between the two environments, it is necessary that both VSoC-Host and VSoC-Acc have a time measurement system. VSoC-Host does not natively provide this kind of mechanisms, so we instrumented it to implement a clock cycle count, based on instructions executed and memory accesses performed. On the contrary for VSoC-Acc there is no need for modifications because it is possible to exploit the SystemC time. The synchronization mechanism used in our platform is based on a threshold protocol acting on simulated time: at fixed synchronization points the simulated time of VSoC-Host and VSoC-Acc is compared. If the difference is greater than the threshold, the entity with the greater simulated time is stopped until the gap is filled.

At fixed synchronization points, cycles count from VSoC-Host  $(C_H)$  and VSoC-Acc  $(C_A)$  are multiplied by the respective clock period  $(P_H \text{ and } P_A)$  and compared. Given a time threshold h if  $|C_A*P_A-C_A*P_A|>h$ , one of the two systems is forward in the future in respect to the other and its execution is stopped until  $|C_H*p_H-C_A*P_A|>0$ . The Global simulation time is always the greater

of the two. It is intuitive to note that the proposed mechanism slows down the simulation speed, due to synchronization points and depending on the difference of simulation speed between the two ecosystems. To avoid unnecessary slowdown, we provide an interface to activate and de-activate the time synchronization when it is not needed (e.g. functional simulation).

# 2.6 Simulation Software Support

In this section we provide a description of the software stack provided with the simulator to allow the programmer to fully exploit the accelerator from within the host Linux system, and to write parallel code to be accelerated.

### Linux Driver

In order to build a full system simulation environment we mapped VSoC-Acc as a device in the device file system of the guest Linux environment running on top of VSoC-Host. A device node /dev/vsoc has been created, and as all Linux devices it is interfaced to the operating system using a Linux driver. The driver is in charge of mapping the shared memory region into the kernel I/O space. This region is not managed under virtual memory because the accelerator can deal only with physical addresses, as a consequence all buffers must be allocated contiguously (done by the Linux driver). The driver provides all basic functions to interact with the device.

### Host Side User-Space Library

To simplify the job of the programmer we have designed a user level library, which provides a set of APIs that rely on the Linux driver functions. Through this library the programmer is able to fully control the accelerator from the host Linux system. It is possible for example to offload a binary, or to check the status of the current executing job (e.g. checking if it has finished).

### Accelerator Side Software Support

The basic manner we provide to write applications for the accelerator is to directly call from the program a set of low-level functions implemented as a user library, called appsupport. appsupport provides basic services for memory management, core ID resolution, synchronization. To further simplify programming and raise the level of abstraction we also support a fully-compliant OpenMP v3.0 programming model, with associated compiler and runtime library.

# 2.7 Evaluation

In this section two use cases of the simulation platform are presented. We will show how the proposed virtual platform can be exploited for both software verification or design space exploration.

# 2.7.1 Experimental Setup

Table 2.1 summarizes the experimental setup of the virtual platform used for all benchmarks discussed. We chose as ARM core clock frequency of 1GHz, even if the ARM modeled by QEMU works at up to 500MHz, to resemble a state of the art ARM processor performance. The frequency would only affect results in terms of global values, all considerations done in this section remain valid even if the ARM core clock frequency is changed.

# 2.7.2 VirtualSoC Use Cases

# Full System Simulation

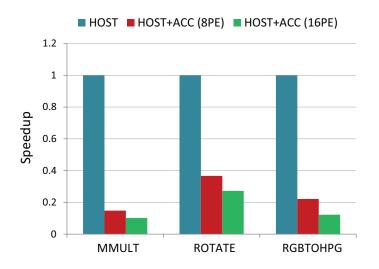

As first use case of the simulator we propose the profiling of an application involving both the ARM host and the many-core accelerator. In this example we want to measure the speedup achievable when accelerating a set of algorithms onto the many-core accelerator. The algorithms chosen are: *Matrix Multiplication*, *RG-BtoHPG* color conversion, and *Image Rotation* algorithm. All the benchmarks

follow a common scheme: the computation starts from the ARM host which in turn will offload a parallel task, one of the algorithms, to the accelerator. Then we compare simulated time obtained varying the number of cores present in the accelerator, with the time taken to run each benchmark on the ARM processor only (i.e. no acceleration).

Figure 2.5 shows the results of this experiment. Using the accelerator with 8 cores we can see a speedup of  $\approx 3 \times$  times for the matrix multiplication,  $\approx 3 \times$  for the rotate benchmark and  $\approx 5 \times$  for the RGBtoHPG benchmark. When running with 16 cores we can appreciate an almost double execution speedup for all the proposed benchmarks.

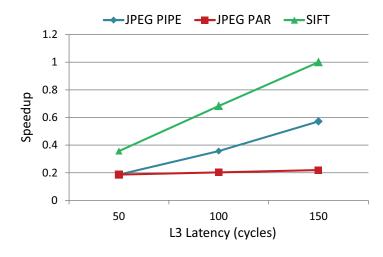

### Standlone Accelerator Simulation

In this section we show an example of stand-alone accelerator analysis by using two real applications, namely a JPEG decoder and a Scale Invariant Feature Transform (SIFT), a widely adopted algorithm in the domain of image recognition. Our analysis will as first evaluate the effects of L3 latency over the execution

Table 2.1: Experimental Setup

|                          | 1                             |  |  |  |

|--------------------------|-------------------------------|--|--|--|

| PARAMETER                | VALUE                         |  |  |  |

| PLATFORM                 |                               |  |  |  |

| L3 latency               | 200 ns                        |  |  |  |

| L3 size                  | 256 MB                        |  |  |  |

| ACCELERATOR              |                               |  |  |  |

| PE                       | 16                            |  |  |  |

| frequency                | $250~\mathrm{MHz}$            |  |  |  |

| L1 $I$ \$ size           | 16 KB                         |  |  |  |

| $t_{hit}$                | = 1 cycle                     |  |  |  |

| $t_{miss}$               | $\geq 50 \text{ cycles}$      |  |  |  |

| TCDM banks               | 16                            |  |  |  |

| TCDM size                | $256~\mathrm{KB}$             |  |  |  |

| HOST                     |                               |  |  |  |

| ARM Core clock frequency | 1GHz                          |  |  |  |

| Guest OS                 | Debian for ARM (Linux 2.6.32) |  |  |  |

time of each benchmark. In a second experiment we evaluate the instruction cache usage made by each application in terms of hit rate and average hit time. Figure 2.6 shows the execution time when varying the L3 latency, and as expected the time increases when increasing the external memory access latency.

The instruction cache utilization is shown in Figure 2.7, depending on the application parallelization scheme the hit rate changes as well as the average hit

Figure 2.5: Speedup due to accelerator exploitation

Figure 2.6: Benchmarks execution for varying L3 access latency (shared I-cache architecture)

Figure 2.7: Benchmarks hit rate and average hit cost

time. The JPEG benchmark has been implemented in two different schemes: a data parallel implementation and a pipelined implementation. Results show that the data parallel version is more efficient in terms of cache hit rate and globally in terms of execution time. A deeper analysis will be the object of the research work presented in the next chapter.

# 2.8 Conclusions

VirtualSoC leverages QEMU to model a ARMv6 host processor, capable of running a full-fledged Linux operating system. The many-core accelerator is modeled with higher accuracy using SystemC. We extended this combined simulation technology with a mechanism to allow for gathering timing information that is kept consistent over the two computational sub-blocks. A set of experiments over a number of representative benchmarks demonstrate the functionality, flexibility and efficiency of the proposed approach. Despite its flexibility, VirtualSoC is still based on sequential simulation whose speed decreases when increasing the complexity of the modeled platform. In the next chapter this problem is tackled by exploiting off-the-shelf GPGPUs to speedup the simulation process.

# Chapter 3

# GP-GPU based Acceleration of Virtual Platforms

# 3.1 Overview