## Alma Mater Studiorum - University of Bologna

ARCES - Advanced Research Center on Electronic Systems for Information and Communication Technologies E.De Castro

PhD Course in Information Technology

XXVI CYCLE - Scientific-Disciplinary sector ING-INF /01

# Heterogeneous Multi-core Architectures for High Performance Computing

Candidate:

Matteo Chiesi

Advisors:

Prof. Roberto Guerrieri

Prof. Eleonora Franchi Scarselli

PhD Course Coordinator:

Prof. Claudio Fiegna

Final examination year: 2014

# **Abstract**

This thesis deals with low-cost heterogeneous architectures in standard workstation frameworks.

Heterogeneous computer architectures represent an appealing alternative to traditional supercomputers because they are based on commodity hardware components fabricated in large quantities. Hence their price-performance ratio is unparalleled in the world of high performance computing (HPC).

In particular in this thesis, different aspects related to the performance and power consumption of heterogeneous architectures have been explored. The thesis initially focuses on an efficient implementation of a parallel application, where the execution time is dominated by an high number of floating point instructions. Then the thesis touches the central problem of efficient management of power peaks in heterogeneous computing systems. Finally it discusses a memory-bounded problem, where the execution time is dominated by the memory latency.

Specifically, the following main contributions have been carried out:

- A novel framework for the design and analysis of solar field for Central Receiver Systems (CRS) has been developed. The implementation based on desktop workstation equipped with multiple Graphics Processing Units (GPUs) is motivated by the need to have an accurate and fast simulation environment for studying mirror imperfection and non-planar geometries [1].

- Secondly, a power-aware scheduling algorithm on heterogeneous CPU-GPU architectures, based on an efficient distribution of the computing workload to the resources, has been realized. The scheduler manages the resources of several computing nodes with a view to reduc-

iv Abstract

ing the peak power. The two main contributions of this work follow:

the approach reduces the supply cost due to high peak power whilst having negligible impact on the parallelism of computational nodes.

- from another point of view the developed model allows designer to increase the number of cores without increasing the capacity of the power supply unit [2].

- Finally, an implementation for efficient graph exploration on reconfigurable architectures is presented. The purpose is to accelerate graph exploration, reducing the number of random memory accesses.

# **Contents**

|   | Abs  | tract    |                                                       | iii |

|---|------|----------|-------------------------------------------------------|-----|

|   | Intr | oductio  | on                                                    | 1   |

| 1 | Het  | erogen   | eous Architectures                                    | 4   |

|   | 1.1  | Classi   | fication of Parallel Architectures                    | 6   |

|   | 1.2  | Heter    | ogeneous Parallel Computing                           | 9   |

|   | 1.3  | Graph    | nics Processing Unit (GPU)                            | 13  |

|   |      | 1.3.1    | NVIDIA Fermi Architectural overview                   | 15  |

|   |      | 1.3.2    | NVIDIA GPU Computational Structures                   | 16  |

|   |      | 1.3.3    | NVIDIA GPU Memory Structures                          | 18  |

|   |      | 1.3.4    | Power consumption                                     | 20  |

|   |      | 1.3.5    | Programming the NVIDIA GPU                            | 21  |

|   |      | 1.3.6    | Multiple GPUs                                         | 21  |

|   |      | 1.3.7    | GPU applications                                      | 23  |

|   | 1.4  | Field    | Programmable Gate Array                               | 25  |

|   |      | 1.4.1    | Programming Technologies                              | 26  |

|   |      | 1.4.2    | Configurable Logic Block                              | 26  |

|   |      | 1.4.3    | Routing Architecture                                  | 29  |

|   |      | 1.4.4    | Software Flow                                         | 29  |

|   | 1.5  | FPGA     | s for High Performance Computing: The Maxeler So-     |     |

|   |      | lution   |                                                       | 31  |

|   |      | 1.5.1    | Programming the FPGA using MaxCompiler                | 32  |

| 2 | Opt  | ical Mo  | odel for Design and Analysis of Solar Field on Multi- | ,   |

|   | GPU  | J platfo | orm                                                   | 34  |

|   | 2.1  | Motiv    | ration and background                                 | 34  |

vi CONTENTS

|   | 2.2  | Mathematical model                                         | 36 |

|---|------|------------------------------------------------------------|----|

|   | 2.3  | Computing System                                           | 40 |

|   | 2.4  | Implementation                                             | 41 |

|   |      | 2.4.1 Programming Model                                    | 42 |

|   |      | 2.4.2 GPU kernels                                          | 44 |

|   |      | 2.4.3 Application Flow                                     | 46 |

|   | 2.5  | Validation                                                 | 46 |

|   | 2.6  | Computational benchmarking                                 | 46 |

|   | 2.7  | Application cases                                          | 51 |

|   |      | 2.7.1 Performance field analysis and optimization          | 51 |

|   |      | 2.7.2 Analysis of mirror non-idealities                    | 53 |

|   |      | 2.7.3 Stretched membrane mirrors                           | 53 |

|   | 2.8  | Conclusions                                                | 56 |

| 3 | Pow  | er-Aware Job Scheduling                                    | 57 |

|   | 3.1  | Motivation and background                                  | 57 |

|   | 3.2  | Power Measuring System                                     | 61 |

|   | 3.3  | Power-aware scheduler                                      | 63 |

|   |      | 3.3.1 The scheduling algorithm                             | 64 |

|   | 3.4  | Performance and Evaluation                                 | 67 |

|   |      | 3.4.1 Job Characterization                                 | 67 |

|   |      | 3.4.2 Experimental Setup                                   | 71 |

|   |      | 3.4.3 Analysis of Results                                  | 72 |

|   | 3.5  | Discussion                                                 | 77 |

|   |      | 3.5.1 Application case                                     | 78 |

|   |      | 3.5.2 Limitations of the approach                          | 78 |

|   | 3.6  | Conclusions                                                | 79 |

| 4 | Hete | rogeneous System using a Reconfigurable approach for effi- |    |

|   | cien | t graph exploration                                        | 80 |

|   | 4.1  | Motivation and background                                  | 80 |

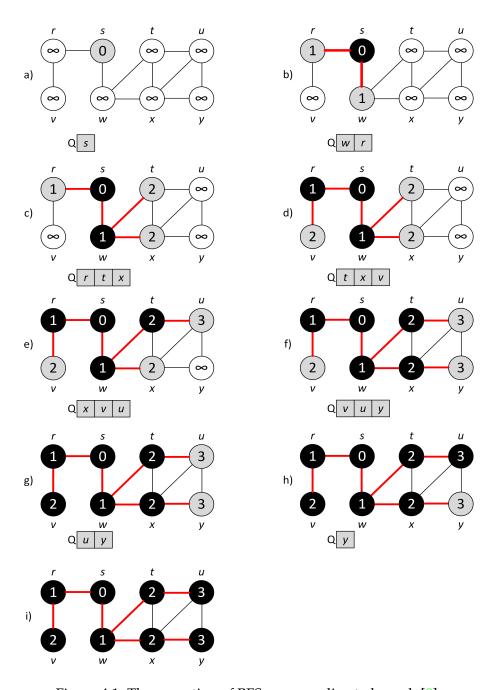

|   | 4.2  | Breadth-first search                                       | 81 |

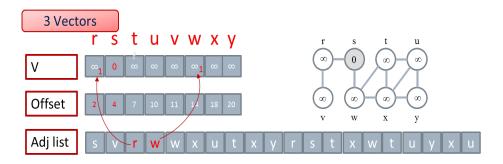

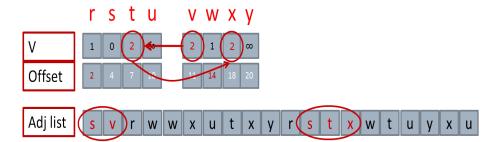

|   | 4.3  | Irregular Graph and Parallel BFS Algorithm                 | 84 |

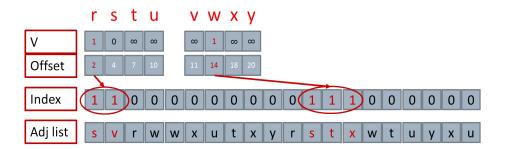

|   | 4.4  | Parallel BFS implementation                                | 88 |

|   | 4.5  | -                                                          | 91 |

|   | 4.6  |                                                            | 95 |

| CONTENTS | vii |

|----------|-----|

|          |     |

| 5  | General Discussion |                                                            |     |

|----|--------------------|------------------------------------------------------------|-----|

|    | 5.1                | Summary of the contributions and results                   | 96  |

|    | 5.2                | Performance and limitations of heterogeneous architectures | 97  |

|    | 5.3                | Applications and Algorithms                                | 98  |

|    | Conclusions        |                                                            |     |

| A  | Acr                | onyms                                                      | 100 |

| Bi | ibliography 10     |                                                            |     |

# **List of Figures**

| 1.1  | Transistor counts for integrated circuits plotted against their |    |

|------|-----------------------------------------------------------------|----|

|      | dates of introduction. (source: Wikipedia).                     | 5  |

| 1.2  | Pollack's Rule [3]                                              | 5  |

| 1.3  | Amdahl's Law. (source: Wikipedia).                              | 6  |

| 1.4  | Flynn's taxonomy                                                | 7  |

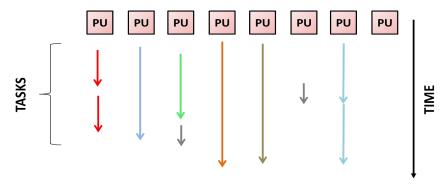

| 1.5  | Multiple tasks executed on MIMD architecture                    | 8  |

| 1.6  | Multiple tasks executed on SIMD architecture                    | 8  |

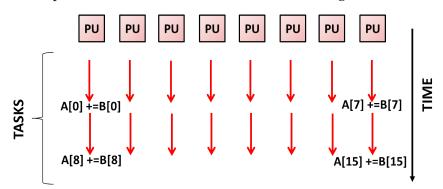

| 1.7  | Memory Architectures                                            | 9  |

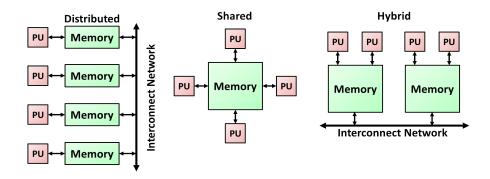

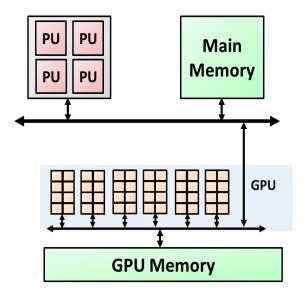

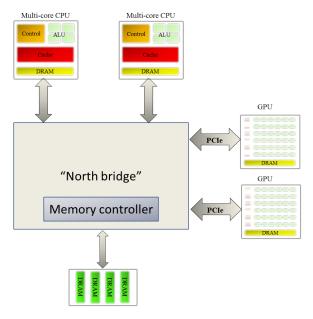

| 1.8  | Block Diagram of a typical heterogeneous architecture           | 10 |

| 1.9  | Heterogeneous architecture coupling CPU and GPU; in yel-        |    |

|      | low are GPU computational cores                                 | 11 |

| 1.10 | Control Flow Architectures (GPU)                                | 12 |

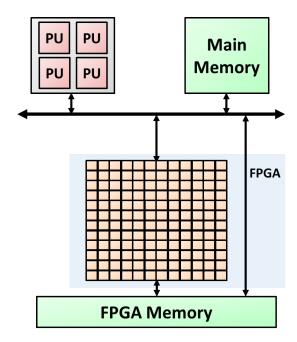

| 1.11 | Heterogeneous architecture coupling CPU and FPGA                | 12 |

| 1.12 | Data Flow Architectures (FPGA)                                  | 13 |

| 1.13 | Floating-point operations per second for the CPU and GPU.       |    |

|      | (source: NVIDIA)                                                | 15 |

| 1.14 | Block diagram of the NVIDIA GeForce 500 series                  | 15 |

| 1.15 | The mapping of a Grid [4]                                       | 17 |

| 1.16 | Block Diagram of Fermi's Dual Warp Thread Scheduler [4]         | 18 |

| 1.17 | GPU Memory structures [4]                                       | 19 |

| 1.18 | NVIDIA GTX590 Graphics card                                     | 20 |

| 1.19 | Heterogeneous programming of a CPU/GPU system                   | 21 |

| 1.20 | GPUs in Multiple Slots [5]                                      | 22 |

| 1.21 | Parallel processing with OpenMP                                 | 22 |

| 1.22 | Software hierarchy and interaction with hardware                | 23 |

| 1.23 | Arithmetic Intensity, specified as the number of floating-point    |    |

|------|--------------------------------------------------------------------|----|

|      | operations to run the program divided by the number of             |    |

|      | Bytes accessed in main memory [4].                                 | 24 |

| 1.24 | Roofline model of several kernels on an NVIDIA C2050 GPU           |    |

|      | [6]                                                                | 24 |

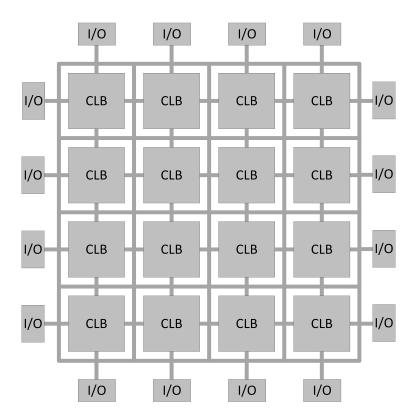

| 1.25 | Overview of FPGA architecture [7]                                  | 26 |

| 1.26 | Basic Logic Element (source: Tree-Based Heterogeneous FPGA         |    |

|      | Architectures.)                                                    | 27 |

| 1.27 | A configurable logic block (CLB) (source: Tree-Based Het-          |    |

|      | erogeneous FPGA Architectures.)                                    | 28 |

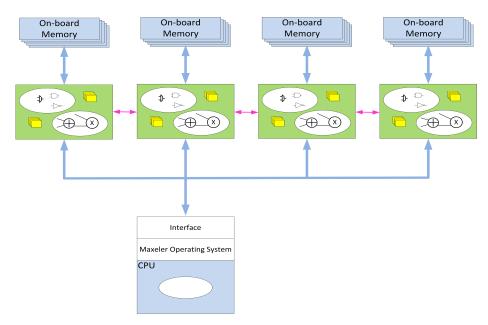

| 1.28 | FPGA-based computing architecture (source: Maxeler.)               | 32 |

| 1.29 | MaxCompiler chain (source: Maxeler.)                               | 33 |

| 1.30 | Maxeler dataflow system architecture (source: Maxeler.)            | 33 |

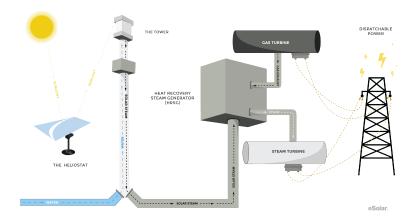

| 2.1  | Block diagram of a Solar tower power plant (source: eSolar).       | 35 |

| 2.2  | Reflection of the sun's rays by a heliostat to a single aim point. | 36 |

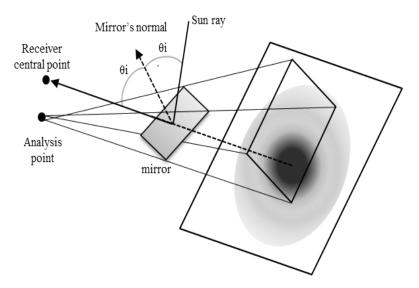

| 2.3  | Geometrical model for optical simulation                           | 38 |

| 2.4  | Simulation model geometry for a single receiver point analysis.    | 39 |

| 2.5  | Geometric model for simulation with non-idealities in mir-         |    |

|      | ror surface                                                        | 40 |

| 2.6  | Flow chart of the algorithm                                        | 41 |

| 2.7  | Shadowing evaluation                                               | 43 |

| 2.8  | Comparison of GPU parallel model in a case of planar and           |    |

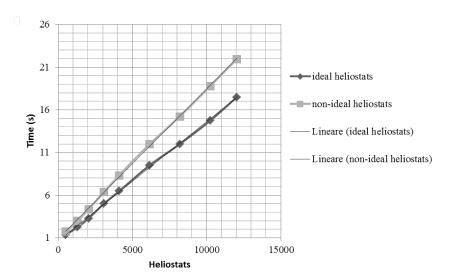

|      | non-planar geometry                                                | 49 |

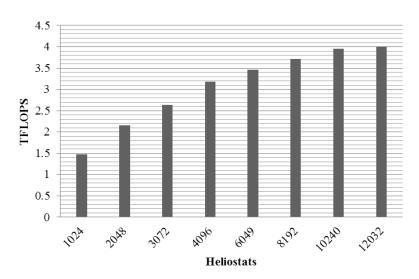

| 2.9  | Comparison of throughput of our application in TFLOPS              | 50 |

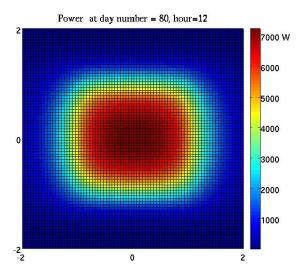

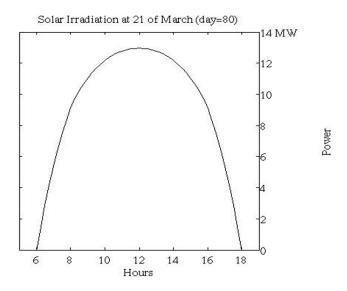

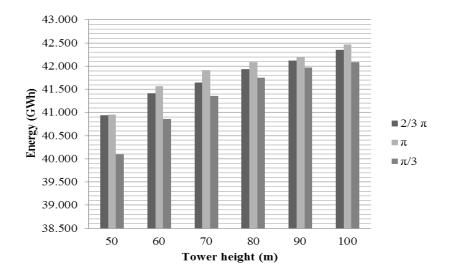

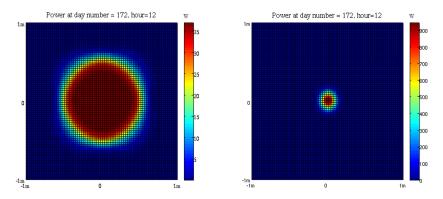

| 2.10 | Power on the receiver surface at noon of 21st March                | 52 |

| 2.11 | Solar irradiance collected by the receiver on March 21st           | 52 |

| 2.12 | Annual field performance                                           | 53 |

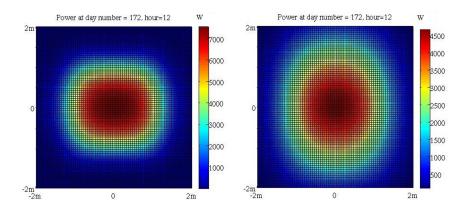

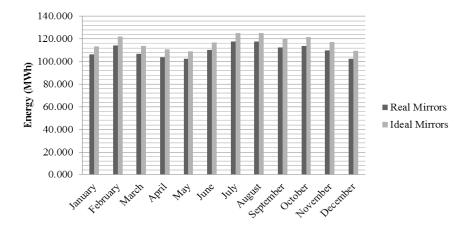

| 2.13 | Power on the receiver surface for ideal (left) mirrors and         |    |

|      | non-ideal (right) mirrors                                          | 54 |

| 2.14 | Comparison of energy collected by the field on a typical day,      |    |

|      | using ideal and real mirrors                                       | 54 |

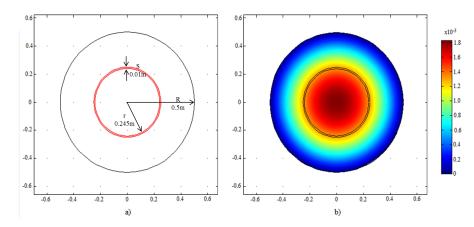

| 2.15 | Simulated bending of a mirror realized with aluminum stretched     | 1  |

|      | membrane                                                           | 55 |

| 2.16 | Receiver spot using flat and stretched membrane mirrors            | 56 |

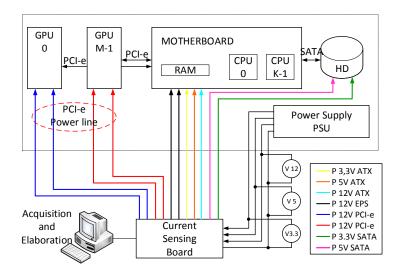

| 3.1 | Measuring setup for the generic computing node                  | 62 |

|-----|-----------------------------------------------------------------|----|

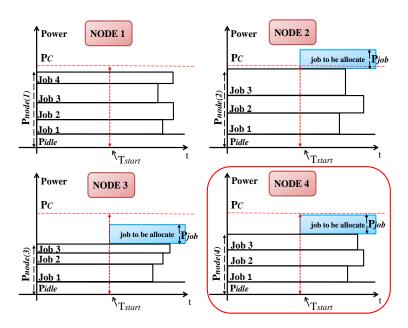

| 3.2 | Example of scheduling: 4 nodes, each one composed of 4 cores    | 67 |

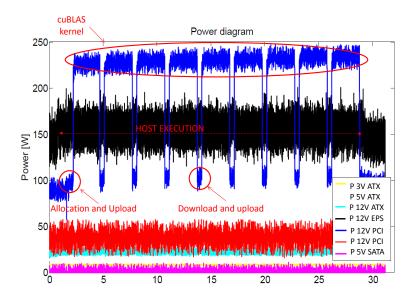

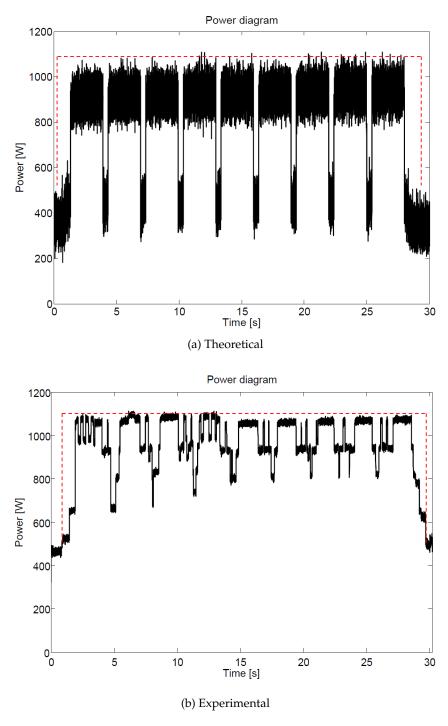

| 3.3 | Power profile measured during a matrix multiplication on        |    |

|     | GPU                                                             | 68 |

| 3.4 | Comparison between theoretical and experimental evalua-         |    |

|     | tion of total power absorption during 4 concurrent matrix       |    |

|     | multiplications                                                 | 70 |

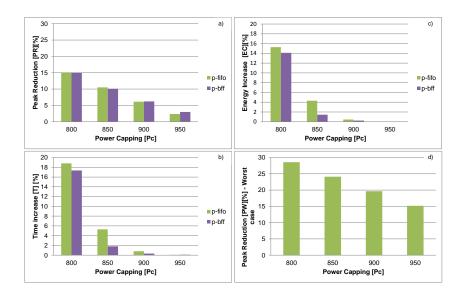

| 3.5 | Average performance obtained using the power-aware schedul-     |    |

|     | ing algorithm. In a) one sees the average peak reduction ob-    |    |

|     | tained by the algorithm, while b) shows the increase in time.   |    |

|     | Fig. c) shows the increase in energy consumption and Fig.       |    |

|     | d) the power reduction with respect to the worst case scenario. | 74 |

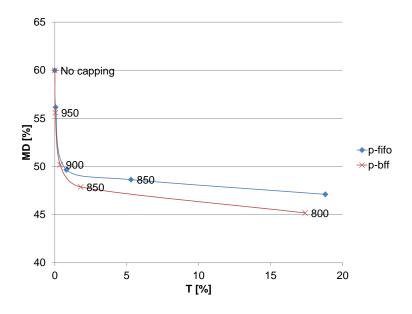

| 3.6 | Power-Performance comparison                                    | 75 |

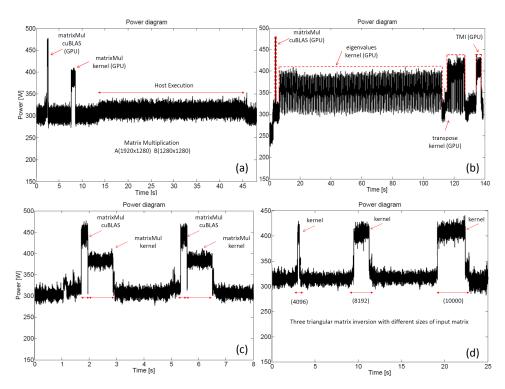

| 3.7 | a) Comparison between GPU and CPU execution of matrix           |    |

|     | multiplication, b) Four different GPU kernels, c) Triangular    |    |

|     | matrix inversion with different sizes of matrix, d) Analysis    |    |

|     | of power requirements of different jobs                         | 76 |

| 4.1 | The operation of BFS on an undirected graph [8]                 | 82 |

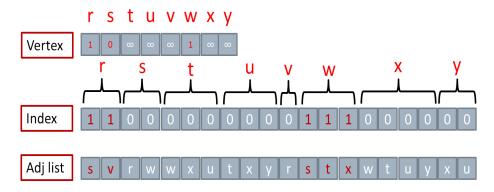

| 4.2 | Compressed sparse row format                                    | 84 |

| 4.3 | Data access pattern                                             | 88 |

| 4.4 | Additional Index Vector                                         | 89 |

| 4.5 | Relationship between Index and Vertex vectors                   | 90 |

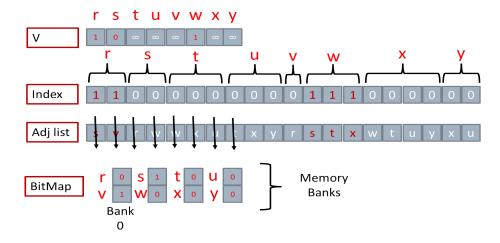

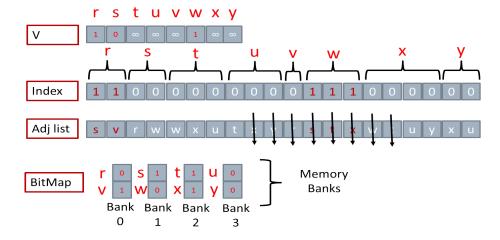

| 4.6 | Bitmap update: first step in parallel                           | 91 |

| 4.7 | Bitmap update: second step in parallel                          | 91 |

# **List of Tables**

| 2.1 | Nomenclature table of the algorithm                             | 42 |

|-----|-----------------------------------------------------------------|----|

| 2.2 | Comparison between the GPU model and PS10 published             |    |

|     | data                                                            | 47 |

| 2.3 | Setup parameters of the simulation                              | 47 |

| 2.4 | Error in the flux collected on the receiver aperture as a func- |    |

|     | tion of $m$                                                     | 48 |

| 2.5 | Comparison between CPU and GPU execution times                  | 49 |

| 2.6 | Parameter space used in the optimization                        | 51 |

| 2.7 | Material properties                                             | 55 |

| 3.1 | Nomenclature table of the algorithm                             | 64 |

| 3.2 | Power consumption of GPU jobs                                   | 69 |

| 3.3 | Power-Performance Comparison                                    | 75 |

| 4.1 | Number of vertices in each BFS level: result from typical ex-   |    |

|     | ecution in an RMAT graph [9]                                    | 86 |

| 4.2 | Parameters table                                                | 94 |

# Introduction

Heterogeneous multi-core architectures represent the future of high performance computing (HPC). Traditionally, to increase the performance of Supercomputers, designers just scale up the number of CPUs (Central Processing Unit). This because CPUs are general purpose and easy to program. However a large portion of the CPU area is exploited to realize a powerful control unit. This control capability is usually wasted on many computeintensive problems. Since a lot of scientific, engineering and financial applications require that a single instruction is executed on multiple data, heterogeneous architectures are potentially more efficient than homogeneous architectures that require to fetch and decode one instruction for each data. This has led to equip large scale computing systems with heterogeneous accelerators based on commodity hardware components to speed-up dataintensive workloads [10]. For example, the new supercomputer Titan, developed by ORNL [11], uses an heterogeneous architecture composed of conventional 16-core CPUs and GPU accelerators to overcome the computational power achieved by the previous generation of supercomputers, leading to the development of powerful heterogeneous High Performance Computing systems.

Nevertheless, different applications have different needs towards the computing systems. Designing an architecture to address a particular computational problem leads to excellent result, but it would be difficult to design an architecture to address different types of problems and so far no "one size fits all" architecture has been designed [12]. For instance, some architectures offer several simple computational cores vs. fewer complex processors, some depend on multi-threading and some even replace caches with explicitly addressed local stores [4].

This thesis explores the capabilities and the limitations of heterogeneous ar-

2 Introduction

chitectures based on GPUs and FPGAs (Field Programmable Gate Array), to address some real-world "computationally hungry" problems. As target applications this work focuses on data-intensive computational problems. Initially the thesis focuses on the acceleration of complex 3 dimensional optical problems. These problems are based on intensive floating-point operations which can be efficiently implemented on a multi-GPU platform, since GPUs have evolved in highly parallel floating-point processors. In particular the purpose of this work is to speed up the computation in the design and analysis of concentrating tower power plants which represent one of the best ways to harness solar energy on a large scale. The design and optimization of these systems is quite complex and time-consuming, because it requires several design parameters to be considered at different time steps. The contribution of this work is a new simulation environment based on heterogeneous multi-GPU systems. The framework supports tuning of the trade-off between accuracy and computational time to obtain an analysis consistent with the precision required. The parallelism level in multi PCI-express workstations is usually limited by the power consumption. These systems could theoretically host from 2 up to 4 PCI-express devices (e.g. GPUs) for each CPU. However, to equip these systems with a number of GPUs equal to the number of PCI-express slots, could lead to system failure caused by power capacity overload. In particular, the multi-GPU workstation used could theoretically host 4 GPU cards, since 4 PCI-express slots are available. However the system is equipped with 3 GPU cards because with the fourth GPU the specification on the maximum power consumption provided by the power supply unit will be exceeded. Therefore the analysis has been moved to techniques to increase the parallelism on multi-GPU platforms limiting the maximum power consumption of the system. In this scenario, the attention has been focused on a job-level scheduling algorithm that aims to reduce the worst case power condition below a predetermined budget. The main idea is a redistribution of the workload between nodes of the system in order to avoid concurrent execution of the most power-consuming jobs on the same node. The approach used in this work aims to limit the total power consumption of the system under a prefixed budget and allows designers to increase the number of cores without increasing the capacity of the power supply unit.

Introduction 3

Finally the thesis discusses a reconfigurable approach for efficient graph exploration. Differently from the previously studied class of problems, characterized by an high ratio between arithmetic operations and memory accesses, this kind of problems (i.e. breath-first search (BFS)) is largely dominated by memory latency, therefore not suitable for GPU architecture. The methodology adopted in this work is based on a partitioning of the algorithm in different levels. This in order to exploit the fast on-chip memory available in FPGAs and avoid multiple and inefficient random memory accesses.

The rest of this work is organized as follows. Chapter 1 discusses the two heterogeneous architectures based on GPU and FPGA used during this research activity. The goal of this chapter is to explain the concept of heterogeneous systems, comprising systems set-up, architectures and programming models. Chapter 2 provides a brief outline of solar fields explored in this work, pointing out the parallelism of the computational problem, where the previously described architectures based on GPU promise significant improvements. The chapter also describes in details how the simulation environment has been implemented on a multi-GPU platform and the results obtained. Chapter 3 focuses on the GPU power consumption and the techniques used in literature to limit the total power consumption of the system under a prefixed budget. Then the approach proposed to reduce the peak power and to increase the parallelism without increasing the capacity of the power supply unit is illustrated. Chapter 4 discusses a new techniques for efficient graph exploration. This section describes in details how the algorithm could be implemented on reconfigurable architectures and the limitations of this approach. Section 5 contains a general discussion and some conclusions are drawn in Section 6.

# Chapter 1

# Heterogeneous Architectures

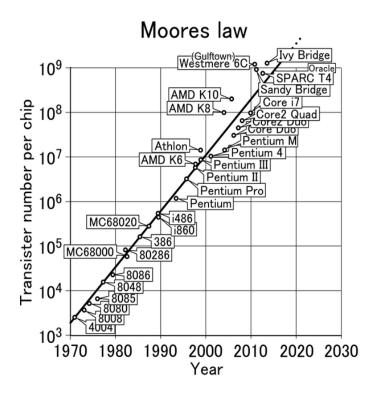

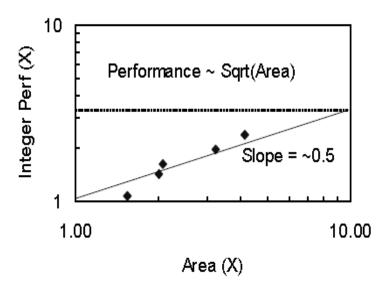

Microprocessors are the basic blocks of the information technology. Their performance has made incredible progress over the last 20 years, driven by transistor speed and energy scaling, as well as by the progress in system integration density. Transistor density increases by about 35% per year. Increases in the die size are less predictable and slower, ranging from 10% to 20% per year. The combination of these two effects leads to a growth rate in transistor count on a chip of about 40% to 55% per year. This trend is known as Moore's law [13] and it is shown in figure 1.1. While transistor density increases with the Moore's law, device speed scales more slowly and is governed by Pollack's Rule, which states that performance increases as the square root of increase in complexity [14]. Figure 1.2 shows integer performance increase of new micro-architectures against area increase from the previous generation micro-architecture, in the same process technology. In particular the figure highlights that if designer doubles the logic in a processor core, then it delivers only 40% more performance. In addition, a further increase of frequency could lead to power dissipation issues. Better results can be obtained with a multi-core micro-architecture. Two smaller processor cores can provide 70-80% more performance, as compared to 40% from a large monolithic core [3].

Therefore chip manufacturers start to build multi-core microprocessors. Each core delivers lower performance than a large complex core; however the total compute throughput of the system is much higher. Nowadays general purpose processors integrate 2 to 16 cores [15], and it is expected that in the future a single multi-core processor will host up to hundreds or

Figure 1.1: Transistor counts for integrated circuits plotted against their dates of introduction. (source: Wikipedia).

Figure 1.2: Pollack's Rule [3].

thousands of cores [16].

### 1.1 Classification of Parallel Architectures

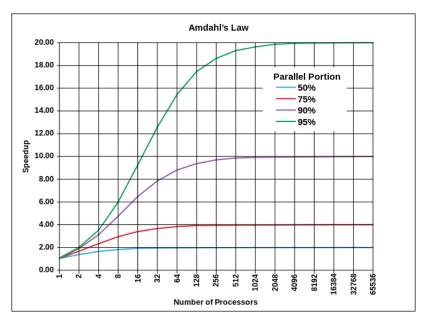

Many scientific applications present a lot of concurrency, since the real world itself is massively parallel. Although multi-core systems deliver higher compute throughput than monolithic core systems, it may be difficult to harvest the performance. The performance gain that can be obtained by improving some portions of an application is limited by the Amdahl's law [17]. It states that the parallel speed up is inherently limited by the serial code in a program according to the equation 1.1:

$$SpeedUp_{overall} = \frac{1}{(1-P) + \frac{P}{N}}$$

(1.1)

where P represents the fraction of parallel code and N the number of computational cores. The speed-up scales with the number of cores as shown in figure 1.3. If the serial part of an application is large (i.e. 50%) the parallel speed-up saturates with a small number of cores (i.e. 16 cores).

Figure 1.3: Amdahl's Law. (source: Wikipedia).

Few applications offer performance which scales with the number of processors. This usually happens when there are no data dependency between different streams. However most applications require communication between the computational cores. In this scenario data traffic and synchronization between nodes can be expensive. In general different computer

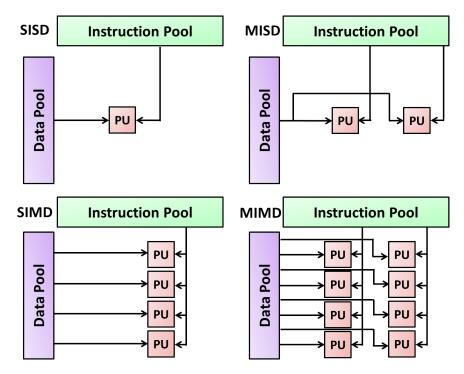

architectures can provide different performance according to the class of problems that programmers need to study. Homogeneous computer architectures are usually classified according to their processing units (PU) or their memory architectures. Concerning their processing units, the most common classification is the Flynn's Taxonomy [18]. This classification is based upon the number of concurrent instructions and data streams available in the architecture:

- Single Instruction Single Data (SISD)

- Multiple Instruction Single Data (MISD)

- Single Instruction Multiple Data (SIMD)

- Multiple Instruction Multiple Data (MIMD)

Figure 1.4 shows the general principles of these architectures.

Figure 1.4: Flynn's taxonomy.

SISD represents a sequential computer which exploits no parallelism in either the instruction or data stream. A single control unit fetches single instruction stream from memory. MISD is a parallel computing architecture where many functional units perform different operations on

the same data. MISD is an uncommon architecture which is generally used for fault tolerance, and not many instances of this architecture exist. The classes of interest in computing are SIMD and MIMD. Multi-core general purpose processors for example are MIMD architectures. Multiple autonomous cores simultaneously execute different instructions on different data. They are suitable to perform parallel tasks as shown in figure 1.5 (each core independently and concurrently processes a serial task).

Figure 1.5: Multiple tasks executed on MIMD architecture.

Task-parallel processing is very useful to control different independent parts of a system. However a wide set of applications has significant data-level parallelism (e.g. matrix-oriented applications, media-oriented images, graphics processing and linear algebra). In this case an application can be decomposed into a large number of concurrent instruction streams which perform the basic operation on different data sets as shown in figure 1.6.

Figure 1.6: Multiple tasks executed on SIMD architecture.

Moreover, since a single instruction can lunch many data operations, SIMD is potentially more energy efficient than MIMD which needs to fetch and execute one instruction per data operation. In the past, this has led to

develop vector architectures which essentially are pipelined execution of many data operations [19] and later to SIMD instruction set extension for CPUs [20].

Computer architectures can also be classified according to their memory organization. Memory architectures can be distributed, shared and hybrid as shown in figure 1.7.

Figure 1.7: Memory Architectures.

Distributed memory provides a portion of private local memory to each core. Hence this kind of architecture ensures fast local memory accesses and is suitable for applications which present independent streams of data. However, communication between processors occurs through an interconnect network, which can become quickly the bottleneck for most applications. Moreover, when multiple cores are working on the same set of data, each of them has to do its own copy, increasing memory consumption and traffic. On the contrary in the shared memory model, the communication between computational cores is the fastest and multiple cores can share the same set of data. However this model does not scale well with the number of cores since data traffic and competition for resources can scale up geometrically with this number. The result is that most architectures adopt a hybrid mix of shared and distributed memory [21].

# 1.2 Heterogeneous Parallel Computing

Since different applications have different needs towards the computing systems, no universal multi-core accelerators have been designed so far. Usually CPUs are considered the closest architectures to universal multi-

core solutions because they present an high versatility. However in a CPU, a large portion of the overall area is used for control unit and cache, leaving a restricted area to computational unit.

In the past supercomputers were built just scaling up the number of CPUs and clustering them together using an high bandwidth interconnect. Recently power consumption has become the most critical issue. Supercomputers can reach up to tens of MW and in 2012 the supply cost over their useful life exceeded the initial capital investment [22]. For that reason heterogeneous architectures with combined traditional general purpose multicore processors and accelerators with a view to reducing the power consumption have become an appealing alternative.

Heterogeneous Architectures are designed to maximize throughput for specific application fields. In heterogeneous architecture a large part of the control logic is cut down. This means that they need an host processor which provides input data and then collects the results from the accelerators output.

The most common approach is therefore to combine few general purpose processors with a uniform and large array of accelerators [23]. The block diagram of a typical heterogeneous system is depicted in figure 1.8.

Figure 1.8: Block Diagram of a typical heterogeneous architecture

The most common general purpose accelerators are graphics processing

unit (GPU) and field programmable gate array (FPGA).

GPUs are massively parallel coprocessors for floating-point operations. They are usually integrated on a board with their own memory. The board communicates with the host system through PCI-express bus. Currently there are two manufacturers of GPUs: AMD [24] and NVIDIA [25]. In this work only NVIDIA GPUs have been used. The architecture of a GPU cluster is reported in figure 1.9.

Figure 1.9: Heterogeneous architecture coupling CPU and GPU; in yellow are GPU computational cores

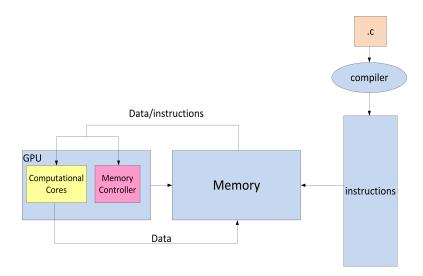

In a GPU application, a source code is transformed into a list of instructions for the computational cores, which is then loaded into the memory as shown in figure 1.10. Processors contain caches, forwarding and prediction logic to improve the efficiency of this paradigm. Performance of these architectures (i.e. called control-flow architectures) depends on the latency of the memory access and the clock speed.

Also FPGAs have a significant mark share in high performance computing. FPGAs can be reconfigured many times to address different problems. This characteristic makes them the most versatile accelerators. However they are hard to program, which is usually done using hardware description languages (HDLs). Rarely FPGAs are used as massively parallel floating-point units, but excellent results using these devices have been reported for pattern matching [26], encryption [27], and signal processing applications

Figure 1.10: Control Flow Architectures (GPU)

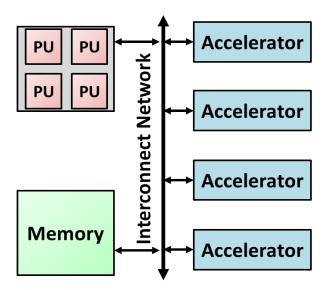

[28]. A system using an FPGA as accelerator is depicted in figure 1.11.

Figure 1.11: Heterogeneous architecture coupling CPU and FPGA

In an FPGA, data streams from memory into the chip where data is forwarded directly from an arithmetic unit to another until the chain is complete as shown in figure 1.12 according to a data-flow paradigm. Once a program has been executed the FPGA can be reconfigured for a new application. Performance of this architecture depends on how the arithmetic

Data FPGA , Arithmetic Arithmetic .vhdl Unit Unit Synthesis tool Arithmetic Arithmetic Arithmetic Unit Unit Unit Memory Arithmetic Arithmetic Arithmetic Unit Unit Unit Arithmetic Arithmetic Unit Unit

units are connected together.

Figure 1.12: Data Flow Architectures (FPGA)

The next sections explain more in details how GPUs and FPGAs work in heterogeneous systems. Performance of GPUs and FPGAs are related to the algorithm characteristics. An FPGA is in general superior over a GPU for algorithms requiring large number of regular memory accesses, while a GPU is superior for algorithms with variable data reuse [29].

# 1.3 Graphics Processing Unit (GPU)

Everybody with few hundreds of euros can buy a GPU which transforms a standard machine desktop in a powerful heterogeneous computing system. GPUs were initially designed as hardware accelerators for 3D applications. These applications involve intensive low precision floating-point operations with a very modest need for control flow and data caching. The market of GPUs has exponentially grown up, when their potential have been combined with a programming language that made GPUs easier to program. AMD and NVIDIA developed their application programming interfaces (API): "Close to Metal" now called "Accelerated Parallel Processing" (APP) [30] and Compute Unified Device Architecture (CUDA) [31]. They also provided new hardware features to make GPUs more appealing for general purpose computing. To date, these include:

• IEEE-compliant Fast Double-Precision Floating-Point Arithmetic – The lat-

est GPUs match the relative double-precision speed of conventional processors at roughly half the speed of single precision.

- Caches for GPU memory While the GPU philosophy is to have enough thread to hide the DRAM latency, there are variables that are needed across threads, such as local variables. New GPU architectures include both an L1 data cache and L1 instruction cache for each multiprocessor. In addition an L2 cache shared by all multi-processors is available.

- 64-Bit Addressing and Unified Address Space for All GPU Memories This

innovation makes it much easier to provide the pointers needed for

C and C++.

- Error correction codes to detect and correct errors in memory and registers.

- Faster Context Switching The new architectures have hardware support to switch contexts much more quickly.

- Faster Atomic Instruction New architectures improve performance of Atomic instructions. Hardware interrupts and other processors cannot read or store the same location concurrently.

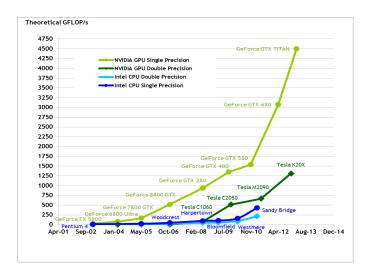

Driven by this scenario, GPUs have evolved in highly parallel, multi-thread, many-core processors with an high computational power as shown in figure 1.13.

Throughput is measured in GFLOP/s that means billion of Floating-point operations per second. Values reported in the plot indicates the maximum theoretical throughput of the device, assuming that all computational units are continuously busy with multiply-add operations. Thanks to these features, GPUs are nowadays computational accelerators not only used for graphics, with capabilities far exceeding their original purpose. As an example the NVIDIA Tesla series of graphics cards does not even have a graphics output [32].

The following section covers different aspect related to GPUs, with particular emphasis to the devices used for the experimental researches described in chapters 2 and 3

Figure 1.13: Floating-point operations per second for the CPU and GPU. (source: NVIDIA).

#### 1.3.1 NVIDIA Fermi Architectural overview

GPUs work well only to address data-level parallel problems, since they are SIMD architectures. This means that instructions must be executed on many data elements in parallel. The reason behind this is that more transistors are devoted to data processing rather than data caching and flow control. Figure 1.14 shows the architecture of NVIDIA GeForce 500 series (codename: *Fermi*) used in the designs described in chapter 2 and 3.

Figure 1.14: Block diagram of the NVIDIA GeForce 500 series.

It is composed of 512 cores, organized in 16 Streaming Multi-Processors

(SM) composed of 32 cores (SP), able to perform a total of 512 single precision or 256 double precision instructions per GPU clock. In addition each SM has four special function units (SFU) which perform transcendental instructions such as sine, cosine, square root, etc. To increase hardware performance with respect to the previous generation of GPUs, each SM has two thread schedulers and two instruction dispatch units.

This GPU has 3 different levels of memory, with different access times. For each SM there is an L1 cache of 64 KB that allows programmer fast data access. This memory can be divided into 2 sub-blocks, one of 16 KB and one of 48 KB, and is used as the shared memory of SM or local cache L1. The second level memory is a 768 KB L2 cache memory. Both L1 and L2 caches are used to cache accesses to local or global memory, including temporary register spills. Finally, the last level is called the device (or global) memory and is a 1536 MB off-chip memory, connected via a high-bandwidth interface. This memory has higher latency than the other two. The GPU cannot reach memory levels further down this memory hierarchy. Hence data must be uploaded to and downloaded from the GPU device memory via the PCI-express port. All control is exerted by the CPU side since the GPU cannot initialize any kernel launch or data transfer on its own. Care in using the on-chip memory is very important because it allows one to limit access to the off-chip device memory, since it is usually the bottleneck of GPU computation performance (see also section 1.3.3).

#### 1.3.2 NVIDIA GPU Computational Structures

The CUDA programming model envisions hierarchical space decomposition to describe natural application parallelism. The basic element of the CUDA computation is the thread. It represents the smallest sequence of instructions that can be managed independently by the scheduler. A CUDA code (usually called kernel) is organized as a *Grid* of *Thread Blocks*, each one executing a certain number of parallel data threads.

As an example, suppose a programmer has to multiply two vectors, each 16384 elements long. The GPU kernel that works on all 16384 elements is called *grid*. The grid is organized in more manageable size, the *thread blocks*, each with up to 512 elements. With 16384 elements in the vectors, this example thus has 32 thread blocks since  $16384 \div 512 = 32$ . An overview of

A[0] = B[0] \* C[0]Warp 0 A[31] = B[31]\*C[31]**Thread Block** 0  $\overline{A[480]} = B[480] * C[480]$ Warp **15** A[511] = B[511]\*C[511]A[512] = B[512]\*C[512]Grid A[15871] = B[15871]\*C[15871]A[15872] = B[15872] \* C[15872]Warp 0 A[15903] = B[15903]\*C[15903] **Thread Block** 31 A[16352] = B[16352] \* C[16352]Warp **15** A[16383] = B[16383] \* C[16383]

the mapping is reported in figure 1.15.

Figure 1.15: The mapping of a Grid [4].

These abstractions help programmer to organize the code. Thus a kernel performs multiple thread blocks, so that the total number of threads (i.e. 16384) is equal to the number of threads per block (i.e. 512) times the number of blocks (i.e. 32). Each SM processes the threads inside these blocks as an isolated problem, no synchronized communication between these blocks being provided. In this example, it would send 32 thread blocks to SMs to compute all 16384 elements.

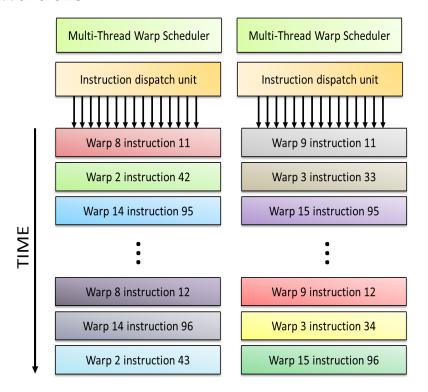

GPUs have 2 levels of hardware schedulers; the thread block scheduler assigns thread blocks to SMs and ensures that thread blocks are assigned to the SMs whose local memories have the corresponding data. The second scheduler is within each SM which schedules when threads of instructions should run. In order to optimize the computation, the CUDA environment introduces *warp* meaning a group of 32 parallel threads which are simultaneously assigned to a SM. By contrast, thread blocks are assigned to different SMs. Hence, a thread block is a stream of vector instructions, and scalar

threads are the vector elements. In order to massively exploit GPU capabilities, the number of threads within a thread block should be composed of an integer number of warps. Each warp consists of 32 thread. In the Fermi architecture (see also figure 1.14) the number of cores is 32 so each warp takes one clock cycle to complete. In the previous example, *thread blocks* would contain  $512 \div 32 = 16$  warps (see also figure 1.15). Since by definition warps are independent, the thread scheduler can pick whatever warp is ready. Figure 1.16 shows the Scheduler picking warps in a different order over the time. The assumption is that GPU applications have so many warps that multi-threading can both hide the latency and increase utilization of SMs.

Figure 1.16: Block Diagram of Fermi's Dual Warp Thread Scheduler [4].

#### 1.3.3 NVIDIA GPU Memory Structures

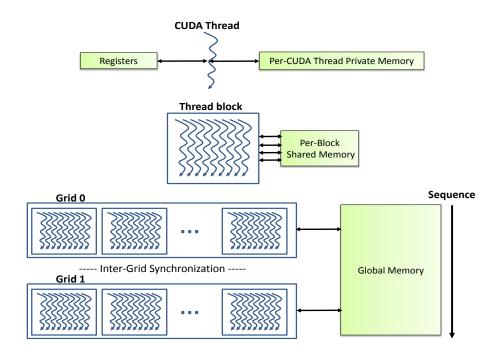

Figure 1.17 shows the GPU memory organization.

Understanding the memory architecture is essential because all GPU applications are inherently bandwidth limited. Since most of the area is devoted to arithmetic units, the amount of on-chip memory is limited. As shown in

Figure 1.17: GPU Memory structures [4].

figure 1.17, three layers of memory are available:

- private memory;

- shared memory;

- global memory.

Each thread has some registers and a private memory. Registers can be accessed in two clock cycles. Private memory consists in a private section of off-chip DRAM and it is used to stack frame, spilling registers, and for private memory variables that do not fit in the registers. Recent GPUs cache this private memory in the L1 and L2 caches to aid register spilling and to speed up function calls. Private memory is freed as soon as the thread finishes.

Threads inside a block can access the same shared on-chip memory that each SM is equipped with. Resources allocated in the shared memory are freed once the block is completely finished. The shared memory can be accessed in two clock cycles if no access conflict occur. To increase bandwidth shared memory is divided into equally sized banks. Hence full parallel access is possible if threads from a warp access data without bank conflicts.

The condition of bank conflict vary depending on the GPU series.

Since the local memory is limited and the accesses to the device memory are slower, it is necessary to organize the code in order to find the best trade-off between the kernel length and the number of accesses to the global memory. Only data in global memory remain consistent for the lifetime of the CUDA context. Therefore, communications between blocks of the same kernel or between different kernels are obtained allocating space for results in the global memory using a shared memory computation model. Global memory has a latency between 400-600 cycles, which can usually be hidden by warp scheduling. The accessing pattern to global memory should be structured in a particular way to allow coalescing of the access, which means that data requested by a *warp* are transferred in a single memory transaction. Failing in this could lead to a performance drops up to 90% [33]. As for the bank conflict, the condition for coalescing vary depending on the GPU generation.

#### 1.3.4 Power consumption

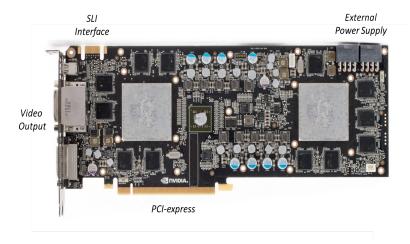

In heterogeneous CPU/GPU computing systems, GPUs are the most power consuming devices. Nowadays GPUs cannot be supplied via the PCI-express interface and they usually require additional power supply lines. In particular each card used in the application described in chapter 3 requires a power supply of 375W [2]. Therefore when multiple cards are packed on the same platform the power requirement rises to order of KW.

Figure 1.18: NVIDIA GTX590 Graphics card.

### 1.3.5 Programming the NVIDIA GPU

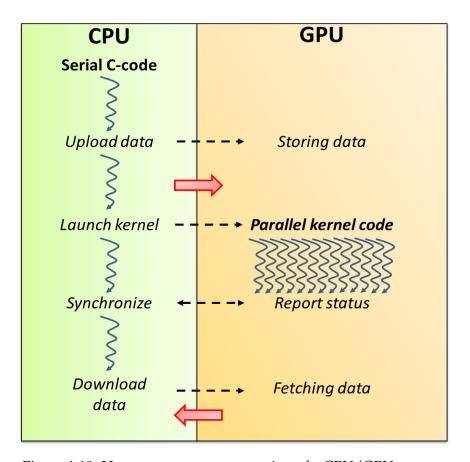

The heterogeneous programming model supported by GPU implies a system composed of a host (CPU) and one or more GPUs each with their own separate memory. Kernels operate out of GPU memory, so the runtime provides functions to allocate, deallocate and copy GPU memory, as well as transfer data between host memory and GPU memory [34]. A typical application flow is shown in figure 1.19.

Figure 1.19: Heterogeneous programming of a CPU/GPU system.

## 1.3.6 Multiple GPUs

Multiple GPUs can work in parallel if the motherboard allows users to accommodate multiple graphics cards, as shown in figure 1.20.

Starting from the Fermi-class each GPU can map memory belonging to the other GPU into its global address space. To fully exploit the performance capabilities of a Multi-GPU system, CUDA has been used in concert

Figure 1.20: GPUs in Multiple Slots [5].

with OpenMp [35]. OpenMP is a multi-threading library based on shared memory principles. OpenMP runtime support, allows programmer to split the code into multiple threads via preprocessors directives. At the end of the region threads are joined again with the master thread. An example is shown in figure 1.21.

```

Float a[4], b[4], c[4];

int i;

#pragma omp parallel (private i)

{

i = omp_get_thread_num();

c[i] = a[i] + b[i];

}

printf(" c= %f %f %f %f\n ", c[0], c[1], c[2], c[3]);

```

Figure 1.21: Parallel processing with OpenMP.

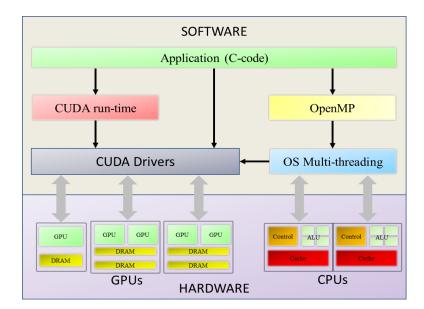

CUDA provides the application programming interface to the GPU, while OpenMP manages CPU multi-threading. Each GPU has a dedicated CPU core for handling and controlling. Other solutions are available, but OpenMP is portable, lightweight and it fits perfectly the needs of the designs presented in chapter 2 and 3. The software hierarchy is depicted in figure 1.22.

Figure 1.22: Software hierarchy and interaction with hardware.

A typical application starts a single master thread. Then a fork is created to assign one CPU thread per GPU. Within each thread a CUDA context is created; the context sets up the synchronization loop and initializes the runtime library. Then all CUDA API calls will refer to the selected GPU. Host Random memory access (RAM) is shared among CPU threads and with them also the CUDA contexts which can be used as buffer to exchange data between GPUs.

### 1.3.7 GPU applications

The introduction of CUDA has changed the world of high performance computing. New applications began to report speedups in the order of ten to hundred times over CPUs. However, not all applications can be efficiently accelerated on GPU. Basically, any application involving an high number of concurrent floating-point operations can greatly benefit from GPU acceleration.

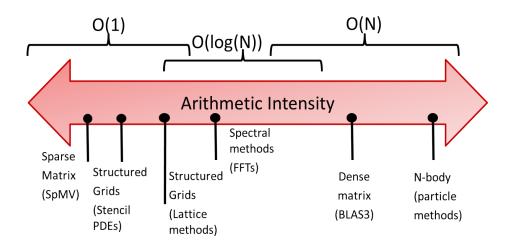

One intuitive way to compare potential performance of a variation of architectures is the Roofline model [36]. It links together floating-point performance and memory performance introducing a parameter called arithmetic intensity. Arithmetic intensity is defined as the ratio of floating-point operations per byte of memory accessed [4].

Figure 1.23: Arithmetic Intensity, specified as the number of floating-point operations to run the program divided by the number of Bytes accessed in main memory [4].

Figure 1.23 shows the arithmetic intensity of several computational problems. Some of these have an arithmetic intensity that scales with problem size (such as dense matrix) while some others have an arithmetic intensity independent of problem size (such as sparse matrix).

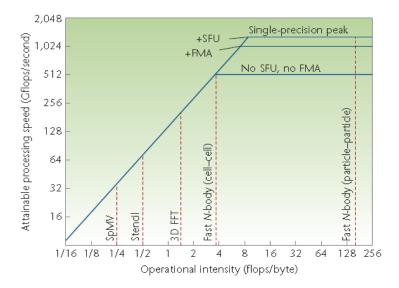

As an example, the Roofline model for a GPU NVIDIA TESLA C2050 (Fermi class) is shown in figure 1.24 [6].

Figure 1.24: Roofline model of several kernels on an NVIDIA C2050 GPU [6].

The graph shows how the throughput changes, changing the application. The SFU label indicates the use of special function units and FMA indicates the use of multiply-add instructions. A sparse matrix-vector multiplication is labelled *SpMV*, a multigrid method with a seven-point-stencil is labelled *Stencil* and a 3D fast-Fourier transform is labelled *3D FFT*. As shown in the graph, only applications which present an high arithmetic intensity (also called operational intensity in figure 1.24) are capable to exploit the throughput provided by GPUs. This because the intensive computation hides the memory latency.

## 1.4 Field Programmable Gate Array

FPGAs were introduced 30 years ago and since then, they have become a popular implementation for digital circuits. Field Programmable Gate Arrays are devices which can be electrically programmed to became a digital circuits or systems. These devices represent a cheaper solution as compared to Application Specific Integrated Circuits (ASICs). In fact, FPGAs cost around a few tens to a few thousand dollars and they take less than a second to configure while ASICs require time and money in order to obtain first device. Moreover a portion of FPGA can be reconfigured while the rest of an FPGA is still running [37]. This flexibility is the main advantage of FPGA but at the same time the major cause of its drawback. This because flexibility makes FPGA larger, slower and more power consuming than their ASICs counterparts [37]. In general ASICs are convenient for large markets while FPGAs for small markets. An example of FPGA is depicted in figure 1.25.

It is composed of an array of programmable logic blocks (including general logic blocks, digital signal processors, multipliers and memory), connected by a programmable routing network. The routing network of an FPGA occupies 80-90% of total area, while the logic area occupies only 10-20% [38]. The entire array is surrounded by programmable input/output blocks which make possible the off-chip connections. The "reconfigurable" term in FPGAs means the ability to program a function into the chip after the fabrication process. This is made possible by the programming technology, which is a method that can cause a change in the behaviour of the chip after

Figure 1.25: Overview of FPGA architecture [7]

the fabrication process [39].

# 1.4.1 Programming Technologies

An FPGA is configured using electrically programmable switches. Several programming technologies have been used so far and their proprieties dictate the trade-off in reconfigurable architectures. The most important are SRAM (Static Random Memory Access) programming technologies [7], flash [40] and anti-fuse [41].

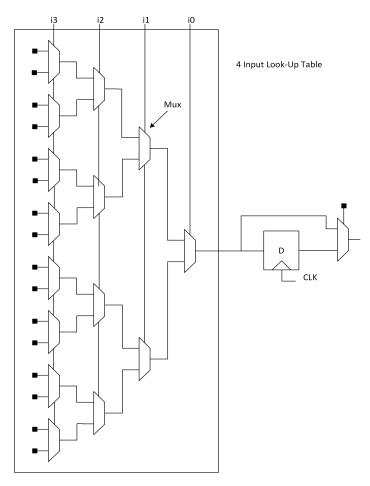

# 1.4.2 Configurable Logic Block

The basic block of an FPGA is the configurable logic block (CLB), which provides logic and and storage for the target application. The purpose of a configurable logic block is to provide the computation and storage elements needed in digital circuits and systems. The CLB could theoretically be either a single transistor or an entire processor. Both the cases present their advantages and disadvantages. When a CLB is very fine-grained, it

requires a lot of programmable interconnect to create any typical logic function. This results in an area-inefficiency (because programmable routing is expensive in terms of area), low performance (each routing hop is slow) and high power consumption (since each interconnect has an high capacitance that must be charged and discharged). At the other extreme, when the CLB is very coarse-grained, it cannot perform small function without a massive wastage of resources. Usually intermediate solutions to implement efficient CLBs are used. Some of them includes basic logic blocks made of transistors [42], NAND gates [43], interconnection of multiplexers [44], lookup tables (LUTs) [45], and PAL-style wide-input gates [46].

Figure 1.26: Basic Logic Element (source: Tree-Based Heterogeneous FPGA Architectures.)

The market's leader Xilinx [47] and Altera [48] use LUT-based CLBs. LUT-based CLBs provide a good compromise between fine-grained and coarse-

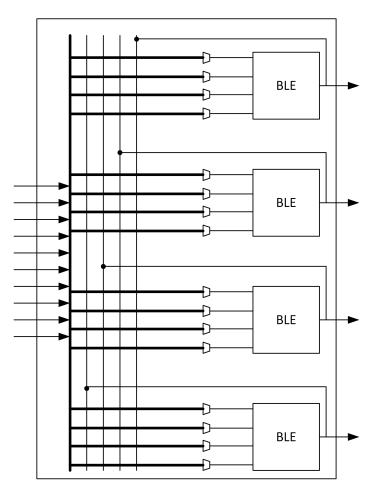

grained blocks. Figure 1.26 shows the architecture of a LUT-based CLB. It consists of a look-up table and a flip-flop. The LUT has k boolean inputs (i.e. 4) and  $2^k$  configuration bits (16 SRAM bits). It can implement any kinput function. A multiplexer selects the basic logic element (BLE) to be either the output of the flip-flop or the output of the look-up table. Figure 1.27 depicts a cluster of BLEs. The output of each BLE is accessible to other BLEs through a local interconnect network. Usually CLB packs together 4 to 10 BLEs in a single cluster.

Figure 1.27: A configurable logic block (CLB) (source: Tree-Based Heterogeneous FPGA Architectures.)

In addition to standard CLB, modern FPGAs contain a heterogeneous mixture of blocks to address specific functions. These specific purpose blocks are DSPs, multipliers or dedicated memory blocks.

# 1.4.3 Routing Architecture

Configurable logic blocks are connected to each other through programmable routing network. This interconnect consists of wires and programmable switches that connect the logic elements. These switching are configured using the programmable technology.

The interconnect structure must be flexible to accommodate a high variety of circuits keeping the design speed as high as possible. Although different circuits need different connections, there are a lot of common characteristics of digital circuits which can be used to optimally design the routing network of FPGA architecture.

Most circuits exhibit locality, hence they require a high number of short wires, while at the same time they need at least some longer wires to support more distant connections. In addition, signals such as clock and reset must be widely distributed across the FPGA. Hence, care in designing routing interconnect is very important because routing has to address both flexibility and efficiency. The macroscopic arrangement of wires with no focus on the more microscopic switching between wires is called global routing architecture. The global routing architecture can be categorized as either hierarchical [49] or island-style [38, 50]. Currently, most commercial FPGA architectures use island-style architectures [51, 52, 53, 54]. This routing structure offers several advantages. First of all, an efficient connection for most designs can be achieved, since routing wires are in close physical proximity to logic blocks. In addition, the physical layout for each logic block can be optimized to form a single tile. As a result, the minimum feasible routing delay between blocks can be quickly evaluated.

### 1.4.4 Software Flow

One of the main aspect of FPGA research is the development of Computer Aided Design (CAD) tools for mapping applications to FPGAs. The software flow, also called CAD flow, takes an application described using a Hardware Description Language and converts it to a stream of bits used to configure the FPGA. This process can be divided into five steps, namely: synthesis, technology mapping, packing, placement and routing. Finally a bitstream that configures the state of the memory bits in an FPGA is pro-

duced. The state of the bits determines the logic function mapped on the FPGA.

# **Logic Synthesis**

The first step in the software flow is the logic synthesis [55, 56] which transforms an HDL description into a set of Flip-Flops and boolean gates. Several technology-independent techniques are applied to optimize the boolean network.

# **Technology Mapping**

The purpose of technology mapping consists in finding a network of logic elements which implements the boolean network. In particular in an FPGA, technology mapping problem involves transforming the boolean network in k-input look-up tables and registers. The most common used tools for FPGA technology mapping are based on the FlowMap algorithm [57]. This algorithm is capable to find an optimal solution in polynomial time.

#### **Packing**

Usually the configurable logic blocks in a Mash-based FPGA are organized in two levels of hierarchy. The first level involves logic blocks which are k-input LUTs and flip-flops, while the second level consists of k logic blocks together to form a cluster. The packaging phase of the flow consists of forming groups of k logic blocks. Hence these clusters can be directly mapped to a logic element of an FPGA.

#### **Placement**

The purpose of placement algorithms is to determine which logic block should implement a logic function required by the circuit. The goal of these algorithms is to connect logic blocks close together in order to balance and minimize the wiring across the FPGA, or to maximize circuit speed.

# Routing

The routing is the process where nets are assigned to routing resources avoiding to share one routing between more nets. The state-of-the-art rout-

ing algorithm is *Pathfinder* [58]. This algorithm operates according a graph abstraction G(V,E) of the routing resources. The routing problem consists in finding a direct tree in G which connects the source and the sink terminals. This process is quite complicate since the routing resources are limited.

#### **Timing Analysis**

The purpose of the timing analysis is to determine the speed of the circuits which have been placed and routed and to estimate the slack [59] between source-sink connections. This is done in order to find and fix the connections which slow down the circuit.

#### **Bitstream Generation**

Bitstream information is generated from the netlist after the placement and routing processes. The bitstream contains information as to which SRAM bit be programmed to 0 or 1. It is configured on the FPGA using a bitstream loader.

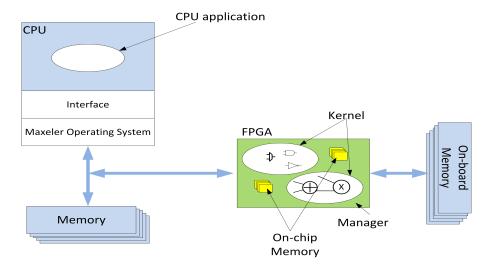

# FPGAs for High Performance Computing: The Max-1.5 eler Solution

Recently FPGAs have expanded their application area to HPC. Several HPC vendors offer FPGA-based high performance computing solutions. These boards are socket compatible with Intel and AMD processors using highspeed bus. To improve the bandwidth, these boards offer on-board memory. In the design presented in chapter 4, the HPC system based on CPUs and FPGAs proposed by Maxeler [60] is used. It consists of a combination of synchronous dataflow, vector and array processors. Figure 1.28 depicts the architecture of a Maxeler dataflow system which comprises FPGAs with their own local memories, connected to a host through PCI-express or Infiniband. Each FPGA can access two types of memory: on-chip memory which can store several Mega-bits of data accessible with an high bandwidth and a large on-board memory which can store many Giga-bytes of data off-chip. However, one important limitation is that the on-board memory works in burst mode. This means that at least a block of 384 byte of data

Figure 1.28: FPGA-based computing architecture (source: Maxeler.)

must be read even if just 1 bit must be modified. This memory access provides excellent performance when data are read in sequential order, but poor performance when data are read randomly.

# 1.5.1 Programming the FPGA using MaxCompiler

A Maxeler supercomputer consists of CPUs and FPGAs. The CPUs run executable files while FPGAs run a configuration file which contains the bitstream information. In particular, a general application consists of a small pieces of source code running on CPU and a large amount of data running on FPGA. In order to create the FPGA configuration file, a domain specific language called MaxCompiler is used. It is a Java-cased programming language with additions for FPGA memory and data access. Therefore an additional preliminary level is added to the software flow described in section 1.4.4. The FPGA is programmed through one or more kernels and a manager file. Kernels are graph of pipelined arithmetic units, which implement the computation. Without loops in the graph, data flows from inputs to outputs. With loops in the graph, data flows in a physical loop inside the FPGA, in addition to flowing from inputs to outputs. The manager orchestrates data movement between kernels, FPGA memory and other input/output interconnects. The first step when using MaxCompiler is to design, debug and simulate the application using a standard computer. Then given kernels and a manager, MaxCompiler generates dataflow implemen-

Manager Dataflow CPU Kernel(s) (.java) Conf. App. (.java) (.c .f) Simple Live MaxelerOS Kernel Compiler Manager CPU HWHardware Build Compiler, Linker Simulation **FPGA** Conf. (.max) .exe

tation which can be called from the CPU.

Figure 1.29: MaxCompiler chain (source: Maxeler.)

Figure 1.29 illustrates the development tool provided by MaxCompiler and how it works to build an accelerated application. Usually in a Maxeler supercomputer, multiple FPGA are connected together via a high-bandwidth interconnect as shown in figure 1.30.

Figure 1.30: Maxeler dataflow system architecture (source: Maxeler.)

# **Chapter 2**

# Optical Model for Design and Analysis of Solar Field on Multi-GPU platform

This is the first in a series of three chapters presenting the major contributions of this thesis. They address the implementation of specific algorithms using different configurations of the systems described in chapter 1. The purpose of this chapter is to present an efficient implementation of optical model for design and analysis of solar field on Graphics Processing Units. The work presented in this chapter was carried out as part of the ERG project supported by ENIAC JU. This chapter follows the structure of [1].

# 2.1 Motivation and background

The depletion of fossil fuels, the increase in energy demand and the attention of public opinion to environmental problems are moving the production of electrical energy towards renewable sources. The sun is the most abundant source of energy on Earth and every year delivers more than 10,000 times the amount of energy that humans currently use [61]. Hence, the global solar electricity market is currently more than \$10 billion/year, and the industry is growing at more than 30% each year [62]. One of the best ways to harness solar energy on a large scale is based on concentrating tower power plants [63, 64]. This system, also called Central Receiver Sys-

tem (CRS), consists of a field of highly reflective mirrors called heliostats which focus the solar radiation on an absorbent surface, positioned at the top of a tower. Solar radiation heats a fluid which is used in thermal or thermo-electrical processes as as shown in figure 2.1 and has been published in [1].

Figure 2.1: Block diagram of a Solar tower power plant (source: eSolar).

The design and optimization of these systems is quite complex and time-consuming, because it requires several design parameters to be considered at different time steps [65]. For example codes like MIRVAL [66] and SolTRACE [67] provide a detailed description of power reflected using a ray-tracing method, but they do not support field optimization. Accuracy of ray-tracing improves, increasing the number of rays, but unfortunately the computation time itself increases. UHC [68] and DELSOL [69] which use the convolution method contain more approximations in the peak flux computation, but they provide a quicker evaluation of the annual performance of a field [70]. These examples show that there is a trade-off between accuracy and simulation time in the existing design tools.

This chapter presents a simulation framework capable of supporting the design and analysis of solar fields for tower power plants with high accuracy and speed. The work is motivated by the need to analyze and optimize solar fields taking into account degradation factors such as shadowing, blocking, atmospheric attenuation, cosine effects, spillage, mirror reflectivity [71, 72], in addition to mirror imperfections and non-planar geometries.

The need to reduce the computational time has been recognized by other

groups who have proposed novel algorithms for this purpose [73]. However better improvements can be obtained by algorithms that exploit parallel computing architectures based on graphic processing units, which, at a lower cost than standard servers, provide an accurate and fast simulation environment.

# 2.2 Mathematical model

The sun can be considered as a Lambertian surface appearing from the Earth as a disk of constant radiance [74]. However, considering a solar concentrating system on the Earth's surface, solar irradiation appears different from the ideal case due to the effect of the atmosphere on the sun's shape. In order to simulate major atmospheric effects, the model describes the sun as a Lambertian plane with a defined irradiation distribution. For simplicity's sake, a normal distribution will be considered, as suggested in [75], because it is simple to implement and introduces a limited error in the sun description. Solar distribution, supported by data available in databases (such as PVGIS [76] for Europe and Africa or TMY3 [77] for the USA), provides site-specified solar irradiation.

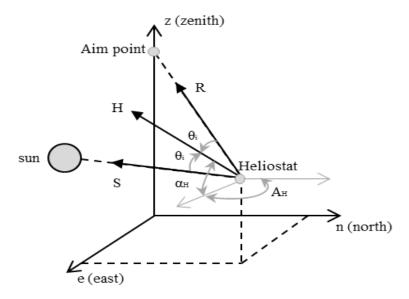

Let us consider the subsystem sun-mirror-absorber as shown in figure 2.2.

Figure 2.2: Reflection of the sun's rays by a heliostat to a single aim point.

Since Snell's law requires that the angle of incidence  $\theta_i$  be equal to the angle

of reflection, the cosine of this angle can be derived from the scalar product between sun ray unit vector S and aim point unit vector R as reported in equation 2.1:

$$\cos(2\,\theta_i) = S \cdot R \tag{2.1}$$

where vectors S and R can be written as:

$$S = S_z \hat{i} + S_e \hat{j} + S_n \hat{k} \tag{2.2}$$

$$R = R_z \hat{i} + R_e \hat{j} + R_n \hat{k} \tag{2.3}$$

$S_z$ ,  $S_e$ ,  $S_n$  and  $R_z$ ,  $R_e$ ,  $R_n$ , represent the direction cosines, where i, j and k are unit vectors along z, e, and n axis. The direction cosines of S may be written in terms of solar altitude ( $\alpha$ ) and azimuth (A) as:

$$\begin{cases} S_z = \sin \alpha \\ S_e = \cos \alpha \sin A \\ S_n = \cos \alpha \cos A \end{cases}$$

(2.4)

The reflection surface unit normal (H) can be found by adding the incidence and reflection vector and dividing by appropriate scalar quantity as shown in Equation 2.5:

$$H = \frac{R+S}{2\cos\theta_i} = \frac{(R_z + S_z)\hat{i} + (R_e + S_e)\hat{j} + (R_n + S_n)\hat{k}}{2\cos\theta_i}$$

(2.5)

In the same way as shown in equation 2.4 it is possible to describe the direction cosines of unit vector H in terms of altitude ( $\alpha_H$ ) and azimuth ( $A_H$ ) of the reflecting surface.

$$\begin{cases} H_z = \sin \alpha_H \\ H_e = \cos \alpha_H \sin A_H \\ H_n = \cos \alpha_H \cos A_H \end{cases}$$

(2.6)

Heliostat tracking angles may be derived from equation 2.5 as shown in equations 2.7 and 2.8:

$$\sin \alpha_H = \frac{R_z + \sin \alpha}{2\cos \theta_i} \tag{2.7}$$

$$\sin A_H = \frac{R_e + \cos \alpha \sin A}{2\cos \theta_i \cos \alpha_H} \tag{2.8}$$

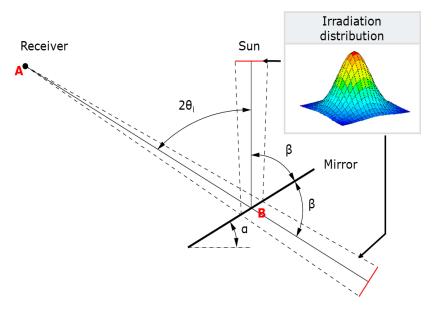

Once the correct tilt angles ( $\alpha_H$ ,  $A_H$ ) have been found, the observer located on the receiver surface, looking in the direction of the mirror will see the sun reflected at an apparent position, called the apparent sun plane, placed behind the mirror as shown in figure 2.3 [78].

Figure 2.3: Geometrical model for optical simulation.

This plane is calculated as the plane located at a distance equal to the earthsun distance, orthogonal to the line that passes through the reflection point and the mirror centre.

An observer sees the sun through the mirror and consequently sees the mirror edges as delimiting the sun disk. Therefore, to find the solar radiation collected by the mirror, it is necessary to project the mirrors corners onto the apparent sun plane as shown in figure 2.4.

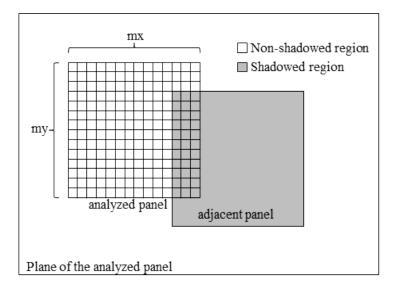

Normally, central receiver systems are composed of hundreds or thousands of heliostats. Consequently, in order to project the mirror corners on the sun plane, it is necessary to verify the blocking and shadowing effects introduced by adjacent heliostats. In order to evaluate these two effects, each mirror is discretized into a matrix of square sub-mirrors. In evaluating the shaded area, the projection of each potentially occluding mirror onto the plane of the mirror under analysis is calculated, taking as observation point the center of the solar dish. A sub-element is then considered in the shad-

Figure 2.4: Simulation model geometry for a single receiver point analysis.

owing area if the neighbour mirrors' projection falls on it. Evaluation of blocking is similar to the detection of shadowing. The only difference is in the observation position which in this case coincides with the receiver's.

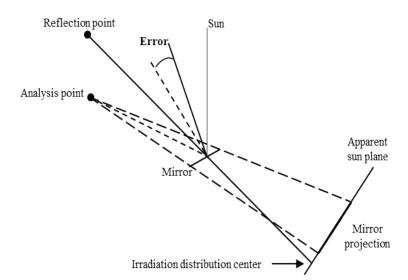

As mentioned above, the proposed model allows one to quickly evaluate field performances, composed of planar mirrors, or to obtain a more detailed description, considering mirror imperfections or non-planar geometry. In the study of planar square mirrors, the adjacent non-shadowed and non-blocked squares are joined up in larger squares, in order to calculate the minimum number of integrals. Otherwise, if a more accurate analysis is needed, it is possible to describe imperfections at the sub square level by introducing two local angles which tilt the sub-mirror from the ideal position. This model feature can also be used to describe non-planar geometries of mirrors. In this case the apparent sun plane must be calculated for each sub-element taking into account the different reflection point as shown in figure 2.5.

The solar radiation collected on the receiver by a heliostat will be given by the integral over the apparent sun plane of the flux density function. The limits of integration are the projected mirror corners on the plane.

$$P = \iint_{\substack{Mirror \\ Projection}} F(x_r, y_r) \, dx_r \, dy_r \tag{2.9}$$

Figure 2.5: Geometric model for simulation with non-idealities in mirror surface.

where  $F(x_r, y_r)$  is the flux density function.

Performing this operation for each heliostat, the total solar radiation on the absorber surface is achieved.

# 2.3 Computing System

The algorithm is implemented to run on a standard desktop machine with one or more GPUs. In particular, the configuration of the computing node used for this work is detailed as follows:

- Motherboard SuperMicro X8DTG-QF;

- Two Intel Xeon E5520 CPUs @ 2.27 GHz;

- 24 GB RAM;

- Two NVIDIA GTX 590 graphics cards.

- One NVIDIA GTX 480 graphics card.

The three GPUs and the two quad-core Intel CPUs share the same mother-board.

# 2.4 Implementation

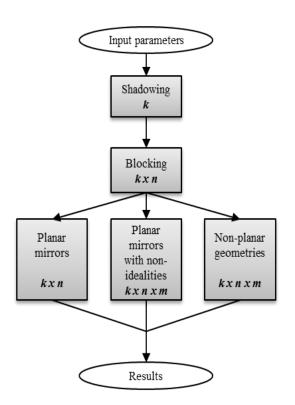

The mathematical model for the system emphasizes a high level of parallelism due to the fact that each mirror is considered as a single element in the system. Thus, the solar flux distribution on the absorber surface is obtained by adding the flux collected by each heliostat. Depending on the specific target, the algorithm presents a different level of parallelism, as shown in figure 2.6.

Figure 2.6: Flow chart of the algorithm.

To analyze the degree of parallelism of each stage in the overall algorithm, three parameters are introduced as shown in table 2.1: k represents the number of heliostats in the solar field, n the number of sub-elements used to discretize the receiver surface, and m the number of elements used to discretize each mirror surface.

| Heliostats k                        | Number of heliostats in the field   |  |

|-------------------------------------|-------------------------------------|--|

| Heliostat grid $m = m_x \times m_y$ | Number of sub-elements used         |  |

|                                     | to discretized each mirror surface  |  |

| Receiver grid $n = n_x \times n_y$  | Number of nodes used                |  |

|                                     | to discretized the receiver surface |  |

Table 2.1: Nomenclature table of the algorithm

# 2.4.1 Programming Model

The main objective of the first part of the algorithm is to study the interactions between adjacent heliostats such as shadowing and blocking. As described in Section 2.2, the first step is to calculate heliostat altitude and azimuthal angles which allow one to obtain the correct position of each mirror. This can be done if one knows the day of the year and the coordinates of each heliostat according to Equation 2.1, 2.7 and 2.8. Once the angles are known, the algorithm calculates the corner positions of each mirror  $(p_1, p_2, p_3, p_4)$  which define the heliostat outer edge.

In detection of shaded areas, the equation of the plane of the mirror being analyzed is calculated solving Equation 2.10:

$$\begin{vmatrix} x - x_1 & y - y_1 & z - z_1 \\ x_2 - x_1 & y_2 - y_1 & z_2 - z_1 \\ x_3 - x_1 & y_3 - y_1 & z_3 - z_1 \end{vmatrix} = 0$$

(2.10)

where  $x_i, y_i$  and  $z_i$  are the three components of the corner  $p_i$ . The outlines of other mirrors, which potentially cover the mirror being analyzed, are projected onto the plane previously calculated, taking the center of the sun as the observation point. The heliostat being analyzed is then discretized into a matrix of  $m = m_x \times m_y$  elements. If the center of a matrix sub-element is contained in one of the neighbor mirror projections, the entire sub-element is considered to lie in the shadowed region and is not included in the peak flux computation, as shown in figure 2.7. This part, which is a computation of the positioning and shadowing interaction of a single heliostat in the field, is repeated for each heliostat. The parallelism level in this part is k.

Detection of a blocked area is similar to the shadowed case. The only difference is the observation point which in this case coincides with that of the

Figure 2.7: Shadowing evaluation.

receiver. Since the receiver is discretized in order to accurately assess the solar flux distribution over the entire surface, the analysis is repeated for each receiver point for each mirror. The level of parallelism for this part is  $k \times n$ .

Once the part of each mirror which actually contributes to collecting solar energy has been identified, the effective mirror outline is projected onto the apparent sun plane and the integration of the irradiation distribution is performed. As stated in Section 2.2, the apparent sun plane is calculated as the plane located at a distance equal to the earth-sun distance, orthogonal to the line that passes through the reflection point and the mirror (submirror) center as shown in 2.3.

Having defined the equation of the apparent sun plane, the algorithm finds parameter values that fit the equations of the four lines that start from the analysis point on the receiver and pass through the four corners of the mirror (sub-mirror) as previously shown in figure 2.4. The cross points between the apparent sun plane and these lines define a polygon on the plane. This polygon represents the integration area. Once the integration polygon is defined in 3D space, the algorithm performs a coordinate space change. The goal of this operation is to pass from a 3D space to a 2D space in order to ease calculation of the integral in 2.9.

The solar flux distribution is numerically evaluated by Gauss-Legendre

quadrature. This part is characterized by a major level of parallelism, the analysis being carried out for each receiver point and for each mirror. In addition, the level of parallelism increases still further when the simulation involves geometries different from the flat one or when mirror non-idealities are introduced. In this case, all the instructions are repeated for each receiver point, for each heliostat and for each sub-element of the heliostats. Thus the number of integrals that can be evaluated in parallel increases to  $k \times n \times m$ .

The solar irradiance on a single mesh element is then calculated by multiplying the integration value by the incident radiation. This value is reduced by the cosine effect estimated considering the solid angle between the normal vector and receiver element, and the line that passes through the mirror center and the analysis point on the receiver. In order to describe the effect of mirror light absorption and non-specular reflectance, a scalar attenuation parameter is then introduced. Another scalar factor is also considered in order to model the attenuation that the light undergoes in crossing the path between the mirror and the receiver due to air scattering and absorption. This last term is dependent on the distance between each mirror and the receiver.