### Alma Mater Studiorum – Università di Bologna Università degli Studi di Padova

### DOTTORATO DI RICERCA IN

### Informatica

### Ciclo XXIII

Settore scientifico-disciplinare di afferenza: INF/01

# Definition, realization and evaluation of a software reference architecture for use in space applications

Presentata da: Marco Panunzio

**Coordinatore Dottorato**

Relatore

Prof. Simone Martini

Prof. Tullio Vardanega

Esame finale anno 2011

### Abstract

A recent initiative of the European Space Agency (ESA) aims at the definition and adoption of a software reference architecture for use in on-board software of future space missions. The initiative responded to high-level strategic goals that ESA set in the last few years in dialogue with its industrial environment. This PhD project was launched in the intent of supporting the ESA initiative with a scientifically-based contribution.

In the initial phase of the PhD project we gathered all the industrial needs relevant to ESA and all the main European space stakeholders: national space agencies, system and software prime contractors and the main software suppliers. The results of this initial phase were submitted to and discussed in a top-level working group comprised of representatives of all those stakeholders. Exploiting knowledge from previous investigations funded by ESA and entertaining focused discussions with the system and software prime suppliers of ESA, we were able to consolidate a set of technical high-level requirements for the fulfillment of those industrial needs. The conclusion of that phase of the investigation is that the best solution for the fulfillment of the high-level requirements is the definition, realization and adoption of a software reference architecture.

The software reference architecture that we are constructing is built on four fundamental constituents: (i) a component model, to design the software as a composition of individually verifiable and reusable software units; (ii) a computational model, to relate the design entities of the component model, their execution needs and their extra-functional properties for concurrency, time and space, to a framework of analysis techniques which ensure that the architectural description is statically analyzable in the dimensions of interest; (iii) a programming model, which consists in a tailored subset of a programming language and a set of code archetypes, and is used to ensure that the implementation of the design entities conforms with the semantics, the assumptions and the constraints of the computational model; and (iv) a conforming execution platform, which is in charge of preserving at run time the system and software properties asserted by static analysis and it is able to notify and react to possible violations of them.

The nature, feasibility and fitness of constituents (ii), (iii) and (iv), in the context of a Model-Driven Engineering approach, were already investigated by the author during the ASSERT project (FP6 IST-004033 2004-8), prior to the launch the PhD project. The results of ASSERT, including the feedback received by the industrial partners of the space domain participating to that project, provided considerable confidence on the overall goodness of the approach we are proposing.

In the core of the PhD project we focused on the design of a component model for use in on-board software, which completes the 4-constituent foundation to the proposed software reference architecture and also is the central contribution of this PhD thesis.

The design of the proposed component model was centered on: (i) rigorous separation of concerns, achieved during software design with the support for design views (following and specializing the standard ISO 42010/IEEE 1471) and by careful allocation of concerns to the three software entities of the approach: the component, the container and the connector; (ii) the support for specification and model-based analysis of extra-functional properties; (iii) the inclusion in the component model of space-specific concerns while consciously trying to keep them separate from domain-neutral concerns.

In this thesis we also discuss a concrete incarnation of the proposed component model, experimentally built around a domain-specific language, a graphical editor and associated design environment for schedulability analysis and code generation. Thanks to our involvement in the CHESS project (ARTEMIS JU grant nr. 216682, 2009-2012) we were also able to compare the results of this effort with an alternative implementation of the same component model based on the extension of a subset of the UML MARTE profile.

**Disclaimer** This work was supported by the Networking/Partnering Initiative of the Directorate of "Technical and Quality Management" at ESA/ESTEC and by the CHESS project ("Composition with Guarantees for High-integrity Embedded Software Components Assembly", ARTEMIS Joint Undertaking grant nr. 216682).

The views presented in this PhD thesis are however those of the author's only, and do not engage those of the European Space Agency or of the members of the CHESS consortium.

### Acknowledgments

During the late summer 2007, almost at the tail end of the ASSERT project in which I was working, my supervisor proposed me to apply to the PhD program in Computer Science.

At the beginning I was not really convinced; and after some discussions, I had only one request: I wanted an industrially-relevant research topic, and opportunities for frequent contacts with industrial stakeholders to receive feedback from them.

A few months later, after passing the admission exam, I started my PhD.

In these years there have been a few periods of despair, others of doubt and reflection, others of enthusiastic breakthrough. In any case, all accompanied by tenacious commitment.

And as regards the industrial relevance of the various strands of my research, I was never disappointed.

Therefore, I want to gratefully thank my thesis supervisor, Prof. Tullio Vardanega; for his support and guidance throughout the PhD and my previous research experiences; for the decisive discussions when the road ahead was unclear; and for setting up all the conditions that made it possible to work on a very interesting topic, strongly tied to industrial needs.

I want to thank Jean-Loup Terraillon and Andreas Jung at ESA-ESTEC. The periods spent at the research center of the European Space Agency were opportunities for interesting discussions. My collaboration with the SAVOIR-FAIRE working group was crucial to submit the ideas of this thesis to the industrial stakeholders and receive feedback and recommendations.

I also want to thank Alain Rossignol and Luc Planche, for the frank discussions we had during my short visit at Astrium Toulouse.

I am sincerely grateful to Gérald Garcia and Xavier Olive, for the invaluable discussions we had during my 10-day visit at Thales Alenia Space - Cannes. The confirmations and the valuable suggestions I received during that visit were the turning point of this investigation.

I want to thank Prof. Fabio Panzieri and Prof. Michael González Harbour, for their guidance during the various stages of this PhD.

I am also very grateful to the external referees of this PhD thesis:

Prof. Michel R.V. Chaudron and Prof. Ivica Crnkovic. Their feedback and precise comments were helpful to improve the quality of this thesis and the presentation of the results.

*E per finire, voglio ringraziare di cuore i miei genitori. Vi ringrazio per tutto il supporto che mi avete dato in questi anni, e per essere sempre disponibili ad aiutarmi in ogni modo.*

# **Table of contents**

| 1 | Problem statement |         |                                                           | 1  |

|---|-------------------|---------|-----------------------------------------------------------|----|

|   | 1.1               | The ro  | le of the software architecture                           | 6  |

|   | 1.2               | On the  | concept of reference architecture                         | 9  |

|   | 1.3               | Contril | bution and structure of this thesis                       | 11 |

| 2 | A so              | ftware  | reference architecture for on-board space applications    | 19 |

|   | 2.1               | Industr | tial needs of the European space domain                   | 20 |

|   |                   | 2.1.1   | Discussion                                                | 29 |

|   |                   | 2.1.2   | Derivation of high-level requirements                     | 30 |

|   | 2.2               | Techni  | cal requirements                                          | 33 |

|   |                   | 2.2.1   | Requirement importance, prioritization and evaluation     | 37 |

|   |                   | 2.2.2   | Discussion                                                | 41 |

|   | 2.3               | Approa  | ach                                                       | 41 |

|   |                   | 2.3.1   | Component model                                           | 45 |

|   |                   | 2.3.2   | Computational model                                       | 47 |

|   |                   | 2.3.3   | Programming model and execution platform                  | 49 |

|   |                   | 2.3.4   | Interactions between constituents                         | 51 |

|   |                   | 2.3.5   | Model-Driven Engineering                                  | 53 |

|   | 2.4               | State o | f the art                                                 | 54 |

| 3 | A co              | mponer  | nt model for on-board space applications                  | 65 |

|   | 3.1               | Foundi  | ing principles                                            | 66 |

|   | 3.2               | Softwa  | re entities                                               | 68 |

|   |                   | 3.2.1   | Execution platform                                        | 71 |

|   | 3.3               | Design  | views                                                     | 72 |

|   |                   | 3.3.1   | Software architecture and architectural description       | 72 |

|   |                   | 3.3.2   | Design views to enforce separation of concerns and C-by-C | 74 |

|   |                   | 3.3.3   | Engineering design views                                  | 74 |

|   |                   |         |                                                           |    |

|   |      | 3.3.4    | View-diagram relation                                       | 76  |

|---|------|----------|-------------------------------------------------------------|-----|

|   | 3.4  | Design   | n process                                                   | 77  |

|   | 3.5  |          | entities and design steps                                   | 78  |

|   | 3.6  |          | design flow and design views                                | 91  |

|   | 3.7  |          | on of domain-specific concerns                              | 96  |

|   |      | 3.7.1    | General approach                                            | 96  |

|   |      | 3.7.2    | Space-specific concerns                                     | 97  |

|   | 3.8  | Realiza  | ation                                                       | 105 |

|   |      | 3.8.1    | Selection of the design language                            | 105 |

|   |      | 3.8.2    | Development of the design environment                       | 107 |

|   |      |          | 3.8.2.1 Definition of the domain-specific language          | 107 |

|   |      |          | 3.8.2.2 Creation of a prototypal design editor              | 109 |

|   |      |          | 3.8.2.3 Model-based schedulability analysis                 | 112 |

|   |      |          | 3.8.2.4 Code archetypes and code generation                 | 113 |

|   |      |          | 3.8.2.5 Component packaging                                 | 119 |

|   | 3.9  | An alte  | ernative implementation using the UML MARTE profile         | 120 |

|   |      | 3.9.1    | Main challenges and comparison with the DSL approach        | 120 |

| 4 | Eval | uation   |                                                             | 127 |

|   | 4.1  | Case st  | tudy: re-engineering the EagleEye Earth observation mission | 127 |

|   | 4.2  |          | age of technical requirements                               | 143 |

|   | 4.3  |          | ack from stakeholders                                       | 149 |

| 5 | Con  | clusions | s and future work                                           | 151 |

| - | 5.1  |          | fic Publications                                            | 155 |

|   | 5.2  |          | work                                                        | 156 |

| A | List | of scien | tific publications                                          | 159 |

# **List of Figures**

| 1.1 | The software schedule for past and future projects.                                                                                                                 | 1  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | The effort proportionally allocated to the various project phases in past and                                                                                       |    |

|     | future projects.                                                                                                                                                    | 2  |

| 1.3 | Diagram of the INTEGRAL spacecraft.                                                                                                                                 | 3  |

| 1.4 | A classic V-model augmented to show iterative cycles and incremental devel-                                                                                         |    |

|     | opment                                                                                                                                                              | 5  |

| 1.5 | Recapitulation of the concerns addressed by the software architecture and those outside its perimeter.                                                              | 9  |

| 1.6 | An example of composable property                                                                                                                                   | 13 |

| 1.7 | An example of compositional property                                                                                                                                | 13 |

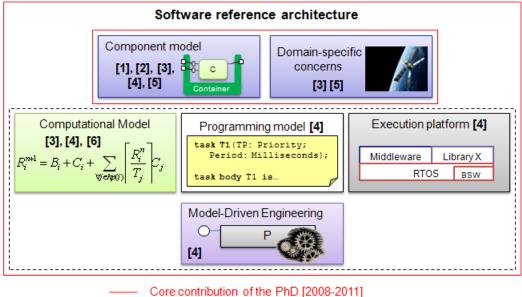

| 1.8 | The goals we set for our investigation and the constituents of the software ref-<br>erence architecture that permit their achievement. We depict in square brackets |    |

|     | the concerns of the software architecture dealt by each constituent (cf. fig. 1.5).                                                                                 | 15 |

| 1.9 | The approach we advocate and the core contribution of the PhD                                                                                                       | 16 |

| 1.7 |                                                                                                                                                                     | 10 |

| 2.1 | The Automated Transfer Vehicle approaching the International Space Station .                                                                                        | 28 |

| 2.2 | Relationship between a selection of the industrial needs and the directions of the forces they act as opposing forces in the development process.                   | 30 |

| 2.3 | Relationship between the industrial needs and the high-level requirements de-                                                                                       | 00 |

|     | rived from them.                                                                                                                                                    | 33 |

| 2.4 | The four constituents of our overall approach and their relationships                                                                                               | 43 |

| 2.5 | Concerns addressed by the various constituents and the overlapping responsi-                                                                                        |    |

|     | bility among them.                                                                                                                                                  | 44 |

| 2.6 | A generic depiction of components and their contractual interfaces                                                                                                  | 46 |

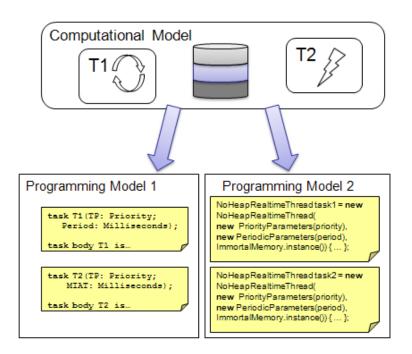

| 2.7 | Relationship between a computational model and its realizing programming                                                                                            |    |

|     | models.                                                                                                                                                             | 50 |

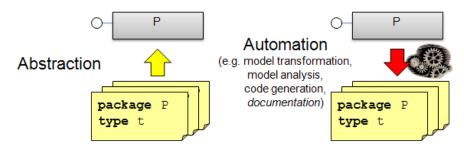

| 2.8 | The greater abstraction level and the automation capabilities provided by a                                                                                         |    |

|     | Model-Driven Engineering approach.                                                                                                                                  | 53 |

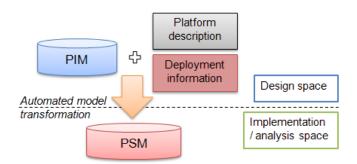

| 2.9 | Transformation from Platform Independent Model to Platform Specific Model .                                                                                         | 54 |

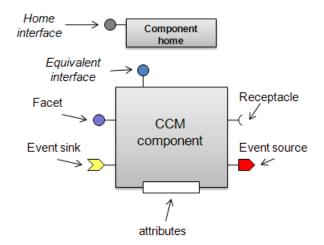

| 2.10       | A component in CCM                                                                                                                                                                       | 57  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

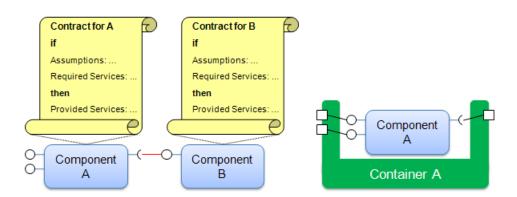

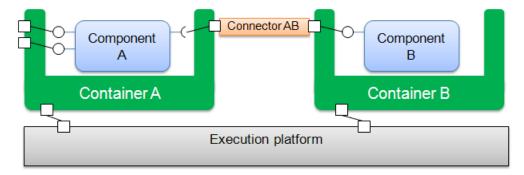

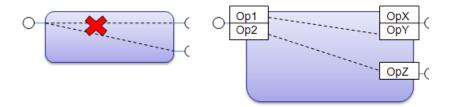

| 3.1<br>3.2 | Two components with their interfaces and component binding and a container<br>A connector that realizes the communication between two containers. The fig-                               | 70  |

|            | ure shows also the underlying execution platform.                                                                                                                                        | 71  |

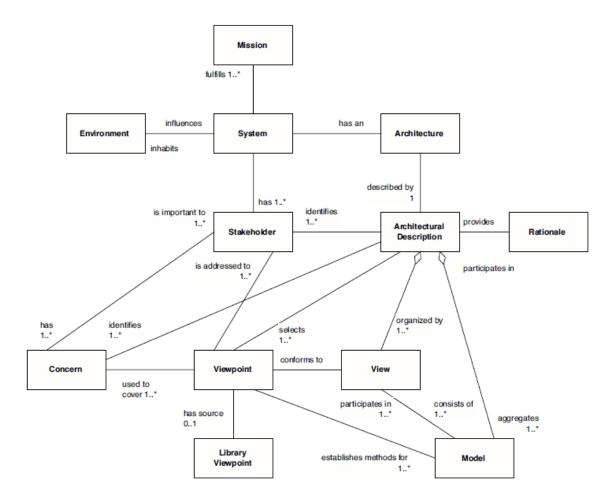

| 3.3        | The conceptual model of an architecture and its architectural description as in the ISO 42010/IEEE 1471 standard.                                                                        | 73  |

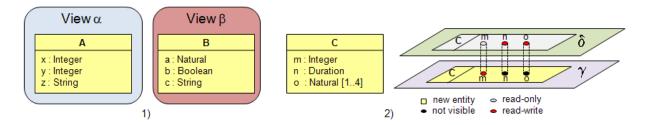

| 3.4        | 1) Entities A and B are visualized by distinct design views: $\alpha$ for A and $\beta$ for B.<br>2) Entity C is partially represented in view $\gamma$ and fully represented (including |     |

| ~ ~        | attributes $n$ and $o$ ) in view $\delta$                                                                                                                                                | 75  |

| 3.5        | <b>a</b> ) Classical relation between a model and the various diagrams; <b>b</b> ) A diagram                                                                                             |     |

|            | is expression of a design view, which focuses on a specific design concern                                                                                                               | 76  |

| 3.6        | A generic component-oriented design process.                                                                                                                                             | 77  |

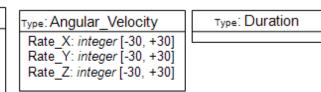

| 3.7        | Data types.                                                                                                                                                                              | 79  |

| 3.8        | Interfaces                                                                                                                                                                               | 79  |

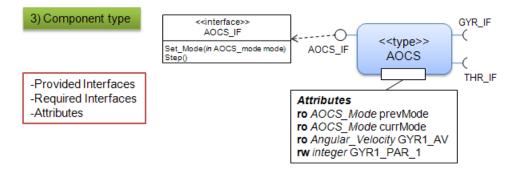

| 3.9        | Component type.                                                                                                                                                                          | 80  |

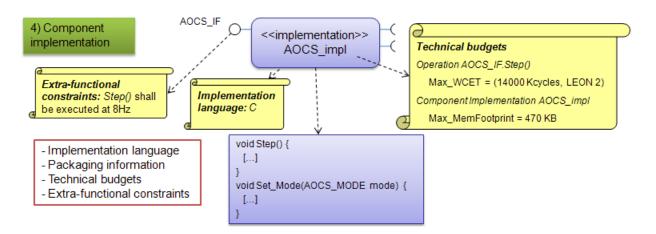

| 3.10       | 1 1                                                                                                                                                                                      | 81  |

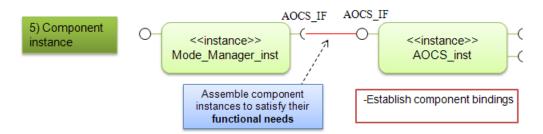

| 3.11       |                                                                                                                                                                                          | 82  |

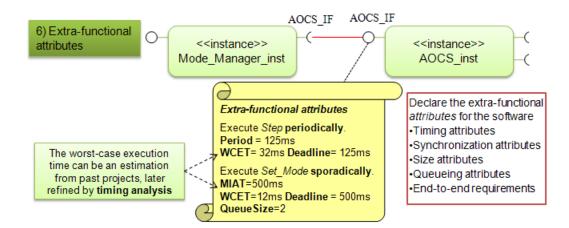

|            | Decoration with extra-functional attributes.                                                                                                                                             | 83  |

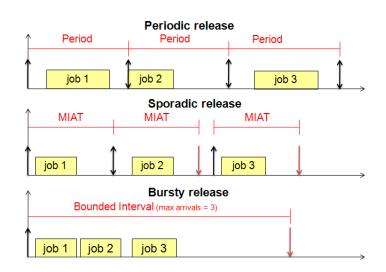

|            | The periodic, sporadic and bursty release patterns                                                                                                                                       | 84  |

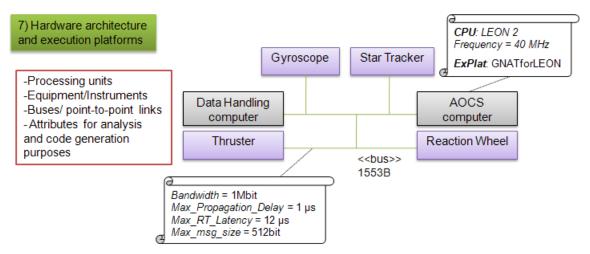

| 3.14       | Hardware architecture                                                                                                                                                                    | 85  |

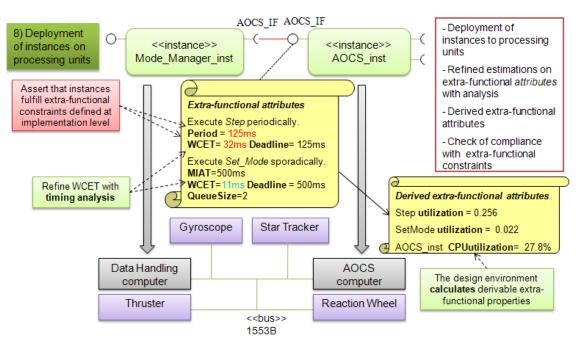

| 3.15       | Deployment of component instances to processing units                                                                                                                                    | 86  |

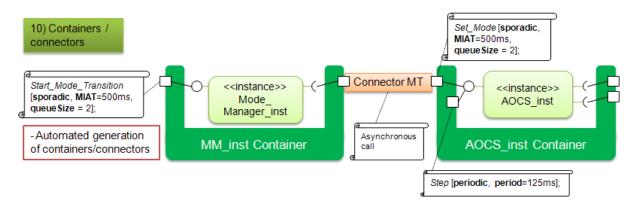

| 3.16       | Automated generation of containers and connectors                                                                                                                                        | 88  |

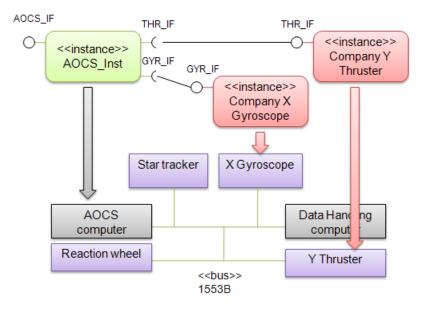

| 3.17       | Sensors and actuators and their relationship with software components                                                                                                                    | 89  |

| 3.18       | Intra-component bindings.                                                                                                                                                                | 90  |

| 3.19       | Inter-component interactions                                                                                                                                                             | 91  |

| 3.20       | The design flow of our component model, including the design steps we de-                                                                                                                |     |

|            | scribed, and the design views used to enforce separation of concerns                                                                                                                     | 92  |

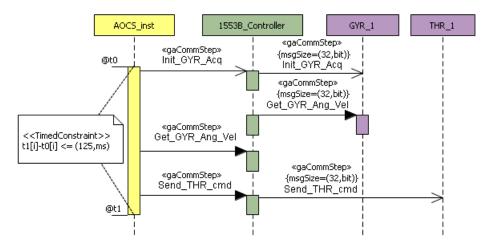

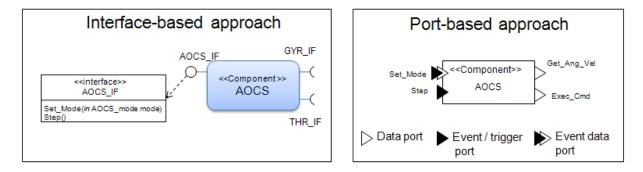

| 3.21       | On the left side: A component which provides services as a set of provided                                                                                                               |     |

|            | interfaces. On the right side: A component which provides services as a set of                                                                                                           |     |

|            | ports.                                                                                                                                                                                   | 93  |

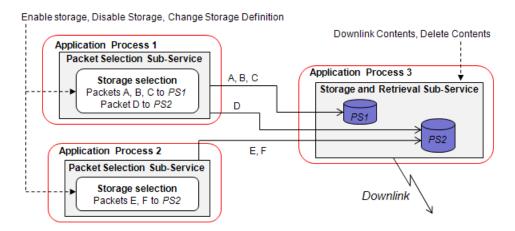

|            | PUS service 15 - On-board storage and retrieval service.                                                                                                                                 | 99  |

|            | 1                                                                                                                                                                                        | 100 |

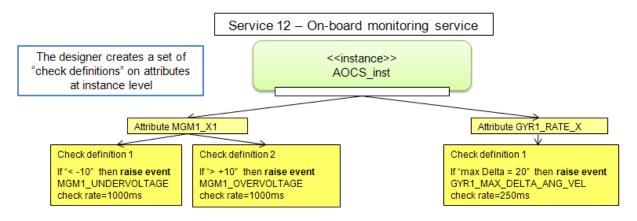

| 3.24       | Our approach to the realization of PUS service 12 - On-board monitoring service.                                                                                                         | 102 |

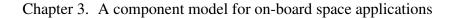

|            | Our approach to the realization of PUS service 8 - Function management service.                                                                                                          |     |

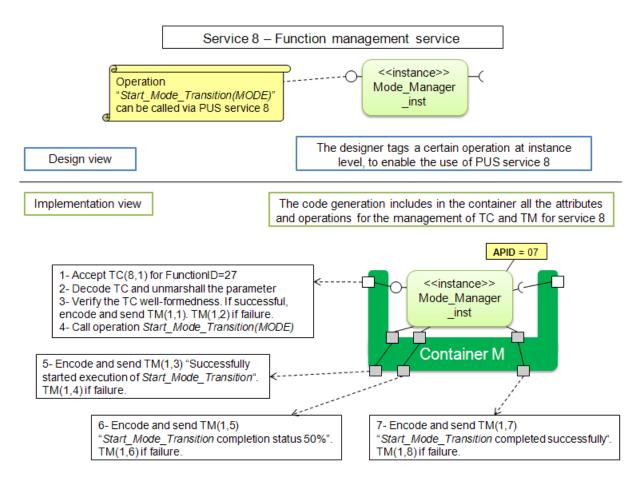

| 3.26       | Relationship between component model and the design language to express it .                                                                                                             | 107 |

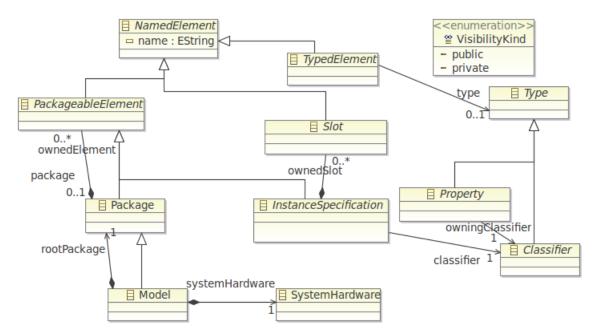

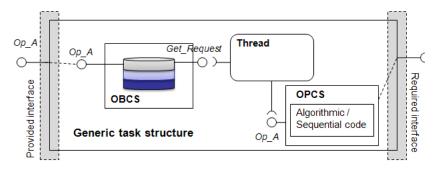

| 3.27       | The core part of our domain-specific metamodel                                                                                                                                           | 108 |

| 3.28       | Metaclasses related to component instances and slots (PI and RI at instance level)                                                                                                       | 109 |

|            |                                                                                                                                                                                          |     |

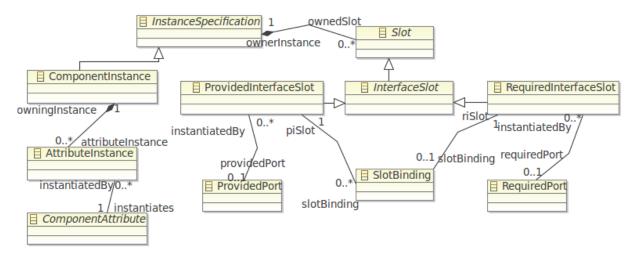

| 3.29 | Model-based schedulability analysis, with back propagation of the analysis re-        |     |

|------|---------------------------------------------------------------------------------------|-----|

|      | sults into the user model.                                                            | 113 |

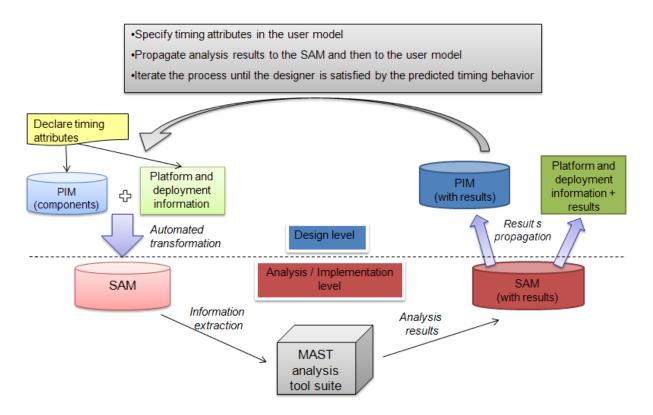

| 3.30 | Generic task structure                                                                | 114 |

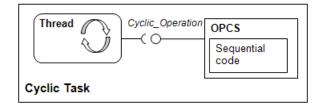

| 3.31 | Structure of a cyclic task                                                            | 116 |

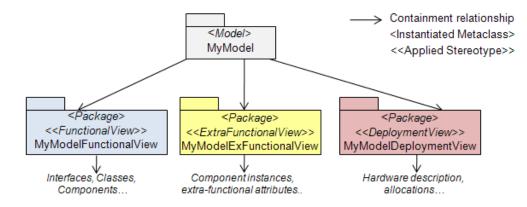

| 3.32 | Realization of design views in UML as packages with an applied stereotype             | 122 |

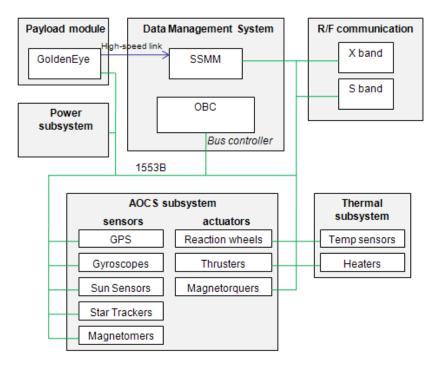

| 4.1  | System architecture of the EagleEye satellite                                         | 128 |

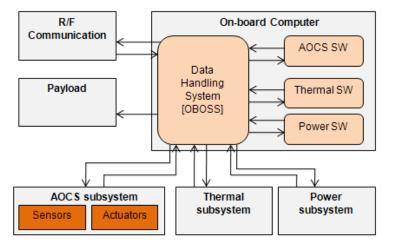

| 4.2  | High-level view of the Eagle Eye on-board software                                    | 129 |

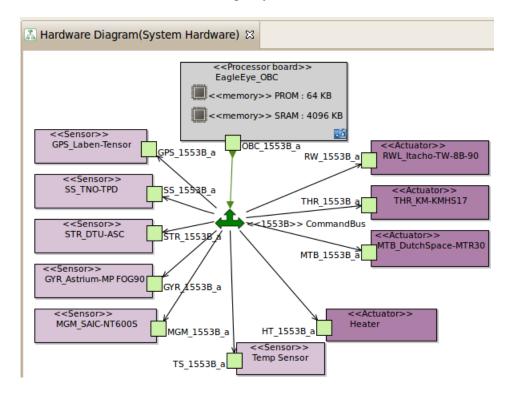

| 4.3  | Hardware diagram for a subset of the EagleEye system architecture                     | 130 |

| 4.4  | Interface diagram for a subset of the EagleEye interfaces                             | 131 |

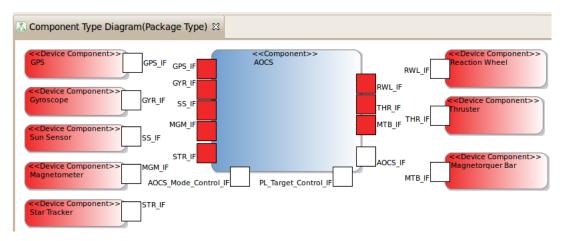

| 4.5  | Component type diagram for the EagleEye AOCS subsystem                                | 132 |

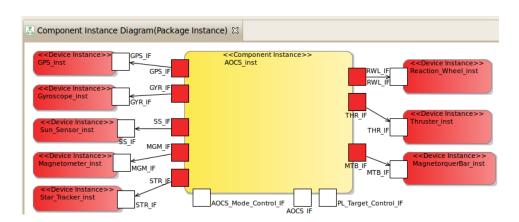

| 4.6  | Component instance diagram for the EagleEye AOCS subsystem                            | 133 |

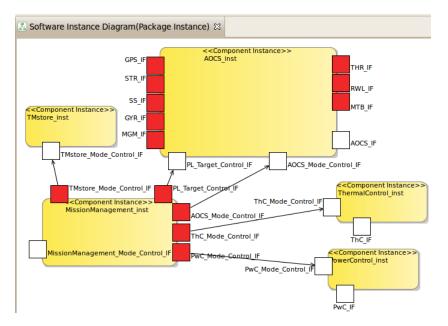

| 4.7  | Component instance diagram for the software components of EagleEye. Visu-             |     |

|      | alization of device instances is selectively deactivated                              |     |

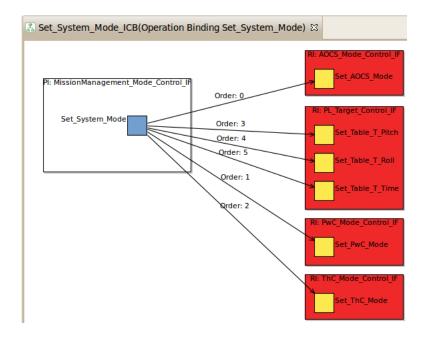

| 4.8  | Intra-component bindings for operation Set_System_Mode                                |     |

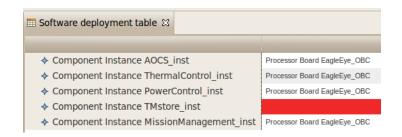

| 4.9  | Deployment table for the EagleEye component instances                                 |     |

| 4.10 | Deployment table of the EagleEye device instances on hardware devices                 |     |

|      | Extra-functional descriptor for the AOCS_IF provided interface in AOCS_inst           | 136 |

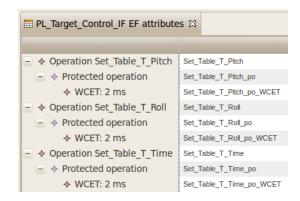

| 4.12 | Extra-functional descriptor for the <i>PL_Target_Control_IF</i> provided interface in |     |

|      |                                                                                       | 137 |

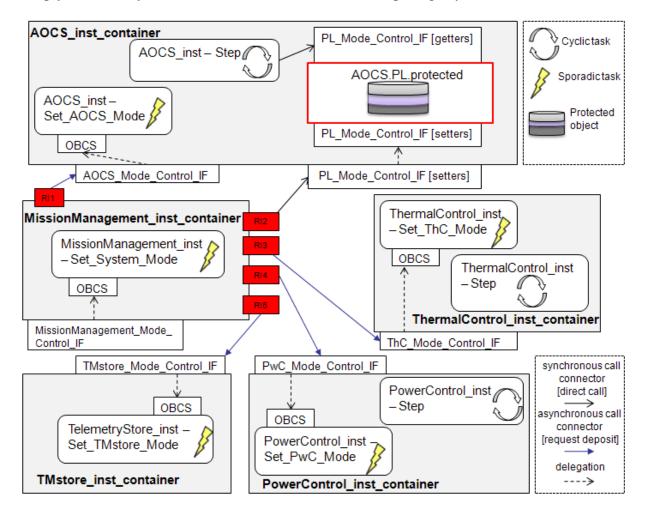

|      | Analysis / Implementation view of EagleEye                                            |     |

| 4.14 | Extra-functional descriptor that allows to call an operation via PUS service 8        | 141 |

| 5.1  | Proposal for hierarchical components.                                                 | 157 |

# **List of Tables**

| 1   | List of acronyms.                                                               | xi  |

|-----|---------------------------------------------------------------------------------|-----|

| 2.1 | The main industrial needs of the European space domain                          | 21  |

| 2.2 | The high-level requirements derived from the industrial needs.                  | 31  |

| 2.3 | Requirement importance, feasibility and the proposed timeframe for their ful-   |     |

|     | fillment                                                                        | 39  |

| 2.4 | Requirement difficulty, with breakdown along the scientific foundation, process |     |

|     | and technological axes.                                                         | 40  |

| 3.1 | Example of permission table for design view $\alpha$ and $\beta$ .              | 75  |

| 3.2 | List of the PUS services.                                                       | 97  |

| 3.3 | PUS service 15 - On-board storage and retrieval service                         | 99  |

| 3.4 | Status of the implementation of the prototype editor                            | 111 |

| 4.1 | List of concurrency and real-time attributes for EagleEye                       | 138 |

| 4.2 | List of results of schedulability analysis                                      | 140 |

| 4.3 | The high-level requirements of the investigation and their fulfillment status   | 144 |

# List of acronyms

### Table 1: List of acronyms.

| Acronym | Meaning                                                 |

|---------|---------------------------------------------------------|

| AADL    | Architecture Analysis & Design Language                 |

| AIT     | Avionics Integration Test                               |

| APEX    | Application/Executive                                   |

| AOCS    | Attitude and Orbit Control System                       |

| ASSERT  | Automated proof-based System and Software Engineering   |

|         | for Real-Time systems                                   |

| ATAM    | Architecture Tradeoff Analysis Method                   |

| ATV     | Automated Transfer Vehicle                              |

| AUTOSAR | Automotive Open System Architecture                     |

| BC      | Bus Controller                                          |

| BSP     | Board Support Package                                   |

| BSW     | Basic Software                                          |

| C-by-C  | Correctness by Construction                             |

| CBSE    | Component-Based Software Engineering                    |

| ССМ     | CORBA Component Model                                   |

| CHESS   | Composition with Guarantees for High-integrity Embedded |

|         | Software Components Assembly                            |

| CNES    | Centre National d'Études Spatiales                      |

| CORBA   | Common Object Request Broker Architecture               |

| DFACS   | Drag Free Attitude Control System                       |

| DHS     | Data Handling System                                    |

| DLR     | Deutsches Zentrum für Luft- und Raumfahrt               |

| DSL     | Domain-specific language                                |

| DSM     | Domain-specific metamodel                               |

| Acronym  | Meaning                                                   |

|----------|-----------------------------------------------------------|

| ECU      | Electronic Control Unit                                   |

| EGSE     | Electrical Ground Support Equipment                       |

| ESA      | European Space Agency                                     |

| FDIR     | Fault Detection, Isolation and Recovery                   |

| GMV      | Grupo Mecánica del Vuelo                                  |

| GNC      | Guidance, Navigation and Control                          |

| GOCE     | Gravity Field and Steady-State Ocean Circulation Explorer |

| GPS      | Global Positioning System                                 |

| HW       | Hardware                                                  |

| ICD      | Interface Control Document                                |

| IDL      | Interface Definition Language                             |

| IMA      | Integrated Modular Avionics                               |

| INTEGRAL | International Gamma-Ray Astrophysics Laboratory           |

| ISS      | International Space Station                               |

| LISA     | Laser Interferometer Space Antenna                        |

| LwCCM    | Lightweight CCM                                           |

| MARTE    | Modeling and Analysis of Real-Time and Embedded Systems   |

| MDE      | Model-Driven Engineering                                  |

| MIAT     | Minimum inter-arrival time                                |

| MOF      | Meta Object Facility                                      |

| NASA     | National Aeronautics and Space Administration             |

| NPI      | Networking/Partnering Initiative                          |

| OBC      | On-board computer                                         |

| OBCS     | Object Control Structure                                  |

| OBOSS    | On-board Operations Support Software                      |

| OBSW     | On-board software                                         |

| OCL      | Object Constraint Language                                |

| OMG      | Object Management Group                                   |

| OPCS     | Operational Control Structure                             |

| PI       | Provided Interface                                        |

| PIM      | Platform Independent Model                                |

| PSM      | Platform Specific Model                                   |

| PUS      | Packet Utilization Standard                               |

| RI       | Required Interface                                        |

| RT       | Remote Terminal                                           |

Table 1 – continued from previous page

| Acronym | Meaning                                           |

|---------|---------------------------------------------------|

| RTOS    | Real-Time Operating System                        |

| RTK     | Real-Time Kernel                                  |

| R/F     | Radio Frequency                                   |

| RUP     | Rational Unified Process                          |

| SAM     | Schedulability Analysis Model                     |

| SRR     | System Requirement Review                         |

| SW-PDR  | Software Preliminary Design Review                |

| SW-SRR  | System Software Requirement Review                |

| SWRR    | Software Requirement Review                       |

| STR     | Star Tracker                                      |

| SW      | Software                                          |

| TC      | Telecommand                                       |

| ТМ      | Telemetry                                         |

| TSP     | Time and Space Partitioning                       |

| TTRM    | Telemetry, Telecommand and Reconfiguration Module |

| UART    | Universal Asynchronous Receiver-Transmitter       |

| UML     | Unified Modeling Language                         |

| V&V     | Verification and Validation                       |

| XML     | eXtensible Markup Language                        |

| WCET    | Worst-case Execution Time                         |

Table 1 – continued from previous page

# Chapter 1 Problem statement

European space industry has entered an economic era in which the funding availed to future space missions are not expected to grow significantly. At the same time, future missions are requested to achieve more and more challenging scientific goals. The steady growth in complexity that accompanies the definition of those missions is at odds with a season of capped budgets for Earth observation, science studies and space exploration.

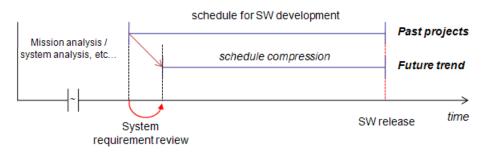

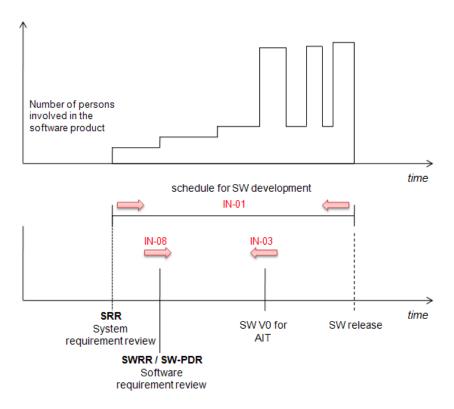

One of the major consequences of this situation is that the activities that contribute the most to the value added of the mission, i.e. mission analysis and system engineering, will play an even bigger role in the overall economy of the project, with a proportional increase of the time and cost invested on them. The implication of this trend is that realization activities, and software development among them, are pushed forward in the project schedule and compressed (cf. figure 1.1 and 1.2).

Figure 1.1: The software schedule for past and future projects. The increased effort for earlier design stages pushes forward the start of software development, hence compressing its schedule.

Interestingly, the complexity of the software product is foreseen to increase significantly to keep pace with the rising mission needs, while the cost of software development is expected to fit in the same or perhaps even decreased budget envelope.

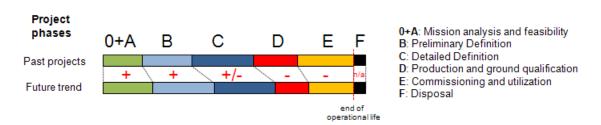

Figure 1.2: The effort proportionally allocated to the various project phases in past and future projects. The figure shows the increased effort for early phases and a reduction of the allocation to "realization activities".

This situation is therefore calling for a rise in the *cost-effectiveness* of software development, thus ultimately increasing the "value" of the software product delivered with a given budget. The best way to succeed in this challenge is to strengthen the efficiency of software development and singling out and abating the recurring costs.

It is therefore necessary to first understand where this is possible, i.e. identify on which factors we can intervene and with how much degree of freedom; and subsequently, to investigate the definition of a solution.

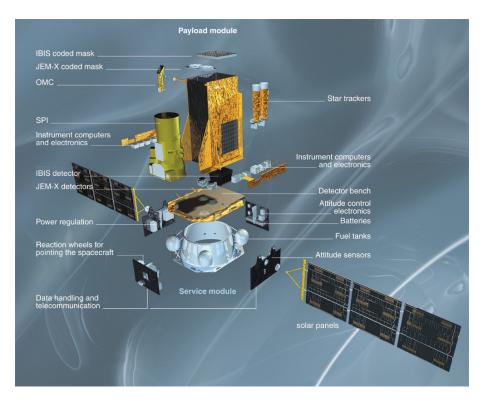

In a typical satellite we can identify two main constituent parts (see figure 1.3): the payload and the service module (also known as platform). The payload part comprises the instruments necessary for the scientific mission (telescopes, spectrometers, detectors, etc..). The service module instead is used to govern the satellite position, orientation and manoeuvres (e.g. perform attitude or orbit changes), communicate with ground, and ensure that the thermal and power needs are satisfied; for this reason the service module is equipped with various sensors (gyroscopes, Earth sensors, magnetometers, thermisters, etc...), actuators (reaction wheels, thrusters, heaters, etc...) or other equipment (solar arrays).

The payload of the satellite obviously is mission-specific: hence, it will differ in form and instruments from one mission to another. Conversely, the service module may present a recurrent structure (i.e. shape and decomposition in subsystems) in several missions.

For example, the INTEGRAL spacecraft used the same service module as the XMM-Newton space telescope, and the Planck and Herschel spacecrafts shared a service module that was very similar both at structural and avionics level.

The on-board software of a satellite conceptually mirrors the same (physical) separation of the satellite structures. Accordingly, we can typically identify a separation of the software in two parts: the payload software and the platform software. Also in this case, the payload software is vastly if not completely different from one mission to the other; there are situations instead in which the platform software may assume a recurrent organization. In software engineering parlance, the "organization" of the software is the *software architecture*.

Figure 1.3: A diagram of the INTEGRAL spacecraft, which outlines the subsystems and instruments of the payload and the service module. *Credits: ESA*

The platform software comprises a set of traditional *functional contents*: the Attitude and Orbit Control System (AOCS) or one of its possible adaptations for particular missions, like the Drag-Free Attitude Control System (DFACS) of the GOCE satellite [32], or a Guidance, Navigation and Control (GNC) system [83] of a deep-space mission; the Data Handling System (DHS); the thermal management subsystem; the power management subsystem; etc.. Additionally it may require the inclusion of more advanced subsystems that realize the functional requirements of future missions, like advanced autonomy and planning or formation flying.

On-board software for satellites can be classified as high-integrity real-time software; the realization of the *functional contents* is therefore subject to stringent requirements at both process and product level in dimensions such as: time and space predictability, safety, dependability, security. As a consequence, the output of the various stages of the development process are strictly regulated by domain-specific standards (like ECSS-E-ST-40C [46] on software development and ECSS-Q-ST-80C [48] on software product assurance). Moreover, the software product is subject to extensive verification and validation campaigns to ascertain its quality, that is to say to verify it performs as expected while fulfilling all *extra-functional* requirements. It is important to appreciate that the value added of the software products resides in its functional contents (what the software does). All the remaining software parts and all the development activities instead contributes to the *quality* of the final product.

Given this clarification, a reduction in the overall cost for software under a comparable complexity for the functional contents can be achieved only by producing a final product with the same level of quality with a reduced effort. Alternatively, the reduced effort necessary to achieve the same level of quality allows to keep constant the overall budget of the satellite while developing more complex functional contents.

In this context the software architecture then plays a truly crucial role, as it expresses the architectural framework that hosts the functional contents, and its underlying architectural assumptions and methodological principles are among the major contributors to the attainment of the quality of the software product. In essence, we regard the software architecture as the instrument that contributes to the realization of our goal.

The space domain, in the specific European context, is heavily influenced by the current structure of the space market that is dominated by two prime contractors: Astrium Satellites (now a business unit of EADS Astrium) and Thales Alenia Space (owned by Thales Group and Finmeccanica). The two competitors (for economic and historical reasons) adopted different concepts, methodologies and technologies with respect to on-board software development and this led to distinct ways of producing the final software product. Therefore, the reconciliation of those two worlds in terms of overall approach to the problem, methodology, architectural solutions and interoperability of products is quite hard. To confirm the extent of this diversification, at the present state of the art, a software supplier can competitively provide its services as subcontractor only in a single supply chain.

As a response to these overall situation, the European Space Agency (ESA) launched an initiative that aims at the definition and realization of a *software reference architecture*, to be used in as many ESA missions as possible.

The rationale behind this decision is to foster the convergence to a single, common and agreed architecture that would be able to ensure the needed quality to the software product and it is adopted in several ESA missions. The net outcome of such adoption would be the possibility to focus on the definition of the functional contents rather than recurrently investing unnecessary engineering effort on the quality side of the problem; furthermore it would enable prime contractors to compete on functionality and performance without recurrently investing budget on quality (which is attained by adhering to the common solution), and software suppliers to compete on both supply chains.

The novel approach shall be able to address two development models that are inherent to the domain. The first model is *incremental development*, as the on-board software is not simply a product to be released at the end of the development, but incremental releases of it are necessary during the development schedule to perform, in coordination with other satellite development

teams, additive hardware/software integration and validation activities. The second model is *iterative development*, which is determined by the fluctuation and late finalization of system and software requirements experienced by almost every project; iterations therefore risk to be destructive backtracks of design and implementation decisions.

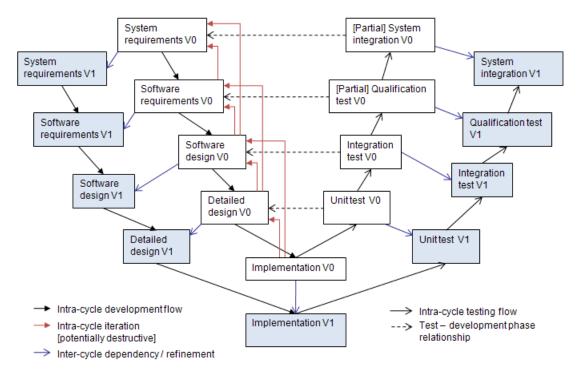

In figure 1.4 we depict an example of how the two development models coexist by extending the classical V-model development.

Figure 1.4: A classic V-model augmented to show iterative cycles and incremental development. For the sake of clarity we omitted the iterations inside the V1 iteration and the relationships between the right and left branch of the V1 iteration.

A first development iteration (termed "V0") comprises a set of sequential activities depicted on the left branch of the figure: from the creation of (a subset of the) system requirements to software requirements and so on, up to the implementation. Each activity is mirrored by the corresponding V&V activity in the right branch. During this sequence of activities, the development actors may be forced to backtrack to the previous activity to reconsider some design choices. Severe design problems may force to amend the output of even earlier phases (for example software requirements may be found infeasible during detailed design or implementation), with the obvious consequences in time and cost. The subsequent development iteration ("V1") incrementally adds contents to the system and hence all its various activities are dependent from the previous iteration. A novel approach shall demonstrate its capability of taming the destructive potential of iterative development and use instead iterations as refining or confirmative steps of the development in the context of an incremental development.

The investigation of this novel approach to the development of on-board software focuses primarily on the application to the platform software for Earth observation, science and deepspace missions, as those are the mission types for which domain experts deem it is possible to produce more easily a common recurrent solution and thus factorize the investment.

Therefore, the reference architecture initiative is currently not intended to address the software for launcher vehicles, re-entry vehicles, and rovers. Additionally, it will not address specifically software for payloads, even though the underlying principles and methodology might be applicable even in that context.

Let us now elaborate on the concept of *software architecture*, in particular on the various aspects it addresses. Subsequently, we focus on the advantages and implications of elevating a software architecture to the role of *reference architecture*.

#### **1.1** The role of the software architecture

One disconcerting situation in the software engineering practice is the informal and liberal interpretation of the concept of *software architecture*. This factual truth is patently at odds with the centrality of that concept for the discipline.

Software architecture is probably the most important concept of software engineering, yet if we were to ask a definition and explanation of it to three different software developers or software engineers, almost for sure the answers would all be different and incomplete.

The main misunderstanding is that software architecture is often liberally used as a synonym of *software design*. Software design instead is (partly) just one of the concerns addressed by the software architecture, whose important role is to govern the software and the process by which it will be built and operated. More importantly, the software architecture deals with the *principles* guiding the design and evolution of a software system. This aspect is fundamental and for sure *precedes in importance* software design, and for this reason shall not be neglected.

To confirm that the notion of software architecture is far from having a universally accepted meaning, the reader can appreciate the multitude of definitions that were given in the course of time and were gathered by a brilliant exercise of the Software Engineering Institute [128]; the "bibliographic definitions" therein can give an idea of the situation in the academic world; the "community definitions" instead are a clear indication of the plethora of interpretations spread among software practitioners. From a quick scrutiny, the reader can understand that even if we discount the poor elegance or the lack of conciseness of some of the definitions, they are not all equivalent, and some of them clearly address only a subset of the concerns of a software

architecture.

For our investigation, we elected as a reference the definition of architecture that was given in the IEEE 1471 standard [69], later adopted and approved by ISO/IEC as ISO 42010 [76], as we consider it is the best and most authoritative:

"The fundamental organization of a system embodied in its components, their relationships to each other, and to the environment, and the principles guiding its design and evolution"

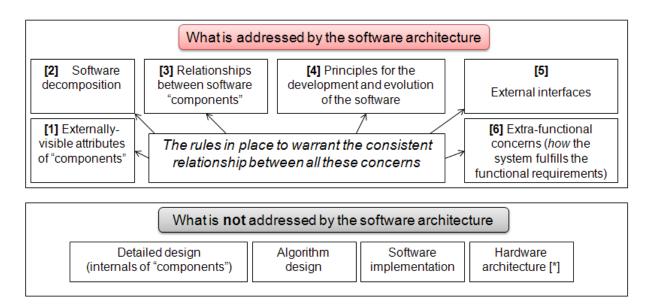

Starting from this definition we then reason on what are the concerns addressed by the software architecture:

- *Software decomposition*: the organization of the software in terms of parts, so that each single part has an own architectural cohesiveness (it addresses a single well-defined part of the problem), and interactions between parts are minimized as to reduce unnecessary dependencies (i.e. coupling), hence incidental complexity of understanding, V&V, operation and maintenance.

- *Externally visible attributes of software "components"*: the attributes of those software parts (which we call, for the moment only informally, components) that are externally visible. Those attributes represent the features or needs that are specific to the component yet can influence other parts of the software or its overall properties. The other attributes shall remain as (invisible) internal details and will not be used for the overall reasoning at the level of the software architecture;

- *Relationship between software "components"*: how components relate one another to provide services and fulfill needs;

- *Extra-functional concerns*: the software architecture is the level of reasoning where most of the extra-functional concerns are addressed;

- *External interfaces*: how the software interacts with the external environment (for example, by commanding sensors or actuators, and acknowledging external interrupts);

- *Principles for the development and evolution of the software*: a process that addresses the design of software, establishes the relevant rules for its development and provides means to perform software maintenance and evolution and dictates the supported form of reuse.

- The rules in place to warrant the consistent relationship between all the aspects above: an overall methodology that is able to consistently harmonize all these aspects; additionally, the methodology shall provide criteria to sanction if a software part can be included in the system by abiding by the principles underlying the architecture or shall be rejected as its inclusion would break the overall consistency of the software.

The latter aspect is very important. Every software has (at least implicitly) some software architecture [69, 117]. However, if we want to establish a software architecture that is supporting our goals, we have to define the methodology that underpins the development approach and warrants the consistency for all the aspects we mentioned above.

Reporting and refining an analogy used by Bran Selic during the discussion held at the FESA workshop<sup>1</sup> in April 2010, the software architecture is to the software product as a *constitution* is to a sovereign state: all the laws of the state must be compatible with the constitution, that is, they shall not violate or contradict implicitly or explicitly the fundamental principles established by the constitution and elected as the pillars of the state. Laws created by the legislative power that are incompatible with those principles are discarded after an assessment (typically performed by the supreme body of the judiciary power). This analogy is quite fascinating and, limiting exclusively to the mentioned aspect, a good representation of our context (even though extending the analogy to other aspects unfortunately makes it misleading).

The central role of the software architecture makes it fundamental to contribute to the value added of the final software product.

In fact, a poor software architecture hinders the fulfillment of functional, behavioural, extrafunctional and life-cycle requirements. Conversely, a good software architecture warrants the quality of the final product and contributes to its value added.

In order to complete the picture, reasoning by exclusion we can enumerate aspects that are not of pertinence of a software architecture, and that we can score out from the investigation.

- *Detailed design*, which is the refinement of the software decomposition performed at architectural level by providing the internal software organization of "components";

- *Algorithm design*, which is the design of the algorithmic behaviour of the software to fulfill the functional requirements;

- *Software implementation*, which is the activity to realize the implementation of the whole software.

- *Hardware architecture*, which is obviously not part of the software architecture. However we have to notice that we need to complement the software architecture with a description of the hardware, limited to the aspects that impact software and its extra-functional properties in particular: therefore we need to specify the hardware aspects relevant for communication, analysis and code generation purposes. There is no interest in complete modeling of the hardware.

Figure 1.5 recapitulates these concepts.

<sup>&</sup>lt;sup>1</sup>"Formalisms for Description And Visualization of Embedded Systems Architectures - Current State Of Practice, Needs And Research Topics" http://www.kth.se/polopoly\_fs/1.58948!EventSummary\_extended.pdf

Figure 1.5: Recapitulation of the concerns addressed by the software architecture and those outside its perimeter.

### **1.2** On the concept of reference architecture

In the previous section we highlighted the confusion around the term "software architecture". It is not surprising that also the concept of *reference architecture* does not have a commonly accepted definition.

The most referred definition of reference architecture is that of the "Rational Unified Process" (RUP) [80]: "a predefined architectural pattern, or set of patterns, possibly partially or completely instantiated, designed, and proven for use in particular business and technical contexts, together with supporting artifacts to enable their use. Often, these artifacts are harvested from previous projects."

The definition is somewhat generic, yet it includes interesting aspects. In the following we try to elaborate and refine it.

It is important to recognize the difference between a software architecture and a software reference architecture. The software reference architecture prescribes the form of the concrete software architectures for a set of systems for which it was developed. We could then say that the reference architecture is a form of "generic" software architecture, which prescribes the founding principles, the underlying methodology and the architectural practices that were recognized by the domain stakeholders as the best solution to the construction of a certain class of software systems. The architecture of one target software system can be considered as a sort

of "instantiation" to the specific system needs of the software reference architecture.

The other interesting part of the RUP definition is that a reference architecture is "proven for use in particular business and technical contexts". This underlines:

- 1. the importance of the elicitation of the industrial needs and technical requirements that define the reference architecture;

- 2. the need of a *validation in use* and of an *evaluation* of the reference architecture. The validation demonstrates empirically that the software architecture(s) resulting from the application of the software reference architecture to concrete systems covers and fulfills satisfactorily all the industrial needs that originated it. The evaluation ascertains the goodness of the reference architecture by analyzing to what extent it satisfies the industrial needs. The evaluation can be facilitated by using appropriate methodological support. The most known evaluation method for software architectures is the Architecture Tradeoff Analysis Method (ATAM) [54, 11]; it would require some adaptation to apply it to the level of reference architecture.

There are very different kinds of reference architectures, and an interesting work by Angelov et al. [6] can help us understand our stance. In that article, the authors define a set of dimensions that help the definition of a classification for reference architectures. They single out a set of dimensions and sub-dimension that characterize the definition and application of a reference architecture.

Their dimensions are: *context*, *goal* and *design*. The context dimension discriminates: *where* the reference architecture will be used (i.e. within a single organization or multiple organizations), *who* defines it (i.e. user organizations, software organizations, research centers, standardization bodies), *when* is it defined (*preliminary* reference architectures are defined before an implementation of it exists, or *classical* when experience on the application on the target class of systems has already been acquired).

The goal dimension describes the main usage of the reference architecture: it may be a *standardization* of existing software architectures, or a *facilitation* for the design of concrete architectures (by providing guidelines, methodologies and patterns of the software architecture).

The design dimension describes the main design choices of the reference architecture: *what* is described (components, interfaces, protocols, guidelines, etc...), the *abstraction level* of the description (concrete, semi-concrete, or abstract; corresponding according to the authors to decreasing levels of dependence with technological and implementation decisions) and the level of formality of the description (*informal, semi-formal, formal*).

We now anticipate how the software reference architecture of our investigation would be classified according to this criteria. For the context dimension: (i) it is defined for use *by* and *across* multiple organizations (a single architecture instantiation for a satellite project may be

shared by a software prime and all its software suppliers); (ii) it is defined by a working group comprised of staff members of the major stakeholders, supported by members of the academic world; (iii) it is a *preliminary* architecture, even though part of the stakeholders (the prime contractors) already have experience and their solutions for the *present* target systems.

For the goal dimension: (i) at the present time the reference architecture is at the *facilitation* stage. If the investigation demonstrates the feasibility and goodness of fit of the reference architecture, the stakeholders may be favourable to its standardization.

For the design dimension, the reference architecture: (i) describes the rules for the specification of components, interfaces, interactions, extra-functional attributes and how they relate to the analysis theories of interest, a design flow for the creation of the design entities, and the complete methodological background for the consistent relationship of all those aspects; (ii) can be considered as *semi-concrete* as it will abstract as much as possible from technological aspects and implementation solutions (that can be chosen or adapted by the users, provided that there is complete adherence with the methodological background), yet the space of the solutions from the technological point of view is constrained in some aspects (for example, the choice of the execution platform); (iii) it will adopt a semi-formal description language so that the resulting architecture description is predictive (i.e. it is possible to reason on and analyze its extra-functional concerns).

#### **1.3** Contribution and structure of this thesis

The PhD project of the author was launched in January 2008 with the intent of supporting the ESA initiative with a scientifically-based contribution toward the definition, realization and evaluation of the software reference architecture. Since October 2008, the author started to collaborate with ESA in the scope of the Networking/Partnering Initiative (NPI) of the Directorate of "Technical and Quality Management" at ESTEC, the research center of ESA at Noordwijk, The Netherlands. The author was able to work directly at ESTEC, as a visiting student in the "Software Systems Engineering" section.

The collaboration with ESA allowed the collaboration of the author with the SAVOIR-FAIRE working group, comprised of staff members of ESA, the French and German space agencies (CNES and DLR), software prime contractors (EADS Astrium, Thales Alenia Space, Swedish Space Corporation), the main software suppliers (Scisys, GMV, Terma, Space Systems Finland), and tool vendors (Intecs).

The relationship with SAVOIR-FAIRE was fundamental to better understand the industrial needs and requirements of the European stakeholders, submit proposals on the various topics of the investigation to their scrutiny, and receive valuable feedback to drive the investigation.

The structure of this thesis is as follows.

In chapter 2, we elaborate on the various industrial needs that motivate the adoption of a single common software architecture. We show that some of those needs are common to all software domains; a few others are in common or similar to the needs of other high-integrity real-time domains; finally, a sizeable subset of them are specific to the European space domain. We motivate why the software reference architecture is an adequate solution capable of fulfilling all such needs.

The elicitation and consolidation of these needs was initially performed thanks to focused discussions with ESA staff members. The task was then facilitated and its results greatly improved thanks to short visits performed at the premises of EADS Astrium (Toulouse) and Thales Alenia Space (Cannes), which allowed the author to have interesting and valuable discussions with managers and engineering teams of the prime contractors.

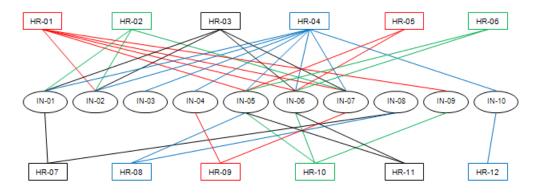

Those discussions led to the derivation and formalization of a set of high-level requirements that are to be considered as the technical objectives to be achieved by the software reference architecture. These high-level requirements were subject to thorough discussion in the SAVOIR-FAIRE working group, which provided feedback and recommendations for their finalization.

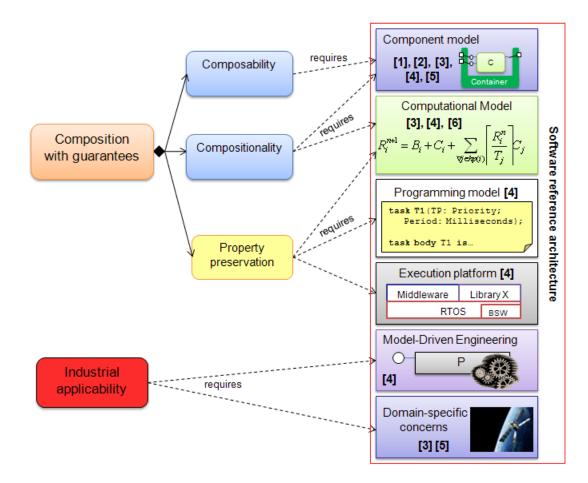

The approach which we propose to base the software reference architecture on aims at two overarching goals: *composability* and *compositionality*. According to Sifakis [127]:

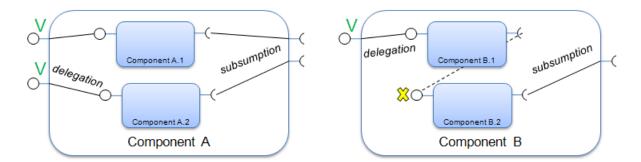

- composability rules "allow inferring that a component's properties are not affected when its structure is modified. That is, if components gl{U1,...,Un} and gl'{U1,...,Un} respectively satisfy the properties P and P', then the component gl ⊕ gl'{U1,...,Un} satisfies P ∧ P'. Composability means stability of component properties across integration.";

- compositionality rules "allow inferring global system properties from component properties. That is, if for i = 1, ..., n a set of components  $U_i$  satisfy properties  $P_i$ , then it is possible to guarantee that the component  $gl(U_1, ..., U_n)$  satisfies some property  $gl'(U_1, ..., U_n)$ where gl' is an operator on properties depending on gl".

Those definitions are in wide use in the real-time and formal methods communities. In contrast, the software engineering and component-based software engineering communities use the same two terms with other meanings; curiously, what the former terms "compositionality", it is referred as "composability" in the latter (see for example the work by Crnkovic et al. [39]). For our investigation, we adopt the definitions by Sifakis, narrowed down as follows:

- *composability*, that is achieved when the properties (needs and obligations) of individual components are preserved on component composition and deployment on the target system;

- *compositionality*, that is achieved when the properties of the system as a whole can be derived (economically and conclusively) as a function of the the properties of its constituting components.

As regards composability, we stress the nature of properties (needs and obligations) and explicitly require that they are preserved both at component composition (at design time) and on deployment on the target. For compositionality, we note that we are interested in composability functions that provide conclusive results in any circumstance on the properties of interest.

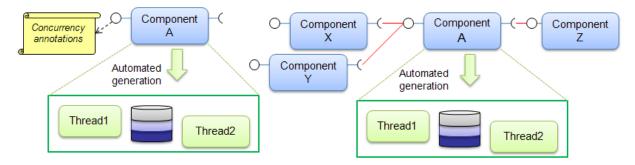

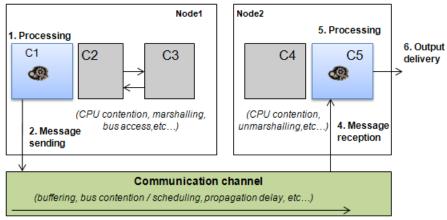

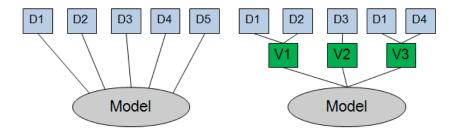

Figure 1.6: An example of composable property: the number of threads and protected objects generated in response to the extra-functional annotations to the component interface.

3. Message transmission

Figure 1.7: An example of compositional property: end-to-end latency.

An example of composable property in our approach is the number of threads and protected objects generated per component, which depends exclusively on the extra-functional annotations to the component interface (see fig. 1.6). The number is invariant across component composition (which and how many other components are later connected to the component of interest).

An example of compositional property is the end-to-end latency in the delivery of an output at the end of a chain of activities (see fig. 1.7). The latency (i.e., the worst-case response time

of the end-to-end chain of activities) is compositional if it is possible to calculate it exclusively from the properties explicitly exposed by components (and those describing the communication channel).

Composability and compositionality shall be consistently achieved by a development methodology that exhibits the crucial property of *composition with guarantees* [138], which may be regarded as a form of composability and compositionality that can be assured by static analysis, guaranteed throughout implementation, and actively preserved at run time.

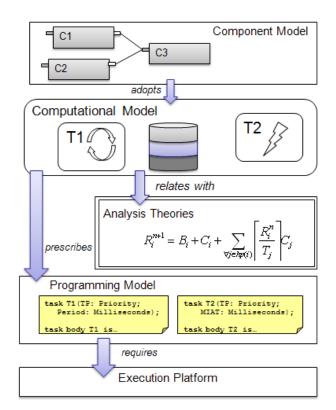

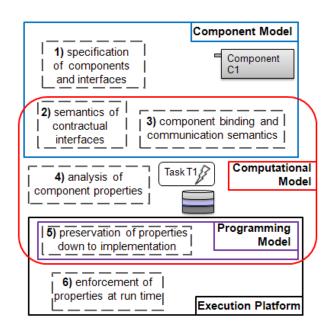

The goal of composition with guarantees can be achieved with an approach centered on four constituents [108]:

- 1. a *component model*, to design the software as a composition of individually verifiable and reusable software units;

- 2. a *computational model*, to relate the design entities of the component model, their execution needs and their extra-functional properties for concurrency, time and space, to a framework of analysis techniques which ensures that the architectural description is statically analyzable in the dimensions of interest;

- 3. a *programming model*, which consists in a tailored subset of a programming language and a set of code archetypes, and is used to ensure that the implementation of the design entities conforms with the semantics, the assumptions and the constraints of the computational model;

- 4. a *conforming execution platform*, which is in charge of preserving at run time the system and software properties asserted by static analysis and it is able to notify and react to possible violations of them.

Compositionality is earned at the level of the *computational model* and *component model*, as it depends on the adopted body of analysis theories as well as how the architectural entities in use relate to them. Composability is earned at the level of the *component model*. Composability and compositionality, augmented with *property preservation* [137] (i.e. preservation of the analyzed properties at run time), lead to the achievement of composition with guarantees.

In order to increase the industrial applicability of the approach, and as a response to industrial needs of the space domain, we further include in the formulation of the software reference architecture: (a) a development process centered on Model-Driven Engineering [120]; (b) the provisions for domain-specific aspects, which complement the approach, yet are consistent to all its underlying principles.

Figure 1.8 recapitulates the goals of our approach and the constituents that we need for their achievements. We also depict in square brackets the concerns of the software architecture addressed by each constituent (cf. fig. 1.5).

Figure 1.8: The goals we set for our investigation and the constituents of the software reference architecture that permit their achievement. We depict in square brackets the concerns of the software architecture dealt by each constituent (cf. fig. 1.5

We conclude chapter 2 by examining the state of the art of similar approaches, to elaborate on the concepts that inspired our work and on the improvements that we introduce with respect to existing approaches.

The central contribution of the thesis is the definition of a software reference architecture which provides a comprehensive approach to fulfill the industrial needs we gathered in the first part of our investigation.

Not all the constituents of the software reference architecture were investigated for the first time in this thesis. The nature, feasibility and fitness of constituents 2, 3 and 4, in the context of a

Model-Driven Engineering approach [120], were already investigated also by the author during the ASSERT project (FP6 IST-004033 2004-8), prior to the launch of the PhD project. The results of ASSERT [7, 24, 106, 21], including the feedback received by the industrial partners of the space domain participating to that project, provided considerable confidence on the overall goodness of the approach we are proposing, and encouraged us to base the foundation of the software reference architecture on the same principles.

In order to complete the 4-constituent foundation to the proposed software reference architecture, in the core of the PhD project we focused on the design of a component model for use in on-board software [109]. The inclusion of the component model in the approach permits to achieve the goal of composability and compositionality in the form that we termed *composition with guarantees*.

Investigated in the ASSERT project [2004-2008]

Figure 1.9: Our proposed approach. In the picture we depict the constituents already investigated in the scope of the ASSERT project. We depict in square brackets the concerns of the software architecture dealt by each constituent (cf. fig. 1.5). The contribution of the PhD to the approach is also highlighted.

In figure 1.9 we depict the constituents of the software reference architecture; the concerns of a software architecture that are addressed by each of the four central constituents of the approach and by MDE and domain-specific aspects; and we clarify the contribution of this PhD thesis.

In chapter 3 we elaborate on the most important elements on which the component model is centered: (i) rigorous separation of concerns, achieved during software design with the support for design views (following and specializing ISO 42010/IEEE 1471 [76, 69]) and by careful allocation of concerns to the the various software entities of the approach; (ii) the support for specification and model-based analysis of extra-functional properties; (iii) the inclusion in the component model of space-specific concerns while consciously trying to keep them separate from domain-neutral concerns.

Additionally we clarify and refine the notion of property preservation that was initially investigated during ASSERT.

In the same chapter we also discuss a concrete incarnation of the proposed component model, experimentally built around a domain-specific language, a graphical editor and associated design environment for schedulability analysis and code generation.

Thanks to our involvement in the CHESS project (ARTEMIS JU grant nr. 216682, 2009-2012) [138, 105] we are also able to compare the results of this effort with an alternative implementation of the same component model based on the extension of a subset of the UML MARTE profile [99].

We highlight the current achievements of the two implementation strands, the different difficulties encountered in the implementation and the remaining challenges ahead of us.

In chapter 4, we provide a qualitative evaluation of the software reference architecture, by elaborating on the technological feasibility of the approach, discussing on the coverage of the requirements by our solution and reflecting on the goodness of the approach with the help of a case study and the preliminary feedback provided by industrial partners.

Finally, in chapter 5, we draw some conclusions on the current results of the initiative and discuss the current and future activities related to the software reference architecture.

### Chapter 2

## A software reference architecture for on-board space applications

In this chapter we elaborate on the proposed approach to the definition and realization of a software reference architecture for on-board space applications.

Initially, in section 2.1 we discuss the industrial needs elicited with interactions and focused discussions with the main stakeholders of the European space domain.

Later on in section 2.2, we describe the technical requirements that represents the baseline that has to be fulfilled by the a novel development approach that aims at fulfilling all the industrial needs elicited by the stakeholders. We report on the activities that permitted the derivation of those requirements, the criteria that were used to assess the difficulty of realization and establish their importance.

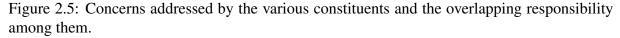

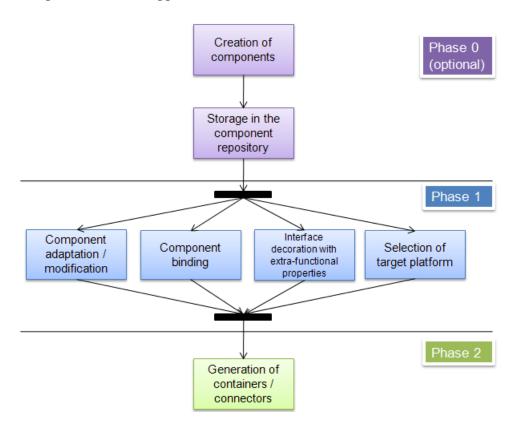

In section 2.3 we describe the overall approach we propose for the software reference architecture. As we argument therein, the software reference architecture shall be centered on four fundamental constituents: (i) a component model; (ii) a computational model; (iii) a programming model; and (iv) a conforming execution platform. We describe in details the role of each of the constituents, and for each of them we report and discuss the most similar approaches in the state of the art. Finally, we elaborate on the interactions and possible overlapping of the four constituents and we motivate why all of them are necessary to fulfill the technical requirements for the software reference architecture.

Finally in section 2.4 we examine the state of the art of similar approaches, to elaborate on the concepts that inspired our work and on the improvements that we introduce with respect to existing approaches.

#### 2.1 Industrial needs of the European space domain

The ESA initiative for the definition of a software reference architecture is a harmonization of methodologies and technologies around the Agency charter (and its *geographic return* policy, presented later on in this section), seeking to earn the different benefits relevant for the involved stakeholders: ESA itself as the procurement agency, software prime contractors and software suppliers.

One of the first goals of the doctoral thesis consisted in gathering all the industrial needs set as strategical goals by ESA, or related to the other stakeholders, in order to have a clear picture of all the strategic and economic objectives to fulfill for future ESA missions. The finalization of these goals is important as the understanding of their impact is fundamental to drive the investigation towards a good solution.

The industrial needs were gathered out of discussions with staff members of ESA and discussed in various meetings of the SAVOIR-FAIRE working group, comprised of staff members of national space agencies (CNES [France], and DLR [Germany]), software prime contractors (EADS Astrium [France], Thales Alenia Space [France], Swedish Space Corporation [Sweden]) and the main software suppliers (Scisys [United Kingdom], GMV [Spain], Terma [Denmark], Space Systems Finland [Finland]) and tool vendors (Intecs [Italy]).

In table 2.1 we present an outline of the industrial needs. We also complemented each industrial need with a personal evaluation of its nature: some industrial needs in fact can be considered common to all software domains including mainstream or enterprise software (albeit the context, hence the possible solutions, are completely different); a subset of the industrial needs are common or very similar to those of comparable high-integrity real-time domains; finally, a sizeable subset of them instead is specific to the space domain in general and the European context in particular.

In the reminder of the section we provide a detailed description of the industrial needs and we comment on their relationships and their collective impact.

| ID    | Industrial need                                                   | Туре  |

|-------|-------------------------------------------------------------------|-------|

| IN-01 | Reduced development schedule                                      | С     |

| IN-02 | Higher cost-effectiveness of software development                 | С     |

| IN-03 | Support for incremental and parallel software development         | С     |

| IN-04 | Multi-team development and product policy                         | HI/DS |

| IN-05 | Quality of the software product                                   | HI    |