Alma Mater Studiorum Università di Bologna

# Binary Neural Networks At The Edge

*Presentata da* Dott.Ing. Lorenzo Vorabbi Supervisore Prof. Davide Maltoni *Co-supervisore* Ph.D. Stefano Santi

Dottorato di Ricerca in Computer Science and Engineering Ciclo XXXVI

> *Coordinatore Dottorato* Prof. Ilaria Bartolini

Settore Concorsuale 09/H1 Settore Scientifico Disciplinare ING-INF/05 SISTEMI DI ELABORAZIONE DELLE INFORMAZIONI

ESAME FINALE ANNO 2024

## Abstract

#### **Binary Neural Networks at the Edge**

#### Lorenzo Vorabbi

In the last decade, Artificial Intelligence demonstrated to achieve great advancements in many areas such as (but not limited to) Computer Vision, Natural Language Processing, Reinforcement Learning, and Autonomous Driving. Nowadays, AI systems potentially overcome the intelligence observed in human beings as the ambition of developing AI models with cognitive, learning, and problem-solving abilities is the driving force in AI research and development. Achieving this goal would imply the creation of highly sophisticated AI systems capable of generalizing knowledge, learning from diverse data sources, and exhibiting a level of adaptability and creativity comparable to human intelligence. Most of the performance improvements obtained by AI systems have been reached by increasing the complexity and memory footprint of the models, leading to solutions whose deployment is most of the time prevented on resource-constrained hardware. Even though many works in literature addressed the problem of compressing and reducing the computational overhead of a neural network, a lot of effort is still required to successfully deploy a complex AI solution on tiny/embedded devices.

Additionally, current AI solutions achieve poor performances at adapting incrementally to new data. This phenomenon, named *catastrophic forgetting*, happens naturally in Deep Learning architectures when a classical training algorithm, such as backpropagation, is applied. By learning through a sequence of *experiences* incrementally, where the model cannot access old training data, the model knowledge falls resulting in the forgetting of past samples.

During my Industrial PhD activity, pursued at University of Bologna and Datalogic, I investigated the optimization of neural network inference and continual learning on edge devices, because they are central to guarantee good performances of the edge and tiny devices produced by Datalogic. AI technology could considerably empower the capabilities of such devices but many hardware and processing constraints have to be satisfied. Many challenges persist to deploy models on embedded systems that can solve complex tasks and the main activity of this work was aimed to simplify and reduce the computational flow and the memory bottlenecks, while preserving the original performance accuracy of the model. This research focused on the exploitation of extremely low-bit-width models, adopting the Binary Neural Networks, which use only 1-bit to represent weights and activations. Binary networks are naturally suitable to be accommodated on low-power devices as they replace the expensive multiply-and-accumulate operation with bit-wise arithmetic, which is more efficient.

Furthermore, we proposed novel techniques to allow the incremental learning of a binary neural network directly on-device, as this is the standard scenario of many real-world applications. On-device learning remains a formidable challenge, especially when dealing with devices that have limited computational capabilities and models that use low bit-width representation like binary neural networks. This thesis will focus on the applicative aspects that embrace continual learning approaches and binary neural networks to allow the deployment of practical deep learning applications in real-world scenarios.

## Outline

Chapter 1 introduces the concepts and motivations of this research activity, outlining the requirements and constraints of real-world applications addressed by Datalogic devices. In particular, it points out the pros and cons of a deep learning approach introducing some of the state-of-the-art techniques adopted to compact and compress a deep learning model.

Chapter 2 describes the Binary Neural Networks by considering several aspects that have driven the advancements and improvements of 1-bit networks. This chapter represents the background knowledge of methods and approaches used for binary networks adopted in the next chapters.

Chapter 3 describes our contributions to the improvement and simplification of data flow of binary networks. In particular, it introduces a technique that reduces the bitwidth of binary convolution outputs to 8-bit, removing floating-point computation. Additionally, this chapter describes a method to binarize the input layer of a binary network more efficiently than state-of-the-art solutions.

Chapter 4 considers the on-device learning (using a continual learning approach) use case applied to binary neural networks. The literature lacks of contributions that consider the combination of these topics and this chapter details the solutions we proposed to continuously train binary networks adopting *ad-hoc* quantization schemes.

Chapter 5 discusses some real-world applications that can be improved by adopting the techniques presented in this thesis. In particular, it shows the advantages achievable by adopting binary neural networks for the detection and localization of two-dimensional codes, which is a processing-intensive task with a challenging latency constraint. Additionally, it reports also two continual learning scenarios that need to continuously adapt a binary model on-device.

Eventually, conclusions and future challenges are discussed in Chapter 6.

## Acknowledgements

First of all, I would like to thank Datalogic, the CEO Valentina Volta, the Chairman Ing. Romano Volta, and the executives who gave me the fantastic opportunity to pursue a PhD. Within this academic journey, I got to explore in depth the machine learning and deep learning fields that could significantly contribute to the improvement of Datalogic products.

A special thanks goes to my advisor prof. Davide Maltoni for his guidance and support during my PhD, spent during the Covid pandemic period, which complicated human relationships.

I would like to take this opportunity to thank my co-advisor Stefano Santi, that is much more than this. He is a friend, colleague, manager, mentor, and professor who remarkably contributed to the overall development of my technical skills, being a guide and a landmark for my activity within Datalogic. Without his support, patience, and driving path, I would not be able to reach the planned goals. He taught me *how to* solve problems and shape the mindset for applied research tasks and I will be forever grateful to him. He is one of the best scientists that I have ever met.

A special thanks goes to my colleagues at SmartCity-BioLab Guido Borghi and Lorenzo Pellegrini who supported me. In particular, for the Friday discussions held with Guido covering both research stuff and other general topics. I cannot miss my current manager Maurizio, who supported my research activity.

Eventually, I would like to dedicate this work to my family: Simona, Giulio, Giovanni, and Licia (from the oldest to the youngest). The caring grandparents (Cristina, Rodolfo, Daniela, and Riccardo) supported us by taking care of our kids every time we needed it and to my brothers Matteo (who undertook this path before me) and Giacomo. Particularly, without Simona I could not afford the PhD opportunity. I remember well how many night hours (after midnight) I spent doing research, while she was taking care of our little children, feeding them, and being close to them during their *active* night hours. Especially at the beginning of the PhD, she encouraged and supported me when things were hard and the desired goals were too far to be considered feasible. I cannot forget my kids, I hope that the effort and difficulty requested by this research activity could be an inspiration for them later in life.

# Contents

| Ał  | ostrac  | t       |                                                         | iii  |

|-----|---------|---------|---------------------------------------------------------|------|

| Lis | st of F | igures  |                                                         | ix   |

| Lis | st of ٦ | Tables  |                                                         | xiii |

| 1   |         | oductio |                                                         | 1    |

|     | 1.1     | -       | Learning (DL)                                           |      |

|     |         | 1.1.1   | Convolutional Neural Networks (CNNs)                    |      |

|     |         | 1.1.2   | Training versus Inference                               |      |

|     |         | 1.1.3   | Optimization techniques to reduce computation           |      |

|     |         |         | Quantization                                            |      |

|     |         |         | Pruning                                                 |      |

|     | 1.2     |         | gic Use Cases                                           |      |

|     |         | 1.2.1   | Open Issues in DNNs                                     |      |

|     |         | 1.2.2   | Contributions of this thesis                            | . 12 |

| 2   | Bina    | ry Neu  | ral Networks (BNNs)                                     | 15   |

|     | 2.1     | Forwa   | rd Propagation                                          | . 16 |

|     | 2.2     | Backw   | ard Propagation                                         | . 18 |

|     | 2.3     | Binary  | Neural Network Optimization                             | . 20 |

|     |         | 2.3.1   | Quantization Error Minimization                         |      |

|     |         |         | Scaling Factor                                          | . 20 |

|     |         |         | Quantization Function                                   | . 21 |

|     |         |         | Activations/weights distribution                        | . 23 |

|     |         | 2.3.2   | Loss Function Improvement                               | . 23 |

|     |         | 2.3.3   | Gradient Approximation                                  | . 24 |

|     |         | 2.3.4   | Network Topology Structure                              | . 25 |

|     |         | 2.3.5   | Tricks and strategy for training Binary Neural Networks | . 28 |

| 3   | Imp     | roving  | BNN Inference                                           | 31   |

|     | 3.1     | 0       | izing data-flow in Binary Neural Networks               | . 31 |

|     |         | 3.1.1   | Data-Flow Optimizations                                 |      |

|     |         |         | Two-stage Clipping                                      |      |

|     |         |         | Batch Normalization Optimization                        |      |

|     |         |         | Binary Direct Convolution optimization on ARM           | . 38 |

|     |         | 3.1.2   | Experimental Results                                    | . 39 |

|     |         |         | Efficiency Analysis                                     |      |

|     |         |         | Accuracy Analysis                                       |      |

|     |         | 3.1.3   | Final Remarks on Data-Flow Optimization                 |      |

|     | 3.2     | Input l | Layer Binarization with bit-plane Encoding              | . 45 |

|     |         | 3.2.1   | Method                                                  |      |

|    |       | 3.2.2  | Implementation Details                                       | 49 |

|----|-------|--------|--------------------------------------------------------------|----|

|    |       | 3.2.3  | Experimental Results                                         | 53 |

|    |       | 3.2.4  | Final Remarks on Input Binarization using bit-plane Encoding | 54 |

| 4  | Con   |        | Learning with Binary Neural Networks                         | 55 |

|    | 4.1   | Binary | y Neural Networks and CWR*                                   | 55 |

|    |       | 4.1.1  | Continual Learning                                           | 56 |

|    |       | 4.1.2  | Method                                                       | 57 |

|    |       |        | Gradients Computation                                        | 57 |

|    |       |        | Quantization Strategy                                        | 59 |

|    |       | 4.1.3  | Experiments                                                  | 60 |

|    |       | 4.1.4  | Results and Remarks                                          | 63 |

|    | 4.2   | Enabl  | ing On-device Continual Learning with Binary Neural Networks |    |

|    |       | and L  | atent Replay                                                 | 67 |

|    |       | 4.2.1  | Method                                                       | 68 |

|    |       |        | Continual Learning with Latent Replays                       | 68 |

|    |       |        | Quantization of activations and weights                      | 69 |

|    |       |        | Quantized Backpropagation                                    | 70 |

|    |       | 4.2.2  | Experiments                                                  | 72 |

|    |       |        | Accuracy comparison                                          | 72 |

|    |       |        | Reducing Storage in Latent Replay                            | 76 |

|    |       |        | Splitting $q_b$ in $q_b^{bin}$ and $q_b^{non-bin}$           | 76 |

|    |       |        | Efficiency Evaluation                                        | 77 |

|    |       | 4.2.3  | Final Remarks                                                | 77 |

| 5  |       |        | y Results on Datalogic Use Cases                             | 81 |

|    | 5.1   |        | natrix Detection                                             | 81 |

|    | 5.2   |        | d Symbols Localization and Classification                    | 84 |

|    | 5.3   | Produ  | ce Classification                                            | 86 |

| 6  | Con   |        | ns and Future Challenges                                     | 91 |

|    | 6.1   |        | ency of Binary Neural Networks                               | 91 |

|    | 6.2   | Conti  | nual Learning at the Edge                                    | 92 |

| Bi | bliog | raphy  |                                                              | 95 |

# **List of Figures**

| 1.1 | Example of feature extraction using deep neural networks. The fea-<br>ture maps computed by each convolutional layer contain features of |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | increased complexity as data goes deeper into the network                                                                                | 3  |

| 1.2 | Uniform quantization function. Real values of <i>r</i> are mapped into low-                                                              | -  |

|     | precision quantized values (marked with red dots) $Q(r)$ . The distance                                                                  |    |

|     | between quantized red values is constant in uniform quantization.                                                                        |    |

|     | The green plot represents the quantization function that converts val-                                                                   |    |

|     | ues from floating-point to integer representation (the corresponding                                                                     |    |

|     | red dots).                                                                                                                               | 6  |

| 1.3 | On the left it is illustrated an example of symmetric quantization (us-                                                                  | Ū  |

| 1.0 | ing a restricted range of $[-127, +127]$ ) that preserves zero representa-                                                               |    |

|     | tion. On the right an example of asymmetric quantization.                                                                                | 6  |

| 1.4 | Flow chart of the steps required to perform Quantization. Aware Train-                                                                   | 0  |

| 1.1 | ing (on the left) and Post-Training Quantization (on the right).                                                                         | 7  |

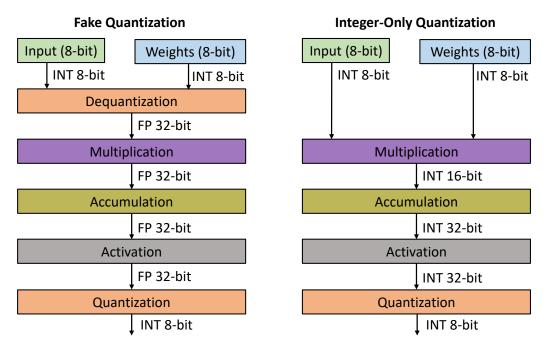

| 1.5 | Comparison of the steps required in simulated quantization (Left) and                                                                    | ,  |

| 1.0 | integer-only quantization (Right).                                                                                                       | 8  |

| 1.6 | Example of devices produced by Datalogic.                                                                                                | 10 |

| 1.0 | Example of devices produced by Educogies                                                                                                 | 10 |

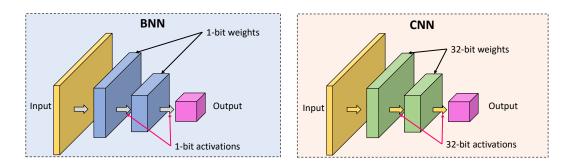

| 2.1 | BNN vs. CNN                                                                                                                              | 16 |

| 2.2 | Internal steps of a 32-bit CNN neuron compared to a naive BNN cell                                                                       | 16 |

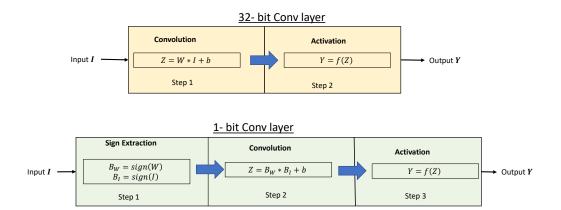

| 2.3 | Naive BNN forward propagation compared to 32-bit CNN. Popcount                                                                           |    |

|     | operation refers to Equation 2.6                                                                                                         | 17 |

| 2.4 | Backward pass approximation as suggested in [58].                                                                                        | 19 |

| 2.5 | BNN optimization solutions.                                                                                                              | 21 |

| 2.6 | Shapes of forward and backward passes.                                                                                                   |    |

| 2.7 | Shapes of forward and backward passes.                                                                                                   |    |

| 2.8 | Representative BNN block structures.                                                                                                     | 28 |

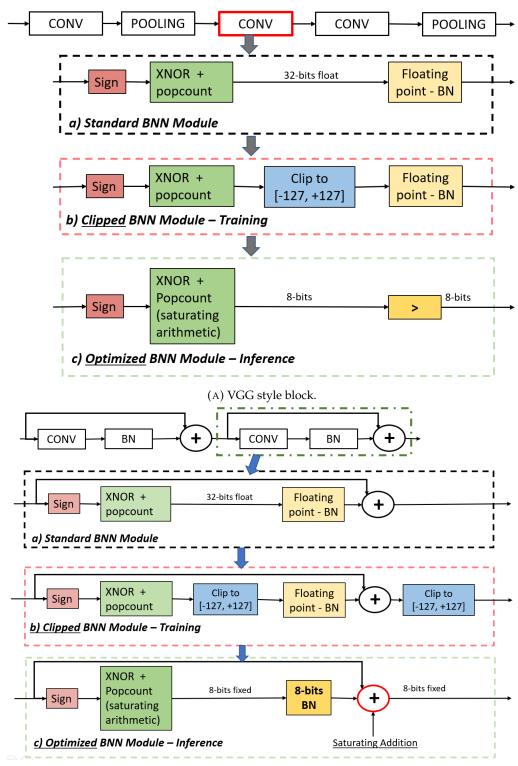

| 3.1 | a) Standard BNN blocks are used in [113] and [88]. b) BNN block with                                                                     |    |

| 5.1 | output convolution clipping used during training. c) Optimized BNN                                                                       |    |

|     | block adopted during inference. Popcount operation is performed us-                                                                      |    |

|     | ing saturation arithmetic to keep the data width to 8 bits at inference                                                                  |    |

|     | time. BN is replaced by a comparison in case a, while in b BN is 8-bit                                                                   |    |

|     |                                                                                                                                          | 33 |

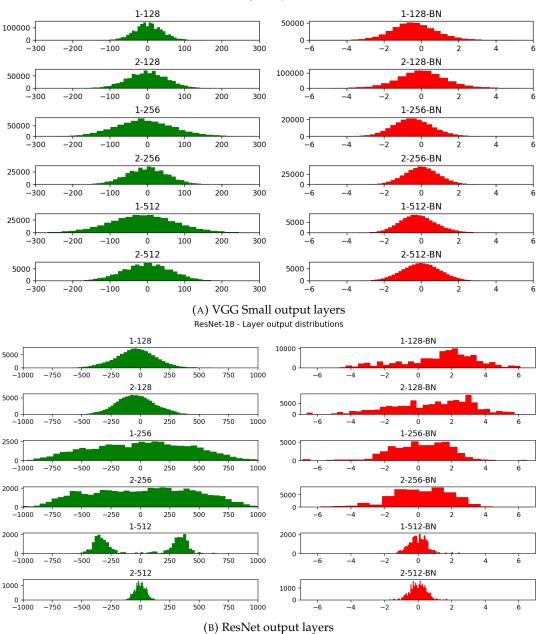

| 3.2 | Example of output distributions after binary convolution. a, refers to                                                                   | 55 |

| 0.2 | a VGG style network while b to a ResNet architecture. Green shows                                                                        |    |

|     | the distribution before the BN layer and red afterward.                                                                                  | 34 |

| 3.3 | a): 8-bit symmetric quantization procedure that reserves fractional/in-                                                                  | 51 |

| 0.0 | teger bits based on the range of input 32-bit floating point values. <b>b</b> ):                                                         |    |

|     | implementation of the BN layer with 8-bit quantization using an in-                                                                      |    |

|     |                                                                                                                                          | 26 |

|     | ternal 16-bit representation to preserve accuracy.                                                                                       | 36 |

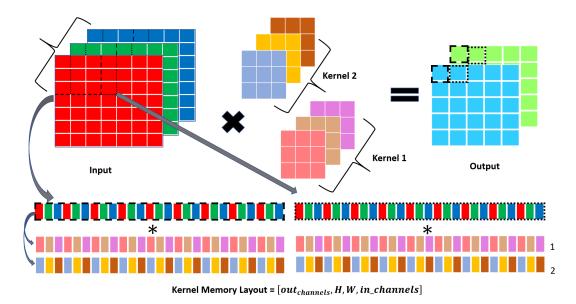

| 3.4  | The $7 \times 7$ input image with 3 different channels (denoted by color) is                                         |            |

|------|----------------------------------------------------------------------------------------------------------------------|------------|

|      | convolved with two separate kernels to obtain a $5 \times 5$ output with two                                         |            |

|      | output channels. To better exploit the SIMD 128-bit registers a differ-                                              | 1          |

| 0 5  | ent memory layout for kernel is devised: $[out_{channels}, H_{filter}, W_{filter}, in_{cha}]$                        | nnels]. 38 |

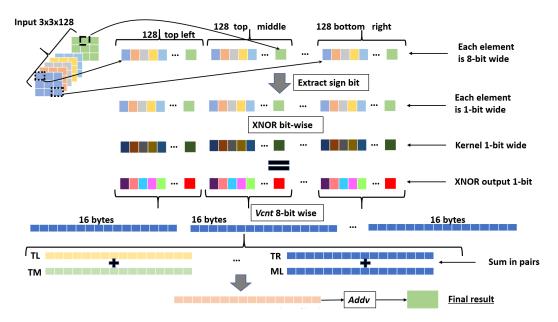

| 3.5  | The $3 \times 3 \times 128$ input patch is convolved (XNOR + popcount) with                                          |            |

|      | one kernel through the Extract sign bit, XNOR, and then popcount                                                     |            |

|      | operations. Popcount is performed using <i>vcnt</i> , summing in pairs the                                           |            |

|      | <i>vcnt</i> output, and the last step uses the <i>addv</i> operation. TL (top left), $TL(t) = LL(t) = LL(t)$         |            |

|      | TM (top middle), TR (top right), and ML (middle left) indicate the                                                   | 20         |

| 26   | position of elements inside the $3 \times 3$ patch.                                                                  | 39         |

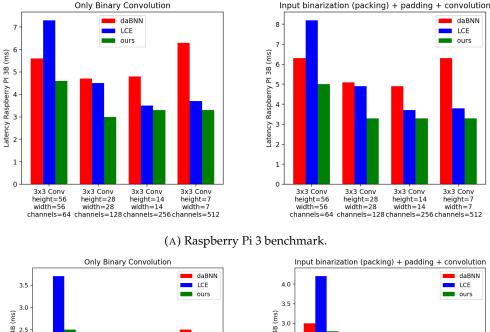

| 3.6  | Latency evaluation of our method compared to DaBNN and LCE on<br>Beauthering $\text{Di}(2B(a))$ and $4B(b)$ deviates | 40         |

| 27   | Raspberry Pi 3B (a) and 4B (b) devices.                                                                              | 40         |

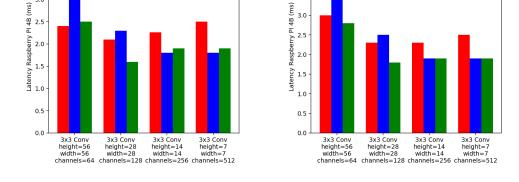

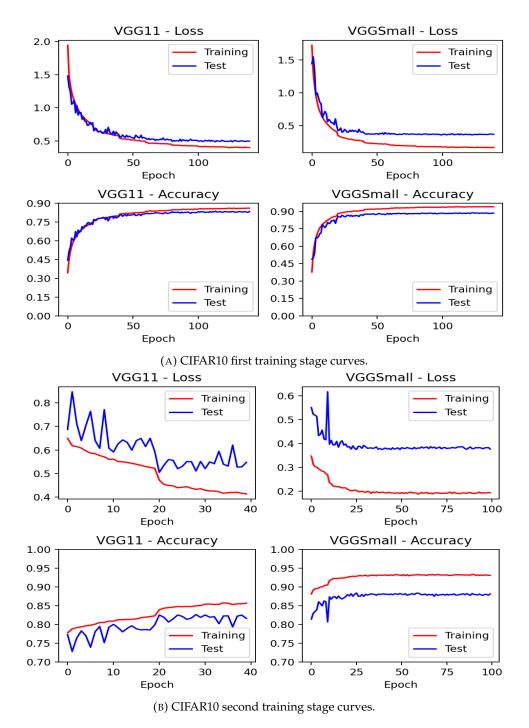

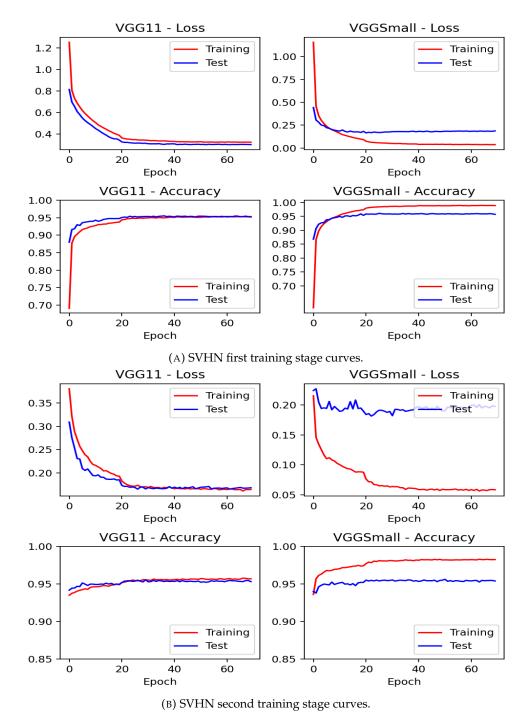

| 3.7  | Training loss and testing accuracy curves for VGG11 and VGGSmall                                                     | 40         |

| 20   | on CIFAR10 of the first and second training stages                                                                   | 42         |

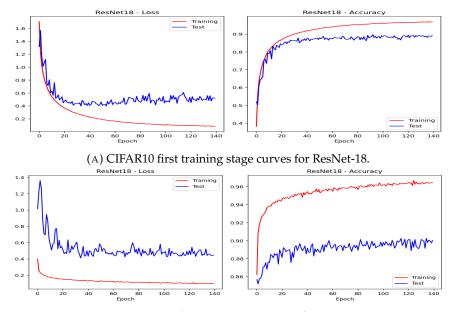

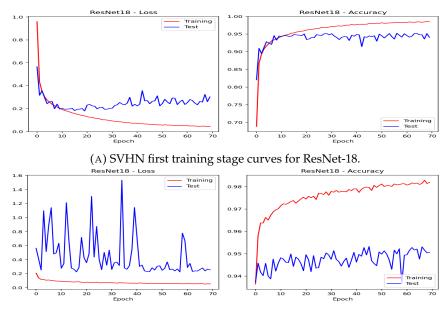

| 3.8  | Training loss and testing accuracy curves for VGG11 and VGGSmall<br>on SVHN of the first and second training stages  | 43         |

| 3.9  | on SVHN of the first and second training stages                                                                      | 43         |

| 5.9  | of the first and second training stages.                                                                             | 44         |

| 3 10 | Training loss and testing accuracy curves for ResNet-18 on SVHN of                                                   | 44         |

| 5.10 | the first and second training stages.                                                                                | 44         |

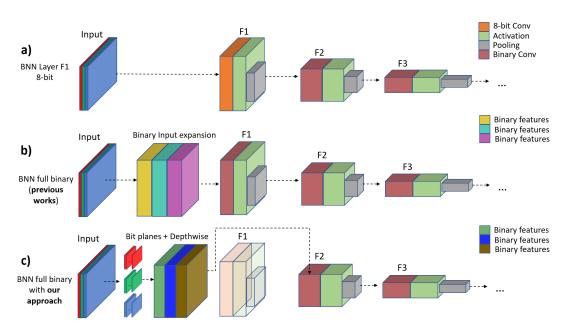

| 3 11 | ( <i>a</i> ) Standard scenario of BNNs where the first convolutional layer is                                        | TT         |

| 5.11 | not binarized; weights and inputs are used in 8-bit/floating-point rep-                                              |            |

|      | resentation. (b) Typical approach of the works that binarized the first                                              |            |

|      | layer $F_1$ incrementing the number of input channels; in this case, the                                             |            |

|      | input expansion is actually an additional layer. (c) Our approach,                                                   |            |

|      | where depth-wise convolutions are applied to input bit-planes and                                                    |            |

|      | the resulting maps can replace the $F_1$ layer, producing a more com-                                                |            |

|      | pact model.                                                                                                          | 46         |

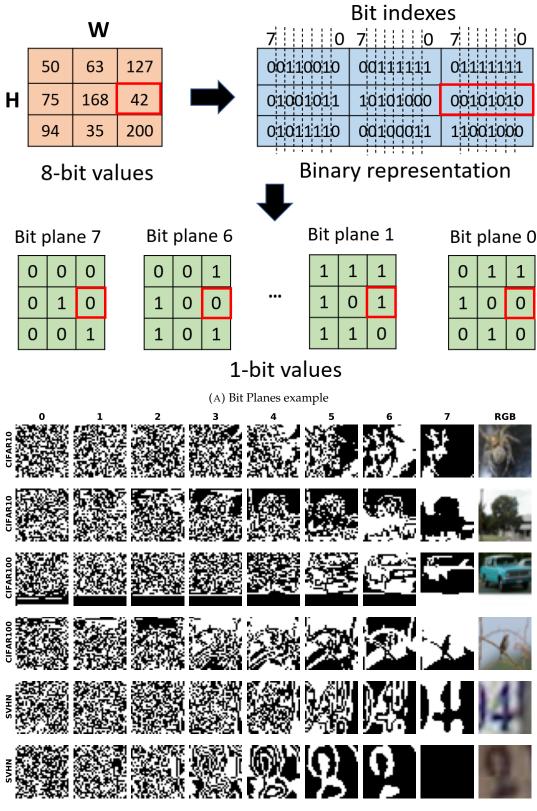

| 3.12 | a Example of bit plane representation for a $3 \times 3$ 8-bit image. b Im-                                          |            |

|      | age representation in bit planes. Each column refers to a bit index                                                  |            |

|      | extracted from the image; for representation purposes, bit 1 is con-                                                 |            |

|      | verted to 255 while bit 0 remains 0. In this example, all bit planes                                                 |            |

|      | refer to channel G of RGB images.                                                                                    | 48         |

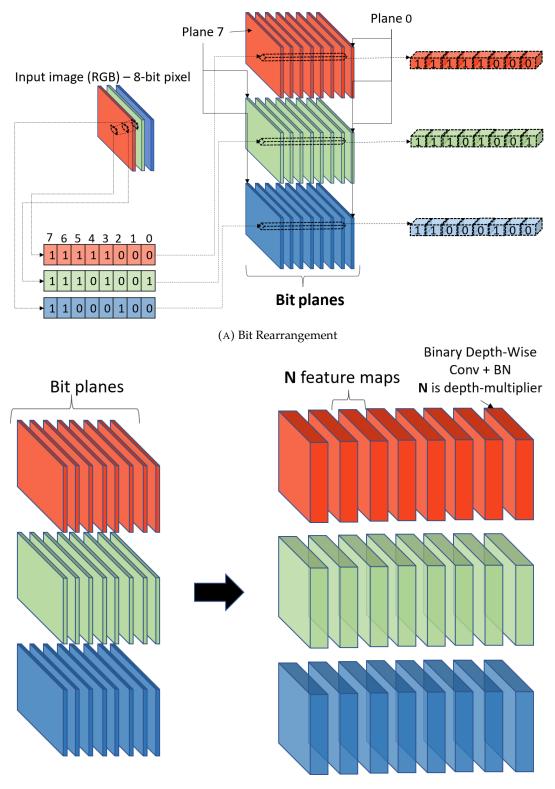

| 3.13 | Binarization process of input layer. a shows the rearrangement phase                                                 |            |

|      | that extracts, for each bit position of the encoded pixel a bit plane. b                                             |            |

|      | shows the binary depth-convolution block applied to each bit plane;                                                  |            |

|      | the depth multiplier (N) is a hyperparameter and it is dataset and                                                   |            |

|      | model dependent.                                                                                                     | 50         |

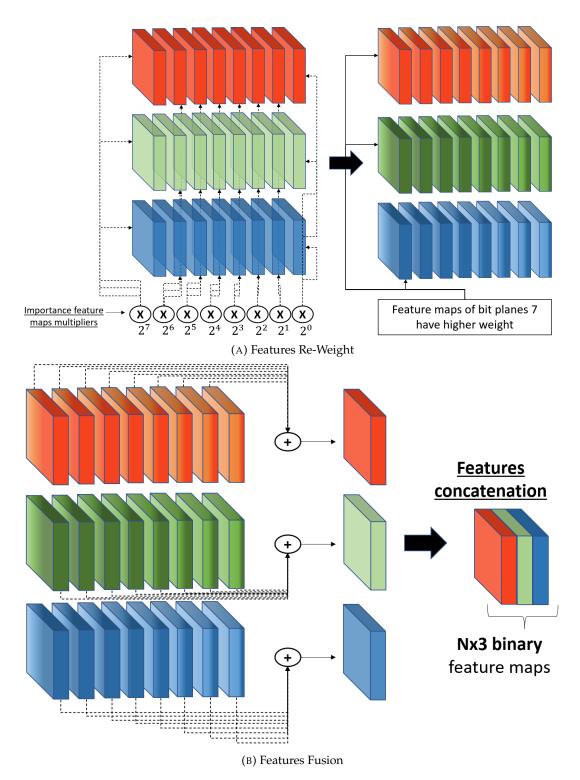

| 3.14 | Binarization process of input layer. a shows how to weigh differ-                                                    |            |

|      | ently feature maps extracted from different bit planes; maps related                                                 |            |

|      | to the most significant bits receive a higher multiplication factor. In                                              |            |

|      | b, the feature maps related to the same 8-bit input channel are fused                                                |            |

|      | together through an addition.                                                                                        | 51         |

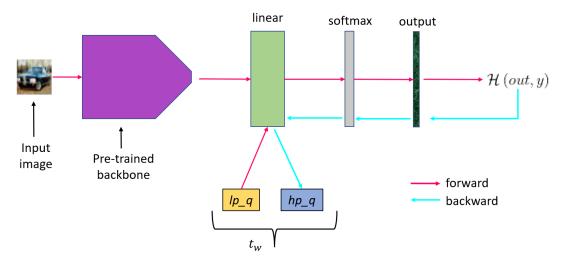

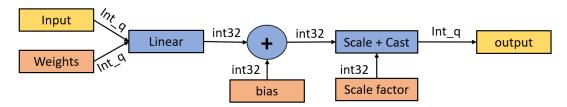

| 4.1  | Double quantization scheme that uses a different quantization level                                                  |            |

|      | for weights/activations used in forward and backward pass.                                                           | 59         |

| 4.2  | Quantization scheme adopted using $q$ bits for weights and activations.                                              | 60         |

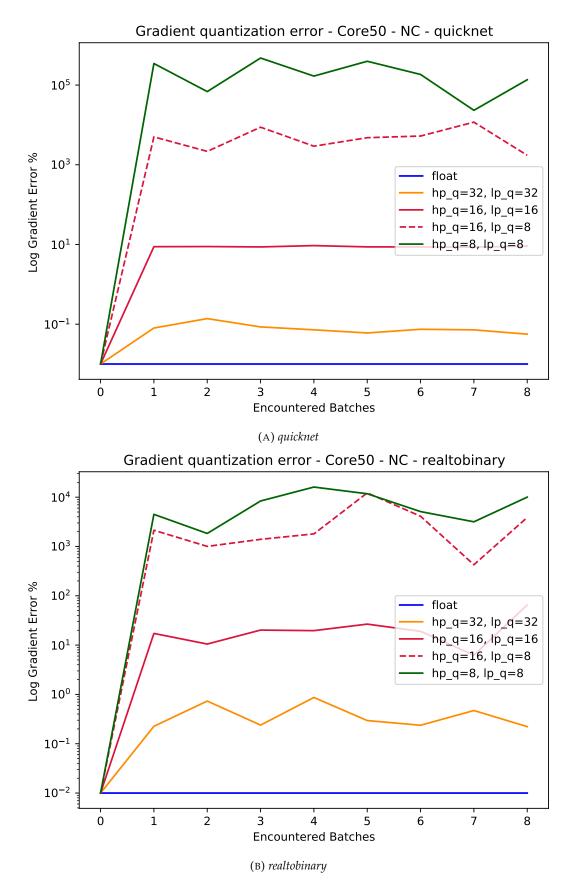

| 4.3  | Accumulation of gradient quantization errors (Mean Absolute Error                                                    |            |

|      | in percentage using a logarithmic scale) between quantized and floating-                                             |            |

|      | point versions for each experience. During the first experience the                                                  |            |

|      | gradient computation is always executed in floating-point.                                                           | 61         |

x

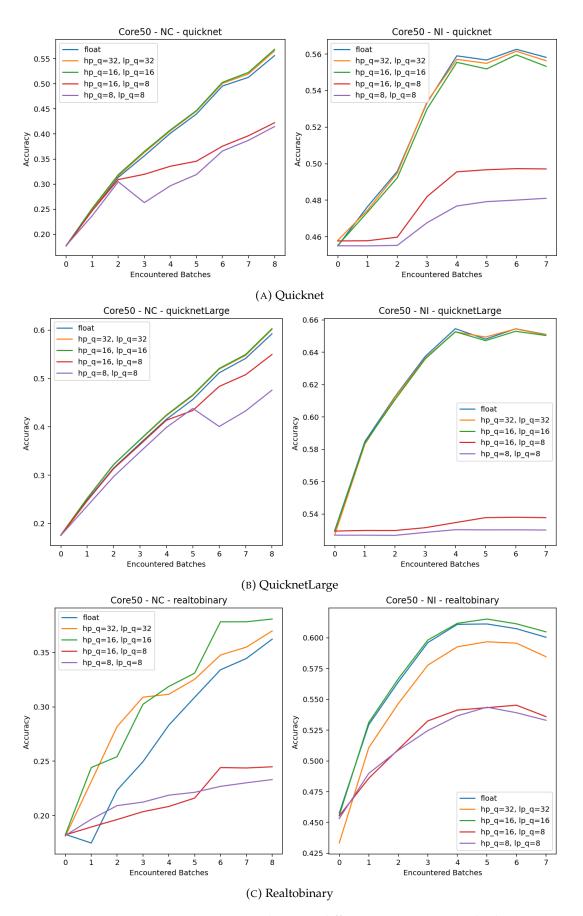

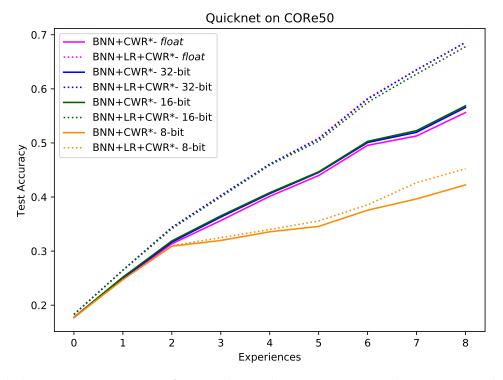

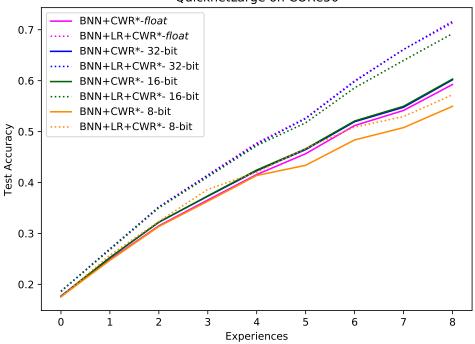

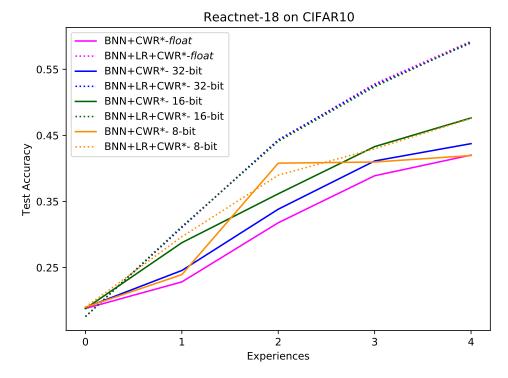

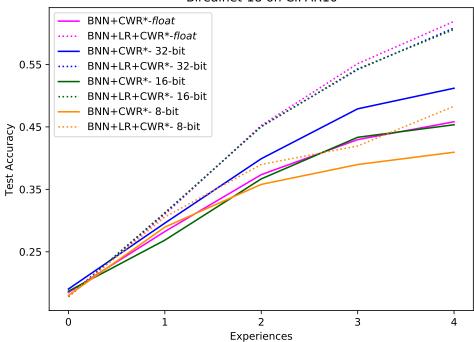

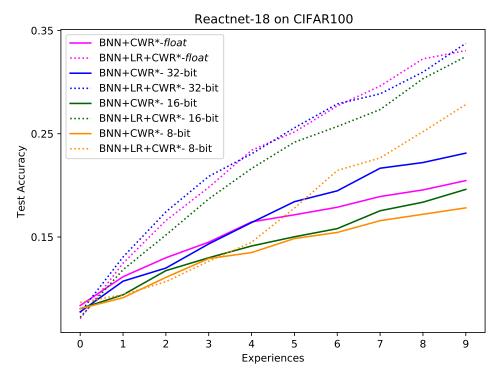

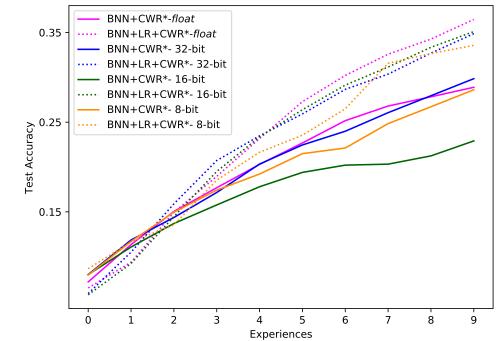

| 4.4  | CORe50 accuracy results using different quantization methods                 | 64 |

|------|------------------------------------------------------------------------------|----|

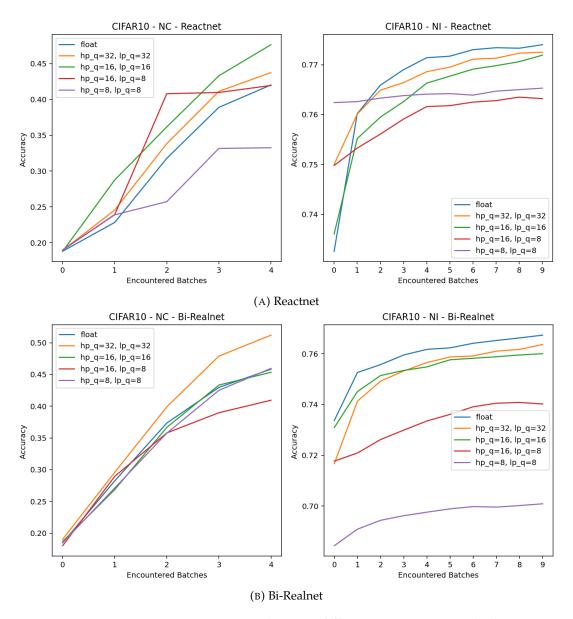

| 4.5  | CIFAR10 accuracy results using different quantization methods                | 65 |

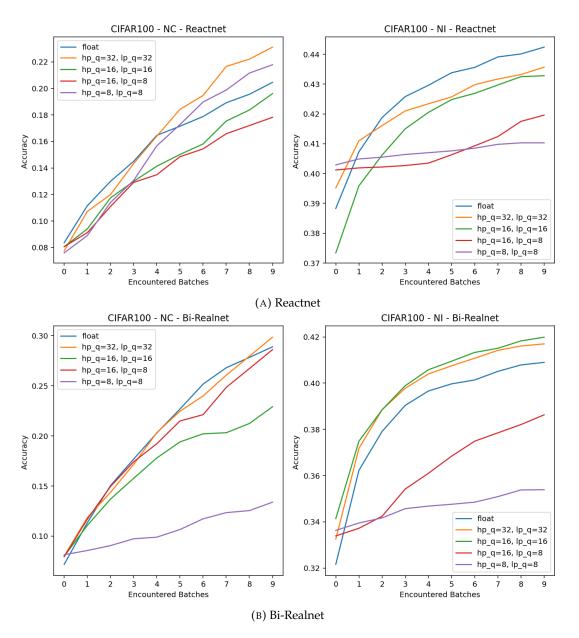

| 4.6  | CIFAR100 accuracy results using different quantization methods               | 66 |

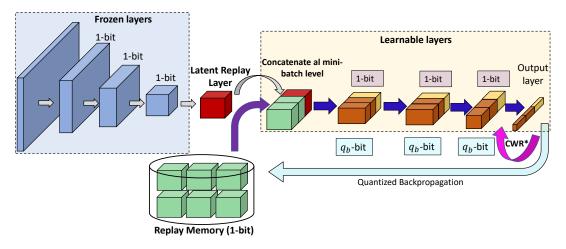

| 4.7  | Continual Learning with latent replay memory. When using a BNN               |    |

|      | the activations stored in the replay memory can be quantized to 1-bit        | 67 |

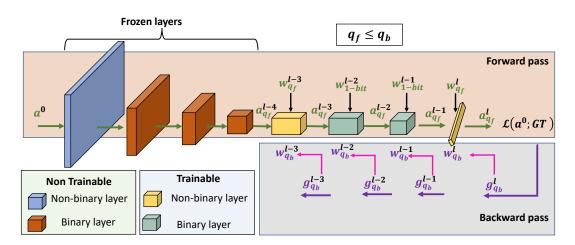

| 4.8  | Quantization scheme that uses a different number of bitwidth for for-        |    |

|      | ward $(q_f)$ and backward $(q_b)$ pass. Usually, trainable non-binary lay-   |    |

|      | ers are Batch Normalization [60], Addition and Concatenation layers.         | 69 |

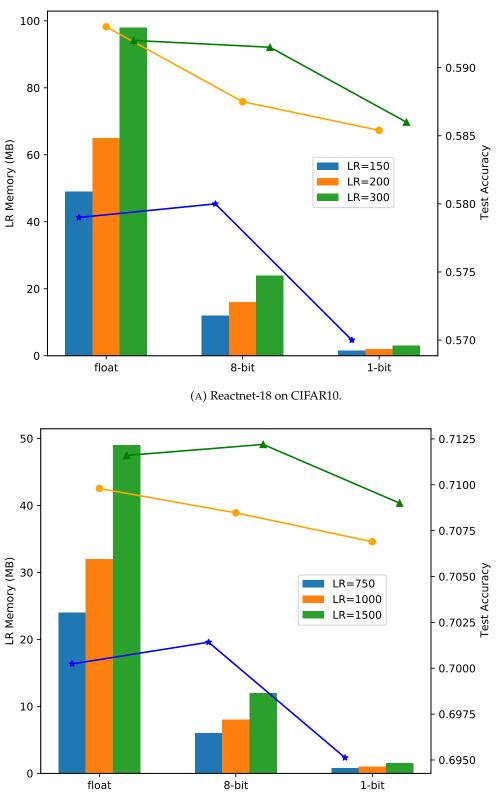

| 4.12 | LR memory requirement using different quantization levels and cor-           |    |

|      | responding test set accuracy on CIFAR10 (a) and CORe50 (b). We con-          |    |

|      | sidered 15, 20 and 30 elements for each class inside LR; for case (a) we     |    |

|      | adopted Reactnet-18 model while in (b) we used Quicknet.                     | 79 |

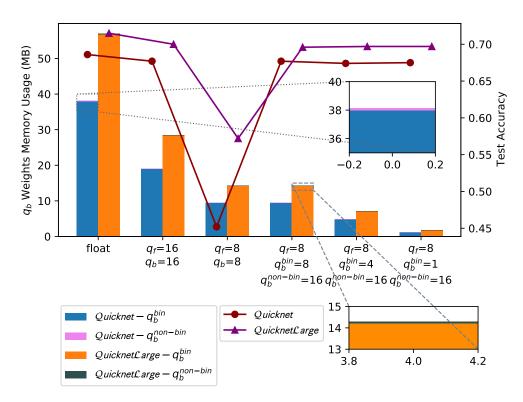

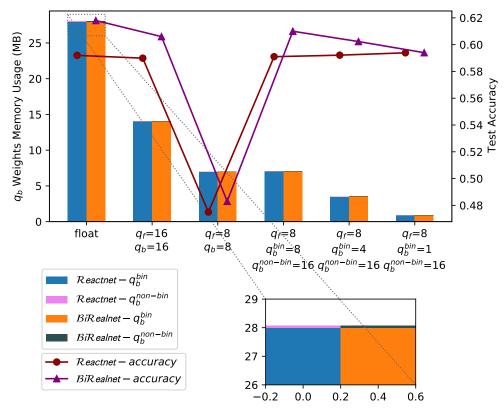

| 4.13 |                                                                              |    |

|      | ward layer on CORe50 (a) and CIFAR10 (b)                                     | 80 |

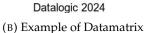

| 5.1  | Examples of 1D and 2D codes. Figure 5.1a represents a <i>linear</i> barcode, |    |

|      | where the red segment indicates the bars and spaces relative to the          |    |

|      | letter <i>D</i> . Figure 5.1b shows an example of datamatrix symbology. The  |    |

|      | red elle represents the finder pattern of Datamatrix.                        | 81 |

| 5.2  | Examples of Datamatrix codes used to train our proprietary BNN               |    |

|      | model.                                                                       | 83 |

| 5.3  | Examples of Hazmat classes supported by our proprietary BNN model            |    |

|      | used for localization and classification tasks.                              | 84 |

| 5.4  | Example of a highly flammable Hazard symbol.                                 | 85 |

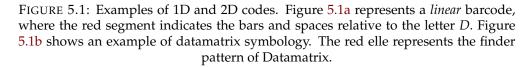

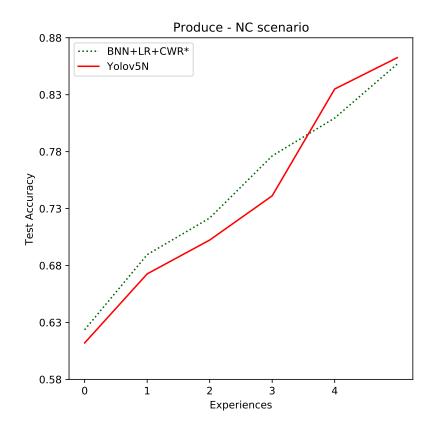

| 5.5  | Accuracy comparison of our custom BNN based on the method BNN+LR             |    |

|      | (Section 4.2.2) with a Yolov5N 8-bit quantized model.                        |    |

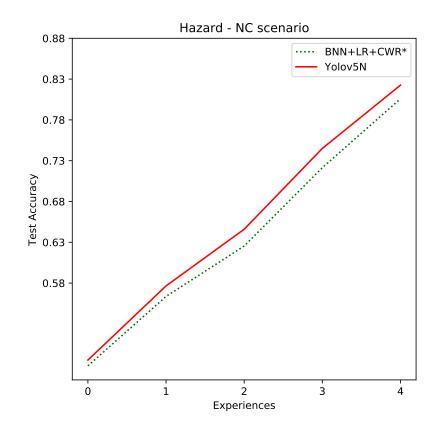

| 5.6  | Examples of a weight-scale used for produce recognition                      | 87 |

| 5.7  | Examples of fruits and vegetables used to train our proprietary BNN          |    |

|      | model used for the classification task.                                      |    |

| 5.8  | Accuracy comparison of our custom BNN based on the method BNN+LR             |    |

|      | (Section 4.2.2) with a Yolov5N 8-bit quantized model                         | 89 |

# **List of Tables**

| 2.1 | BNN XNOR operations                                                                                                                                                                                                                                                                                                                                                                                       | 17 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Accuracy comparison (top1) of our method with SOTA on CIFAR10 and SVHN.                                                                                                                                                                                                                                                                                                                                   | 41 |

| 3.2 | Accuracy comparison of our method with SOTA on ImageNet                                                                                                                                                                                                                                                                                                                                                   | 41 |

| 3.3 | Comparison of the first layer MACs required by our method with re-<br>spect to the state-of-the-art solutions. Input data has a shape $H \times W \times C$ ( $32 \times 32 \times 3$ ) and a precision of M bits; in this example, the<br>first convolutional layer has $F_1 = (128)$ filters with size $F \times F$ (3). The<br>expansion channels is $K = 32$ for methods [31, 159]. The depthwise     | TI |

|     | multiplier of our method can be chosen as $N_1 = \left  \frac{F_1}{C} \right  = 42$ . We con-                                                                                                                                                                                                                                                                                                             |    |

|     | ducted our experiments using also a lower value, $\vec{N}_2 = 32$ instead of $N_1$ and only 4 bits of input pixels. <i>P</i> represents the number of bit                                                                                                                                                                                                                                                 |    |

|     | planes extracted by step 3.13a                                                                                                                                                                                                                                                                                                                                                                            | 49 |

| 3.4 | Top1 accuracy (%) results of test set on CIFAR10. In the first part we report the result of the first test scenario (standard conditions); in the second half, the results achieved in the second scenario (reducing the                                                                                                                                                                                  | =0 |

|     | MACs of binarization of input layer)                                                                                                                                                                                                                                                                                                                                                                      | 53 |

| 3.5 | Top1 accuracy (%) results of test set on SVHN.                                                                                                                                                                                                                                                                                                                                                            | 53 |

| 3.6 | Top1 accuracy (%) results of test set on CIFAR100.                                                                                                                                                                                                                                                                                                                                                        | 54 |

| 4.1 | The table represents a comparison of memory usage (# parameters) for different BNN models. With <i>B</i> we report the number of binary weights that can be updated during back-propagation; with <i>NB</i> the number of non-binary weights. The choice of latent replay (LR) level is discussed in Section 4.2.2. It is worth noting that the largest part of memory weights is used by binary weights. | 70 |

| 4.2 | Efficiency comparison of our method implemented on two different<br>embedded boards, <i>i.e.</i> Raspberry Pi 3B and 4B, using Mobilenetv2<br>and Quicknet model. As shown, our solution achieves up to $2.2 \times$                                                                                                                                                                                      |    |

|     | speedup on the same platform.                                                                                                                                                                                                                                                                                                                                                                             | 77 |

| 5.1 | Acuracy and speed-up comparison of our custom BNN model with<br>a SOTA model (Yolov5 Nano) on our proprietary Datamatrix dataset<br>measured on a Raspberry Pi 3B                                                                                                                                                                                                                                         | 82 |

## Chapter 1

# Introduction

The success of Deep Neural Networks (DNNs) in various high-impact applications over the past decade has been remarkable. These applications include object classification [20], speech recognition [43], computer vision [72], natural language processing [135], self-supervised learning [12], reinforcement learning [99], robotics [79], autonomous driving [27], games [126], and sustainable artificial intelligence [94].

However, the increasing size of state-of-the-art neural networks has led to significant challenges in terms of storage and computation requirements. For example, GPT-3, a leading model for natural language processing, contains a massive 175 billion parameters, resulting in a huge training cost. Training such models is only feasible through extensive parallelization, requiring thousands of GPU units. This presents significant financial and environmental implications, as the training procedure of GPT-3 alone costs approximately 12 million for a single instance of the model. Even pioneer neural network architectures ([72, 50]) pose great challenges due to their large parameter counts, making them impractical for deployment on resource-constrained platforms such as embedded devices, mobile phones, or smallscale robotic platforms.

To address these challenges, several studies focused on techniques for reducing the size, inference cost, and training cost of large-scale DNNs without sacrificing performance. These techniques include quantization [146, 113], knowledge distillation [55, 106], neural architecture search [87] (NAS), low-rank compression, and weight pruning [48], among others. These methods aim to make DNNs more practical and efficient for deployment on various platforms.

Furthermore, each application field requires a certain level of adaptability over time that neural networks have to fulfill because the real world is complex and changes constantly. The ability of a neural network model to adapt to new data collected over time is usually referred to as *incremental learning* or *continual learning* (CL). The main obstacle that limits the continuous adaptability of the models even nowadays is a phenomenon known as *catastrophic forgetting*. Catastrophic forgetting occurs when a model is trained incrementally and leads to poor performance accuracy over samples seen in the past.

### 1.1 Deep Learning (DL)

The success of neural networks took over 50 years to materialize because deep networks required three foundational technologies to become viable: large sets of training data, effective techniques to learn parameters, and high-speed hardware to make the duration of training feasible. Before ImageNet [119], there simply were not large enough public datasets to support deep networks. However, the large size of ImageNet introduced other problems, one of which was how to compute optimal parameters given so many training images. Traditional solvers that directly compute parameters based on the entire dataset were too computationally inefficient to scale to ImageNet proportions. Fortunately, by adopting the Stochastic Gradient Descent (SGD) technique, it is possible to iteratively adapt network parameters to minimize the loss function. SGD operates on small batches of random samples at a time and computes updates of a network's parameters via gradient calculation that reduces error on that batch. When run on a large dataset for many epochs, the parameters slowly improve and the loss descends to a local minimum. Unfortunately, training a network using SGD often requires hundreds of epochs and, when each epoch consists of processing a million images, the prospect of training and adjusting a deep network becomes prohibitive, and would likely be completely infeasible on a CPU. Since 2007, Nvidia released CUDA, allowing the training of the neural networks directly on GPUs, that massively parallelize computation and provide a huge speedup of the training time. Since AlexNet [72], deep neural networks (DNNs) have proliferated quickly and today dominate most machine learning applications across various domains such as computer vision, natural language processing, and signal processing.

Deep learning is usually referred to as neural networks having more than three layers, i.e., more than one hidden layer. Nowadays, DNNs are built around the concept of constructing a hierarchy of hundreds, or even thousands of layers. The deep structure can learn high-level features and generalize better than shallower neural networks. The layers placed at the early stages of the model can be interpreted as low-level feature extractors, such as lines and edges. In subsequent layers, these features are combined into higher-level features until the last layer which aggregates all previous information to predict the final output of the network (e.g. classification of an object in the scene). Some of the key aspects that contributed to the popularity and widespread adoption of deep learning are listed below:

- **High-dimensional learning**. In contrast to classical techniques that often rely on manually engineered features, hard to generalize even across similar tasks, Deep Learning can capture and learn representations that better generalize. DL can learn directly from high-dimensional space of data without any human intervention or intermediate step of dimension reduction. This feature is crucial in real-world applications, such as computer vision tasks.

- End-to-end training. The primary goal of DL is to minimize a loss function representing the distance between the network output and the expected result. This is implemented through an iterative procedure that uses the gradient information to descend towards a loss function minimum. This process, where the gradient of the loss function is passed back across all layers of the network is referred to as *backpropagation*. Many variations of this technique have been proposed but the core idea remains substantially unaltered.

- **Data eager**. A key concept in DL is that the performance of a model is closely connected to the quantity of data available for training. Adding more training data is often more beneficial than investing time in designing new learning techniques. The availability of data (that covers adequately the input variations) usually constitutes a key factor for the achievement of good performance accuracy.

#### 1.1.1 Convolutional Neural Networks (CNNs)

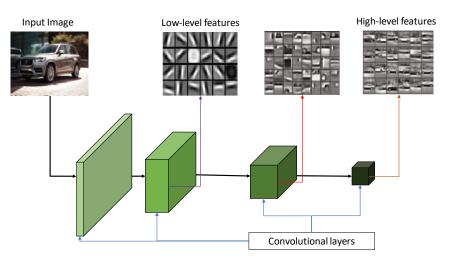

FIGURE 1.1: Example of feature extraction using deep neural networks. The feature maps computed by each convolutional layer contain features of increased complexity as data goes deeper into the network.

Convolutional neural networks emerged from studying the brain's visual cortex, and they have been used in image recognition since the eighties. The widespread adoption of CNNs in computer vision tasks is intrinsically connected to visual processing, as the concept of applying a "sliding window" fits many application scenarios, such as digits recognition [75]. In the last years, the increase in computational power and the amount of training data available significantly pushed the research on CNNs [38, 39, 118, 51], which are nowadays a fundamental building block in a visual recognition system. CNNs are a special type of DNNs that are composed of multiple convolutional layers. In such networks, each layer produces a higher level of abstraction of its input data, called *feature map*. The feature maps extracted by each convolutional layer go from low to high level as data go deeper into the network, as shown in Figure 1.1. Compared to more traditional multi-layer perceptrons, CNNs extract useful information by sliding a kernel of weights (learned at training time and shared for all input neurons) on the input data. In a convolutional layer, the neurons are not connected to every single input neuron, but only to those that belong to the *receptive field*, i.e. are local w.r.t. the considered neuron. The number of kernel parameters is related only to the kernel and input/output channel sizes, reducing the total number of weights. In 2012, Krizhevsky et al. [71] published a ground-breaking work, CNN-based, by outperforming conventional methods on a large-scale dataset, such as Imagenet. The authors showed that a convolutional neural network was able to learn useful representations on such high-dimensional data by adopting a simple training technique. Convolutional layers are particularly suited for computer vision applications as they exploit local information to extract useful information. Nowadays, CNNs are widely employed in a multitude of applications and thousands of papers have been written on this topic.

#### 1.1.2 Training versus Inference

The distinction between training and inference in the context of neural networks is crucial as they require different computational needs. Specifically, training involves refining the network's learnable parameters through an iterative process on a dataset (often large), taking several hours to multiple days to achieve the desired accuracy.

This phase is resource-intensive and the hardware used usually involves the usage of expensive GPUs (or TPUs) that require high power consumption. Most of the time, to train very huge and deep models, training is performed in the cloud or powerful local servers.

In contrast, once trained, the network is used for inference, which can happen both in the cloud or at the edge. In real-world applications, it is often desirable to execute DNN inference directly at the edge near the sensors. Edge processing allows to maintain privacy of data avoiding the costs related to the cloud. The focus on optimizing inference, as opposed to training, is justified by several factors. While training is a one-time cost, inference scales with the usage of the application. As a result, the optimization of inference speed and model size is of paramount importance, especially given the widespread use of trained models in various applications.

The focus on inference optimization is driven by the need for efficient and scalable deployment of models in real-world scenarios. The techniques presented in this thesis are primarily addressed to improve the speed and reduce the model size during inference. An efficient inference pass opens the door to accommodate CNNs on tiny embedded devices and also enables the chance to apply an incremental learning approach directly on devices. On-device learning represents a fundamental milestone for DNNs as it allows to automatically adapt a model to new data, directly at the edge, which would foster significantly the DNNs spread. Unfortunately, training at the edge imposes severe limitations and constraints that must be addressed to reach a good compromise between hardware resource utilization and processing load, as reported in Chapter 4.

#### 1.1.3 Optimization techniques to reduce computation

As introduced in previous sections, DNNs can reach human-level capabilities but at the cost of significant computational complexity. To reach these superior performances, in recent years, DNNs stacked thousands of layers resulting in longer and complex training procedures. As a result, such deep models are difficult to deploy on embedded platforms that cannot provide enough memory and computation resources. Luckily, as reported by Sze et al. [129], deep neural networks are overparameterized, i.e. redundant neurons are present, and by removing the neurons that do not contribute to an improvement in the accuracy of results it is possible to reduce model complexity. To achieve efficient and accurate DNNs it is necessary to rethink the design, training, and deployments of DNNs. A large part of the literature addressed previous limitations by improving the efficiency of DNNs (lower latency, memory footprint, and energy consumption) while preserving accuracy and generalization. Network optimization techniques can be substantially divided into several groups: 1) designing efficient architectures, 2) designing architectures considering hardware constraints, 3) knowledge distillation, 4) network quantization, and 5) network pruning.

For the relevance of the topics covered in this thesis, in the next paragraphs, we cover quantization and pruning strategies, respectively.

#### Quantization

Quantization is the process of mapping discrete values belonging to a large input set into output values belonging to a smaller countable set. In DNNs, quantization is a technique used to reduce the size of a model by converting its highprecision floating-point weights to lower-precision representations, such as 16-bit or 8-bit floating-point or fixed-point formats. This conversion leads to improvements in model size, inference speed, and resource utilization without compromising accuracy significantly. Quantization is particularly beneficial for reducing memory bandwidth requirements and enhancing cache utilization during model deployment. Additionally, quantization can be employed to simplify and optimize the computational pipeline of large-scale models, that are anyway too big to fit embedded devices. For instance, large language models (LLMs) can achieve excellent performance on various tasks [12, 157] but their huge memory footprint and computational overhead increase the deployment cost and energy consumption. By quantizing both weights and activations using low-bit integers [153], it is possible to reduce GPU memory requirements and speed up the processing-intensive operations.

Quantization approaches vary based on the model, requiring prior knowledge and extensive fine-tuning for successful implementation. Challenges and trade-offs arise in terms of accuracy and model size, especially with low-precision integer formats like 4-bit fixed-point, which can have a limited dynamic range and lead to accuracy loss during conversion from higher-precision floating-point representations.

Assuming to have a neural network with *L* layers, whose learnable parameters (denoted as  $\theta$ ) and hidden activations (denoted as  $h_i$  for layer *i*) stored in floating point precision, the goal of quantization is to reduce the precision of both  $\theta$  weights and  $h_i$  intermediate activations to low-precision, with minimal loss of accuracy.

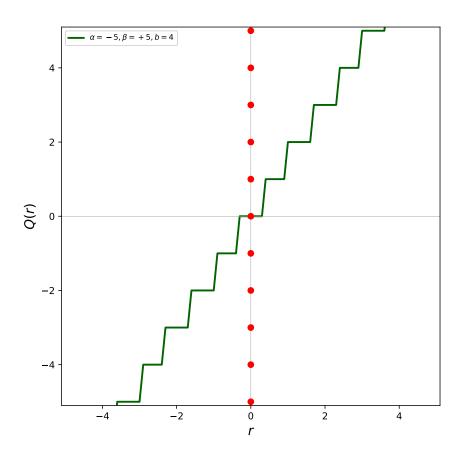

A common quantization function [62, 103]  $Q(\cdot)$  used in DNNs is expressed as follows:

$$Q(r) = Int\left(\frac{r}{S}\right) - Z \tag{1.1}$$

where *r* is the real-valued input, *S* is the real-valued scaling factor, *Z* is the integer zero point, and *Int* ( $\cdot$ ) approximates a real value to an integer value with a rounding operation. Equation 1.1 is known as *uniform quantization* because the quantized values are equally spaced, as depicted in Figure 1.2. The inversion of Equation 1.1, known as *dequantization*, can be used to recover *r* real values from *Q*(*r*) quantized values, as reported below:

$$\widetilde{r} = S\left(Q\left(r\right) + Z\right) \tag{1.2}$$

Recovered  $\tilde{r}$  values do not match exactly the original r values due to the rounding operation.

The scaling factor *S* uniformly divides the range of real values, as reported below:

$$S = \frac{\beta - \alpha}{2^b - 1} \tag{1.3}$$

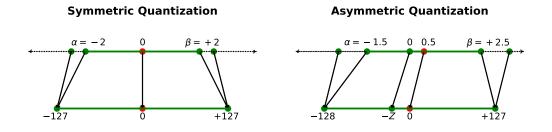

where  $[\alpha, \beta]$  denotes the range of real values and *b* is the quantization bitwidth. In order to compute the scaling factor *S*, the range  $[\alpha, \beta]$  must be determined through a process named *calibration*. When  $\alpha \neq -\beta$  the Equation 1.3 is referred to as *asymmetric quantization*, as it changes the zero representation between real and quantized values (Figure 1.3). In asymmetric quantization, a typical choice for the parameters is  $\alpha = r_{min}$ ,  $\beta = r_{max}$ . By choosing  $\alpha = -\beta$ , Equation 1.3 is referred to as *symmetric* quantized to a symmetric quantization.

FIGURE 1.2: Uniform quantization function. Real values of *r* are mapped into lowprecision quantized values (marked with red dots) Q(r). The distance between quantized red values is constant in uniform quantization. The green plot represents the quantization function that converts values from floating-point to integer representation (the corresponding red dots).

*quantization*, as it preserves the zero point representation (Figure 1.3). In symmetric quantization, a common choice is to set  $-\alpha = \beta = \max(|r_{max}|, |r_{min}|)$ . Asymmetric quantization better exploits the quantized range than symmetric quantization when adopted to quantize unbalanced data, such as outputs of the ReLU activation function. On the other side, symmetric quantization simplifies the computation as it sets Z = 0, resulting in:

$$Q\left(r\right) = Int\left(\frac{r}{S}\right) \tag{1.4}$$

FIGURE 1.3: On the left it is illustrated an example of symmetric quantization (using a restricted range of [-127, +127]) that preserves zero representation. On the right an example of asymmetric quantization.

The determination of the clipping range  $[\alpha, \beta]$  is typically executed statically both for weights and activations as the dynamic determination of the range for the activations is too computationally expensive. The range for weights can be statically determined at the end of the training by freezing the parameters before inference. For activations, the range is calculated by feeding the network with a series of calibration samples and computing the resulting range for each activation that needs to be quantized.

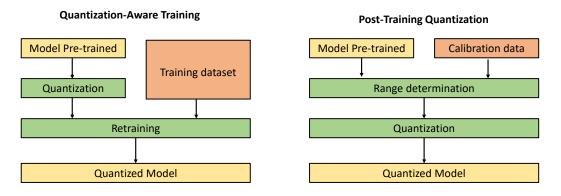

The quantization of weights and activations inevitably introduces approximations that could degrade model accuracy. It is therefore necessary to slightly change quantized values. This can be achieved by retraining the model, through a process called Quantization-Aware Training (QAT), or performed without re-training, referred to as Post-Training Quantization (PTQ). Both processes are illustrated in Figure 1.4.

FIGURE 1.4: Flow chart of the steps required to perform Quantization-Aware Training (on the left) and Post-Training Quantization (on the right).

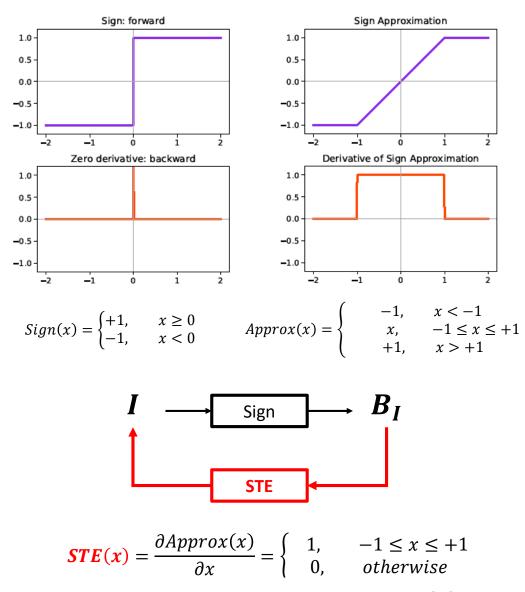

Quantization-aware training is a technique that simulates the quantization process during model training, helping to prepare the model for quantization. In QAT, forward and backward passes are executed on floating-point values which have been approximated using Equations 1.1 and 1.2. The execution of backward passes using floating-point precision is essential as quantized gradients could lead to zero gradient updates with high error. In QAT the Equation 1.1 is not differentiable and even worse, its gradient is zero almost everywhere. A common approach used to address this issue is to approximate the gradient of Equation 1.1 with the Straight Through Estimator [9] (STE), which substantially ignores the quantization operation by approximating gradient with the identity function. STE plays a central role also in Binary Neural Networks and it is further discussed in Section 2.2. The main drawback of QAT is the computation effort required to retrain the model. This process could require hundreds of epochs to recover floating-point accuracy.

A valuable alternative to QAT is represented by Post-Training Quantization, which quantizes weights and activations without any post-training phase [6, 17, 22, 33, 34, 35, 36, 52, 59, 77, 80, 97, 104, 125]. Unlike QAT, which necessitates a large portion of the training dataset, PTQ can be applied to use cases where the availability of data is limited or unbalanced. However, PTQ, as it uses a limited set of training data, yields lower accuracy compared to QAT.

The deployment of a quantized model can happen using directly the *integer-only quantization* or by *simulating quantization*. In the first case, a real quantized graph is deployed where all the operations are executed using integer arithmetic (e.g. 8-bit) and it can provide memory-saving and processing speed-up. Instead, the simulated

quantization generates a fake quantized graph where model weights are stored using integer precision, but the computationally expensive convolutions and matrix multiplications are performed using floating point precision. So, fake quantized graphs cannot provide good efficiency as they require to quantize/dequantize activations before each floating-point operation. Additionally, the execution of the graph requires more memory as all the intermediate activations have to be stored using floating-point precision. Nevertheless, fake quantization can be employed in scenarios that are bandwidth-bound rather than compute-bound. The comparison between integer-only and fake quantization graphs is depicted in Figure 1.5 (more detailed discussions on this topic can be found in [103, 37]).

FIGURE 1.5: Comparison of the steps required in simulated quantization (Left) and integer-only quantization (Right).

#### Pruning

Network pruning involves the removal of redundant parameters or neurons that do not significantly contribute to the accuracy of results. Research on network pruning can be broadly categorized into sensitivity calculation and penalty-term methods [116] and recent works have shown continued interest and improvements in both categories or a combination of them. New pruning techniques have also been developed, and modern approaches can be classified based on various aspects, including whether pruning is structured or unstructured (depending on whether the pruned network is symmetric or not), neuron and connection pruning (based on the pruned element type), and static versus dynamic pruning. In the latter, the distinction between static and dynamic pruning lies in when the pruning steps are performed, offline for static pruning, while dynamic pruning occurs during runtime.

Magnitude-based pruning, introduced by Han et al. [48], involves iteratively removing weights below a certain threshold, fine-tuning the network, and repeating the process until accuracy begins to degrade. The method was applied to various networks, including LeNet [75] on MNIST, as well as AlexNet [72] and VGG16 [127] on ImageNet. The results showed that the number of weights could be significantly reduced without sacrificing accuracy. The study emphasized the benefits of iterative pruning, showing that earlier layers are more sensitive to pruning, and iterative pruning is more effective than one-shot pruning. Pruning a weight means setting it to zero generating a sparse weight representation that can lead both to memory reduction and processing speed-up. Han et al. achieved an impressive  $40 \times$  compression rate reduction on AlexNet and VGG16. Additionally, Guo et al. [45] noted a limitation of magnitude pruning, where important weights might be prematurely removed. To address this, they proposed Dynamic Network Surgery (Dyn Surg), maintaining a mask indicating which weights to remove or retain in each training cycle.

In the realm of pruning, methods that operate at the granularity of filters and channels offer advantages over those dealing with sparse-weight matrices, as the former can leverage existing optimizations in many toolkits without requiring specialized libraries or hardware for sparse matrices. Approaches to filter and channel pruning generally fall into three categories:

- **Data-dependent channel pruning methods**: These methods operate on the premise that when presented with different inputs, output channels (or feature maps) should exhibit variations since they are designed to detect discriminative features.

- **Data-independent pruning methods**: These techniques utilize properties of filters and output channels, such as the proportion of zeros present, to determine which filters and channels should be pruned. These methods do not rely on specific data but focus on inherent characteristics.

- Optimization-based channel approximation pruning methods: These methods employ optimization techniques to reconstruct filters that approximate the output feature maps. The goal is to recreate filters that capture the essential information conveyed by the original ones, allowing for more informed pruning decisions.

Compared to quantization, pruning requires in general optimized libraries to take advantage of the sparse weight matrices and a specific hardware support [63, 19, 111] to be effective, as tensor processing unit or general purpose SIMD do not offer dedicated instructions. Mixing quantization with pruning can guarantee good speed-up improvements  $(3 - 4 \times)$ , as shown by Han et al. [48].

### 1.2 Datalogic Use Cases

Datalogic is a company that produces and sells devices used to automatically capture and identify data, operating in many market segments, such as retail, health care, transportation, logistics, and manufacturing. A representative set of Datalogic products is reported in Figure 1.6. Some of them (*Powerscan, Hand-Scanner*, *QuickScan, Rida* and *Memor*) are battery-powered, therefore requiring efficient processing to increase battery duration (adopting a low-power embedded CPU). Instead, other devices (such as *AV series*) employing more powerful CPUs, are cablepowered as they are used to analyze a huge amount of data with real-time constraints. All the devices shown in Figure 1.6 are equipped with an input sensor used to extract information from the scene: 1D/2D CMOS or CCD sensors but also 3D cameras. In general, the requirements (specific for each application/product) of depth-of-field (DOF) and field-of-view (FOV) force the adoption of high-resolution

With SeriesWith SeriesWith SeriesWith SeriesPowerscanHand-ScannerQuickScanRidaImage: SeriesWith SeriesWith SeriesWith SeriesWith SeriesSeriesMemorGrybonMagelanMagelanAv series

FIGURE 1.6: Example of devices produced by Datalogic.

input sensors that are processing-hungry. The data-processing step usually represents the most critical part of Datalogic devices that must be efficient and optimized to reduce latency. By leveraging AI technology it would be possible to increase the performance of the devices but accurate considerations must be made. AI cannot slow down the actual processing even though could increase the accuracy of the results. Therefore, the scope of this work is focused primarily on deploying efficient deep neural networks on Datalogic devices. On such devices, which are usually limited in terms of memory, power (many devices are battery-powered), and computing capabilities, the deployment of neural network models can be challenging. Indeed, considering the barcode decoding scenario, even the low-end devices usually have to process images, having a resolution of  $1280 \times 1024$ , at a frame rate varying from 30 to 60 frames per second. In a simple use case scenario, with a frame rate of 30 fps, the time budget available to analyze each video stream image is around 30 milliseconds. Considering an off-the-shelf shallow model, such as MobileNet [57, 121, 70] or EfficientNet [130, 131], the inference time of its 8-bit quantized version (using technique introduced in section 1.1.3) on a Raspberry Pi 3B is around 300<sup>1</sup> milliseconds for an input image resolution of  $224 \times 224$ , as reported in [40]. This means that a huge speed-up is required to equip Datalogic devices with AI technology without adopting additional dedicated hardware such as a Tensor Processing Unit (TPU), ASIC, or FPGA that would increase the overall cost and power of the system. In Chapter 5, we present some real-world applications running on edge devices showing some preliminary details and solutions using the techniques reported in Chapters 3 and 4.

#### 1.2.1 Open Issues in DNNs

Despite the aforementioned advantages of DNNs and CNNs, some other negative aspects persist, by preventing the deployments of such models on Datalogic's devices (Figure 1.6). In particular, the most important investigated within this thesis are reported below:

<sup>&</sup>lt;sup>1</sup>Single thread computation using TF Lite with XNN-Pack.

- **Computationally inefficiency**. Deep Learning is computationally very demanding, requiring consistent computational power and time to train deep architectures. Even though many powerful GPUs (or specialized hardware such as TPU) are available for the training of large models, the deployment of such models on edge or embedded devices is still challenging because of a lack of resources. Neural networks are usually trained using 32-bit floating-point computation which is more inefficient compared to fixed-point computation. Moreover, many embedded CPUs are not equipped with floating-point units (FPUs) resulting in prohibitive forward pass timings. Some optimization techniques, such as quantization, have been adopted to speed up the computation but the processing load is still not acceptable for many industrial-embedded applications. In Chapter 3, some optimization techniques that allow to speed up Binary Neural Networks are introduced.

- Memory demanding. Deep Learning relies on a deep sequence of layers used to extract features to be propagated along the model. The memory necessary to execute the training and the inference is often too high to accommodate these models on embedded devices. The reduced volatile memory (RAM) available on such tiny systems usually does not fit the memory constraints, limiting or even preventing the usage of neural networks.

- Poor availability of frameworks for on-device training. Many inference engines, used to execute forward pass of neural networks, are available on the market, such as Tensorflow Lite, OpenVINO, ONNX Runtime and STMicro-electronics X-Cube-AI or NanoEdgeAI. They can handle many kinds of layers supporting both floating-point and fixed-point computation. Unfortunately, they completely miss the necessary implementations to execute efficient on-device training. This limitation prevents the deployment of models that can continuously learn on-device.

- Lack of adaptability. Despite the great improvements achieved in recent years, DNNs still reach poor performances when applied to the target application that inevitably differs from the training data. To face the continual learning challenges offered by real-world use cases, a DNN should be able to distill or eventually learn the core skills or concepts necessary to reach a goal. Ideally, neural networks should be able to incrementally improve when unknown data or problems are encountered. Unfortunately, Deep Learning and the iterative learning procedure (gradient-based) are not sufficient to achieve this level of adaptability and DNNs usually incur in the *catastrophic forgetting* issue. This research field, applied to efficient and quantized models, has been only marginally addressed in the literature. In Chapter 4, some continual learning solutions that work in combination with binary neural network models are presented.

To address previous DNN limitations, many strategies have been proposed but unfortunately, when a low-power device is used to accommodate a quite computationally demanding task with challenging processing constraints, state-of-the-art techniques are not sufficient to guarantee good performances, and further optimizations are requested.

#### **1.2.2** Contributions of this thesis

Binary Neural Networks (Chapter 2) demonstrated to be a valid solution to deploy models on tiny low-power devices as they do not require the multiply-andaccumulate operation, relying exclusively on bitwise and popcount arithmetic. Additionally, BNNs heavily reduce the memory footprint of the models as they need to use only 1-bit for weights and activations. Therefore, BNNs represent a valid alternative to off-the-shelf models such as MobileNet, to be incorporated within Datalogic devices as they reach good speed-up preserving an accuracy comparable to non-binary models.

Pushing further research into binary neural networks is a fundamental element in empowering Datalogic devices with AI technology. Therefore, to facilitate the adoption of deep learning-based solutions within Datalogic products, extending them beyond the current predominant use of traditional and hand-crafted computer vision algorithms, the next points require to be addressed:

- *Efficiency in BNN data flow*. Despite the great advancements proposed in the literature, only a few works proposed solutions benchmarked on real embedded devices without using dedicated hardware such as FPGA or TPU. Most of the solutions proposed rely on floating-point computation to execute non-binary layers, therefore mixing quantized (binary) with floating-point computation. By improving BNN data flow it is possible to further reduce inference time and remove the constraint of using a floating-point unit, not available on many tiny devices (Section 3.1).

- *Fully-binary model*. Almost all the works on BNNs do not binarize the input layer of the model as the binarization of the first layer usually introduces a high accuracy gap compared to the equivalent model with the input layer in floating-point. The binarization of the first layer offers the opportunity to completely remove floating-point calculus allowing a simpler deployment on FPGA or ASIC devices, as the floating-point unit usually dominates the amount of silicon chip used (Section 3.2).

Furthermore, real-world applications require a certain level of adaptability to the constantly changing environment. The ability of the systems to adapt their behaviors represents a crucial feature for the widespread adoption of such devices. Many works in literature addressed the incremental or continual learning task but only a few of them focused on low bit-width efficient models. Putting effort into making a model computationally efficient is important as much as letting it adapt to new data acquired. The continual learning solution, to be employed in real-world applications, should investigate the following points, all related to the so-called *on-device learning* (as reported in Chapter 4):

- Operate with limited memory available. Training a model requires much more memory compared to the model memory footprint (weights) [83]. To avoid the catastrophic forgetting issue, a useful technique adopted is to replay past samples when learning new data. This approach requires additional memory to store past samples, further increasing the total memory demand. On embedded devices such memory amount is often challenging and ad-hoc optimization is requested to fit the constraints.

- *Learn with a truly-quantized model.* Network training is executed with floatingpoint precision to guarantee enough precision in gradients computation and

update. Unfortunately, models deployed on embedded devices are usually quantized (or binarized) to be more efficient. Improving model adaptability by learning with quantized weights and activation represents a great challenge that requires investigations to balance the trade-offs.

• *Handle unknown scenarios*. A system deployed on real devices should have the capability to handle unexpected scenarios and tasks. If a system is restricted to a specific setting then it is challenging for the system to learn and act autonomously and effectively.

## Chapter 2

# **Binary Neural Networks (BNNs)**

Binary Neural Networks (BNNs) are a specific type of neural network where the activations and weights in all hidden layers, usually except for the input and output layers, are represented with 1-bit values. BNNs can be seen as a highly compressed variant of NN (including Convolutional Neural Networks, CNNs), as they share the same structure but differ in the precision of their activations and weights. BNNs specifically focus on the technique of binarization, which involves converting 32-bit activations and weights into 1-bit values. This binarization process is used both to reduce the storage requirements of the model and also to minimize matrix computation costs by utilizing XNOR and popcount operations. Research by Rastegari et al. [113] has demonstrated that BNNs could achieve memory savings 32 times greater and perform convolution operations  $58 \times$  faster than their 32-bit CNN counterparts. In traditional CNNs, a significant portion of computational costs is attributed to matrix multiplication within the convolution operation. The basic convolution operation, excluding bias, can be mathematically expressed as:

$$Z = I \circledast W, \tag{2.1}$$

where *I* and *W* represent the activations and weights, respectively, while *Z* is the output. This multiplication involves a significant number of floating-point operations, including both multiplication and addition, which can increase latency during neural network inference. To address this issue, Courbariaux et al. [23] proposed the first vanilla BNN architecture, reported in the next section.

An artificial neural network requires two fundamental processes: forward propagation and backward propagation. Forward propagation involves the information flow from the input layer (located on the left side) to the output layer (located on the right side) as depicted in Figure 2.1. This process is also referred to as model inference, where the network makes predictions based on the given input. On the other hand, backward propagation entails the movement of information from the output layer (right) back to the input layer (left), as shown in Figure 2.1. This process is responsible for fine-tuning the model's weights through a technique known as gradient descent.

Sections 2.1 and 2.2 specifically delve into the functioning of BNN during forward propagation and backward propagation, respectively.

FIGURE 2.1: BNN vs. CNN.

### 2.1 Forward Propagation

The neural cell serves as a fundamental computational unit in the forward propagation of a neural network. In contrast to the 32-bit Convolutional Neural Network (CNN), the neural cell in the Binary Neural Network (BNN) incorporates binarization step for the input activations (I) and weights (W) prior to the convolution operation. This binarization step aims to represent the floating-point values of the activations and weights using a single bit. Figure 2.2 illustrates the disparity in computation steps within a neural cell along the forward path between the naive BNN and the 32-bit CNN. The sign function (Equation 2.2) is widely adopted to binarize both weights and activations:

$$sign(x) = \begin{cases} +1 & \text{if } x \ge 0\\ -1 & \text{otherwise.} \end{cases}$$

(2.2)

After binarization, the binary weights (Equation 2.3) and activations (Equation 2.4) can be expressed respectively as:

$$B_{W} = sign\left(W\right) \tag{2.3}$$

$$B_I = sign\left(I\right). \tag{2.4}$$

By using Equations 2.3 and 2.4 we can express the binary convolution operation as:

FIGURE 2.2: Internal steps of a 32-bit CNN neuron compared to a naive BNN cell.

FIGURE 2.3: Naive BNN forward propagation compared to 32-bit CNN. Popcount operation refers to Equation 2.6.

| Binary Activations $B_I$ | Binary Weights $B_W$ | XNOR Results % |

|--------------------------|----------------------|----------------|

| -1(0)                    | -1(0)                | +1(1)          |

| -1(0)                    | +1(1)                | -1(0)          |

| +1(1)                    | -1(0)                | -1(0)          |

| +1(1)                    | +1(1)                | +1(1)          |

TABLE 2.1: BNN XNOR operations

$$B_Z = B_I \circledast B_W = sign\left(I\right) \circledast sign\left(W\right). \tag{2.5}$$

Because  $B_I$  and  $B_W$  possible values are -1, +1, the output of the binary multiplication corresponds to the result of XNOR, as shown in Table 2.1. This result allows us to replace the expensive matrix multiplication of Equation 2.5, with a lightweight bitwise XNOR and popcount operation. The complete formula that uses XNOR and popcount to compute the binary convolution is expressed in Equation 2.6

$$B_Z = popcount \left(XNOR\left(B_W, B_I\right)\right) * 2 - N_{size},$$

(2.6)

*popcount* returns the number of bits set to 1 and is already available on all modern CPUs (ARM, Intel).  $N_{size}$  is the input size of the XNOR operation; in Figure 2.3 is equal to 9. Figure 2.3 shows a comparison of the convolution operation between a standard CNN and a BNN.

### 2.2 Backward Propagation

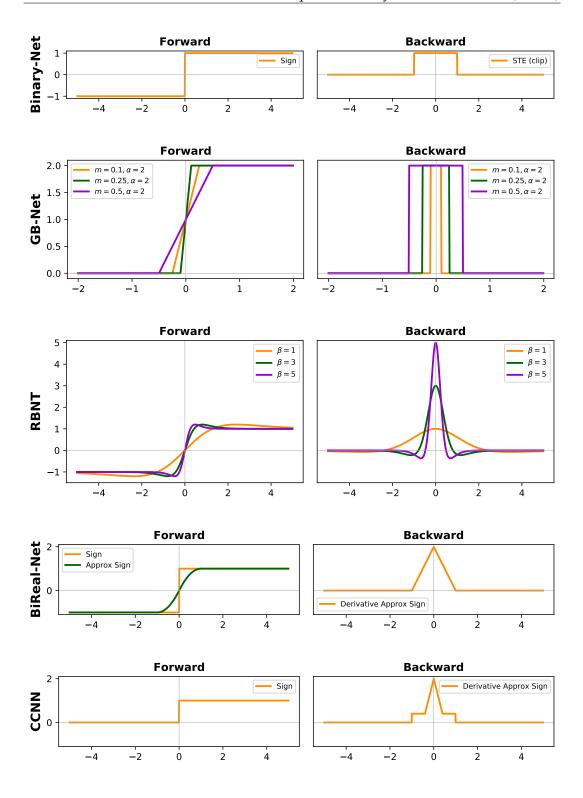

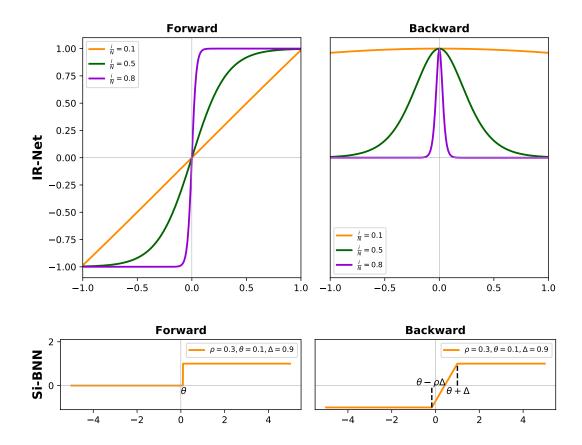

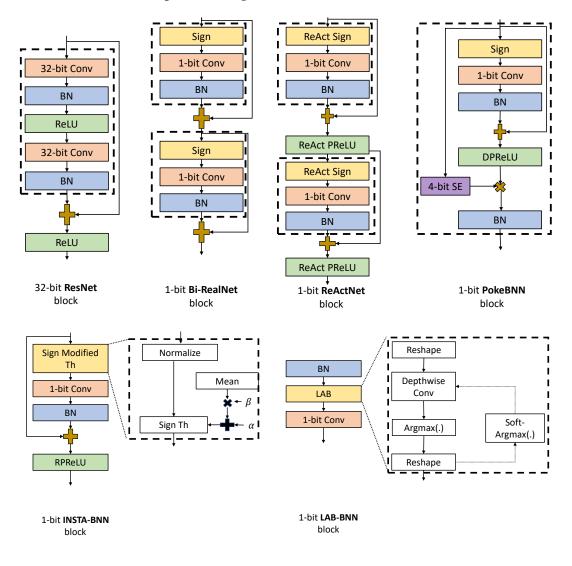

The binarization function 2.2 is not differentiable, and even worse, is zero almost everywhere. So, the traditional gradient descent method based on a backward propagation algorithm would not work for learning the binary weights. To overcome this challenge, Courbariaux et al. [23] utilize the technique known as the straight-through estimator (STE) [133, 9] to learn binary weights during backward propagation, as reported below: