ALMA MATER STUDIORUM Università di Bologna

# DOTTORATO DI RICERCA IN INGEGNERIA ELETTRONICA, TELECOMUNICAZIONI E TECNOLOGIE DELL'INFORMAZIONE - (ET-IT)

Ciclo 36

Settore Concorsuale: 09/E3 - Elettronica Settore Scientifico Disciplinare: ING-INF/01 - Elettronica

## Experimental Characterization and Modeling of GaN-based Power Devices Reliability

Presentata da: Maurizio Millesimo

**Coordinatore Dottorato** Prof. Aldo Romani **Supervisore** Prof. Claudio Fiegna

**Co-supervisore** Prof. Andrea Natale Tallarico

Esame finale anno 2024

# Keywords

Semiconductor Power Device Gallium Nitride (GaN) High-Electron Mobility Transistor (HEMT) p-GaN Gate HEMTs Reliability Lifetime TCAD Simulations

# Acknowledgements

First of all, I would like to express my gratitude to my supervisors Prof. Andrea Natale Tallarico and Prof. Claudio Fiegna who gave me the opportunity to start this PhD. I appreciate their guidance in the semiconductor physics and, in particular, in the reliability field.

I would like to thank Dr. Stefaan Decoutere who gave me the opportunity to perform research activities at the Interuniversity Microelectronics Centre (imec).

Special thanks to imec researchers I met or worked with. In particular, Dr. Matteo Borga, Dr. Niels Posthuma and Dr. Benoit Bakeroot for the the scientific and stimulating discussions we had during my PhD.

Il più grande ringraziamento va ai miei genitori e alla mia ragazza. Grazie per l'enorme supporto morale che mi avete dato durante questo percorso.

Thank you all, Maurizio <u>ii</u>\_\_\_\_\_

## Abstract

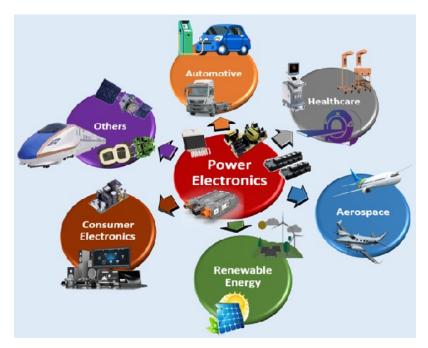

Nowadays, power electronics plays a fundamental role in enhancing energy efficiency, reducing  $CO_2$  emissions, and promoting sustainable development, which is crucial for a more environmentally conscious and energy-efficient future. Its applications are spreading everywhere, including energy saving, renewable energy systems, electric/hybrid vehicles, industrial automation, aerospace, etc.. In particular, power electronics deals with the conversion and the control of electric power, using high-efficiency, reliable and even more compact electronic converters based on switching mode semiconductor power devices. In this scenario, gallium nitride (GaN) devices grown on silicon substrates are of great interest due to their capability to operate at relatively high voltage and frequency with higher efficiency and comparable cost of the silicon counterparts. Although GaN transistors demonstrate impressive characteristics, as emerging technology, there are still many degradation mechanisms affecting the device performance and reliability that need further investigation and understanding. More specific, charge trapping and de-trapping mechanisms, triggered by high electric fields and temperatures, are the main causes leading to the transistor degradation/failure.

This PhD research project is focused on the comprehensive identification, characterization, and modeling of the root causes that limit the gate reliability of AlGaN/GaN high electron mobility transistors (HEMTs) featuring pGaN gate technology, by accelerated life tests and electro-thermal simulations. Regarding this topic, this dissertation provides the following contributions:

- gate biases, temperatures, and device geometry dependencies of the long-term gate reliability in GaN-based power HEMTs with p-type gate under DC stress conditions are analyzed. Two failure mechanisms have been identified, hence, accurate field-acceleration fitting models are adopted to estimate the gate lifetime.

- a combined experimental/simulation analysis has been performed to study the time-dependent gate breakdown (TDGB) under pulse stress

conditions. Thanks to this investigation, reliability issues introduced by the switching operation, which could not be identified by DC stress analysis, have been highlighted.

• an extensive analysis on the role of both switching frequency (ranging from 100 kHz to 1 MHz) and duty cycle (from 10% to 90%) on the time-dependent gate breakdown of high electron mobility transistors (HEMTs) with Schottky metal to p-GaN gate. Findings of this analysis are useful both for further technology improvement and for GaN-based power circuit designers.

In addition, storage/release mechanisms within the buffer layers responsible for ON-resistance degradation ( $\Delta R_{ON}$ ) have been investigated by means of back-gating current deep-level transient spectroscopy (I-DLTS) and Technology Computer Aided Design (TCAD) simulations. A genetic algorithm has been employed to accurately fit the experiments allowing to understand the temperature, stress-bias, and stress-time dependence of  $\Delta R_{ON}$ . Moreover, devices featuring different buffer layers composition are compared, providing useful information for the epi-stack optimization, i.e., vertical down scaling.

# List of Figures

| 1.1 | Application fields of Power electronics [1]                        | 1  |

|-----|--------------------------------------------------------------------|----|

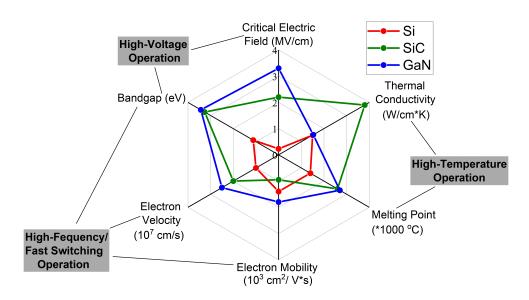

| 1.2 | Radar chart of the different physical material properties of Si,   |    |

|     | SiC and GaN [13, 14]. $\ldots$                                     | 5  |

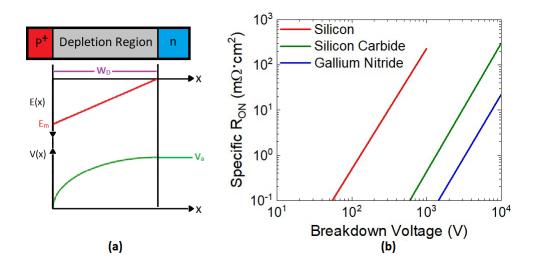

| 1.3 | Electric field distribution in a reverse biased $P + /N$ junction  |    |

|     | [15] (a) and specific ON-resistance versus breakdown voltage       |    |

|     | (theoretical limits) of different semiconductor (b) [16]           | 6  |

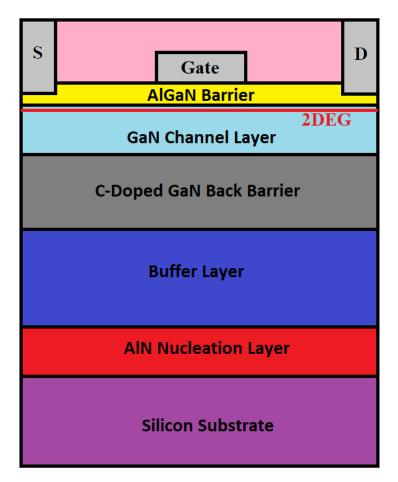

| 1.4 | Sketch (not to scale) of a typical GaN-on-Si HEMT epi-stack        |    |

|     | composition.                                                       | 9  |

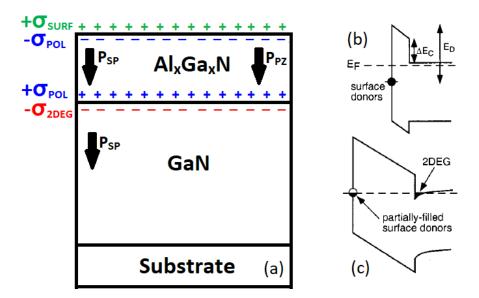

| 1.5 | Schematic of charge distribution and polarization orientation      |    |

|     | within the Ga-face AlGaN/GaN heterstructure (a). Band di-          |    |

|     | agram illustrating the surface donor model with the undoped        |    |

|     | AlGaN barrier thickness (b) less than, and (c) greater than        |    |

|     | the critical thickness for the formation of the 2DEG [34]          | 11 |

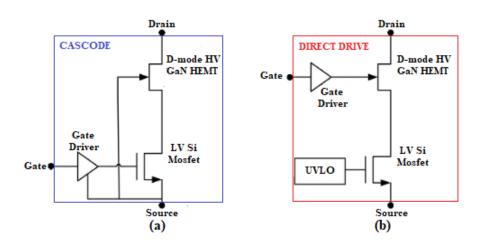

| 1.6 | Schematic of (a) Cascode and (b) Direct-drive GaN HEMTs            |    |

|     | for normally-off operation.                                        | 13 |

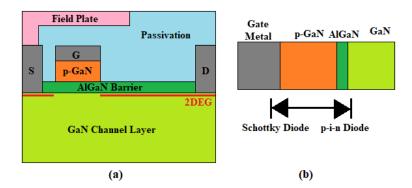

| 1.7 | Schematic of a normally-off HEMT with a p-GaN gate (a) and         |    |

|     | back-to back diode for gate leakage reduction (b).                 | 13 |

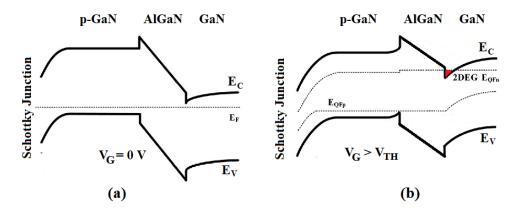

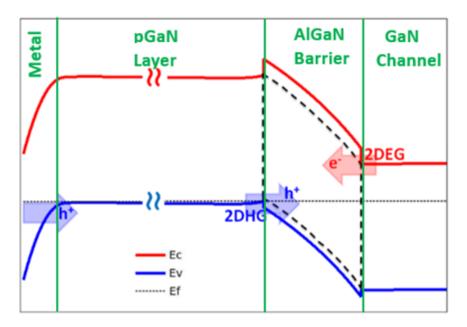

| 1.8 | Simulated band-diagram of p-GaN HEMTs along the gate epi-          |    |

|     | stack for (a) $V_G = 0$ V and (b) $V_G > V_{TH}$ .                 | 14 |

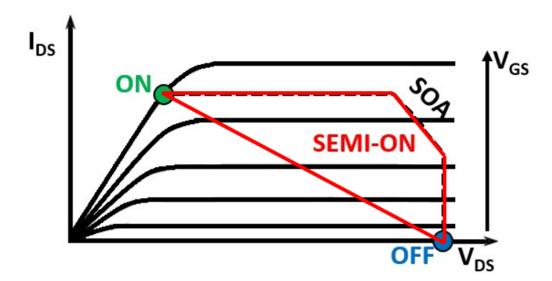

| 1.9 | $I_D - V_D$ curve of a hard-switching transition from on- to off-  |    |

|     | state (and viceversa) with an inductive load.                      | 15 |

|     |                                                                    |    |

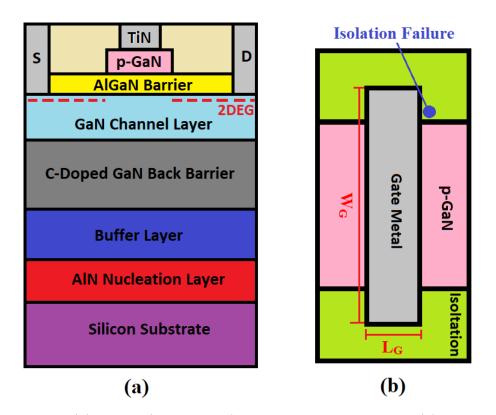

| 2.1 | (a) Sketch (not to scale) of the device under tests. (b) Repre-    |    |

|     | sentation of the top-view of the gate region                       | 29 |

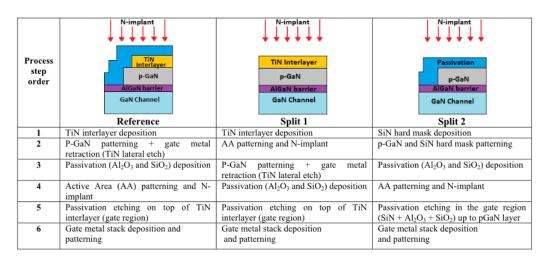

| 2.2 | Process flow for three different isolation process options (from   |    |

|     | the left): Reference process, Split1 and Split2. Note that the     |    |

|     | process steps 1 is equivalent at the first step after the $p$ -GaN |    |

|     | layer deposition                                                   | 30 |

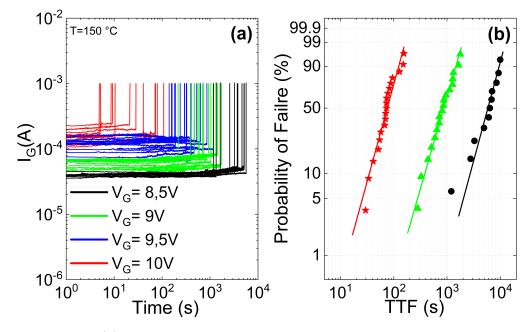

| 2.3 | (b) Gate leakage monitored during the CVS tests at VG 8.5V         |    |

|     | (black line), 9V (green line), 9.5V (blue line) and 10V (red       |    |

|     | line). (b) Weibull plot of TTF extrapolated from (a). $\ldots$ .   | 31 |

|     |                                                                    |    |

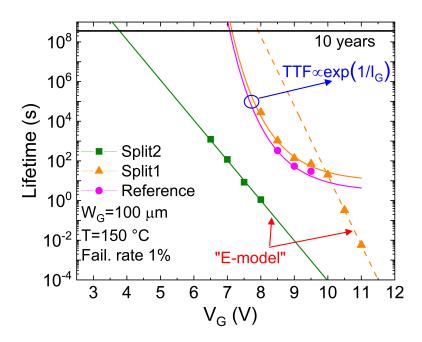

| 2.4  | Lifetime comparison between Reference, Split 1, and Split 2<br>isolation process options. Depending on the kind of breakdown<br>mechanism, if area- or isolation-related, the TTF is fit with |          |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|      | the "E-model" or with the " $TTF \propto exp(1/I_G)$ " model, respec-                                                                                                                         |          |

|      | tively. Failure criterion: 1% of failure at 150°C extrapolated                                                                                                                                |          |

|      | from the Weibull plots.                                                                                                                                                                       | 32       |

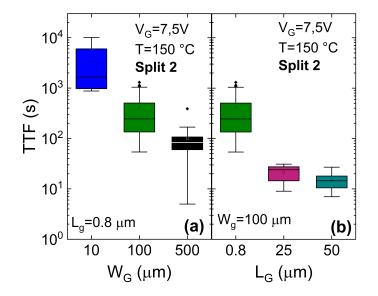

| 2.5  | a) Gate width and (b) gate length dependency of the TTF at                                                                                                                                    | 02       |

| 2.0  | $V_G = 7.5 V$ and $T = 150^{\circ}C$ for devices fabricated with the process Split 2. About 16 devices per group have been stressed.                                                          |          |

|      | $TTF$ scales with both $W_G$ and $L_G$                                                                                                                                                        | 33       |

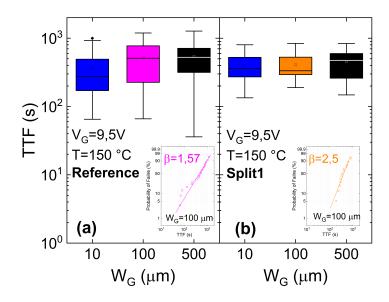

| 2.6  | Gate width dependency of the TTF at $V_G = 9.5$ V and $T =$                                                                                                                                   | 00       |

| 2.0  | $150^{\circ}C$ for devices fabricated with (a) Reference and (b) Split                                                                                                                        |          |

|      | 1 process option. In both cases, $TTF$ does not scale with $W_G$ .                                                                                                                            |          |

|      | The insets show the Weibull plot of devices featuring $W_G =$                                                                                                                                 |          |

|      | $100 \ \mu m$ . Different TTF distributions (Weibull slope $\beta$ ) are                                                                                                                      |          |

|      | observed                                                                                                                                                                                      | 34       |

| 2.7  | Optical microscopy image after the isolation region failure shown                                                                                                                             | υı       |

|      | for the first time in $[11]$ .                                                                                                                                                                | 34       |

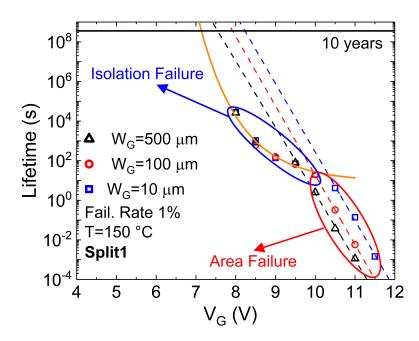

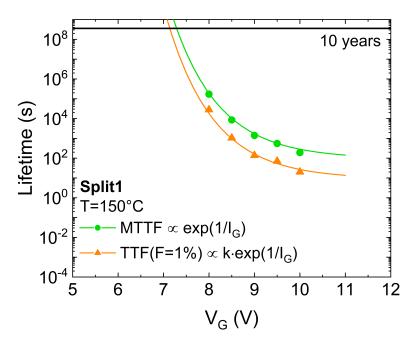

| 2.8  | Lifetime plot in the case of Split 1 process on devices with three                                                                                                                            | 01       |

|      | different gate widths ( $W_G$ ). Different $V_G$ dependencies of the                                                                                                                          |          |

|      | TTF, ascribed to different failure mechanisms, are observed.                                                                                                                                  |          |

|      | Failure criterion: $1\%$ of failure at 150°C extrapolated from the                                                                                                                            |          |

|      | Weibull plots, with slope $\beta \sim 2.5$ (not shown).                                                                                                                                       | 35       |

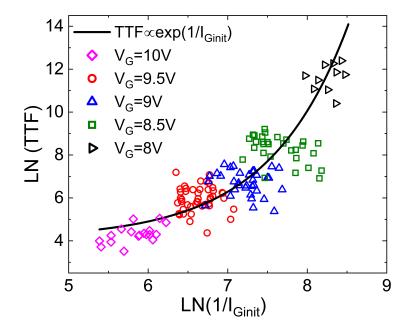

| 2.9  | Correlation between the inverse of the initial gate leakage cur-                                                                                                                              |          |

|      | rent ( $I_{Ginit}$ ), monitored at the beginning of CVS tests, and                                                                                                                            |          |

|      | the TTF, in the case of Split 1. An exponential relationship                                                                                                                                  |          |

|      | has been identified $[8]$ by means of a statistical analysis at $T$                                                                                                                           |          |

|      | $= 150^{\circ}C.$                                                                                                                                                                             | 36       |

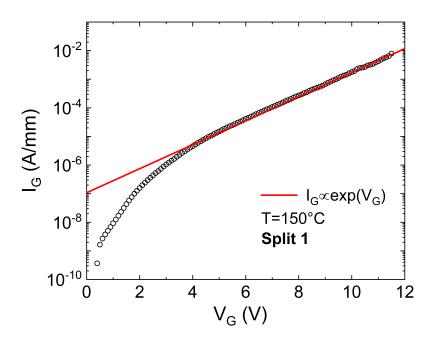

| 2.10 | Measured gate leakage characteristics (symbols) and fitting model                                                                                                                             |          |

|      | (line) at $T = 150^{\circ}C$ in the case of Split 1. For $V_G \ge 4V$ , the                                                                                                                   |          |

|      | gate current shows a purely exponential dependency                                                                                                                                            | 37       |

| 2.11 | Lifetime plot comparison in the case of the TTF extrapolate                                                                                                                                   |          |

|      | with $F = 1\%$ (triangles) and the mean time-to-failure (MTTF)                                                                                                                                |          |

|      | (circles). The process is Split 1 and the temperature is $150^{\circ}C$ .                                                                                                                     |          |

|      | To better fit the TTF at $F = 1\%$ , the empirical model has been                                                                                                                             |          |

|      | multiplied by a constant $k < 1. \ldots \ldots \ldots \ldots \ldots$                                                                                                                          | 38       |

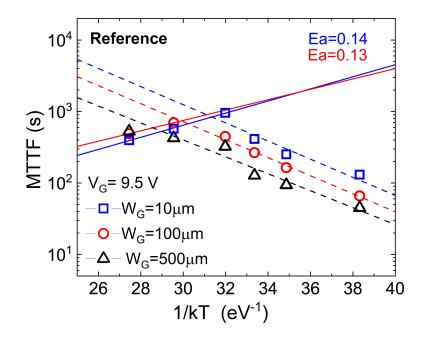

| 2.12 | Arrhenius plot at $V_G = 9.5$ V showing the MTTF of devices                                                                                                                                   |          |

|      | featuring three different gate widths $(W_G)$ : 10, 100, and 500                                                                                                                              |          |

|      | $\mu m$ . The fitting dashed and solid lines are referred to the area                                                                                                                         |          |

|      | failure and isolation region failure, respectively. The isolation                                                                                                                             | <u> </u> |

|      | process option is the Reference                                                                                                                                                               | 39       |

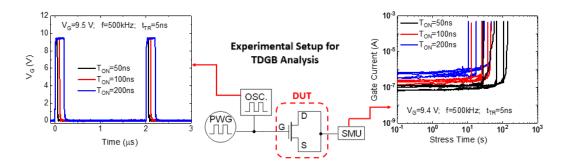

| 3.1  | Schematic of the experimental setup for time-dependent gate<br>breakdown analysis under pulsed stress conditions                                                                                                                                                                                                                         | 47 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

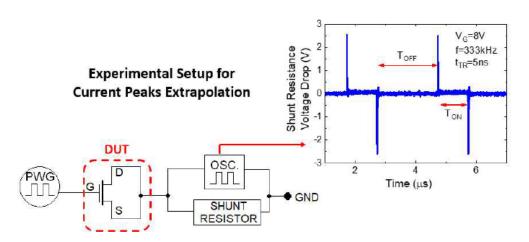

| 3.2  | Schematic of the experimental setup for current peaks extrap-<br>olation at the transition phases.                                                                                                                                                                                                                                       | 49 |

| 3.3  | Schematic of band diagram Simulated band diagram of the gate<br>epi-stack at $V_G = 0$ V. Moreover, the tunneling component and<br>the spatial and energy window of the acceptor traps uniformly                                                                                                                                         |    |

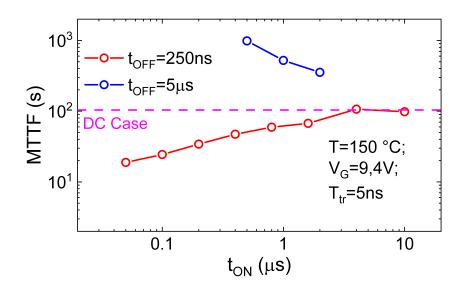

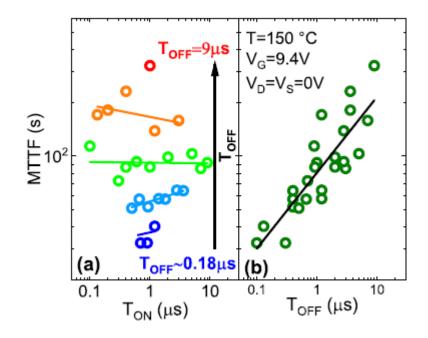

| 3.4  | distributed in the AlGaN barrier layer (dashed line) are sketched.<br>ON-Time dependency of the Mean Time-to-Failure with two<br>fixed OFF time, i.e., 250 ns (red) and 5 $\mu$ s (blue). Results<br>of time-dependent gate breakdown tests with $V_G = 9.4$ V, $T =$<br>150 °C and $t_{TR} = 5ns$ . Each experimental data point is the |    |

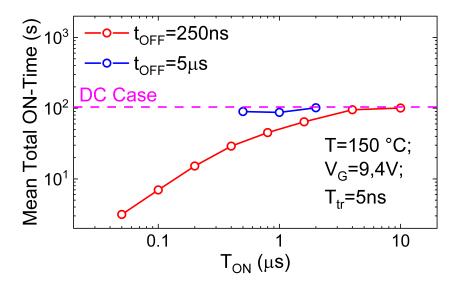

| 3.5  | average over 7-15 devices                                                                                                                                                                                                                                                                                                                | 51 |

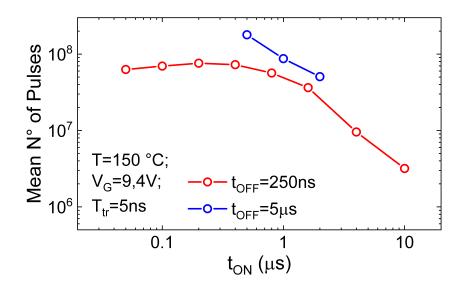

| 3.6  | Results have been derived from the MTTF in Fig. 3.4<br>ON-Time dependency of the Mean Number of Pulses with two<br>fixed OFF time, i.e., 250 ns (red) and 5 $\mu$ s (blue). Results                                                                                                                                                      | 52 |

| 3.7  | have been derived from the MTTF in Fig. 3.4 OFF-Time dependency of the Mean Total ON-Time (a) and Mean Number of Pulses (b) with fixed ON-time (1 $\mu$ s.). Results of time dependent gate breakdown tests with VG = 9.4 V, $T = 150^{\circ}C$ and three different $t_{TR}$ (5 ns, 20 ns and 80 ns).                                    | 52 |

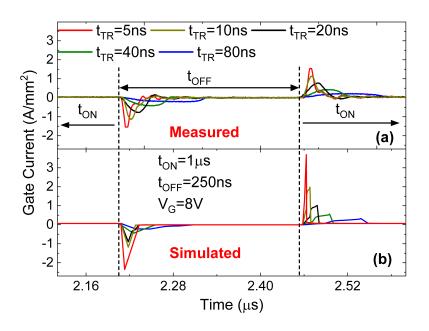

| 3.8  | Each experimental data point is the average over 7-15 devices.<br>Measured (a) and simulated (b) gate current with $t_{ON}=1 \ \mu s$                                                                                                                                                                                                    | 53 |

| 3.9  | and $t_{OFF} = 250$ ns and different transition times                                                                                                                                                                                                                                                                                    | 54 |

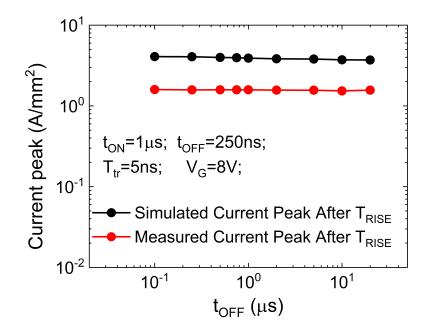

| 3.10 | (black) current peak at the switching phase                                                                                                                                                                                                                                                                                              | 55 |

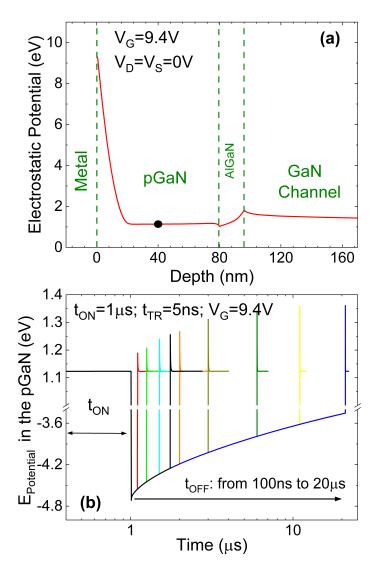

| 3.11 | trostatic potential monitored in the semi-floating p-GaN layer<br>with different OFF-Time (b)                                                                                                                                                                                                                                            | 56 |

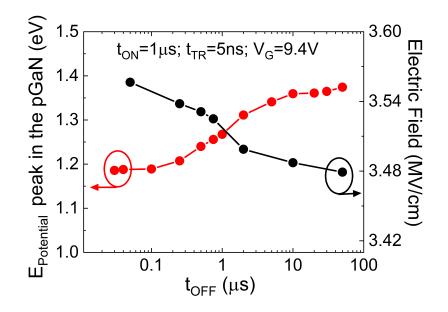

| 3.12 | corresponding mean electric field evaluated across the depletion<br>region of the Schottky junction                                                                                                                                                                                                                                      | 57 |

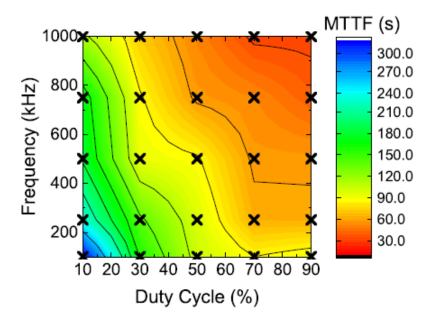

|      | the MTTF. The symbols "x" represent the implemented stress conditions                                                                                                                                                                                                                                                                    | 58 |

| 3.13        | (a) ON-Time and (b) OFF-Time dependency of the MTTF at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

|             | $V_G = 9.4$ V and $T = 150^{\circ}C$ . Each MTTF point is the result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 50        |

| 014         | of 10 stressed devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 59        |

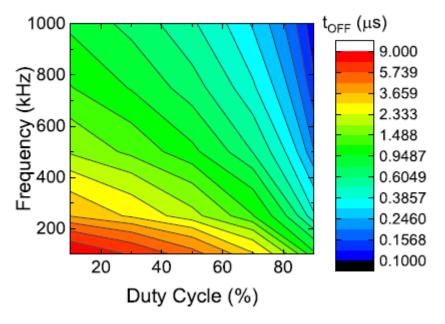

| 3.14        | Contour plot showing how the OFF-Time changes with both                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <u>co</u> |

| 0.15        | the frequency and the duty cycle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 60        |

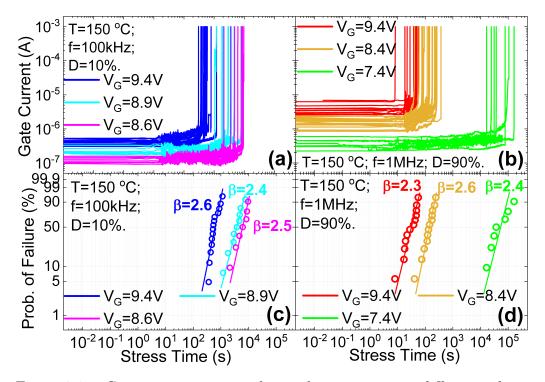

| 3.15        | Gate current monitored over the stress time at different volt-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

|             | ages in the case of (a) $f = 100$ kHz; $D = 10\%$ and (c) $f = 1$<br>MHz; $D = 90\%$ with the corresponding Weibull plots (b) and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |

|             | (d), respectively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 61        |

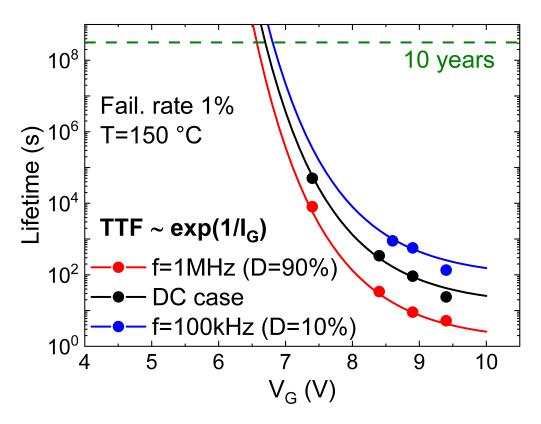

| 3.16        | Lifetime comparison under three different stress conditions: f                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 01        |

| 0.10        | = 1 MHz and $D = 90%$ (red), DC (black), $f = 100 kHz$ and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

|             | $D = 10\%$ (blue). " $TTF \propto exp(1/I_G)$ " fitting model has been                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|             | adopted for all conditions. Failure criterion: $1\%$ at $150^{\circ}C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |

|             | extrapolated from the Weibull plots                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62        |

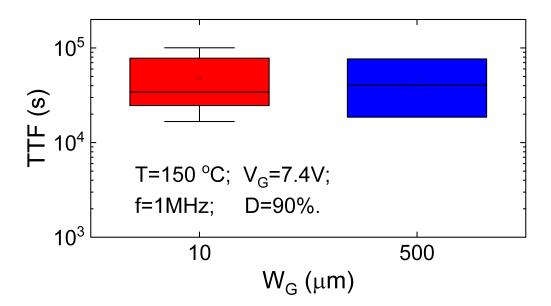

| 3.17        | Area (gate width) dependency of the gate TTF at $V_G = 7.4 V$ ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

|             | f = 1 MHz, D = 90% and $T = 150°C.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 63        |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

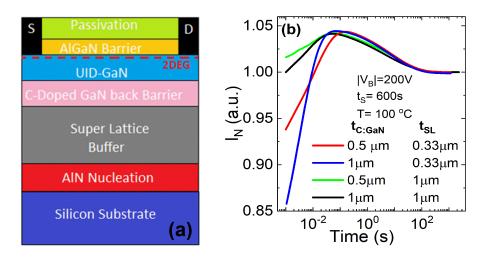

| 4.1         | Sketch (not to scale) of the device under test and the epi-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |

|             | structure. (a) Recovery current transient for different buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

|             | configurations. (b) Stressing phase has been performed for 600<br>s with $ V_B  = 200$ V at $T = 100^{\circ}C.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 71        |

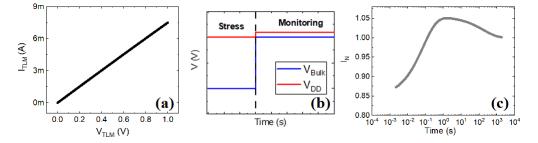

| 4.2         | I-DLTS experimental steps: (a) voltage ramp to monitor the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11        |

| 1.2         | fresh current and (b) stressing and monitoring phase. Mea-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |

|             | sured current during the monitoring phase and normalized wrt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |

|             | the fresh current. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72        |

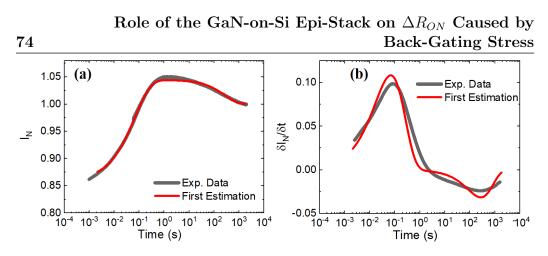

| 4.3         | (a) Recovery current transient compared with the first estima-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |

|             | tion and (b) their derivatives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74        |

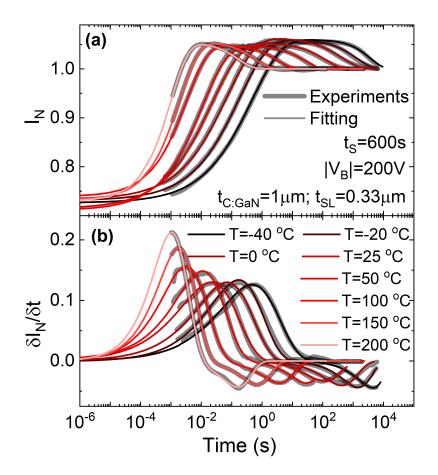

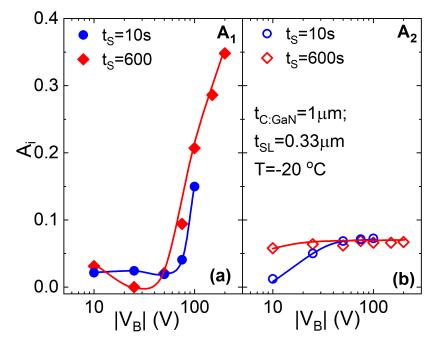

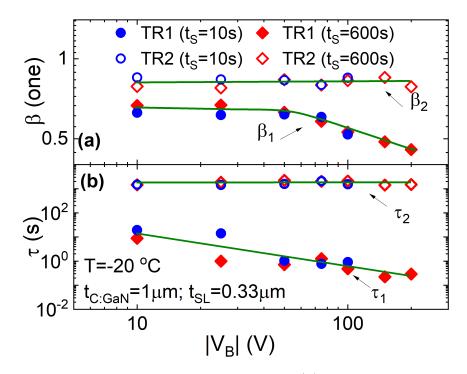

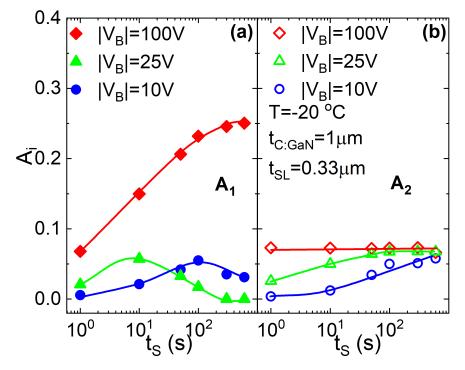

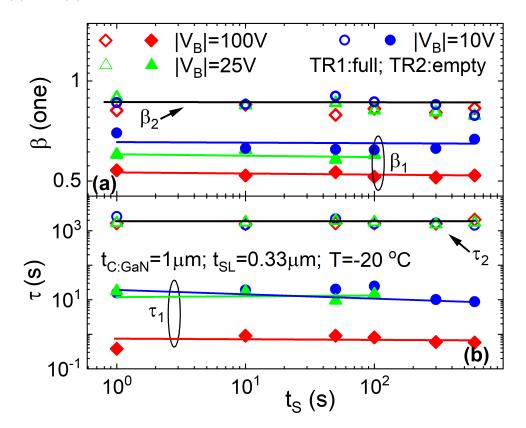

| 4.4         | (a) Recovery current transient and (b) its derivative with dif-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |

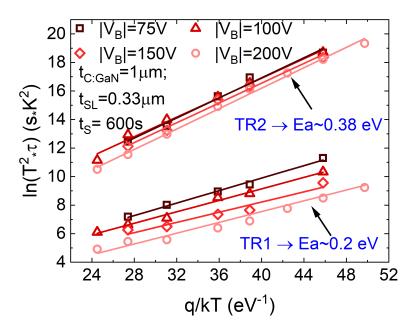

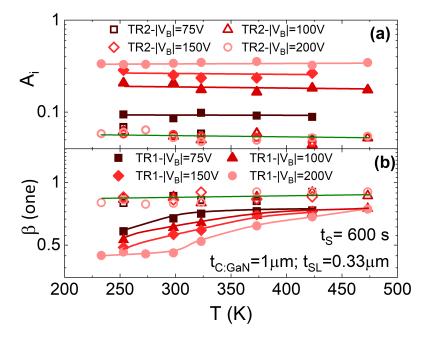

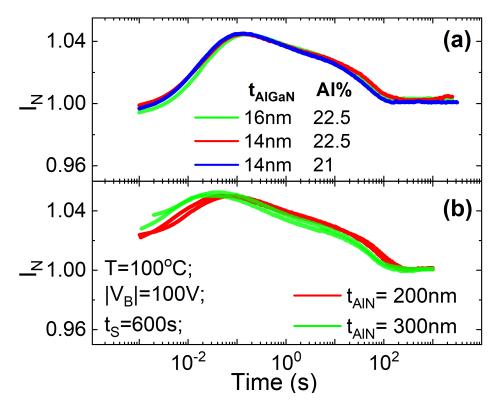

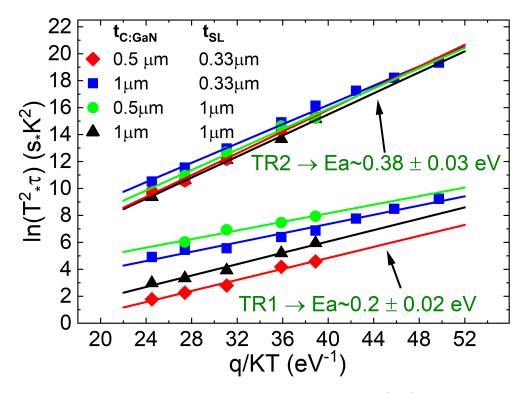

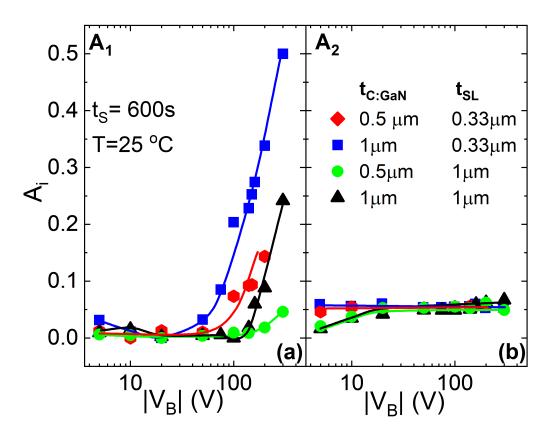

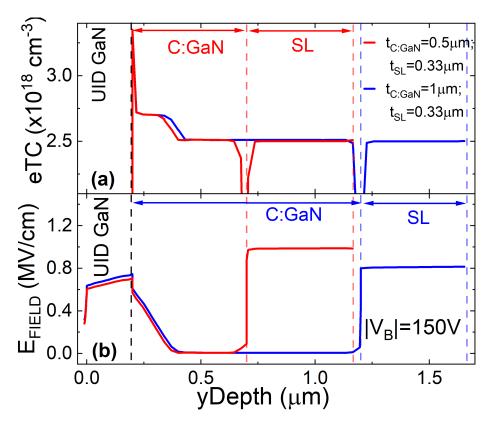

|             | ferent temperatures ranging between - $40^{\circ}C$ and $200^{\circ}C$ . The                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |